# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI MICROCOMPUTERS

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### DESCRIPTION

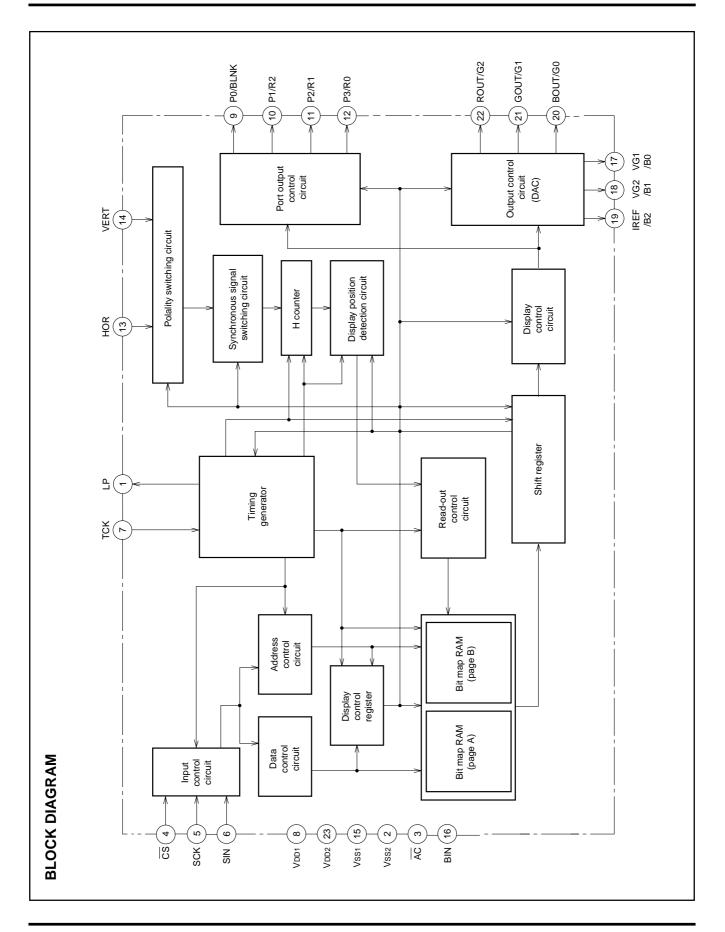

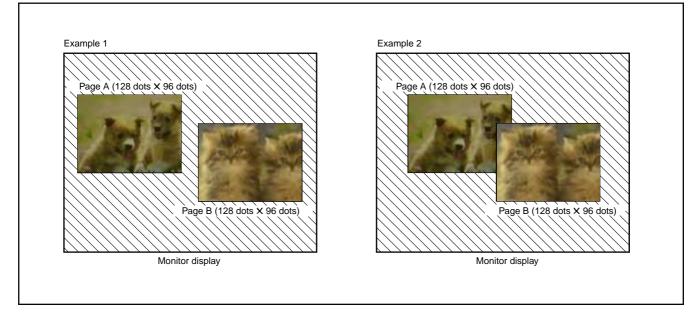

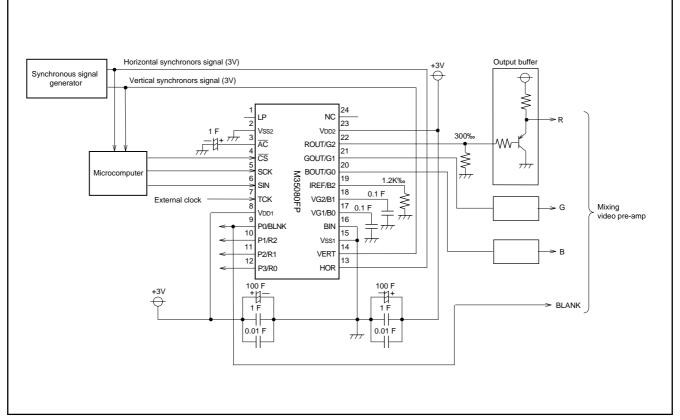

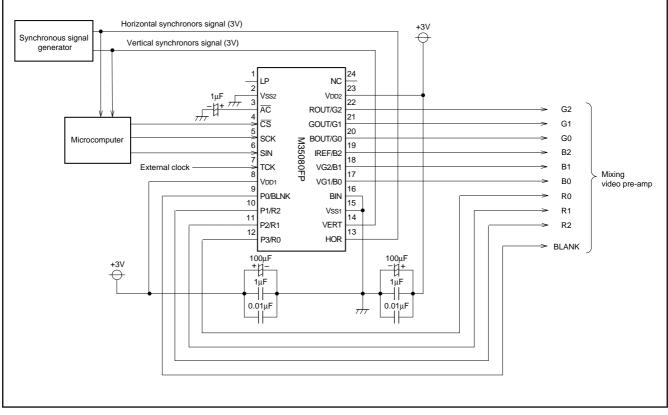

The M35080FP is a bitmap pattern display control IC can display on the screen. Display frequency can operate in 3.3MHz to 20MHz, and is equipped with the analog RGB output (512 colors / 260k colors) and the digital RGB output (512 colors) function. Moreover, 2 pages (horizontal 128 dot X vertical 96 dots/page) display can be simultaneously performed on 1 screen.It uses a silicon gate CMOS process and it housed in a 24-pin shrink SOP package.

### FEATURES

| • Pixel composition Eight kinds (Can be chosen from the following) |

|--------------------------------------------------------------------|

| horizontal 128 dots X verical 96 dots X 2 pages                    |

| horizontal 192 dots X verical 64 dots X 2 pages                    |

| horizontal 256 dots X verical 48 dots X 2 pages                    |

| horizontal 384 dots X verical 32 dots X 2 pages                    |

| horizontal 32 dots X verical 384 dots X 2 pages                    |

| horizontal 48 dots X verical 256 dots X 2 pages                    |

| horizontal 64 dots X verical 192 dots X 2 pages                    |

| horizontal 96 dots X verical 128 dots X 2 pages                    |

| RGB output                                                         |

| Analog RGB outputROUT, GOUT,BOUT                                   |

| Number of colors displayed                                         |

| double-screen display (3 bits each of RGB) : 512 colors            |

| one-screen display (6 bits each of RGB) : 260 K colors             |

| Digital RGB output R0 to R2, G0 to G2, B0 to B2,                   |

| Number of colors displayed                                         |

| one and double-screen display (3 bits each of RGB) : 512 colors    |

| • Bit map RAM 1000h to 3AFFh                                       |

|                                                                    |

|                                                                    |

| Display input frequency range                                      |

| external input Fosc = 3.3 MHz to 20 MHz                            |

| <ul> <li>Horizontal synchronous input frequency</li> </ul>         |

| H.sync = 10 kHz to 20 kHz                                          |

| Output ports (Combination port output)                             |

|                                                                    |

| • DAC                                                              |

| • Operating voltage 2.7 V to 3.3 V                                 |

### APPLICATION

Liquid crystal display, Plasma display, Multi-scan monitor

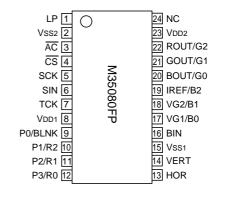

#### **PIN CONFIGURATION (TOP VIEW)**

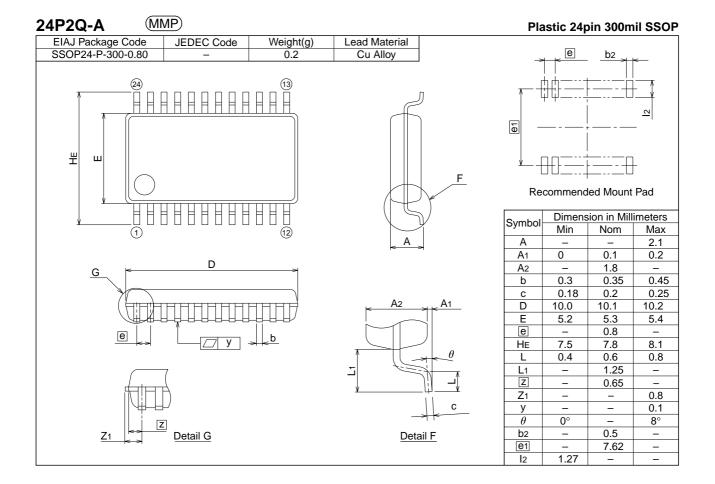

Outline 24P2Q-A

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### **PIN DESCRIPTION**

| Symbol  | Pin name                                 | Input/<br>Output | Function                                                                                                                                                              |

|---------|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP      | Test output                              | Output           | Test pin. Open this pin.                                                                                                                                              |

| VSS2    | Earthing pin                             | _                | Connect to GND.                                                                                                                                                       |

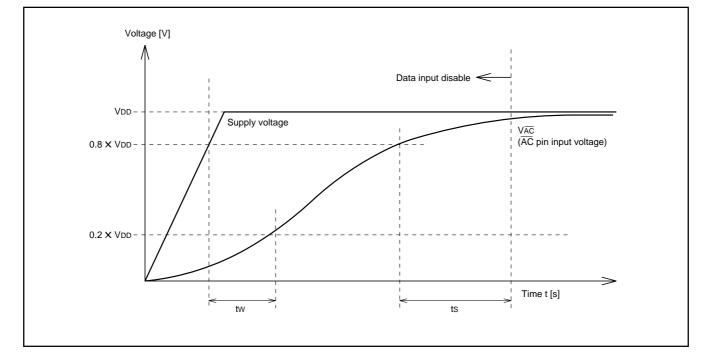

| ĀĊ      | Auto-clear input                         | Input            | When "L", this pin resets the internal IC circuit. Hysteresis input. Built-in pull-up resistor.                                                                       |

| CS      | Chip select input                        | Input            | This is the pin for chip select input. Set "L" level at serial data transmission. Hysteresis input.                                                                   |

| SCK     | Serial clock input                       | Input            | At $\overline{CS}$ pin is "L" level, SDA pin serial data is taken in when SCL rises. Hysteresis input. Built-in pull-up resistor.                                     |

| SIN     | Serial data input                        | Input            | This is the pin for serial input of display control register and display RAM data. Also, this pin output acknowledge signal. Hysteresis input. Nch open-drain output. |

| тск     | External clock                           | Input            | This is the pin for external clock input.                                                                                                                             |

| VDD1    | Power pin                                | _                | Digital power supply. Connect to +3V with the power pin.                                                                                                              |

| P0/BLNK | Port P0 output                           | Output           | This is a general purpose port output at analog RGB output. Outputs port output or BLNK signal.<br>Outputs BLNK signal at digital RGB output.                         |

| P1/R2   | Port P1 output                           | Output           | This is the output port output at analog RGB output.                                                                                                                  |

|         | R2                                       |                  | Outputs R2 signal at digital RGB output.                                                                                                                              |

| P2/R1   | Port P2 output                           | Output           | This is the output port output at analog RGB output.                                                                                                                  |

| P3/R0   | R1<br>Port P3 output                     | Output           | Outputs R1 signal at digital RGB output.<br>This is the output port output at analog RGB output.                                                                      |

| F3/KU   | R0                                       | Output           | Outputs R0 signal at digital RGB output.                                                                                                                              |

| HOR     | Horizontal synchro-<br>nous signal input | Input            | Input horizontal synchronous signal. (Hysteresis input.)                                                                                                              |

| VERT    | Vertical synchro-<br>nous signal input   | Input            | Input vertical synchronous signal. (Hysteresis input.)                                                                                                                |

| VSS1    | Earthing pin                             | _                | Connect to GND.                                                                                                                                                       |

| BIN     | Test pin                                 | _                | Test pin. Connect to GND.                                                                                                                                             |

| VG1/B0  | Reference voltage<br>output 1            | Output           | Use reference voltage output 1 of DAC for analog RGB output at analog RGB output. Connect to capacitor.                                                               |

|         | B0                                       |                  | Output B0 signal at digital RGB output.                                                                                                                               |

| VG2/B1  | Reference voltage<br>output 1            | Output           | Use reference voltage output 2 of DAC for analog RGB output at analog RGB output. Connect to capacitor.                                                               |

|         | B1                                       |                  | Output B1 signal at digital RGB output.                                                                                                                               |

| IREF/B2 | Reference voltage<br>output 2            | Output           | The pin connects resistors which convert voltage current at analog RGB output.                                                                                        |

|         | B2                                       |                  | Output B2 signal at digital RGB output.                                                                                                                               |

| BOUT/G0 | Analog B signal output<br>G0             | Output           | Output analog B signal at analog RGB output(Current output). Connect to load resistance.                                                                              |

| GOUT/G1 | Analog G signal output                   | Output           | Output analog G signal at analog RGB output(Current output). Connect to load resistance.<br>Output G1 signal at digital RGB output.                                   |

| ROUT/G2 | Analog R signal output                   | Output           | Output analog R signal at analog RGB output(Current output). Connect to load resistance.<br>Output G2 signal at digital RGB output.                                   |

| VDD2    | Power pin                                | _                | Digital power supply. Connect to +3V with the power pin.                                                                                                              |

| NC      | NC                                       | _                | NC pin. Open.                                                                                                                                                         |

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### **MEMORY CONSTITUTION**

Address 000016 to 000716 are assigned to the display RAM, address 100016 to 3AFF16 are assigned to bitmap RAM. The internal circuit is reset and all display control registers (address 000016 to 000716) are set to "0" when the AC pin level is "L". And then, bit map RAM is not erased and be undefinited. This memory has 2page composition (an address is Page A and page B community) of the memory for page A, and the memory for page B. Registers PAGEONA and PAGEONB perform page control at the time of writing in data. For detail, refer to "DATA INPUT EXAMPLE". Memory constitution is shown in Figure 1 to 10.

| Address | DAF | DAE     | DAD     | DAC     | DAB    | DAA  | DA9 | DA8 | DA7     | DA6     | DA5     | DA4     | DA3  | DA2    | DA1     | DA0     |

|---------|-----|---------|---------|---------|--------|------|-----|-----|---------|---------|---------|---------|------|--------|---------|---------|

| 000016  | _   | _       | _       | _       | _      | -    | _   | _   | _       | _       | _       | _       | _    | -      | PAGEONB | PAGEONA |

| 000116  | -   | -       | -       | -       | -      | YM2  | YM1 | YM0 | BLANK1  | BLANK0  | ALLON   | DSPON   | _    | WIDTH2 | WIDTH1  | WIDTH0  |

| 000216  | -   | VSIZE1  | VSIZE0  | _       | -      | _    | VP9 | VP8 | VP7     | VP6     | VP5     | VP4     | VP3  | VP2    | VP1     | VP0     |

| 000316  | -   | -       | -       | -       | -      | _    | HP9 | HP8 | HP7     | HP6     | HP5     | HP4     | HP3  | HP2    | HP1     | HP0     |

| 000416  | -   | ANADIG2 | ANADIG1 | ANADIG0 | SYNCCK | TEST | -   | -   | -       | -       | -       | POLV    | POLH | MODE2  | MODE1   | MODE0   |

| 000516  | Ι   | I       | -       | _       | -      | -    |     | -   | -       | -       | -       | _       | -    | -      | -       | _       |

| 000616  | 1   | DACON   | _       | _       | -      | _    | _   | _   | _       | _       | _       | _       | _    | _      | _       | _       |

| 000716  | -   | -       | _       | -       | -      | _    | -   | _   | SBLANK3 | SBLANK2 | SBLANK1 | SBLANK0 | PTD3 | PTD2   | PTD1    | PTD0    |

Fig.1 Memory constitution (Display Control register)

Note : Address 000016 and 000416 to 000716 are Page A and B common registers. The writing of data is made regardless of registers PAGEONA and PAGEONB. As for addresses 000116 to 000316, register of Page A and Page B exists for every page (common to an address.) When write data in the memory for page A, and write data in the memory for page B, set it as register PAGEONA = "1" at register PAGEONB = "1." When both of PAGEONA and PAGEONB are set to "1", data can be simultaneously written in both the memory for page A, and the memory for page B. Address 0XXX16 other than addresses 000016 to 000716 are write-protected.

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address | DA | \F I | DAE | DAD | DAC | DAB | DAA | DA9    | DA8    | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots X 96 dots |

|---------|----|------|-----|-----|-----|-----|-----|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 100016  | Γ  |      | •   |     | •   |     |     |        |        | •      |        |     |     | •   | •   |     |     | Dot 1 to 16 of line 1                                 |

| 100116  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

| 100216  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 33 to 48 of line 1                                |

| 100316  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 49 to 64 of line 1                                |

| 100416  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 65 to 80 of line 1                                |

| 100516  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 1                                |

| 100616  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 1                               |

| 100716  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 113 to 128 of line 1                              |

| 100816  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 2                                 |

| 100916  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 2                                |

| 100A16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 33 to 48 of line 2                                |

|         |    |      |     |     |     |     | E   | Bit ma | ıp RAI | M (R0  | ) data |     |     |     |     |     |     |                                                       |

| 120616  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 95                               |

| 120716  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 95                              |

| 120816  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 113 to 128 of line 95                             |

| 12F916  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 96                                |

| 12FA16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 96                               |

| 12FB16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 33 to 48 of line 96                               |

| 12FC16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 49 to 64 of line 96                               |

| 12FD16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 65 to 80 of line 96                               |

| 12FE16  |    |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 12FF16  | L  |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 130016  | Γ  |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

|         |    |      |     |     |     |     |     | ι      | inuse  | d area | a      |     |     |     |     |     |     | _                                                     |

| 13FF16  | L  |      |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

#### Fig.2 Memory constitution (Bit map RAM (R0))

Notes : Bit map RAM (Addresses 100016 to 3AFF16) has 2-page composition of the memory for page A, and the memory for page B. When write data in the memory for page A, and write data in the memory for page B, set it as register PAGEONA = "1" at register PAGEONB = "1." When both of PAGEONA and PAGEONB are set to "1", data can be simultaneously written in both the memory for page A, and the memory for page B.

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8    | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots × 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 140016  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 140116  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | E   | Bit ma | p RAI  | M (R1) | ) data |     |     |     |     |     |     |                                                       |

| 16FE16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 16FF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 170016  |     |     |     |     |     |     | u      | inused | d area | l      |     |     |     |     |     |     |                                                       |

| 17FF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

### Fig.3 Memory constitution (Bit map RAM (R1))

| Address                                 | DAF | DAE | DAD | DAC | DAB | DAA    | DA9    | DA8   | DA7    | DA6    | DA5   | DA4  | DA3   | DA2 | DA1 | DA0 | Dot composition (DAF to DA0) |

|-----------------------------------------|-----|-----|-----|-----|-----|--------|--------|-------|--------|--------|-------|------|-------|-----|-----|-----|------------------------------|

| /////////////////////////////////////// |     |     |     |     |     | 27.0.1 |        | 27.00 |        |        | 27.10 | 27.1 | 27.00 |     |     |     | at 128 dots X 96 dots        |

| 180016                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     | Dot 1 to 16 of line 1        |

| 180116                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     | Dot 17 to 32 of line 1       |

|                                         |     |     |     |     |     | I      | Bit ma | ap RA | M (R2  | ) data |       |      |       |     |     |     |                              |

|                                         |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     |                              |

| 1AFE16                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     | Dot 81 to 96 of line 96      |

| 1AFF16                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     | Dot 97 to 112 of line 96     |

| 1B0016                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     |                              |

| :                                       |     |     |     |     |     |        | ι      | unuse | d area | a      |       |      |       |     |     |     |                              |

|                                         |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     |                              |

| 1FFF16                                  |     |     |     |     |     |        |        |       |        |        |       |      |       |     |     |     |                              |

Fig.4 Memory constitution (Bit map RAM (R2))

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8   | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DAO | Dot composition (DAF to DA0)<br>at 128 dots × 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|-------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 200016  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 200116  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | ł   | 3it ma | p RAI | M (G0  | ) data |     |     |     |     |     |     |                                                       |

| 22FE16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 22FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 230016  |     |     |     |     |     |     | ι      | inuse | d area | 1      |     |     |     |     |     |     |                                                       |

| 23FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     |                                                       |

#### Fig.5 Memory constitution (Bit map RAM (G0))

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8    | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots × 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 240016  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 240116  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | I   | Bit ma | ip RAI | M (G1  | ) data | l   |     |     |     |     |     |                                                       |

| 26FE16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 26FF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 270016  |     |     |     |     |     |     | ι      | unuse  | d area | a      |     |     |     |     |     |     |                                                       |

| 27FF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

#### Fig.6 Memory constitution (Bit map RAM (G1))

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8    | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots × 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 280016  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     | ·   | Dot 1 to 16 of line 1                                 |

| 280116  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | E   | Bit ma | ıp RAI | M (G2  | ) data |     |     |     |     |     |     |                                                       |

| 2AFE16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 2AFF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 2B0016  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

|         |     |     |     |     |     |     | ι      | unuse  | d area | 1      |     |     |     |     |     |     |                                                       |

| 2FFF16  |     |     |     |     |     |     |        |        |        |        |     |     |     |     |     |     |                                                       |

Fig.7 Memory constitution (Bit map RAM (G2))

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8   | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DAC | Dot composition (DAF to DA0)<br>at 128 dots X 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|-------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 300016  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 300116  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | I   | Bit ma | ıp RA | M (B0  | ) data |     |     |     |     |     |     |                                                       |

| 32FE16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 32FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 330016  |     |     |     |     |     |     | ι      | inuse | d area | 1      |     |     |     |     |     |     |                                                       |

| 33FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     |                                                       |

#### Fig.8 Memory constitution (Bit map RAM (B0))

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8   | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots X 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|-------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 340016  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 340116  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | I   | Bit ma | ap RA | M (B1  | ) data |     |     |     |     |     |     |                                                       |

| 36FE16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 36FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 370016  |     |     |     |     |     |     | ι      | unuse | d area | a      |     |     |     |     |     |     |                                                       |

| 37FF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     |                                                       |

#### Fig.9 Memory constitution (Bit map RAM (B1))

| Address | DAF | DAE | DAD | DAC | DAB | DAA | DA9    | DA8   | DA7    | DA6    | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | Dot composition (DAF to DA0)<br>at 128 dots × 96 dots |

|---------|-----|-----|-----|-----|-----|-----|--------|-------|--------|--------|-----|-----|-----|-----|-----|-----|-------------------------------------------------------|

| 380016  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 1 to 16 of line 1                                 |

| 380116  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 17 to 32 of line 1                                |

|         |     |     |     |     |     | I   | Bit ma | ap RA | M (B2  | ) data |     |     |     |     |     |     |                                                       |

| 3AFE16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 81 to 96 of line 96                               |

| 3AFF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     | Dot 97 to 112 of line 96                              |

| 3B0016  |     |     |     |     |     |     | L      | unuse | d area | 1      |     |     |     |     |     |     |                                                       |

| 3FFF16  |     |     |     |     |     |     |        |       |        |        |     |     |     |     |     |     |                                                       |

Fig.10 Memory constitution (Bit map RAM (B2))

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### **Pixel composition**

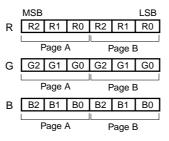

Each bit of a bit map display consists of nine bit map RAM (R0 to R2, G0 to G2, and B0 to B2.) Color setup can be specified out of 512 kinds per dot. The bit map RAM address corresponding to dot composition in case pixel composition is 128 dot x 96 dot is shown

in Fig. 11. And, the bit map RAM address corresponding to dot composition in case pixel composition is 64 dot x192 dot is shown in Fig. 12. In other pixel composition, the bit map RAM is similarly assigned in an order from the dots 1 to 16 of line 1.

| Lines | 1 to 16       | 17 to 32 | 33 to 48 | 49 to 64 | 65 to 80 | 81 to 96 | 97 to 112 | 113 to 128 |

|-------|---------------|----------|----------|----------|----------|----------|-----------|------------|

| 1     | 00016         | 00116    | 00216    | 00316    | 00416    | 00516    | 00616     | 00716      |

| 2     | 00816         | 00916    | 00A16    | 00B16    | 00C16    | 00D16    | 00E16     | 00F16      |

| 3     | 01016         | 01116    | 01216    | 01316    | 01416    | 01516    | 01616     | 01716      |

| 4     | <b>018</b> 16 | 01916    | 01A16    | 01B16    | 01C16    | 01D16    | 01E16     | 01F16      |

| 5     | 02016         | 02116    | 02216    | 02316    | 02416    | 02516    | 02616     | 02716      |

| 6     | 02816         | 02916    | 02A16    | 02B16    | 02C16    | 02D16    | 02E16     | 02F16      |

|       |               |          |          |          |          |          |           |            |

| 91    | 2D016         | 2D116    | 2D216    | 2D316    | 2D416    | 2D516    | 2D616     | 2D716      |

| 92    | 2D816         | 2D916    | 2DA16    | 2DB16    | 2DC16    | 2DD16    | 2DE16     | 2DF16      |

| 93    | 2E016         | 2E2E6    | 2E216    | 2E316    | 2E416    | 2E516    | 2E616     | 2E716      |

| 94    | 2E816         | 2E916    | 2EA16    | 2EB16    | 2EC16    | 2ED16    | 2EE16     | 2EF16      |

| 95    | 2F016         | 2F116    | 2F216    | 2F316    | 2F416    | 2F516    | 2F616     | 2F716      |

| 96    | 2F816         | 2F916    | 2FA16    | 2FB16    | 2FC16    | 2FD16    | 2FE16     | 2FF16      |

\* The numerical value in a thick frame corresponds to lower 10-bits of bit map RAM (R0 to R2, G0 to G2, B0 to B2) address. (n RAM character number : 0 to 7) Dot composition in 1 address (16 bits) is MSB.....LSB

Fig.11 Pixel composition (at 128 dots × 96 dots)

|     | _    |         |          |               |          |

|-----|------|---------|----------|---------------|----------|

|     | Dots |         |          |               |          |

| Lin | es   | 1 to 16 | 17 to 32 | 33 to 48      | 49 to 64 |

|     | 1    | 00016   | 00116    | 00216         | 00316    |

|     | 2    | 00416   | 00516    | 00616         | 00716    |

|     | 3    | 00816   | 00916    | 00A16         | 00B16    |

|     | 4    | 00C16   | 00D16    | 00E16         | 00F16    |

|     | 5    | 01016   | 01116    | 01216         | 01316    |

|     | 6    | 01416   | 01516    | <b>016</b> 16 | 01716    |

|     |      |         |          |               |          |

| 1   | 87   | 2E816   | 2E916    | 2EA16         | 2EB16    |

| 1   | 88   | 2EC16   | 2ED16    | 2EE16         | 2EF16    |

| 1   | 89   | 2F016   | 2F116    | 2F216         | 2F316    |

| 1   | 90   | 2F416   | 2F516    | 2F616         | 2F716    |

| 1   | 91   | 2F816   | 2F916    | 2FA16         | 2FB16    |

| 1   | 92   | 2FC16   | 2FD16    | 2FE16         | 2FF16    |

\* The numerical value in a thick frame corresponds to lower 10-bits of bit map RAM (R0 to R2, G0 to G2, B0 to B2) address. (n RAM character number : 0 to 7) Dot composition in 1 address (16 bits) is MSB.....LSB

Fig.12 Pixel composition (at 64 dots × 192 dots)

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### Register

| ddress ( |          |        | Contents                                                                                    |                                    |

|----------|----------|--------|---------------------------------------------------------------------------------------------|------------------------------------|

| DA       | Register | Status | Function                                                                                    | Remarks                            |

| •        |          | 0      | Writing to the memory(display control registers and Bit map RAM) for page A is disapproval. | Memory writing control for page A. |

| 0        | PAGEONA  | 1      | Writing to the memory(display control registers and Bit map RAM) for page A is permission.  |                                    |

| 1        | PAGEONB  | 0      | Writing to the memory(display control registers and Bit map RAM) for page B is disapproval. | Memory writing control for page B. |

|          | TROEOND  | 1      | Writing to the memory(display control registers and Bit map RAM) for page B is permission.  |                                    |

| 2        | _        | 0      | Set "0" to this bit.                                                                        | _                                  |

| _        |          | 1      | Can not be used.                                                                            |                                    |

| 3        | _        | 0      | Set "0" to this bit.                                                                        | _                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| 4        | _        | 0      | Set "0" to this bit.                                                                        | _                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| 5        | _        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| 6        | _        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| 7        | _        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| 8        | -        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 0      | Can not be used. Set "0" to this bit.                                                       |                                    |

| 9        | -        | 1      | Can not be used.                                                                            | -                                  |

|          |          | 0      | Set "0" to this bit.                                                                        |                                    |

| A        | -        | 1      | Can not be used.                                                                            | -                                  |

|          |          | 0      | Set "0" to this bit.                                                                        |                                    |

| В        | -        | 1      | Can not be used.                                                                            |                                    |

| С        |          | 0      | Set "0" to this bit.                                                                        | _                                  |

| <u> </u> |          | 1      | Can not be used.                                                                            |                                    |

| D        | _        | 0      | Set "0" to this bit.                                                                        |                                    |

|          |          | 1      | Can not be used.                                                                            |                                    |

| Е        | _        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

| F        | _        | 0      | Set "0" to this bit.                                                                        | -                                  |

|          |          | 1      | Can not be used.                                                                            |                                    |

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address 0 | 00116    |        |                                                                                                                   |                                                                                  |

|-----------|----------|--------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| DA        | Register |        | Contents                                                                                                          | Remarks                                                                          |

|           |          | Status | Function                                                                                                          |                                                                                  |

| 0         | WIDTHO   | 0      | WIDTH2 WIDTH1 WIDTH0 Pixel (Horizontal X Vertical)                                                                | Set the pixel composition.                                                       |

|           |          | 1      | 0         0         128 × 96 dots           0         0         1         192 × 64 dots                           |                                                                                  |

|           |          | 0      | 0         1         192 × 64 dots           0         1         0         256 × 48 dots                           | The BLNK signal of the range set up by this register is outputted at the time of |

| 1         | WIDTH1   |        | 0 1 1 384 X 32 dots                                                                                               | BLANK1, $0 = 0$ , and 0 (normal) setup.                                          |

|           |          | 1      | 1 0 0 32 X 384 dots                                                                                               |                                                                                  |

|           |          | 0      | 1         0         1         48 × 256 dots           1         1         0         64 × 192 dots                 |                                                                                  |

| 2         | WIDTH2   | 1      | 1 1 1 96 X 128 dots                                                                                               |                                                                                  |

|           |          | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

| 3         | -        | 1      | Can not be used.                                                                                                  | _                                                                                |

|           |          | 0      | Display OFF                                                                                                       |                                                                                  |

| 4         | DSPON    | 1      | Display ON                                                                                                        | _                                                                                |

|           |          | 0      | Set "0" to this bit.                                                                                              | The second second second second second                                           |

| 5         | -        | 1      | Can not be used.                                                                                                  | The measure against a character bend<br>(test bit)                               |

|           |          | 0      |                                                                                                                   | Control of blank size of                                                         |

| 6         | BLANK0   | 1      | BLANK1         BLANK0         Blank signal           0         0         Normal(Control by register WIDTH 0 to 2) | Control of blank signal.<br>(a blank setup in a bit unit is possible).           |

|           |          |        | 0 1 Control by Bit map RAM(R0)                                                                                    | Note 2                                                                           |

| 7         | BLANK1   | 0      | 1         0         Control by Bit map RAM(G0)           1         1         Control by Bit map RAM(B0)           |                                                                                  |

|           |          | 1      |                                                                                                                   |                                                                                  |

| 8         | YMO      | 0      | $R = \sum_{2}^{2} 2^{n}R_{n} - \sum_{2}^{2} 2^{n}YM_{n}$                                                          | Control of R, G and B output luminosity                                          |

|           |          | 1      | n = 0 n = 0                                                                                                       |                                                                                  |

| 9         | YM1      | 0      |                                                                                                                   |                                                                                  |

| 9         |          | 1      | when set to $R < 0$ , $R = 0$ .                                                                                   |                                                                                  |

| A         | YM2      | 0      | Same as G output and B output.                                                                                    |                                                                                  |

| A         | 11012    | 1      |                                                                                                                   |                                                                                  |

| в         |          | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

| D         | _        | 1      | Can not be used.                                                                                                  |                                                                                  |

| C         |          | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

| С         |          | 1      | Can not be used.                                                                                                  |                                                                                  |

|           |          | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

| D         |          | 1      | Can not be used.                                                                                                  |                                                                                  |

| E         | _        | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

|           |          | 1      | Can not be used.                                                                                                  |                                                                                  |

| F         | _        | 0      | Set "0" to this bit.                                                                                              |                                                                                  |

| ·         |          | 1      | Can not be used.                                                                                                  |                                                                                  |

Notes 1 : This register is consisted of 2 pages (address community) of the register for page A, and the register for page B. Writing control to each page is performed by registers PAGEONA and PAGEONB (address 000016).

2 : The bit map RAM used for blank signal control is not applicable to color setup.

### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| DA | Register  |                                 | Contents                                                                                    | Remarks                             |

|----|-----------|---------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------|

|    | rtegiotei | Status                          | Function                                                                                    | Remains                             |

| 0  | VP0       | 0                               | If VS is the vertical display start location,<br>VS = H $\times \sum_{n=0}^{9} 2^{n}$ VPn   | Setting vertical start location     |

| 1  | VP1       | ① 1                             | H: Cycle with the horizonal synchronizing pulse                                             |                                     |

| 2  | VP2       | ① 1                             |                                                                                             |                                     |

| 3  | VP3       | 0<br>1                          |                                                                                             |                                     |

| 4  | VP4       | 0<br>1                          | VS<br>VS<br>VS<br>Vote 2                                                                    |                                     |

| 5  | VP5       | 0                               | HS<br>Note 2                                                                                |                                     |

| 6  | VP6       | 0<br>1                          | Monitor display                                                                             |                                     |

| 7  | VP7       | 0<br>1                          |                                                                                             |                                     |

| 8  | VP8       | 0                               |                                                                                             |                                     |

| 9  | VP9       | 0<br>1                          |                                                                                             |                                     |

| A  | -         | ① 1                             | It should be fixed to "0".                                                                  |                                     |

| В  | _         | <ul><li>(0)</li><li>1</li></ul> | It should be fixed to "0".<br>Can not be used.                                              | _                                   |

| С  | VSIZE0    | ① 1                             | VSIZE1VSIZE0Vertical direction size001H/dot012H/dot                                         | Setting vertical direction dot size |

| D  | VSIZE1    | ()<br>1                         | 1     0     3H/dot       1     1     4H/dot   H : Synchronous of horizontal direction pulse |                                     |

| Е  | _         | <ul><li>(0)</li><li>1</li></ul> | It should be fixed to "0".<br>Can not be used.                                              |                                     |

| F  | _         | 0                               | It should be fixed to "0".<br>Can not be used.                                              | _                                   |

Notes 1 : This register is consisted of 2 pages (address community) of the register for page A, and the register for page B. Writing control to each page is performed by registers PAGEONA and PAGEONB (address 000016).

2 : Set up the horizontal and vertical display start location so that display range may not exceed it.

Set the character code "1FF16" (blank without background) for the display RAM of the part which the display range exceeds.

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Address 0 | 000316   | 1      | <b>2</b> · · · ·                                                          | 1                                 |

|-----------|----------|--------|---------------------------------------------------------------------------|-----------------------------------|

| DA        | Register | Status | Contents<br>Function                                                      | Remarks                           |

| 0         | HP0      | 0      |                                                                           |                                   |

| 0         |          | 1      | If HS is the horizontal display start location,<br>$\sum_{n=1}^{9} 2^{n}$ | Setting horizontal start location |

| 1         | HP1      | 0      | $HS = T \times \sum_{n=0}^{\infty} 2^{n} HP_{n}$<br>T: Display clock      |                                   |

| 2         | HP2      | 0      |                                                                           |                                   |

| 3         | HP3      | 0      |                                                                           |                                   |

| 4         | HP4      | 0      | vs<br>↓ Vs<br>↓ Note 2                                                    |                                   |

| 5         | HP5      | 0      | HS Display area Note 2                                                    |                                   |

| 6         | HP6      | 0      | Monitor display                                                           |                                   |

| 7         | HP7      | 0      |                                                                           |                                   |

| 8         | HP8      | 0      |                                                                           |                                   |

| 9         | HP9      | 0      |                                                                           |                                   |

| A         | _        | 0      | It should be fixed to "0".                                                | -                                 |

|           |          | 1      | Can not be used.                                                          |                                   |

| в         | -        | 0      | It should be fixed to "0".                                                | -                                 |

|           |          | 1      | Can not be used.                                                          |                                   |

| С         | -        | 0      | It should be fixed to "0".<br>Can not be used.                            | -                                 |

|           |          | 0      | It should be fixed to "0".                                                |                                   |

| D         | -        | 1      | Can not be used.                                                          | -                                 |

| E         | _        | 0      | It should be fixed to "0".                                                |                                   |

| C         |          | 1      | Can not be used.                                                          |                                   |

| F         | _        | 0      | It should be fixed to "0".                                                | -                                 |

|           |          | 1      | Can not be used.                                                          |                                   |

Notes 1 : This register is consisted of 2 pages (address community) of the register for page A, and the register for page B. Writing control to each page is performed by register is consisted of 2 pages (address community) of the register for page A, and the register for page D. while go the object of page D. while control to by register of page D. while register for page A, and the register for page D. while control to by register of page D. While register for page A, and the register for page D. while register for page A.

2 : Set up the horizontal and vertical display start location so that display range may not exceed it. Set the character code "1FF16" (blank without background) for the display RAM of the part which the display range exceeds.

| DA | Pogiator |        | Contents                                                                                                                                                                                                 |                                                                                                                            |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|    | Register | Status | Function                                                                                                                                                                                                 | Remarks                                                                                                                    |

| 0  | MODE0    | 0      | MODE1         MODE0         Display mode           0         0         Priority is given to Page A                                                                                                       |                                                                                                                            |

| 1  | MODE1    | ①<br>1 | 01Priority is given to Page B10260 K colors display11The average of Page A and Page B                                                                                                                    |                                                                                                                            |

| 2  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| 3  | POLH     | 0      | HOR pin is negative polarity HOR pin is positive polarity                                                                                                                                                | Polarity of HOR pin                                                                                                        |

|    |          |        | VERT pin is negative polarity                                                                                                                                                                            |                                                                                                                            |

| 4  | POLV     | 0      | VERT pin is positive polarity                                                                                                                                                                            | Polarity of VERT pin                                                                                                       |

|    |          | (0)    | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

| 5  | -        | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

|    |          | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

| 6  | _        | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| 7  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

| ,  |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| 8  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| 9  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| А  | TEST     | 0      | Set "0" to this bit.                                                                                                                                                                                     | Test bit                                                                                                                   |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| В  | SBLANK0  | 0      | It synchronizes with a display CK rising and is port output (at the time of digital output setup).<br>It synchronizes with a display CK falling and is port output (at the time of analog output setup). | BLNK signal output timing control (BLNK<br>signal). Effective at the time of SBLANK1,<br>2 = 1, and 1 (BLNK output) setup. |

|    |          | 0      | SBLANK1         SBLANK2         P0/BLNK pin output           0         0         Port P0 output                                                                                                          | P0/BLNK pin output control.                                                                                                |

| С  | SBLANK1  | 1      | 0         1         Can not be used           1         0         Can not be used           1         1         BLNK output                                                                              | SBLANK2 : address 000716                                                                                                   |

| D  | PTC13    | 0      | Port P1 to P3 output (at the time of analog RGB output setup "L" fixation)                                                                                                                               | P1 to P3 output control                                                                                                    |

|    |          | 1      | R0 to R2 output (at the time of digital RGB output setup "H" fixation)                                                                                                                                   |                                                                                                                            |

| E  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| F  | _        | 0      | Set "0" to this bit.                                                                                                                                                                                     |                                                                                                                            |

|    |          | 1      | Can not be used.                                                                                                                                                                                         |                                                                                                                            |

| DA       | Register |        | Contents             | Remarks |

|----------|----------|--------|----------------------|---------|

|          |          | Status | Function             | Remarks |

| 0        | -        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 1        | 1 –      | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 2        | -        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 3        | -        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 4        | _        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 5        | -        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 6        | -        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 7        | _        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| 8        | _        | 0      | Set "0" to this bit. |         |

| _        |          | 1      | Can not be used.     |         |

| 9        | _        | 0      | Set "0" to this bit. |         |

| 0        |          | 1      | Can not be used.     |         |

| А        | _        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| В        | _        | 0      | Set "0" to this bit. |         |

| 5        |          | 1      | Can not be used.     |         |

| С        | _        | 0      | Set "0" to this bit. |         |

| <u> </u> |          | 1      | Can not be used.     |         |

| D        | _        | 0      | Set "0" to this bit. |         |

|          |          | 1      | Can not be used.     |         |

| E        | _        | 0      | Set "0" to this bit. |         |

| -        |          | 1      | Can not be used.     |         |

| F        | _        | 0      | Set "0" to this bit. |         |

| г        |          | 1      | Can not be used.     |         |

| DA | Register |        | Contents                                                                                                                                     | Remarks                                          |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|    | Register | Status | Function                                                                                                                                     | Remarks                                          |

| 0  | _        | 0      | Set "0" to this bit.                                                                                                                         | -                                                |

|    |          | 1      | Can not be used.                                                                                                                             |                                                  |

| 1  | _        | 0      | Set "0" to this bit.                                                                                                                         | -                                                |

|    |          | 1      | Can not be used.                                                                                                                             |                                                  |

| 2  | _        | 0      | Set "0" to this bit.                                                                                                                         | _                                                |

| 2  |          | 1      | Can not be used.                                                                                                                             |                                                  |

| 2  |          | 0      | Set "0" to this bit.                                                                                                                         |                                                  |

| 3  |          | 1      | Can not be used.                                                                                                                             |                                                  |

|    |          | 0      | Set "0" to this bit.                                                                                                                         |                                                  |

| 4  |          | 1      | Can not be used.                                                                                                                             |                                                  |