# 256-Bit Nonvolatile CMOS Static RAM

RoHS Compliance

## **FEATURES**

- Single 5V Supply

- Fast RAM Access Times:

-200ns

-300ns

- Infinite EEPROM to RAM Recall

- CMOS and TTL Compatible I/O

- Power Up/Down Protection

- 100,000 Program/Erase Cycles (E<sup>2</sup>PROM)

- Low CMOS Power Consumption: -Active: 40mA Max. -Standby: 30µA Max.

- JEDEC Standard Pinouts:

–18-lead DIP

–16-lead SOIC

- 10 Year Data Retention

- Commercial, Industrial and Automotive Temperature Ranges

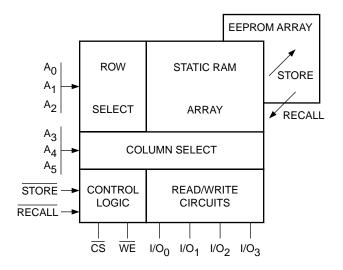

### DESCRIPTION

The CAT22C10NVRAM is a 256-bit nonvolatile memory organized as 64 words x 4 bits. The high speed Static RAM array is bit for bit backed up by a nonvolatile EEPROM array which allows for easy transfer of data from RAM array to EEPROM (STORE) and from EEPROM to RAM (RECALL). STORE operations are completed in 10ms max. and RECALL operations typically within 1.5 $\mu$ s. The CAT22C10 features unlimited RAM write operations either through external RAM

writes or internal recalls from EEPROM. Internal false store protection circuitry prohibits STORE operations when  $V_{CC}$  is less than 3.0V.

The CAT22C10 is manufactured using Catalyst's advanced CMOS floating gate technology. It is designed to endure 100,000 program/erase cycles (EEPROM) and has a data retention of 10 years. The device is available in JEDEC approved 18-lead plastic DIP and 16-lead SOIC packages.

### **PIN CONFIGURATION**

| DI                                                                             | DIP Package (L)                      |                                              |                                                                                                                               | SOIC Package (W)                                                                             |                      |                                                                                                                                                   |

|--------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NC   <br>A4   <br>A3   <br>A2   <br>A1   <br>A0   <br>CS   <br>V <sub>SS</sub> | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 18<br>17<br>16<br>15<br>14<br>13<br>12<br>11 | V <sub>cc</sub><br>NC<br>A <sub>5</sub><br>I/O <sub>3</sub><br>I/O <sub>2</sub><br>I/O <sub>1</sub><br>I/O <sub>0</sub><br>WE | A4 [ 1<br>A3 [ 2<br>A2 [ 3<br>A1 [ 4<br>A0 [ 5<br>CS [ 6<br>V <sub>SS</sub> [ 7<br>STORE [ 8 | 13<br>12<br>11<br>10 | 2 V <sub>cc</sub><br>2 A <sub>5</sub><br>2 I/O <sub>4</sub><br>2 I/O <sub>3</sub><br>2 I/O <sub>2</sub><br>2 I/O <sub>1</sub><br>2 WE<br>2 RECALL |

| STORE 🖂                                                                        | 9                                    | 10                                           | 🗀 RECALL                                                                                                                      |                                                                                              |                      |                                                                                                                                                   |

#### **PIN FUNCTIONS**

| Pin Name                           | Function     |

|------------------------------------|--------------|

| A <sub>0</sub> -A <sub>5</sub>     | Address      |

| I/O <sub>0</sub> –I/O <sub>3</sub> | Data In/Out  |

| WE                                 | Write Enable |

| CS                                 | Chip Select  |

| RECALL                             | Recall       |

| STORE                              | Store        |

| V <sub>CC</sub>                    | +5V          |

| V <sub>SS</sub>                    | Ground       |

| NC                                 | No Connect   |

© 2009 SCILLC. All rights reserved. Characteristics subject to change without notice.

## **BLOCK DIAGRAM**

#### MODE SELECTION<sup>(1)(2)(3)</sup>

|              | Input |    |        |       |                      |

|--------------|-------|----|--------|-------|----------------------|

| Mode         | CS    | WE | RECALL | STORE | I/O                  |

| Standby      | Н     | Х  | Н      | Н     | Output High-Z        |

| RAM Read     | L     | Н  | Н      | Н     | Output Data          |

| RAM Write    | L     | L  | Н      | Н     | Input Data           |

| (EEPROM→RAM) | Х     | Н  | L      | Н     | Output High-Z RECALL |

| (EEPROM→RAM) | Н     | Х  | L      | Н     | Output High-Z RECALL |

| (RAM→EEPROM) | Х     | Н  | Н      | L     | Output High-Z STORE  |

| (RAM→EEPROM) | Н     | Х  | Н      | L     | Output High-Z STORE  |

#### **POWER-UP TIMING**<sup>(4)</sup>

| Symbol | Parameter                 | Min. | Max.  | Units |

|--------|---------------------------|------|-------|-------|

| VCCSR  | V <sub>CC</sub> Slew Rate | 0.5  | 0.005 | V/ms  |

Note:

(1) RECALL signal has priority over STORE signal when both are applied at the same time.

(2) STORE is inhibited when RECALL is active.

(3) The store operation is inhibited when V<sub>CC</sub> is below  $\approx$  3.0V. (4) This parameter is tested initially and after a design or process change that affects the parameter.

## **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias –55°C to +125°C                                            |

|-----------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                 |

| Voltage on Any Pin with<br>Respect to Ground <sup>(2)</sup> 2.0 to +VCC +2.0V     |

| $V_{CC}$ with Respect to Ground2.0V to +7.0V                                      |

| Package Power Dissipation<br>Capability (Ta = 25°C)1.0W                           |

| Lead Soldering Temperature (10 secs) 300°C                                        |

| Output Short Circuit Current <sup>(3)</sup> 100 mA<br>RELIABILITY CHARACTERISTICS |

|                                                                                   |

## \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

| Symbol                             | Parameter          | Min.    | Max. | Units       | Reference Test Method         |

|------------------------------------|--------------------|---------|------|-------------|-------------------------------|

| N <sub>END</sub> <sup>(1)</sup>    | Endurance          | 100,000 |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(1)</sup>     | Data Retention     | 10      |      | Years       | MIL-STD-883, Test Method 1008 |

| VZAP <sup>(1)</sup>                | ESD Susceptibility | 2000    |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> <sup>(1)(4)</sup> | Latch-Up           | 100     |      | mA          | JEDEC Standard 17             |

#### D.C. OPERATING CHARACTERISTICS

$V_{CC}$  = +5V ±10%, unless otherwise specified.

|                 |                                    |      | Limits |      |      |                                                               |

|-----------------|------------------------------------|------|--------|------|------|---------------------------------------------------------------|

| Symbol          | Parameter                          | Min. | Тур.   | Max. | Unit | Conditions                                                    |

| Icc             | Current Consumption<br>(Operating) |      |        | 40   | mA   | All Inputs = $5.5V$<br>T <sub>A</sub> = 0°C<br>All I/O's Open |

| I <sub>SB</sub> | Current Consumption (Standby)      |      |        | 30   | μA   | CS = V <sub>CC</sub><br>All I/O's Open                        |

| ILI             | Input Current                      |      |        | 10   | μA   | $0 \le V_{IN} \le 5.5 V$                                      |

| I <sub>LO</sub> | Output Leakage Current             |      |        | 10   | μA   | $0 \leq V_{OUT} \leq 5.5 V$                                   |

| VIH             | High Level Input Voltage           | 2    |        | Vcc  | V    |                                                               |

| VIL             | Low Level Input Voltage            | 0    |        | 0.8  | V    |                                                               |

| V <sub>OH</sub> | High Level Output Voltage          | 2.4  |        |      | V    | I <sub>OH</sub> = -2mA                                        |

| V <sub>OL</sub> | Low Level Output Voltage           |      |        | 0.4  | V    | I <sub>OL</sub> = 4.2mA                                       |

| V <sub>DH</sub> | RAM Data Holding Voltage           | 1.5  |        | 5.5  | V    | V <sub>CC</sub>                                               |

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                         | Parameter                | Max. | Unit | Conditions     |

|--------------------------------|--------------------------|------|------|----------------|

| CI/O <sup>(1)</sup>            | Input/Output Capacitance | 10   | pF   | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(1)</sup> | Input Capacitance        | 6    | pF   | $V_{IN} = 0V$  |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> +2.0V for periods of less than 20 ns.

(3) Output shorted for no more than one second. No more than one output shorted at a time.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to  $V_{CC}$  +1V.

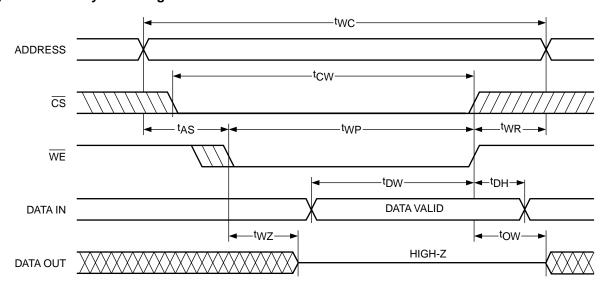

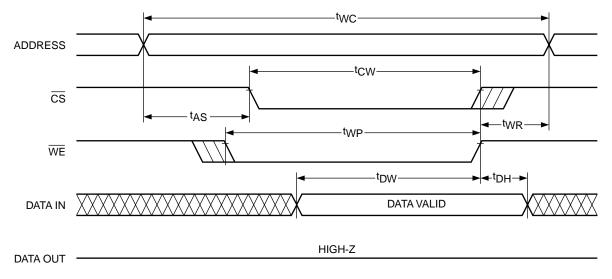

## A.C. CHARACTERISTICS, Write Cycle

$V_{CC}$  = +5V ±10%, unless otherwise specified.

|                                |                      | 22C1 | 22C10-20 |      | 22C10-30 |      |                        |

|--------------------------------|----------------------|------|----------|------|----------|------|------------------------|

| Symbol                         | Parameter            | Min. | Max.     | Min. | Max.     | Unit | Conditions             |

| t <sub>WC</sub>                | Write Cycle Time     | 200  |          | 300  |          | ns   |                        |

| t <sub>CW</sub>                | CS Write Pulse Width | 150  |          | 150  |          | ns   |                        |

| t <sub>AS</sub>                | Address Setup Time   | 50   |          | 50   |          | ns   | C <sub>L</sub> = 100pF |

| t <sub>WP</sub>                | Write Pulse Width    | 150  |          | 150  |          | ns   | +1TTL gate             |

| t <sub>WR</sub>                | Write Recovery Time  | 25   |          | 25   |          | ns   | V <sub>OH</sub> = 2.2V |

| t <sub>DW</sub>                | Data Valid Time      | 100  |          | 100  |          | ns   | $V_{OL} = 0.65V$       |

| t <sub>DH</sub>                | Data Hold Time       | 0    |          | 0    |          | ns   | $V_{IH} = 2.2V$        |

| t <sub>WZ</sub> <sup>(1)</sup> | Output Disable Time  |      | 100      |      | 100      | ns   | $V_{IL} = 0.65V$       |

| tow                            | Output Enable Time   | 0    |          | 0    |          | ns   |                        |

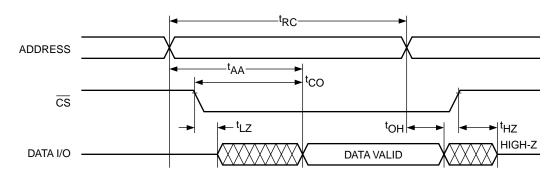

### A.C. CHARACTERISTICS, Read Cycle

$V_{CC}$  = +5V ±10%, unless otherwise specified.

|                                |                                     | 22C1 | 22C10-20 |      | 22C10-30 |      |                        |

|--------------------------------|-------------------------------------|------|----------|------|----------|------|------------------------|

| Symbol                         | Parameter                           | Min. | Max.     | Min. | Max.     | Unit | Conditions             |

| t <sub>RC</sub>                | Read Cycle Time                     | 200  |          | 300  |          | ns   | $C_L = 100 pF$         |

| t <sub>AA</sub>                | Address Access Time                 |      | 200      |      | 300      | ns   | +1TTL gate             |

| tco                            | CS Access Time                      |      | 200      |      | 300      | ns   | V <sub>OH</sub> = 2.2V |

| tон                            | Output Data Hold Time               | 0    |          | 0    |          | ns   | $V_{OL} = 0.65V$       |

| t <sub>LZ</sub> <sup>(1)</sup> | CS Enable Time                      | 0    |          | 0    |          | ns   | V <sub>IH</sub> = 2.2V |

| t <sub>HZ</sub> <sup>(1)</sup> | $\overline{\text{CS}}$ Disable Time |      | 100      |      | 100      | ns   | $V_{IL} = 0.65V$       |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

## A.C. CHARACTERISTICS, Store Cycle

$V_{CC}$  = +5V ±10%, unless otherwise specified.

|                                 |                    | Lim  | Limits |       |                                    |

|---------------------------------|--------------------|------|--------|-------|------------------------------------|

| Symbol                          | Parameter          | Min. | Max.   | Units | Conditions                         |

| tstc                            | Store Time         |      | 10     | ms    |                                    |

| t <sub>STP</sub>                | Store Pulse Width  | 200  |        | ns    | C <sub>L</sub> = 100pF + 1TTL gate |

| t <sub>STZ</sub> <sup>(1)</sup> | Store Disable Time |      | 100    | ns    | $V_{OH} = 2.2V, V_{OL} = 0.65V$    |

| tost <sup>(1)</sup>             | Store Enable Time  | 0    |        | ns    | $V_{IH} = 2.2V, V_{IL} = 0.65V$    |

## A.C. CHARACTERISTICS, Recall Cycle

$V_{CC}$  = +5V ±10%, unless otherwise specified.

|                  |                         | Limits |      |       |                                 |

|------------------|-------------------------|--------|------|-------|---------------------------------|

| Symbol           | Parameter               | Min.   | Max. | Units | Conditions                      |

| t <sub>RCC</sub> | Recall Cycle Time       | 1.4    |      | μs    |                                 |

| t <sub>RCP</sub> | Recall Pulse Width      | 300    |      | ns    | $C_L = 100 pF + 1TTL gate$      |

| t <sub>RCZ</sub> | Recall Disable Time     |        | 100  | ns    | $V_{OH} = 2.2V, V_{OL} = 0.65V$ |

| torc             | Recall Enable Time      | 0      |      | ns    | $V_{IH} = 2.2V, V_{IL} = 0.65V$ |

| t <sub>ARC</sub> | Recall Data Access Time |        | 1.1  | μs    |                                 |

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

## **DEVICE OPERATION**

The configuration of the CAT22C10 allows a common address bus to be directly connected to the address inputs. Additionally, the Input/Output (I/O) pins can be directly connected to a common I/O bus if the bus has less than 1 TTL load and 100pF capacitance. If not, the I/O path should be buffered.

When the chip select ( $\overline{CS}$ ) pin goes low, the device is activated. When CS is forced high, the device goes into the standby mode and consumes very little current. With the nonvolatile functions inhibited, the device operates like a Static RAM. The Write Enable ( $\overline{WE}$ ) pin selects a write operation when  $\overline{WE}$  is low and a read operation when  $\overline{WE}$  is high. In either of these modes, an array byte (4 bits) can be addressed uniquely by using the address lines (A<sub>0</sub>–A<sub>5</sub>), and that byte will be read or written to through the Input/Output pins (I/O<sub>0</sub>–I/O<sub>3</sub>).

The nonvolatile functions are inhibited by holding the STORE input and the RECALL input high. When the RECALL input is taken low, it initiates a recall operation which transfers the contents of the entire EEPROM

array into the Static RAM. When the **STORE** input is taken low, it initiates a store operation which transfers the entire Static RAM array contents into the EEPROM array.

#### Standby Mode

The chip select ( $\overline{CS}$ ) input controls all of the functions of the CAT22C10. When a high level is supplied to the  $\overline{CS}$  pin, the device goes into the standby mode where the outputs are put into a high impendance state and the power consumption is drastically reduced. With I<sub>SB</sub> less than 100µA in standby mode, the designer has the flexibility to use this part in battery operated systems.

#### Read

When the chip is enabled ( $\overline{CS}$  = low), the nonvolatile functions are inhibited ( $\overline{STORE}$  = high and  $\overline{RECALL}$  = high). With the Write Enable ( $\overline{WE}$ ) pin held high, the data in the Static RAM array may be accessed by selecting an address with input pins A<sub>0</sub>–A<sub>5</sub>. This will occur when the outputs are connected to a bus which is loaded by no more than 100pF and 1 TTL gate. If the loading is greater than this, some additional buffering circuitry is recommended.

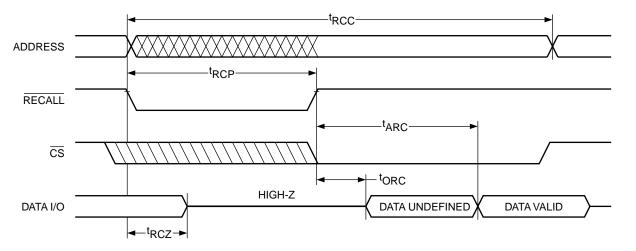

#### Figure 1. Read Cycle Timing

#### Write

With the chip enabled and the nonvolatile functions inhibited, the Write Enable ( $\overline{WE}$ ) pin will select the write mode when driven to a low level. In this mode, the address must be supplied for the byte being written. After the set-up time ( $t_{AS}$ ), the input data must be supplied to pins  $I/O_0-I/O_3$ . When these conditions, in-

cluding the write pulse width time ( $t_{WP}$ ) are met, the data will be written to the specified location in the Static RAM. A write function may also be initiated from the standby mode by driving  $\overline{WE}$  low, inhibiting the nonvolatile functions, supplying valid addresses, and then taking  $\overline{CS}$  low and supplying input data.

Figure 2. Write Cycle Timing

Figure 3. Early Write Cycle Timing

#### Recall

At anytime, except during a store operation, taking the RECALL pin low will initiate a recall operation. This is independent of the state of  $\overline{CS}$ ,  $\overline{WE}$ , or  $A_0$ – $A_5$ . After the RECALL pin has been held low for the duration of the Recall Pulse Width (t<sub>RCP</sub>), the recall will continue independent of any other inputs. During the recall, the entire contents of the EEPROM array is transferred to the Static RAM array. The first byte of data may be externally accessed after the recalled data access time from end of recall (t<sub>ARC</sub>) is met. After this, any other byte may be accessed by using the normal read mode.

If the  $\overrightarrow{RECALL}$  pin is held low for the entire Recall Cycle time (t<sub>RCC</sub>), the contents of the Static RAM may be immediately accessed by using the normal read mode. A recall operation can be performed an unlimited number of times without affecting the integrity of the data.

The outputs  $I/O_0-I/O_3$  will go into the high impedance state as long as the RECALL signal is held low.

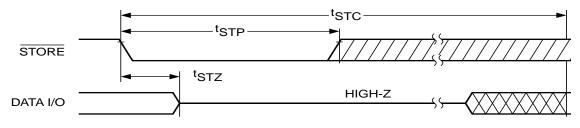

#### Store

At any time, except during a recall operation, taking the STORE pin low will initiate a store operation. This takes

place independent of the state of  $\overline{CS}$ ,  $\overline{WE}$  or  $A_0$ – $A_5$ . The STORE pin must be held low for the duration of the Store Pulse Width ( $t_{STP}$ ) to ensure that a store operation is initiated. Once initiated, the STORE pin becomes a "Don't Care", and the store operation will complete its transfer of the entire contents of the Static RAM array into the EEPROM array within the Store Cycle time ( $t_{STC}$ ). If a store operation is initiated during a write cycle, the contents of the addressed Static RAM byte and its corresponding byte in the EEPROM array will be unknown.

During the store operation, the outputs are in a high impedance state. A minimum of 100,000 store operations can be performed reliably and the data written into the EEPROM array has a minimum data retention time of 10 years.

# DATA PROTECTION DURING POWER-UP AND POWER-DOWN

The CAT22C10 has on-chip circuitry which will prevent a store operation from occurring when  $V_{CC}$  falls below 3.0V typ. This function eliminates the potential hazard of spurious signals initiating a store operation when the system power is below 3.0V typ.

#### Figure 4. Recall Cycle Timing

#### Figure 5. Store Cycle Timing

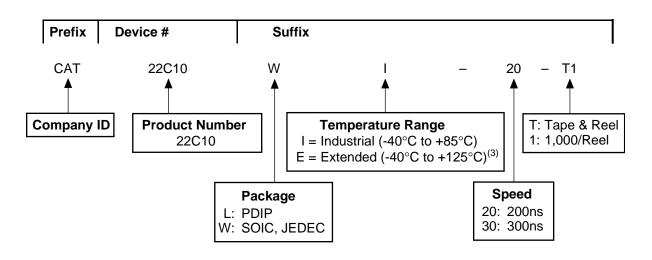

## EXAMPLE OF ORDERING INFORMATION<sup>(1)</sup>

## ORDERING INFORMATION

| Orderable Part Numbers (for Pb-Free Devices) |                  |  |

|----------------------------------------------|------------------|--|

| CAT22C10LE20                                 | CAT22C10WE-20-T1 |  |

| CAT22C10LE30                                 | CAT22C10WE-30-T1 |  |

| CAT22C10LI20                                 | CAT22C10WI-20-T1 |  |

| CAT22C10LI30                                 | CAT22C10WI-30-T1 |  |

Notes:

- (1) The device used in the above example is a CAT22C10WI-20-T1 (SOIC, Industrial Temperature, 200ns, Tape & Reel, 1,000/Reel).

- (2) For additional package option please contact your nearest Catalyst Semiconductor Sales office.

- (3) Extended Temperature available upon request.

#### **REVISION HISTORY**

| Date      | Revision | Description                                                                 |

|-----------|----------|-----------------------------------------------------------------------------|

| 16-Apr-04 | 0        | Add Lead free logo                                                          |

|           |          | Update Features                                                             |

|           |          | Update Pin Configuration                                                    |

|           |          | Update Ordering Information                                                 |

|           |          | Update Revision Number                                                      |

| 24-Jun-08 | Р        | Update Example of Ordering Information                                      |

| 17-Mar-09 | Q        | Change logo and fine print to ON Semiconductor                              |

| 31-Jul-09 | R        | Update Example of Ordering Information<br>Update Ordering Information table |

ON Semiconductor and

are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability a r i n q

a r i n g out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiltates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center: Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative