# **ASSP**

### **BIPOLAR**

# **Switching Regulator Controller**

# **MB3778**

#### **■ DESCRIPTION**

The MB3778 is a dual switching regulator control IC. It has a two-channel basic circuit that controls PWM system switching regulator power. Complete synchronization is achieved by using the same oscillator output wave. This IC can accept any two of the following types of output voltage: step-down, step-up, or voltage inversion (inverting voltage can be output to only one circuit). The MB3778's low power consumption makes it ideal for use in portable equipment.

#### **■ FEATURES**

- Wide input voltage range: 3.6 V to 18 V

- Low current consumption : 1.7 mA Typ operation, 10 μA Max stand-by

- Wide oscillation frequency range: 1 kHz to 500 kHz

- Built-in timer latch short-circuit protection circuit

- Built-in under-voltage lockout circuit

- Built-in 2.46 V reference voltage circuit : 1.23 V output can be obtained from R<sub>T</sub> terminal

- Variable dead-time provides control over total range

- Built-in stand-by function: power on/off function

- Two types of packages (SOP-16pin :1 type, SSOP-16pin :1 type)

#### APPLICATIONS

- LCD monitor/panel

- Surveillance camera etc.

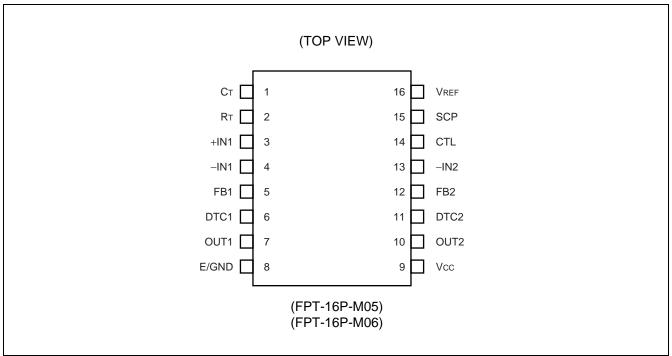

### ■ PIN ASSIGNMENT

### **■ PIN DESCRIPTION**

| No. | Pin   | Function                                                                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Ст    | Oscillator timing capacitor terminal (150 pF to 15,000 pF) .                                                                                                                                                                                                                                                                      |

| 2   | R⊤    | Oscillator timing resistor terminal (5.1 k $\Omega$ to 100 k $\Omega$ ) . V <sub>REF</sub> $\times$ 1/2 voltage is also available at this pin for error amplifier reference input.                                                                                                                                                |

| 3   | +IN1  | Error amplifier 1 non-inverted input terminal.                                                                                                                                                                                                                                                                                    |

| 4   | -IN1  | Error amplifier 1 inverted input terminal.                                                                                                                                                                                                                                                                                        |

| 5   | FB1   | Error amplifier 1 output terminal. A resistor and a capacitor are connected between this terminal and the –IN1 terminal to adjust gain and frequency.                                                                                                                                                                             |

| 6   | DTC1  | OUT1 dead-time control terminal.  Dead-time control is adjusted by an external resistive divider connected to the VREF pin.  A capacitor connected between this terminal and GND enables soft-start operation.                                                                                                                    |

| 7   | OUT1  | Open collector output terminal. Output transistor has common ground independent of signal ground. This output can source or sink up to 50 mA.                                                                                                                                                                                     |

| 8   | E/GND | Ground terminal.                                                                                                                                                                                                                                                                                                                  |

| 9   | Vcc   | Power supply terminal (3.6 V to 18 V)                                                                                                                                                                                                                                                                                             |

| 10  | OUT2  | Open collector output terminal. Output transistor has common ground independent of signal ground. This output can source or sink up to 50 mA.                                                                                                                                                                                     |

| 11  | DTC2  | Sets the dead-time of OUT2. The use of this terminal is the same as that of DTC1.                                                                                                                                                                                                                                                 |

| 12  | FB2   | Error amplifier 2 output terminal.  Sets the gain and adjusts the frequency when a resistor and a capacitor are connected between this terminal and the –IN2 terminal.  Voltage of VREF × 1/2 voltage is internally connected to the non-inverted input of error amplifier 2. Uses error amplifier 2 for positive voltage output. |

| 13  | -IN2  | Error amplifier 2 inverted input terminal.                                                                                                                                                                                                                                                                                        |

| 14  | CTL   | Power control terminal. The IC is set in the stand-by state when this terminal is set "Low." Current consumption is 10 μA or lower in the stand-by state. The input can be driven by TTL or CMOS.                                                                                                                                 |

| 15  | SCP   | The time constant setting capacitor connection terminal of the timer latch short-circuit protection circuit.  Connects a capacitor between this pin and GND.  For details, see "■ HOW TO SET TIME CONSTANT FOR TIMER LATCH SHORT-CIRCUIT PROTECTION CIRCUIT".                                                                     |

| 16  | VREF  | 2.46 V reference voltage output terminal which can be obtained up to 1 mA. This pin is used to set the reference input and idle period of the error amplifiers.                                                                                                                                                                   |

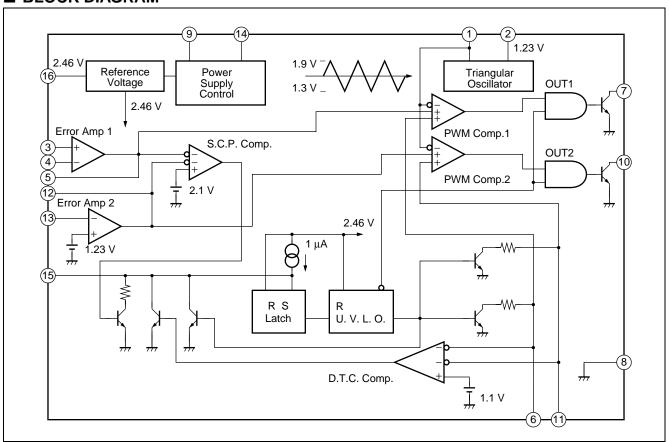

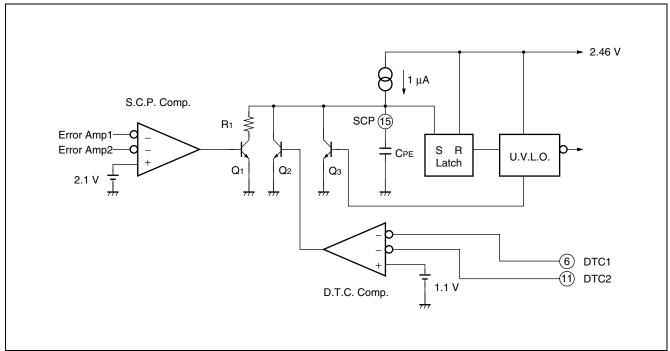

### **■ BLOCK DIAGRAM**

#### **■ OPERATION DESCRIPTION**

#### 1. Reference voltage circuit

The reference voltage circuit generates a temperature-compensated reference voltage ( $\pm$  2.46 V) from Vcc terminal (pin 9). The reference voltage is used as an operation power supply for internal circuit. The reference is obtained from the V<sub>REF</sub> terminal (pin 16).

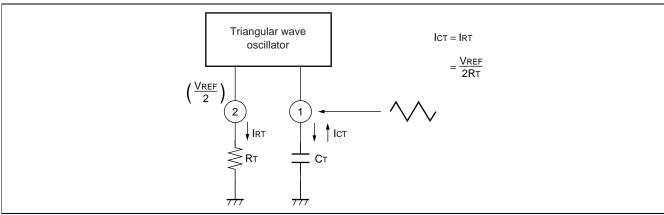

#### 2. Triangular wave oscillator

Triangular waveforms can be generated at any frequency by connecting a timing capacitor and resistor to the  $C_T$  terminal (pin 1) and to the  $R_T$  terminal (pin 2).

The amplitude of this waveform is from 1.3 V to 1.9 V. These waveforms are connected to the non-inverting inputs of the PWM comparator and can be output through the C<sub>T</sub> terminal (pin 1).

#### 3. Error amplifiers (Error Amp)

The error amplifier detects the output voltage of the switching regulator and outputs PWM control signals. The in-phase input voltage range is from 1.05 V to 1.45 V. The reference voltage obtained by dividing the reference voltage output (recommended value:  $V_{REF}/2$ ) or the  $R_T$  terminal (pin 2) voltage (1.23 V) is supplied to the non-inverting input. The  $V_{REF}/2$  voltage is internally connected to non-inverting input of the other error amplifier. Any loop gain can be chosen by connecting the feedback resistor and capacitor to the inverting input terminal from the output terminal of the error amplifier. Stable phase compensation is possible.

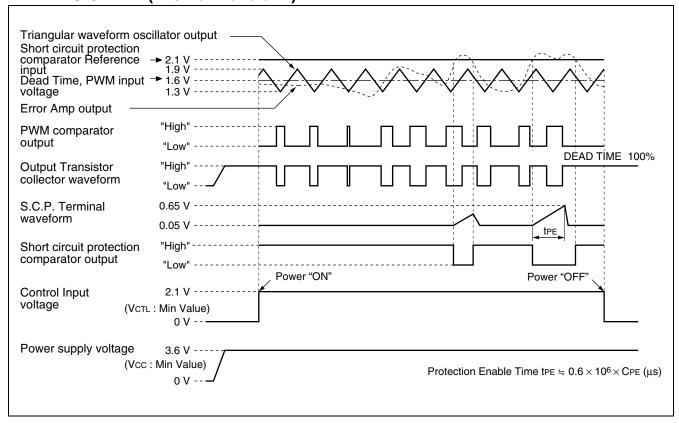

#### 4. Timer latch short circuit protection circuit

This circuit detects the output levels of each error amplifier. If the output level of one or both of the error amplifiers is 2.1 V or higher, the timer circuit begins charging the externally connected protection enable-capacitor. If the output level of the error amplifier does not drop below the normal voltage range before the capacitor voltage reaches the transistor base-emitter voltage,  $V_{BE}(\pm 0.65 \text{ V})$ , the latch circuit turns the output drive transistor off and sets the idle period to 100%.

#### 5. Under voltage lock-out circuit

The transition state at power-on or a momentary drops in supply voltage may cause the control IC to malfunction, which may adversely affect or even destroy the system. The under voltage lockout circuit monitors  $V_{CC}$  with reference to the internal reference voltage and resets the latch circuit to turn the output drive transistor off. The idle period is set to 100%. It also pulls the SCP terminal (pin 15) "Low".

#### 6. PWM comparator unit

Each PWM comparator has one inverting input and two non-inverting inputs. This voltage-to-pulse-width converter controls the turning on time of the output pulse according to the input voltage.

The PWM comparator turns the output drive transistor on while triangular waveforms from the oscillator are lower than the error amplifier output and the DTC terminal voltage.

#### 7. Output drive transistor

The output drive transistors have open collector outputs with common source supply and common grounds independent of Vcc and signal ground. The output drive transistors for switching can sink or source up to 50 mA.

#### 8. Power control unit

The CTL terminal (pin 14) controls power on/off modes(the power supply current in stand-by mode is 10  $\mu$ A or lower).

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol   | Condition          | Rat         | Unit  |       |

|-------------------------------|----------|--------------------|-------------|-------|-------|

| Farameter                     | Syllibol |                    | Min         | Max   | Oille |

| Power Supply Voltage          | Vcc      | _                  | _           | 20    | V     |

| Error Amp Input Voltage       | Vin      | _                  | -0.3        | +10   | V     |

| Control Input Voltage         | Vctl     | _                  | -0.3        | +20   | V     |

| Collector Output Voltage      | Vоит     | _                  | _           | 20    | V     |

| Collector Output Current      | Іоит     | _                  | _           | 75    | mA    |

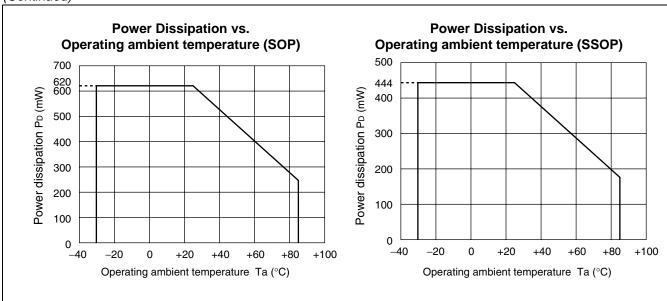

| Power Dissipation             | Po       | Ta ≤ +25 °C (SOP)  | _           | 620*1 | mW    |

| Power Dissipation             |          | Ta ≤ +25 °C (SSOP) | _           | 444*2 | mW    |

| Operating Ambient Temperature | Ta       | _                  | -30         | +85   | °C    |

| Storage Temperature           | Tstg     | _                  | <b>–</b> 55 | +125  | °C    |

<sup>\*1:</sup> The packages are mounted on the epoxy board (4 cm × 4 cm)

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                     | Symbol | Value |     |       | Unit |

|-------------------------------|--------|-------|-----|-------|------|

| Farameter                     |        | Min   | Тур | Max   | Onit |

| Power Supply Voltage          | Vcc    | 3.6   | 6.0 | 18    | V    |

| Error Amp Input Voltage       | Vin    | 1.05  | _   | 1.45  | V    |

| Control Input Voltage         | Vctl   | 0     | _   | 18    | V    |

| Collector Output Voltage      | Vouт   | _     | _   | 18    | V    |

| Collector Output Current      | Іоит   | 0.3   | _   | 50    | mA   |

| Timing Capacitor              | Ст     | 150   | _   | 15000 | pF   |

| Timing Resistor               | R⊤     | 5.1   | _   | 100   | kΩ   |

| Oscillator Frequency          | fosc   | 1     | _   | 500   | kHz  |

| Operating Ambient Temperature | Та     | -30   | +25 | +85   | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

<sup>\*2:</sup> The packages are mounted on the epoxy board (10 cm  $\times$  10 cm)

### **■ ELECTRICAL CHARACTERISTICS**

$(Ta = +25 \, {}^{\circ}C, \, Vcc = 6 \, V)$

| Donomoton                         | Council of        | Condition                                        | Value |      |      | T    |

|-----------------------------------|-------------------|--------------------------------------------------|-------|------|------|------|

| Parameter                         | Symbol Condition  |                                                  | Min   | Тур  | Max  | Unit |

| Reference Block                   | •                 |                                                  |       | •    | •    | •    |

| Output Voltage                    | VREF              | $I_{OR} = -1 \text{ mA}$                         | 2.41  | 2.46 | 2.51 | V    |

| Output Temp. Stability            | VRTC              | Ta = -30 °C to +85 °C                            | -2    | ±0.2 | +2   | %    |

| Input Stability                   | Line              | Vcc = 3.6 V to 18 V                              | _     | 2    | 10   | mV   |

| Load Stability                    | Load              | $I_{OR} = -0.1 \text{ mA to } -1 \text{ mA}$     | _     | 1    | 7.5  | mV   |

| Short Circuit Output Current      | los               | V <sub>REF</sub> = 2 V                           | -30   | -10  | -3   | mA   |

| Under Voltage Lockout Protection  | n Block           |                                                  |       |      |      |      |

| Threshold Voltage                 | VtH               | $I_{OR} = -0.1 \text{ mA}$                       | _     | 2.72 |      | V    |

| Threshold Voltage                 | VtL               | $I_{OR} = -0.1 \text{ mA}$                       | _     | 2.60 | _    | V    |

| Hysteresis Width                  | V <sub>H</sub> ys | $I_{OR} = -0.1 \text{ mA}$                       | 80    | 120  | _    | mV   |

| Reset Voltage (Vcc)               | VR                | _                                                | 1.5   | 1.9  |      | V    |

| Protection Circuit Block (S.C.P.) | •                 |                                                  |       |      |      |      |

| Input Threshold Voltage           | V <sub>tPC</sub>  | _                                                | 0.60  | 0.65 | 0.70 | V    |

| Input Stand by Voltage            | VstB              | No pull up                                       | _     | 50   | 100  | mV   |

| Input Latch Voltage               | Vin               | No pull up                                       | _     | 50   | 100  | mV   |

| Input Source Current              | lbpc              | _                                                | -1.4  | -1.0 | -0.6 | μΑ   |

| Comparator Threshold Voltage      | VtC               | Pin 5, Pin 12                                    | _     | 2.1  |      | V    |

| Triangular Waveform Oscillator    | Block             |                                                  |       |      |      | 1    |

| Oscillator Frequency              | fosc              | $C_T = 330 \text{ pF}, R_T = 15 \text{ k}\Omega$ | 160   | 200  | 240  | kHz  |

| Frequency Deviation               | f <sub>dev</sub>  | $C_T = 330 \text{ pF}, R_T = 15 \text{ k}\Omega$ | _     | ±5   |      | %    |

| Frequency Stability (Vcc)         | fd∨               | Vcc = 3.6 V to 18 V                              |       | ±1   |      | %    |

| Frequency Stability (Ta)          | <b>f</b> dT       | Ta = -30 °C to +85 °C                            | -4    | _    | +4   | %    |

| Dead-Time Control Block (D.T.C    | )                 | -                                                |       | •    | •    | •    |

| Input Bias Current                | <b>I</b> bdt      | _                                                | _     | 0.2  | 1    | μΑ   |

| Latch Mode Sink Current           | l <sub>dt</sub>   | $V_{dt} = 2.5 \text{ V}$                         | 150   | 500  | _    | μΑ   |

| Latch Input Voltage               | V <sub>dt</sub>   | $I_{dt}=100~\mu A$                               | _     | _    | 0.3  | V    |

### (Continued)

$(Ta = +25 \, {}^{\circ}C, \, Vcc = 6 \, V)$

| Devementer                         | Symbol Condition  | Condition                                | Value                  |      |      | I I m i 4 |

|------------------------------------|-------------------|------------------------------------------|------------------------|------|------|-----------|

| Parameter                          |                   | Condition                                | Min                    | Тур  | Max  | Unit      |

| Error Amp Block                    | •                 |                                          | •                      |      |      | •         |

| Input Offset Voltage               | Vio               | Vo = 1.6 V                               | -6                     |      | +6   | mV        |

| Input Offset Current               | lio               | Vo = 1.6 V                               | -100                   | _    | +100 | nA        |

| Input Bias Current                 | Iв                | Vo = 1.6 V                               | -500                   | -100 |      | nA        |

| Common Mode Input Voltage<br>Range | VICR              | Vcc = 3.6 V to 18 V                      | 1.05                   |      | 1.45 | V         |

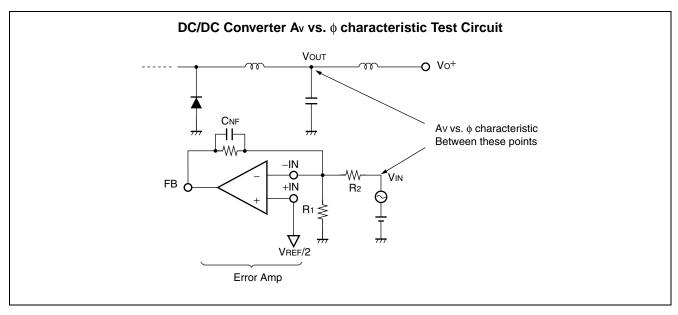

| Voltage Gain                       | Av                | $R_{NF} = 200 \text{ k}\Omega$           | 70                     | 80   |      | dB        |

| Frequency Band Width               | BW                | $A_V = 0 dB$                             | _                      | 1.0  | _    | MHz       |

| Common Mode Rejection Ratio        | CMRR              | _                                        | 60                     | 80   |      | dB        |

| Max Output Voltage Width           | V <sub>OM+</sub>  | _                                        | V <sub>REF</sub> - 0.3 |      |      | V         |

|                                    | V <sub>ОМ</sub> – | _                                        | _                      | 0.7  | 0.9  | V         |

| Output Sink Current                | Іом+              | Vo = 1.6                                 | _                      | 1.0  | _    | mA        |

| Output Source Current              | Іом-              | Vo = 1.6                                 |                        | -60  |      | μΑ        |

| PWM Comparator Block               | •                 |                                          |                        |      |      | '         |

| Input Threshold Voltage            | V <sub>t100</sub> | Duty Cycle = 100%                        |                        | 1.9  | 2.25 | V         |

| (fosc = 10 kHz)                    | V <sub>t0</sub>   | Duty Cycle = 0%                          | 1.05                   | 1.3  |      | V         |

| On duty Cycle                      | Dtr               | V <sub>dt</sub> = V <sub>REF</sub> /1.45 | 55                     | 65   | 75   | %         |

| Input Sink Current                 | I <sub>IN+</sub>  | Pin 5, Pin 12 = 1.6 V                    |                        | 1.0  |      | mA        |

| Input Source Current               | I <sub>IN</sub> - | Pin 5, Pin 12 = 1.6 V                    |                        | -60  |      | μΑ        |

| Control Block                      |                   | •                                        | •                      |      |      |           |

| Input Off Condition                | Voff              | _                                        |                        | _    | 0.7  | V         |

| Input On Condition                 | Von               | _                                        | 2.1                    | _    | _    | V         |

| Control Terminal Current           | Ість              | Vctl = 10 V                              |                        | 200  | 400  | μΑ        |

| Output Block                       |                   | •                                        |                        |      |      |           |

| Output Leak Current                | Leak              | Vo = 18 V                                |                        | _    | 10   | μΑ        |

| Output Saturation Voltage          | Vsat              | lo = 50 mA                               |                        | 1.1  | 1.4  | V         |

| All Device Block                   | •                 |                                          | •                      |      |      | •         |

| Stand-by Current                   | Iccs              | Vctl = 0 V                               |                        |      | 10   | μΑ        |

| Average Supply Current             | Icca              | Vctl = Vcc, No Output Load               | _                      | 1.7  | 2.4  | mA        |

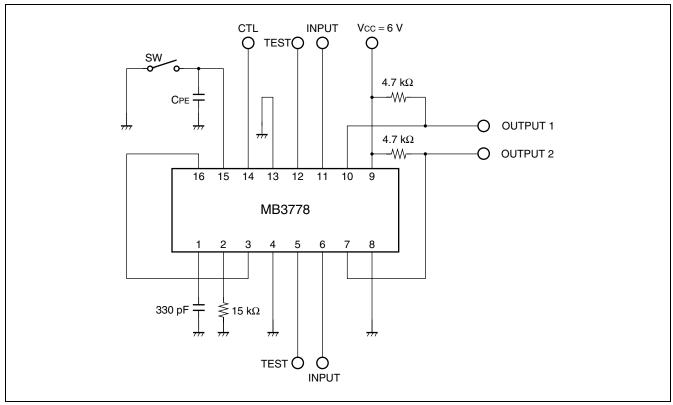

#### **■ TEST CIRCUIT**

### **■ TIMING CHART (Internal Waveform)**

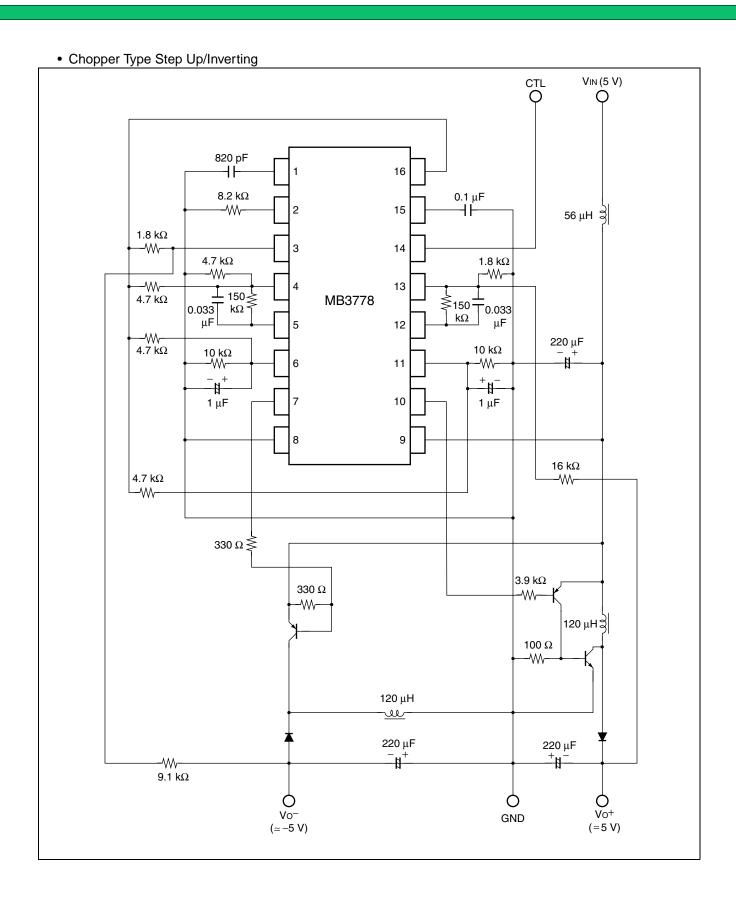

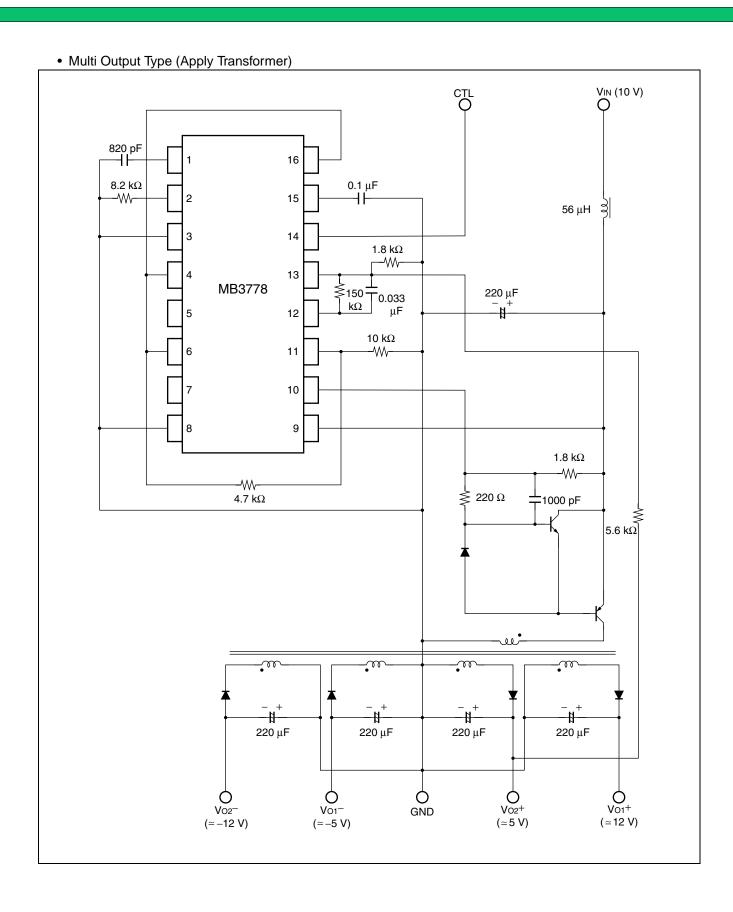

### **■ APPLICATION CIRCUIT**

• Chopper Type Step Down/inverting VIN (10 V) CTL Q 820 pF ΗĖ 16  $8.2~\text{k}\Omega$  $0.1 \, \mu F$ ------2 15 56 μH ਤੇ  $1.8~\text{k}\Omega$ -\\\ 3 14  $1.8~\mathrm{k}\Omega$  $4.7~\mathrm{k}\Omega$ -///----\/\/\-4.7 kΩ 13 150 0.033 kΩ 150 0.033 μF MB3778 5 12 220 μF - + 10 k $\Omega$ 6 11 -------<sub>|</sub>+ + + -10  $1\,\mu F$  $1\,\mu F$ 8 9  $5.6~\text{k}\Omega$  $2.4~\text{k}\Omega$ -\\\ <del>-</del>/W/-330 Ω ≶ 330  $\Omega$ 330  $\Omega$ 330  $\Omega$ 120 μΗ 120 μH ຊ  $9.1~k\Omega$ 220 μF 220 μF  $V_0^ (\simeq -5 \text{ V})$ Ó Vo+ GND (≃5 V)

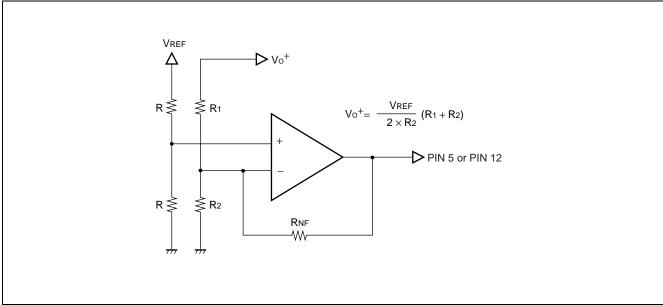

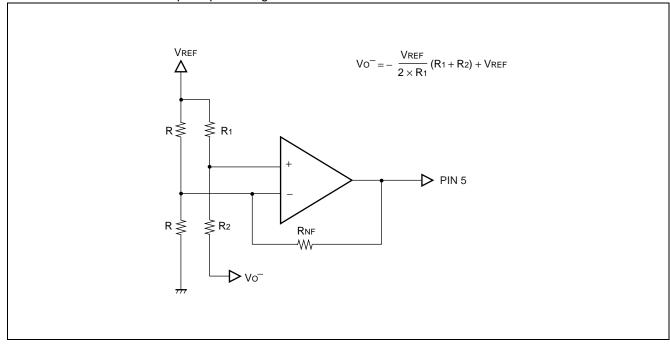

#### **■ HOW TO SET THE OUTPUT VOLTAGE**

The output voltage is set using the connections shown in "Connection of error Amp Output Voltage  $V_0 \ge 0$ " and "Connection of Error Amp Output Voltage  $V_0 < 0$ ".

The error amplifier power is supplied by the reference voltage circuit as is that of the other internal circuits. The common mode input voltage range is from 1.05 V to 1.45 V.

Set 1.23 V (VREF/2) as the reference input voltage that is connected to either inverting or non-inverting input terminals.

$\bullet$  Connection of Error Amp Output Voltage  $V_0 \, \geq \, 0$

#### • Connection of Error Amp Output Voltage Vo < 0

# ■ HOW TO SET TIME CONSTANT FOR TIMER LATCH SHORT-CIRCUIT PROTECTION CIRCUIT

Below Figure shows the configuration of the protection latch circuit.

Each error amplifier output is connected to the inverting inputs of the short-circuit protection comparator and is always compared with the reference voltage (2.1 V) connected to the non-inverting input.

When the load condition of the switching regulator is stable, the error amplifier has no output fluctuation. Thus, short-circuit protection control is also kept in balance, and the SCP terminal (pin 15) voltage is held at about 50 mV. If the load changes drastically due to a load short-circuit and if the inverting inputs of the short-circuit protection comparator go above 2.1 V, the short-circuit protection comparator output goes "Low" to turn off transistor Q<sub>1</sub>. The SCP terminal voltage is discharged, and then the short-circuit protection comparator charges the protection enable capacitor CPE according to the following formula:

$$V_{PE} = 50 \ mV + t_{PE} \times 10^{-6} \ / \ C_{PE} \\ 0.65 = 50 \ mV + t_{PE} \times 10^{-6} \ / \ C_{PE} \\ C_{PE} = t_{PE} \ / \ 0.6 \ (\mu F)$$

When the protection enable capacitor is charged to about 0.65 V, the protection latch is set to enable the under voltage lockout circuit and the output drive transistor is turned off. The idle period is also set to 100% at the same time.

Once the under voltage lockout circuit is enabled, the protection enable is released; however, the protection latch is not reset if the power is not turned off.

The inverting inputs (pin 6 or 11) of the D.T.C. comparator are compared to the reference voltage (about 1.1 V) connected to the non-inverting input.

To prevent malfunction of the short-circuit protection-circuit when the soft-start operation is done by using the DTC terminal (pin 6 or 11), the D.T.C. comparator outputs a "High" level while the DTC terminal (pin 6 or 11) goes up to about 1.1 V, and then closes the SCP terminal (pin 15) by turning transistor  $Q_2$  on.

#### Protection Latch Circuit

#### **■ SETTING THE IDLE PERIOD**

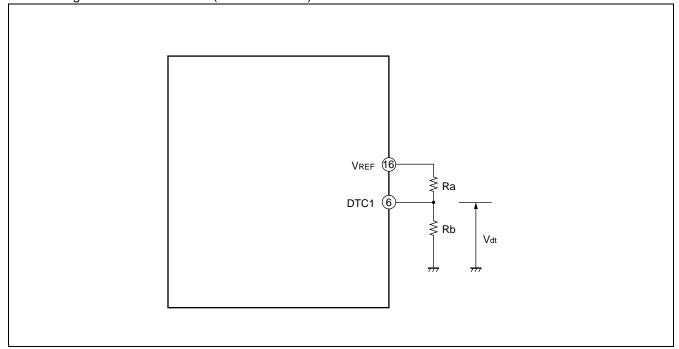

When voltage step-up, fly-back step-up or inverted output are set, the voltage at the FB terminal may go higher than the triangular wave voltage due to load fluctuation, etc. In this case the output transistor will be in full-on state(ON duty 100%). This can be prevented by setting the maximum duty for the output transistor. This is done by setting the DTC1 terminal (pin 6) voltage using resistance division of the VREF voltage as illustrated below.

When the DTC1 terminal voltage is higher than the triangular waveform voltage, the output transistor is turned on. If the triangular waveform amplitude specified by the maximum duty calculation formula is 0.6 V, and the lower voltage limit of the triangular waveform is 1.3 V, the formula would be as follows (other channels are similar):

Duty (ON) max (%)

$$\Rightarrow$$

(V<sub>dt</sub> - 1.3 V) / 0.6 V × 100, V<sub>dt</sub> (V) = Rb / (Ra + Rb) × V<sub>REF</sub>

Also, if no output duty setting is required, the voltage should be set greater than the upper limit voltage of the triangular waveform, which is 1.9 V.

• Setting the idle time at DTC1 (DTC2 is similar)

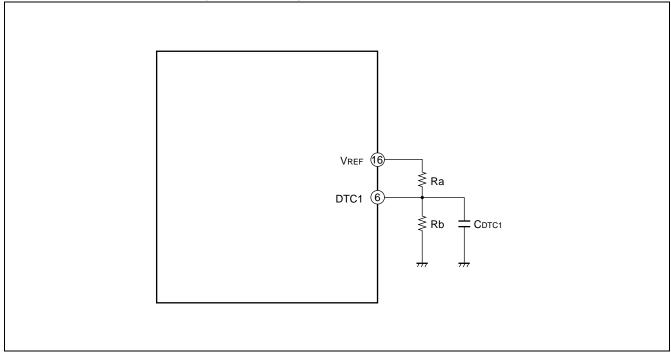

#### ■ SETTING THE SOFT START TIME

When power is switched on, the current begins charging the capacitor (CDTC1) connected the DTC1 terminal (pin 6). The soft start process operates by comparing the soft start setting voltage, which is proportional to the DTC1 terminal voltage, with the triangular waveform, and varying the ON-duty of the OUT terminal (pin 7).

The soft start time until the ON duty reaches 50% is determined by the following equation:

Soft start time (time until output ON duty = 50%).

$$ts(s) = -C_{DTC1} \times Ra \times Rb / (Ra + Rb) \times ln(1 - 1.6 (Ra + Rb)) / (2.46 Rb)$$

For example, if Ra = 4.7 k $\Omega$  and Rb = 10 k $\Omega$ , the result is:

ts (s)

$$\neq$$

0.01  $\times$  CDTC1 ( $\mu$ F)

• Soft Start on DCT1 terminal (DTC2 is similar)

#### ■ USING THE RT TERMINAL

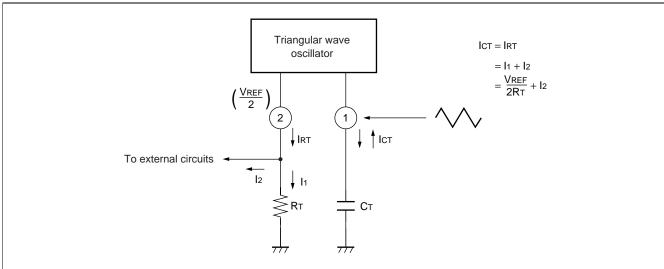

The triangular waves, as shown in Figure "No  $V_{REF}/2$  connection to external circuits from  $R_T$  terminal", act to set the oscillator frequency by charging and discharging the capacitor connected to the  $C_T$  terminal using the current value of the resistor connected to the  $R_T$  terminal.

In addition, when voltage level  $V_{REF}/2$  is output to external circuits from the  $R_T$  terminal (pin 2), care must be taken in making the external circuit connections to adjust for the fact that  $I_1$  is increased by the value of the current  $I_2$  to the external circuits in determining the oscillator frequency (see Figure " $V_{REF}/2$  connection to external circuits from  $R_T$  terminal").

#### • No VREF/2 connection to external circuits from R<sub>T</sub> terminal

#### • VREF/2 connection to external circuits from RT terminal

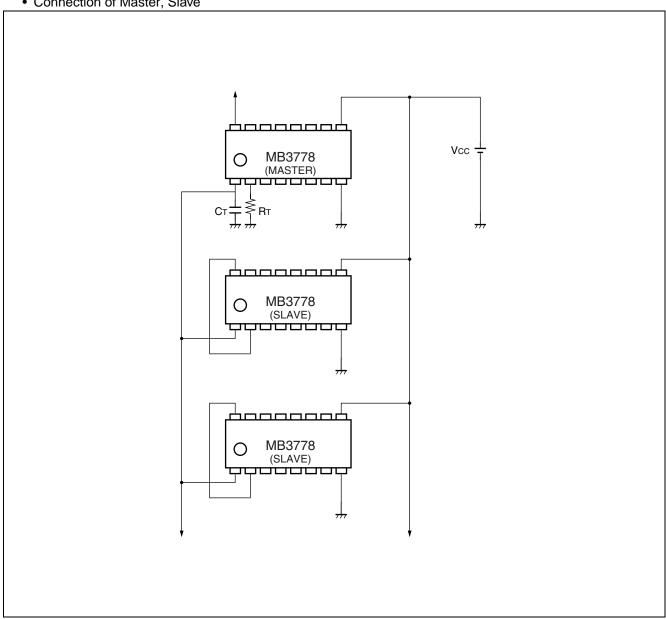

#### **■ SYNCHRONIZATION OF ICs**

A fixed condenser and resistor are inserted in the C<sub>T</sub> and R<sub>T</sub> terminals of IC which becomes a master when synchronizing by using plurality of MB3778. As a result, the slave ICs oscillate automatically. The R<sup>⊤</sup> terminals (pin 2) of the slave ICs are connected to the VREF terminal (pin 16) to disable the charge/discharge circuit for triangular wave oscillation. The C<sub>T</sub> terminals of the master and slave ICs are connected together.

· Connection of Master, Slave

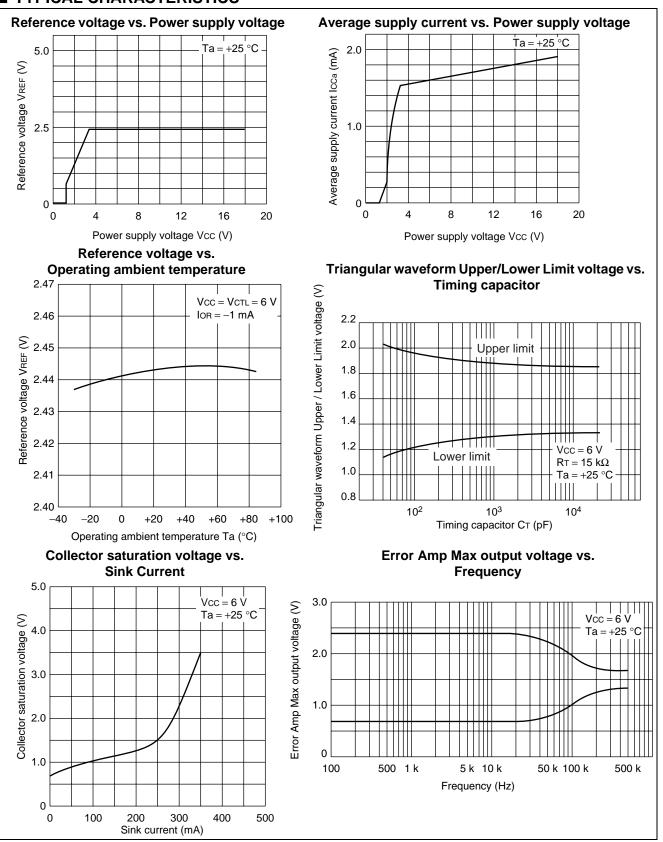

#### **■ TYPICAL CHARACTERISTICS**

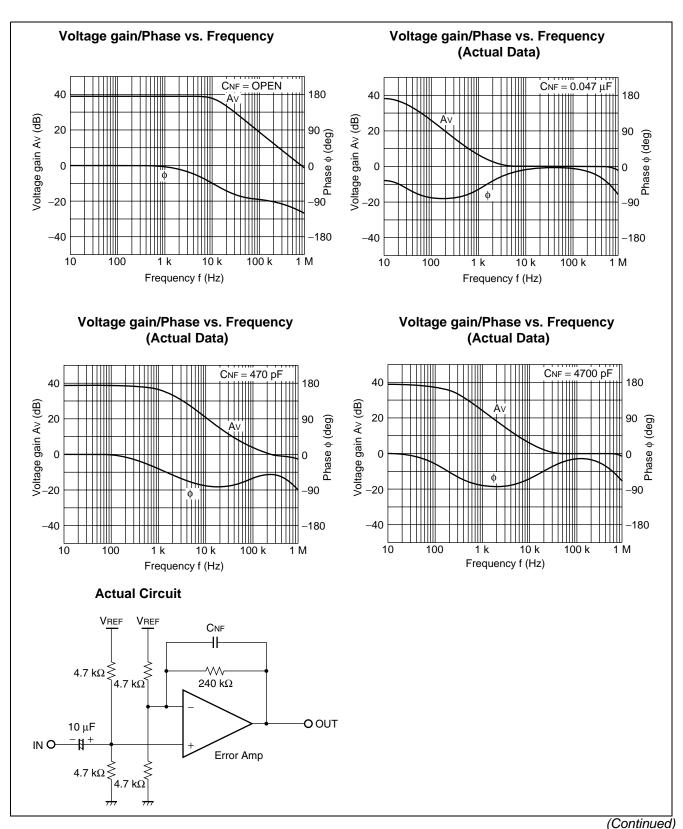

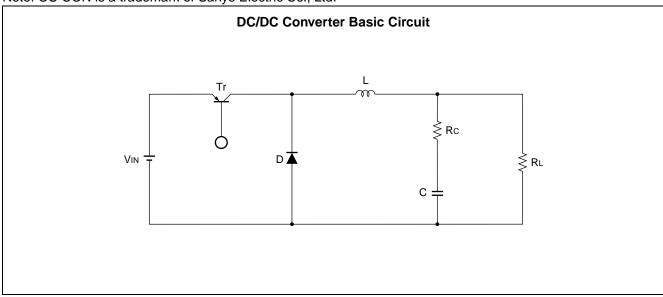

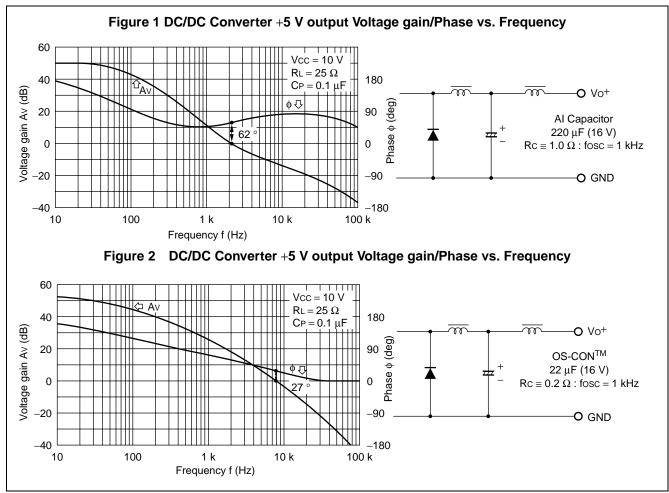

#### ■ EQUIVALENT SERIES RESISTOR AND STABILITY OF SMOOTHING CAPACITOR

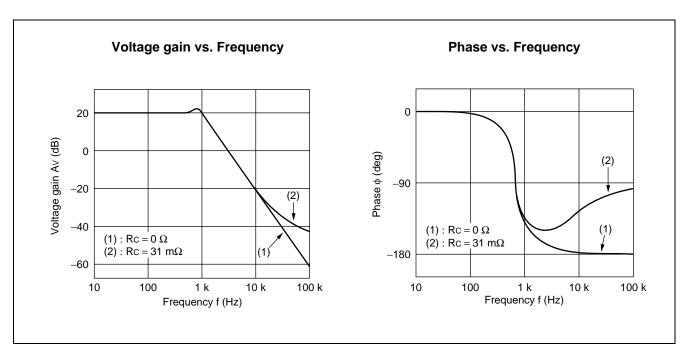

The equivalent series resistor (ESR) of the smoothing capacitor in the DC/DC converter greatly affects the loop phase characteristic.

The stability of the system is improved so that the phase characteristic may advance the phase to the ideal capacitor by ESR in the high frequency region (see "Voltage gain vs. Frequency" and "Phase vs. Frequency"). A smoothing capacitor with a low ESR reduces system stability. Use care when using low ESR electrolytic capacitors (OS-CON<sup>TM</sup>) and tantalum capacitors.

Note: OS-CON is a trademark of Sanyo Electric Co., Ltd.

#### · Reference data

If an aluminum electrolytic smoothing capacitor (RC  $\cong$  1.0  $\Omega$ ) is replaced with a low ESR electrolytic capacitor (OS-CON<sup>TM</sup> : RC  $\cong$  0.2  $\Omega$ ), the phase margin is reduced by half(see Fig.1 and Fig.2).

#### **■ NOTES ON USE**

- Take account of common impedance when designing the earth line on a printed wiring board.

- · Take measures against static electricity.

- For semiconductors, use antistatic or conductive containers.

- When storing or carrying a printed circuit board after chip mounting, put it in a conductive bag or container.

- The work table, tools and measuring instruments must be grounded.

- The worker must put on a grounding device containing 250 k $\Omega$  to 1 M $\Omega$  resistors in series.

- Do not apply a negative voltage

- Applying a negative voltage of -0.3 V or less to an LSI may generate a parasitic transistor, resulting in malfunction.

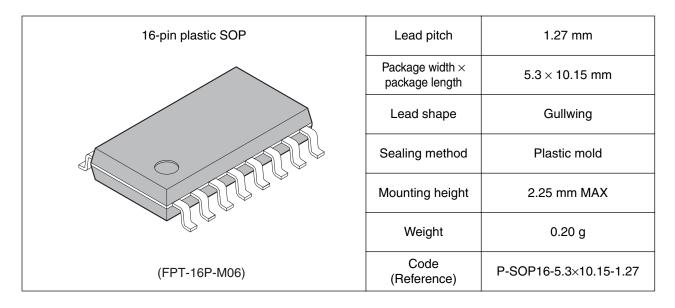

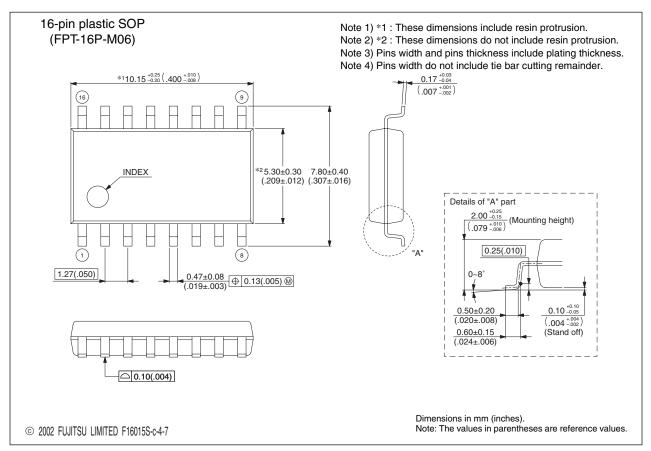

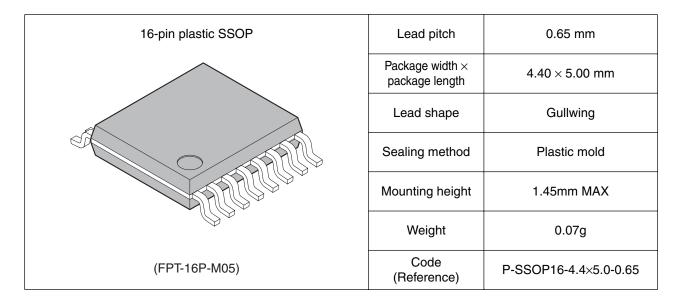

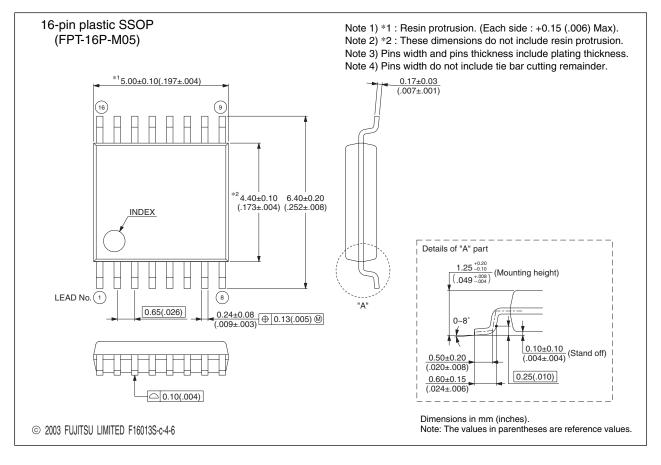

#### **■** ORDERING INFORMATION

| Part number     | Package                              | Remarks              |

|-----------------|--------------------------------------|----------------------|

| MB3778PFV-□□□   | 16-pin plastic SSOP<br>(FPT-16P-M05) | Conventional version |

| MB3778PF-□□□    | 16-pin plastic SOP<br>(FPT-16P-M06)  | Conventional version |

| MB3778PFV-□□□E1 | 16-pin plastic SSOP<br>(FPT-16P-M05) | Lead Free version    |

| MB3778PF-□□□E1  | 16-pin plastic SOP<br>(FPT-16P-M06)  | Lead Free version    |

#### ■ RoHS Compliance Information of Lead (Pb) Free version

The LSI products of Fujitsu with "E1" are compliant with RoHS Directive , and has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB) , and polybrominated diphenyl ethers (PBDE) .

The product that conforms to this standard is added "E1" at the end of the part number.

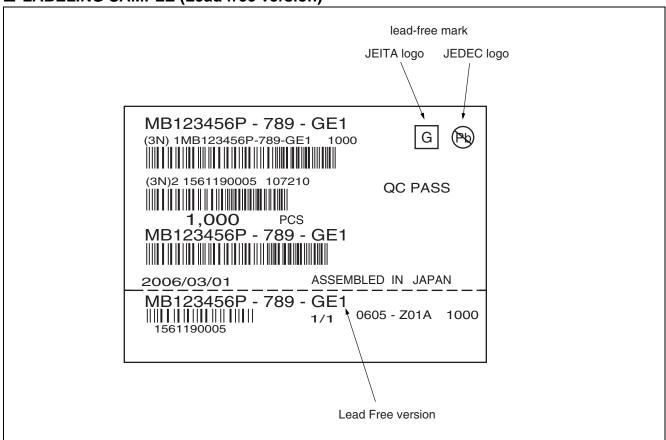

# **■ MARKING FORMAT (Lead Free version)** MB3778 XXXX XXX SOP-16 (FPT-16P-M06) INDEX Lead Free version Lead Free version SSOP-16 (FPT-16P-M05) INDEX

### ■ LABELING SAMPLE (Lead free version)

# ■ MB3778PF-□□□E1, MB3778PFV-□□□E1 RECOMMENDED CONDITIONS OF MOISTURE SENSITIVITY LEVEL

| Item               | Condition                                                       |                                                           |  |

|--------------------|-----------------------------------------------------------------|-----------------------------------------------------------|--|

| Mounting Method    | IR (infrared reflow), Manual soldering (partial heating method) |                                                           |  |

| Mounting times     | 2 times                                                         |                                                           |  |

|                    | Before opening                                                  | Please use it within two years after Manufacture.         |  |

| Storage period     | From opening to the 2nd reflow                                  | Less than 8 days                                          |  |

|                    | When the storage period after opening was exceeded              | Please processes within 8 days after baking (125 °C, 24H) |  |

| Storage conditions | 5 °C to 30 °C, 70%RH or less (the lowest possible humidity)     |                                                           |  |

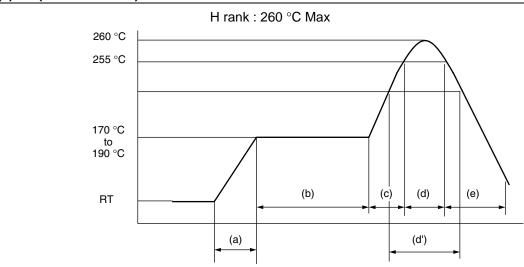

#### [Temperature Profile for FJ Standard IR Reflow]

#### (1) IR (infrared reflow)

(a) Temperature Increase gradient : Average 1 °C/s to 4 °C/s

(b) Preliminary heating : Temperature 170 °C to 190 °C, 60s to 180s

(c) Temperature Increase gradient : Average 1 °C/s to 4 °C/s

(d) Actual heating : Temperature 260 °C Max; 255 °C or more, 10s or less

(d') : Temperature 230 °C or more, 40s or less

or

Temperature 225 °C or more, 60s or less

or

Temperature 220 °C or more, 80s or less

(e) Cooling : Natural cooling or forced cooling

Note: Temperature: the top of the package body

### (2) Manual soldering (partial heating method)

Conditions : Temperature 400 °C Max

Times : 5 s max/pin

### **■ PACKAGE DIMENSIONS**

# **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

Edited Business Promotion Dept.