# M16C/6S Group

### SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0014-0501 Rev.5.01 Dec 10, 2009

# **Overview**

The M16C/6S group are highly integrated single-chip microcomputers with PLC (Power Line Communication) modem core and AFE (Analog Front End) in a 64-pin plastic molded LQFP package, which incorporates IT800 PLC modem technology developed by Yitran Communications Ltd. M16C/60 Series CPU core enables a high level of code efficiency and high-speed operation. In addition, the implementation of Yitran's patented DCSK (Differential Code Shift Keying) spread spectrum modulation technique in the IT800 modem core enables extremely robust communication over the existing electrical wiring, with data rates up to 7.5Kbps. The M16C/6S complies with worldwide regulations (FCC part 15, ARIB and CENELEC bands) and is suitable for a variety of narrowband applications like smart metering and home networking.

# **Applications**

Power Line Communication

# -----Table of Contents-----

| Overview                      | 1  |

|-------------------------------|----|

| Memory                        | 10 |

| Central Processing Unit (CPU) | 11 |

| SFR                           | 13 |

| Reset                         | 19 |

| Processor Mode                | 23 |

| Clock Generation Circuit      | 27 |

| Protection                    |    |

| Interrupts                    | 47 |

| Watchdog Timer                | 66 |

| DMAC                          | 68 |

| Timers                        | 78 |

| Timer A                       | 70 |

| Serial I/O                        | 92    |

|-----------------------------------|-------|

| Clock Synchronous serial I/O Mode | . 101 |

| UART Mode                         | . 109 |

| Special Mode                      | . 117 |

| SI/O3 and SI/O4                   | . 132 |

| Programmable I/O Ports            | . 137 |

| Electrical Characteristics        | . 149 |

| Flash Memory Version              | . 160 |

| IT800AFE (Analog Front End)       | . 184 |

| Usage Notes                       | . 189 |

| Appendix                          | . 199 |

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error. Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

# **Performance Outline**

Table 1.1.1 lists performance outline of M16C/6S group.

Table 1.1.1. Performance outline of M16C/6S group

| ltem                              |                       |           | Performance                                                      |  |

|-----------------------------------|-----------------------|-----------|------------------------------------------------------------------|--|

| CPU                               | Number of basic ins   |           | 91 instructions                                                  |  |

|                                   | Minimum Instruction E | Execution | 65.1 ns (f(BCLK)= 15.36MHz, VCC= 3.0V to 3.6V)                   |  |

|                                   | time                  |           |                                                                  |  |

|                                   | Operation Mode        |           | Single-chip mode                                                 |  |

|                                   | Memory Space          |           | 1M Byte                                                          |  |

|                                   | Memory Capacity       | ROM       | See Tables 1.1.3 and 1.1.4 Product List                          |  |

|                                   |                       | RAM       | 24K Byte                                                         |  |

| Peripheral                        | Port                  |           | Input/Output: 21 pins, Input: 1 pin                              |  |

| Function                          | Multifunction Timer   |           | Timer A: 16 bits x 5 channels,                                   |  |

|                                   | Serial I/O            |           | 2 channels                                                       |  |

|                                   |                       |           | Clock synchronous, UART, I <sup>2</sup> C bus <sup>(1)</sup> ,   |  |

|                                   |                       |           | 1 channel                                                        |  |

|                                   |                       |           | UART, I <sup>2</sup> C bus <sup>(1)</sup> ,                      |  |

|                                   |                       |           | 2 channels                                                       |  |

|                                   |                       |           | Clock synchronous(*)                                             |  |

|                                   |                       |           | (*) 1 channel is internally connected to IT800                   |  |

| DMAC                              |                       |           | 2 channels                                                       |  |

|                                   | Watchdog Timer        |           | 15 bits x 1 channel (with prescaler)                             |  |

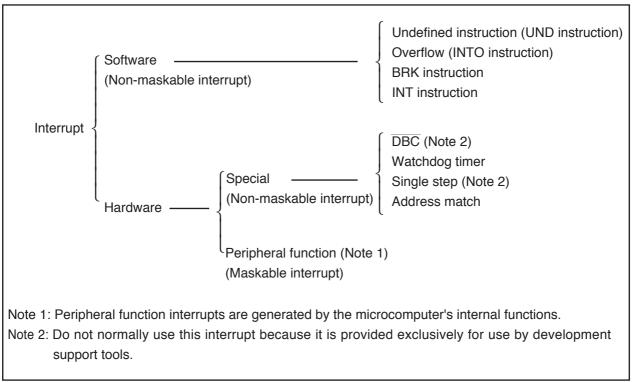

|                                   | Interrupt             |           | 21 internal and 3 external sources, 4 software sources, 7 levels |  |

|                                   | Clock Generation C    | ircuit    | 2 circuits                                                       |  |

|                                   |                       |           | Main clock generation circuit with PLL synthesizer (*),          |  |

|                                   |                       |           | On-chip oscillator,                                              |  |

|                                   |                       |           | (*) This circuit contains a built-in feedback resister.          |  |

| Electrical                        | Power supply voltage  |           | 3.0V to 3.6V                                                     |  |

| Characteristics                   | Power Consumption     |           | 70mA (VCC= VCCA= 3.3V, f(XIN)= 5.12MHz)                          |  |

| Flash memory                      |                       |           | 3.0V to 3.6V (Topr= 0 to 60°C)                                   |  |

| Version                           | S .                   |           | 100 times or 1,000 times <sup>(2)</sup>                          |  |

| Power consumption                 |                       |           | 70mA (VCC= VCCA= 3.3V, f(XIN)= 5.12MHz)                          |  |

| Operating Ambient Temperature (2) |                       | :)        | -20 to 85°C                                                      |  |

|                                   |                       |           | -40 to 85°C                                                      |  |

|                                   |                       |           | -40 to 105°C                                                     |  |

| Package                           |                       |           | 64-pin plastic mold LQFP                                         |  |

#### Notes

- 1. I<sup>2</sup>C Bus is a registered trademark of Koninklijke Philips Electronics N. V.

- 2. See Tables 1.1.5 and 1.1.6 Product code for increased program/erase cycle version, and version of expanded operating ambient temperature.

## IT800 PHY performance outline of M16C/6S group.

The IT800 PHY is a PLC optimized Physical Layer (PHY) which consists of IT800 modem core and internal AFE (Analog Front End). The implementation of Yitran's patented DCSK spread spectrum modulation technique in the IT800 modem core enables extremely robust communication over the existing electrical wiring, with data rates up to 7.5Kbps. In addition to the inherent interference immunity provided by the DCSK modulation, the IT800 PHY utilizes several mechanisms for enhanced communication robustness, such as forward short block soft decoding error correction algorithm and special synchronization algorithms.

The IT800PHY communicates M16C core with clock synchronous serial I/O, interrupt and input/output ports in M16C/6S (Note). M16C/6S requires external AFE. Table 1.1.2 lists IT800 PHY performance outline of M16C/6S group.

Table 1.1.2. IT800 PHY performance outline of M16C/6S group

|                     | tem         | Performance                                                    |  |  |

|---------------------|-------------|----------------------------------------------------------------|--|--|

| Features            |             | High immunity to signal fading, various noise characteristics, |  |  |

|                     |             | impedance modulation and phase/frequency distortion            |  |  |

|                     |             | High in-phase and cross-phase reliability                      |  |  |

| Modulation Technic  | lue         | DCSK (Differential Code Shift Keying)*                         |  |  |

|                     |             | *Yitran patented modulation technique                          |  |  |

| Error Correction/De | tection     | Forward short-block soft decoding error correction mechanism,  |  |  |

|                     |             | CRC-16                                                         |  |  |

| Complies with W/W   | Regulations | FCC, ARIB, EN50065-1-CENELEC                                   |  |  |

| Data Rate &         | FCC & ARIB  | 120-400 KHz                                                    |  |  |

| Frequency Band      |             | 7.5Kbps Standard Mode (SM)                                     |  |  |

|                     |             | 5.0Kbps Robust Mode (RM)                                       |  |  |

|                     |             | 1.25Kbps Extremely Robust Mode (ERM)                           |  |  |

|                     | CENELEC     | A-Band (Outdoor): 20-80 KHz                                    |  |  |

|                     |             | B-Band (Indoor): 95-125 KHz                                    |  |  |

|                     |             | 2.5 Kbps Robust Mode (RM)                                      |  |  |

|                     |             | 0.625Kbps Extremely Robust Mode (ERM)                          |  |  |

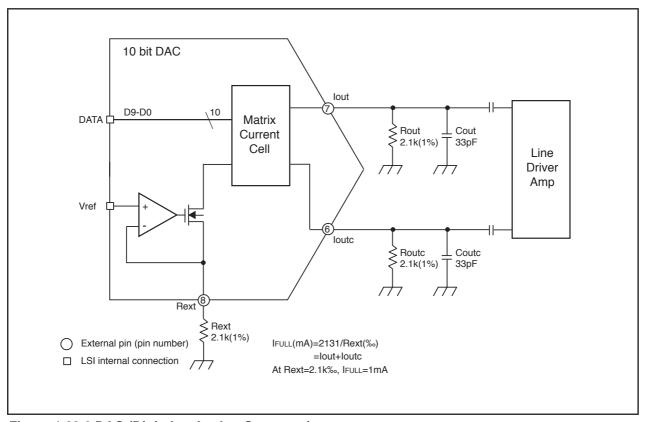

| Internal AFE        |             | 10bit-D/A converter, preamp,                                   |  |  |

|                     |             | 1bit-A/D converter x 3 channels                                |  |  |

#### Note:

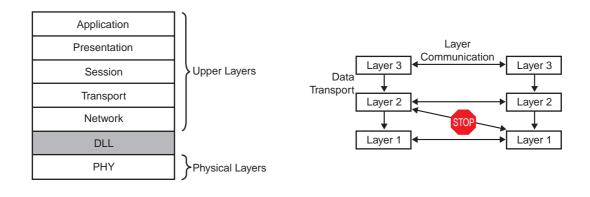

Direct operation of IT800 PHY is not recommended. Since the Layer 2 (DLL) handles the channel access procedure, using the IT800DLL as such assures coexistence with other IT800 technology based products, regardless of the vendor, protocol and the application. There is NO such coexistence if the device is used in direct operation of IT800 PHY. Note that the coexistence here is not with other technologies but with other IT800 technology based products. As for details, please refer to the next section and Appendix.

#### **About Firmware**

Renesas recommends IT800DLL (Product name: D2DL) as a Data Link Layer (DLL) of M16C/6S group. The IT800 DLL is a PLC optimized DLL especially for the products based on Yitran's IT800 technology. For availability of IT800DLL, please contact Renesas technical support representative. For more details about the IT800DLL advantages, please refer to Appendix.

# **Block Diagram and PLC application Outline**

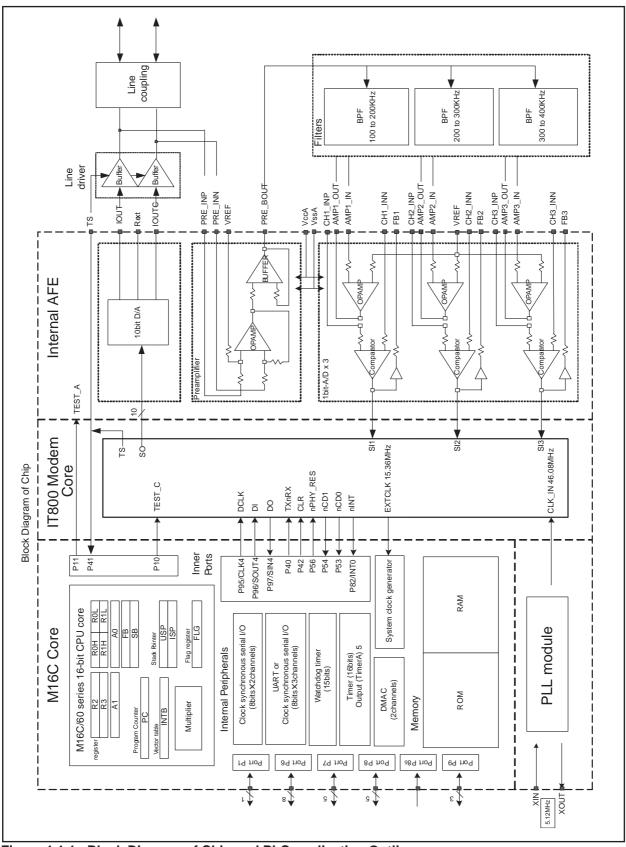

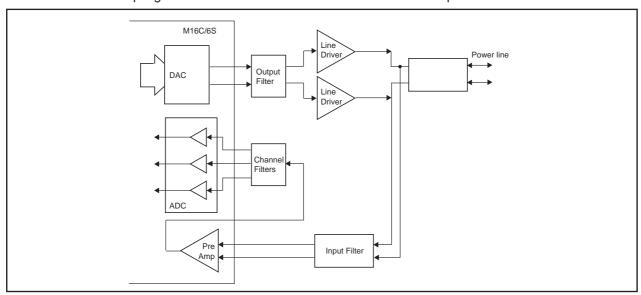

Figure 1.1.1 is a block diagram of the M16C/6S group and PLC application Outline.

Figure 1.1.1. Block Diagram of Chip and PLC application Outline

#### **Product List**

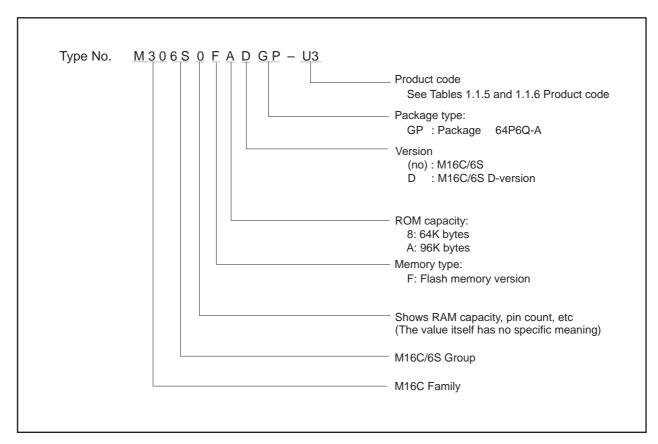

Tables 1.1.3 and 1.1.4 list the M16C/6S group product and Figure 1.1.2 shows the type numbers, memory sizes and packages.

Table 1.1.3. Product List (1) M16C/6S

Current of Dec. 2009

| Type No.   | ROM capacity | RAM capacity | Package type           | Remarks      | Product Code         |

|------------|--------------|--------------|------------------------|--------------|----------------------|

| M306S0FAGP | 96K bytes    | 24K bytes    | PLQP0064KB-A (64P6Q-A) | Flash memory | U3, U5, U7(D), U9(D) |

(D): under development

Table 1.1.4. Product List (2) M16C/6S D-version

Current of Dec. 2009

| Type No.    | ROM capacity | RAM capacity | Package type           | Remarks      | Product Code |

|-------------|--------------|--------------|------------------------|--------------|--------------|

| M306S0F8DGP | 64K bytes    | 24K bytes    | PLQP0064KB-A (64P6Q-A) | Flash memory | U3           |

| M306S0FADGP | 96K bytes    | 24K bytes    | PLQP0064KB-A (64P6Q-A) | Flash memory | U3           |

Figure 1.1.2. Type No., Memory Size, and Package

Table 1.1.5. Product Code (1) M16C/6S

|                 |           | Interna    | al ROM            | Microcomputer            |               |

|-----------------|-----------|------------|-------------------|--------------------------|---------------|

| Product<br>Code | Package   | E/W cycles | Temperature range | operating<br>temperature |               |

| U3              |           | 100        |                   | -40°C to 85°C            |               |

| U5              | LEAD from | 1,000      | 000 to 0000       | -20°C to 85°C            |               |

| U7 (D)          | LEAD free |            |                   | 0°C to 60°C              | -40°C to 85°C |

| U9 (D)          |           |            |                   | -20°C to 85°C            |               |

(D): under development

Table 1.1.6. Product Code (2) M16C/6S D-version

|                |           | Interna    | al ROM            | Microcomputer            |  |

|----------------|-----------|------------|-------------------|--------------------------|--|

| Produc<br>Code | t Package | E/W cycles | Temperature range | operating<br>temperature |  |

| U3             | LEAD free | 100        | 0°C to 60°C       | -40°C to 105°C           |  |

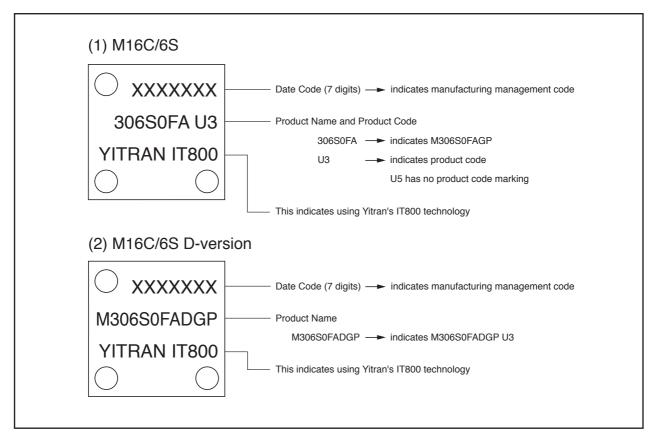

Figure 1.1.3. Marking (Top View)

# **Pin Configuration**

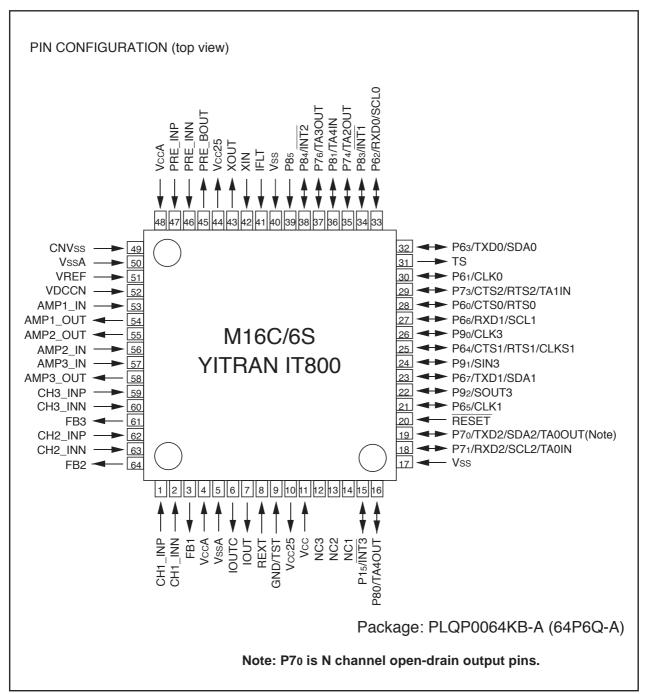

Figures 1.1.4 show the pin configurations (top view).

Figure 1.1.4. Pin Configuration (Top View)

# Table 1.1.7 Pin Description (1)

| Pin name                      | Signal name                 | I/O type            | Function                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss                      | Power supply input          |                     | Apply 3.0V to 3.6V to the Vcc pin. Apply 0V to the Vss pin.                                                                                                                                                                                                                                                                                   |

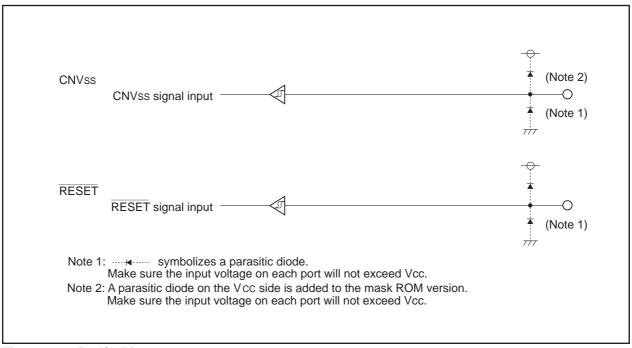

| CNVss                         | CNVss                       | Input               | This is a pin for changing flash memory mode. Usually, connect to Vss.                                                                                                                                                                                                                                                                        |

| RESET                         | Reset input                 | Input               | "L" on this input resets the microcomputer.                                                                                                                                                                                                                                                                                                   |

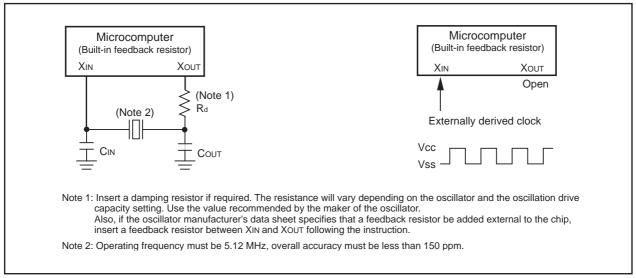

| XIN                           | Clock input<br>Clock output | Input<br>Output     | I/O pins for the main clock generation circuit. Connect a ceramic resonator or crystal oscillator between XIN and XOUT (3). To use the external clock, input the clock from XIN and leave XOUT open.                                                                                                                                          |

| VccA                          | Analog power supply input   | •                   | This pin is a power supply input of analog circuit. Connect to Vcc.                                                                                                                                                                                                                                                                           |

| VssA                          | Analog power supply input   |                     | This pin is a power supply input of analog circuit. Connect to Vss.                                                                                                                                                                                                                                                                           |

| GND/TST                       | Input for test              | Input               | This is input pin for test. Connect to Vss.                                                                                                                                                                                                                                                                                                   |

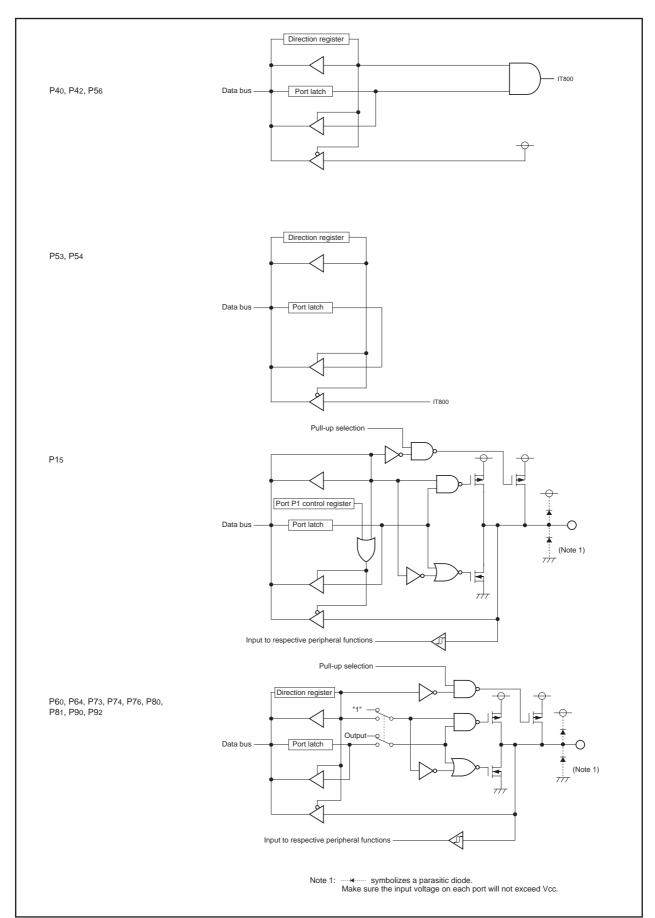

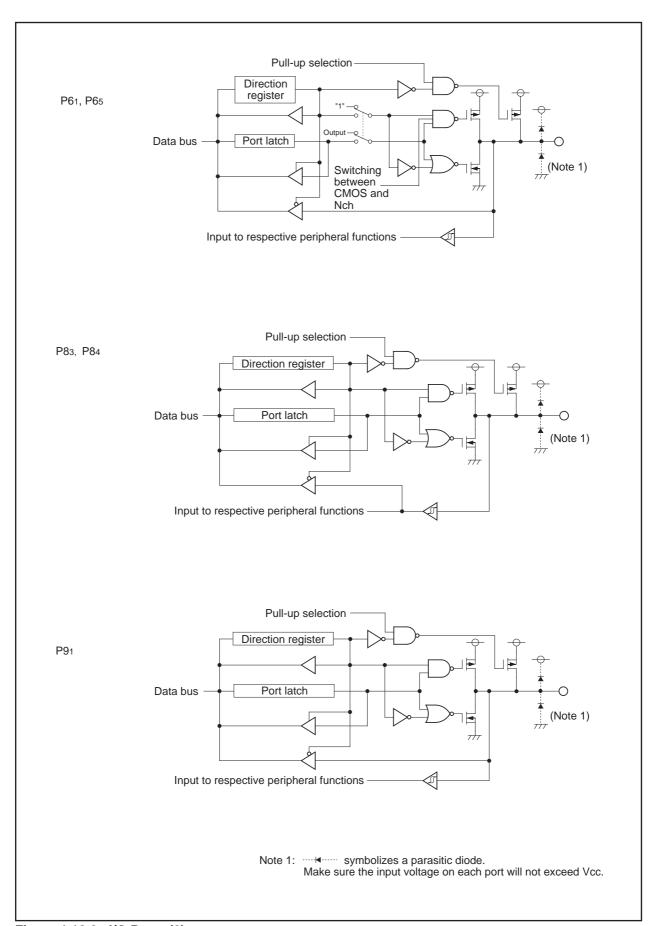

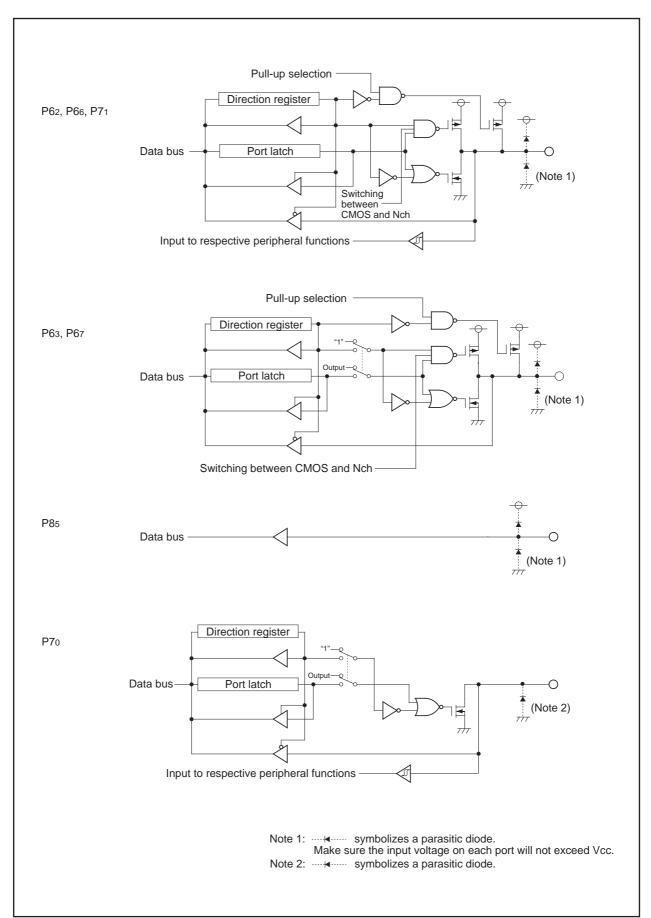

| P15                           | I/O port P1                 | Input/output        | This is an 1-bit I/O port equivalent to P6. By choosing by the program, it functions as an input pin of INT interrupt.                                                                                                                                                                                                                        |

| Vcc25                         | Power supply                |                     | It is the 2.5V power supply pin which is carrying out internal generating.  Connect Vcc25 two pins each other and add stabilization capacity.                                                                                                                                                                                                 |

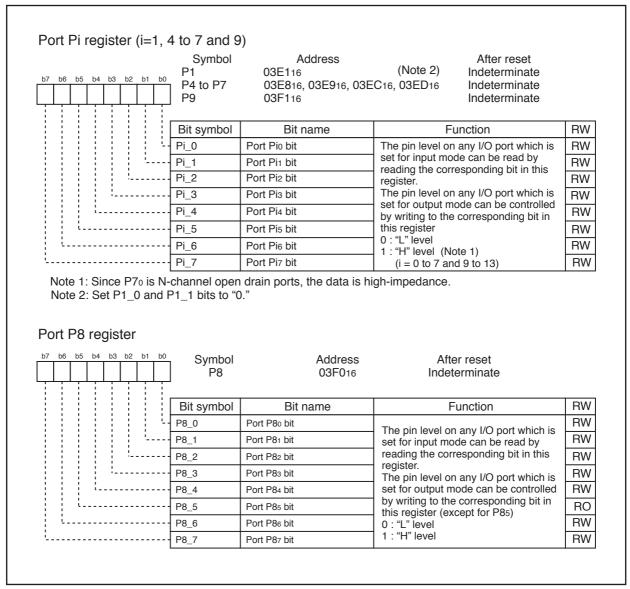

| P60 to P67                    | I/O port P6                 | Input/output        | This is the 8-bit I/O port of CMOS. It has a direction register for choosing I/O, and is made for every pin in an input port or an output port. An input port can choose the existence of pull-up resistance in a 4-bit unit by the program. It functions as an I/O pin of what is chosen by the program which are therefore UARTO and UART1. |

| P70, P71,<br>P73, P74,<br>P76 | I/O port P7                 | Input/output        | It is an I/O port with a function equivalent to P6 (however, P7o N channel open-drain output). By choosing by the program, it functions as an I/O pin of timers A0 to A3. Moreover, P7o to P73 function also as an I/O pin of UART2.                                                                                                          |

| P80, P81,<br>P83, P84,<br>P85 | I/O port P8                 | Input/output        | P80, P81, P83, and P84 are I/O ports with a function equivalent to P6. By choosing by the program, P80 to P81 function as an I/O pin of timer A4, and P83 to P84 functions as an input pin of INT interruption.                                                                                                                               |

|                               | Input port<br>P85           | Input               | P8s cannot be used as general input pin. Pull-up resistance cannot set up this pin. This pin must be pulled-up externally to Vcc, and be fixed to "H".                                                                                                                                                                                        |

| P90 to P92                    | I/O port P9                 | Input/output        | It is an I/O port with a function equivalent to P6. It functions as an I/O pin of SILO3 by choosing by the program.                                                                                                                                                                                                                           |

| TS                            | Output port<br>TS           | Output              | This is the pin with which IT800 controls ON/OFF of an output to the external transmission AMP at the time of power line communication.                                                                                                                                                                                                       |

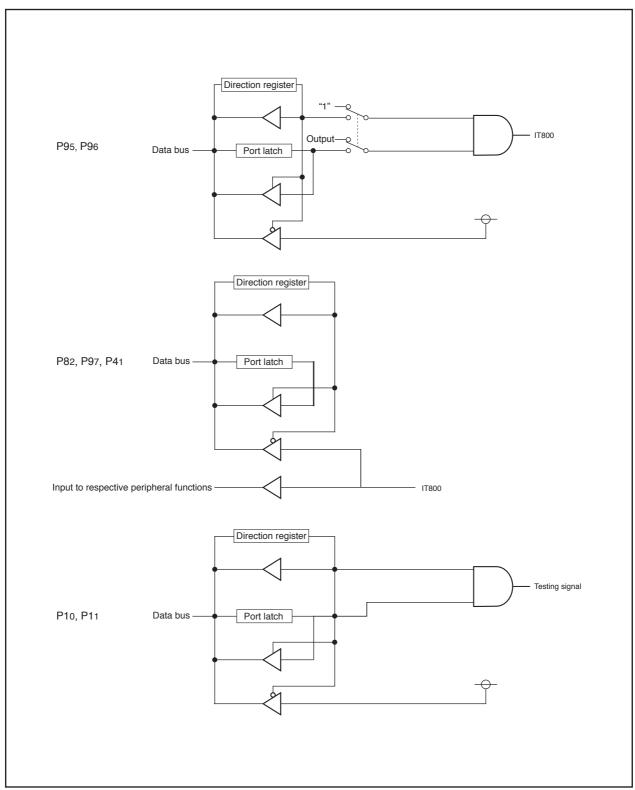

| P10                           | Inner port P10              | keep Input          | Port for IT800 Testing. Please set Direction Register PD1_0 "0" for keeping Input.                                                                                                                                                                                                                                                            |

| P11                           | Inner port P11              | keep Input          | Port for AFE Testing. Please set Direction Register PD1_1 "0" for keeping Input.                                                                                                                                                                                                                                                              |

| P40                           | Inner port<br>P40           | Output to<br>IT800  | I/O Port for communication between M16C Core and IT800 Modem. Please set Direction Register PD4_0 "1" to Output a signal to IT800. The output signal is connected to TXnRX of IT800 inside of chip.                                                                                                                                           |

| P41                           | Inner port<br>P41           | Input from<br>IT800 | I/O Port for communication between M16C Core and IT800 Modem (Note.1). Please set Direction Register PD4_1 "0" to Input a signal from IT800. The TS signal is input from IT800 inside of chip.                                                                                                                                                |

| P42                           | Inner port<br>P42           | Output to<br>IT800  | I/O Port for communication between M16C Core and IT800 Modem. Please set Direction Register PD4_2 "1" to Output a signal to IT800. The output signal is connected to CLR of IT800 inside of chip.                                                                                                                                             |

| P53                           | Inner port<br>P53           | Input from<br>IT800 | I/O Port for communication between M16C Core and IT800 Modem (Note.1). Please set Direction Register PD5_3 "0" to Input a signal from IT800. The nCD0 signal is input from IT800 inside of chip.                                                                                                                                              |

| P54                           | Inner port<br>P54           | Input from<br>IT800 | I/O Port for communication between M16C Core and IT800 Modem (Note.1). Please set Direction Register PD5_4 "0" to Input a signal from IT800. The nCD1 signal is input from IT800 inside of chip.                                                                                                                                              |

| P56                           | Inner port<br>P56           | Output to<br>IT800  | I/O Port for communication between M16C Core and IT800 Modem. Please set Direction Register PD5_6 "1" to Output a signal to IT800. The output signal is connected to nPHY_RES of IT800 inside of chip.                                                                                                                                        |

| P82                           | Inner port<br>P82           | Input from<br>IT800 | I/O Port for communication between M16C Core and IT800 Modem (Note.1). nINT signal of IT800 is connected to this port inside of chip for carrying out Interrupt function by software.                                                                                                                                                         |

| P95                           | Inner port<br>P95           | Output to<br>IT800  | I/O Port for communication between M16C Core and IT800 Modem. This port is connected to DCLK signal of IT800 inside of chip as SILO4 CLK4 functional Output port by choosing by the program.                                                                                                                                                  |

| P96                           | Inner port<br>P96           | Output to<br>IT800  | I/O Port for communication between M16C Core and IT800 Modem. This port is connected to DI signal of IT800 inside of chip as SILO4 SOUT4 functional Output port by choosing by the program.                                                                                                                                                   |

| P97                           | Inner port<br>P97           | Input from<br>IT800 | I/O Port for communication between M16C Core and IT800 Modem. This port is connected to DI signal of IT800 inside of chip as SILO4 SOUT4 functional Input port by choosing by the program.                                                                                                                                                    |

### NOTES:

- 1. In case of Direction Register "1", any signal is not output from M16C to assigned signal of IT800 . Refer to Programmable I/O Ports pages.

- 2. Ask the oscillator maker the oscillation characteristic.

Table 1.1.8 Pin Description (2) (Analog pin)

| Pin name | I/O type | Function                                                                         |

|----------|----------|----------------------------------------------------------------------------------|

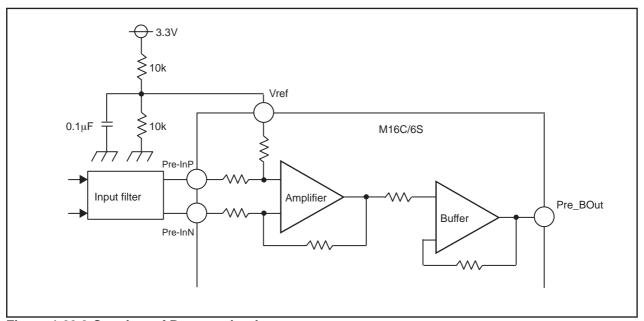

| PRE-BOUT | Output   | This is a pre-amp buffer output.                                                 |

| PRE-INN  | Input    | This is a pre-amp differential signal input.                                     |

| PRE-INP  | Input    | This is a pre-amp differential signal input.                                     |

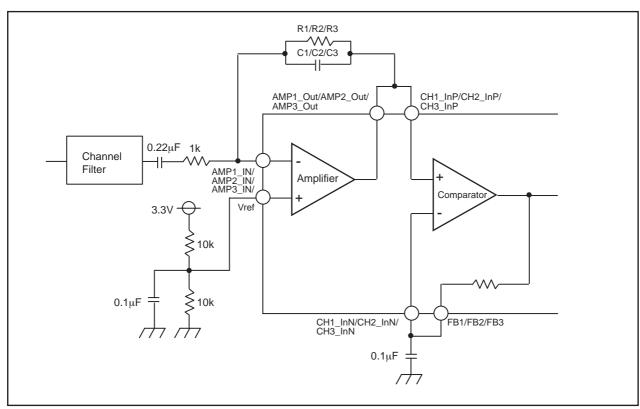

| VREF     | Input    | This is the reference voltage input of amplifier common to channels 1, 2, and 3. |

| VDCCN    | Input    | This is a pin for a test. Usually, please carry out a pull-up.                   |

| AMP1-IN  | Input    | This is a channel 1 amplifier input.                                             |

| AMP1-OUT | Output   | This is a channel 1 amplifier output.                                            |

| AMP2-IN  | Input    | This is a channel 2 amplifier input.                                             |

| AMP2-OUT | Output   | This is a channel 2 amplifier output.                                            |

| AMP3-IN  | Input    | This is a channel 3 amplifier input.                                             |

| AMP3-OUT | Output   | This is a channel 3 amplifier output.                                            |

| CHI-INP  | Input    | This is a channel 1 comparator differential input.                               |

| CHI-INN  | Input    | This is a channel 1 comparator differential input.                               |

| FB1      | Output   | This is a channel 1 comparator feedback output.                                  |

| CH2-INP  | Input    | This is a channel 2 comparator differential input.                               |

| CH2-INN  | Input    | This is a channel 2 comparator differential input.                               |

| FB2      | Output   | This is a channel 2 comparator feedback output.                                  |

| CH3-INP  | Input    | This is a channel 3 comparator differential input.                               |

| CH3-INN  | Input    | This is a channel 3 comparator differential input.                               |

| FB3      | Output   | This is a channel 3 comparator feedback output.                                  |

| IOUTC    | Output   | This is the differential current output of DAC.                                  |

| IOUT     | Output   | This is the differential current output of DAC.                                  |

| REXT     | Input    | This is for external reference resistor of DAC.                                  |

| IFLT     | Input    | This is the pin for low path filters of PLL.                                     |

M16C/6S Group Memory

# **Memory**

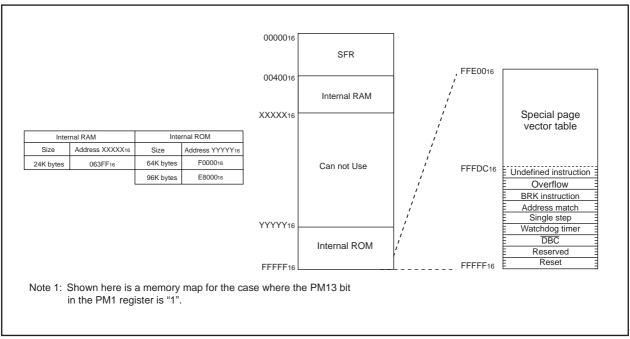

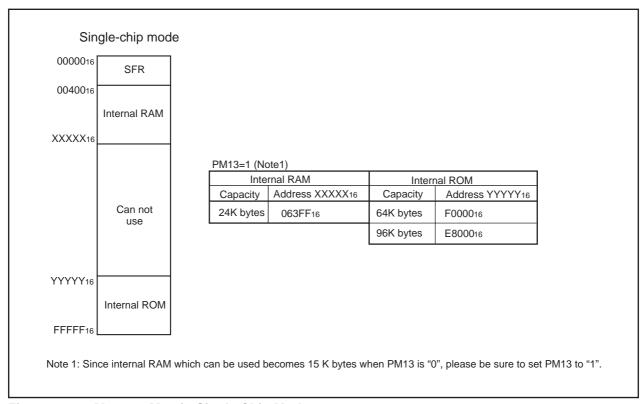

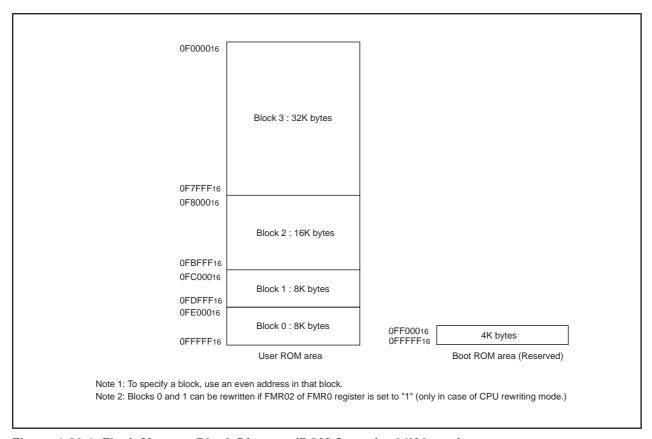

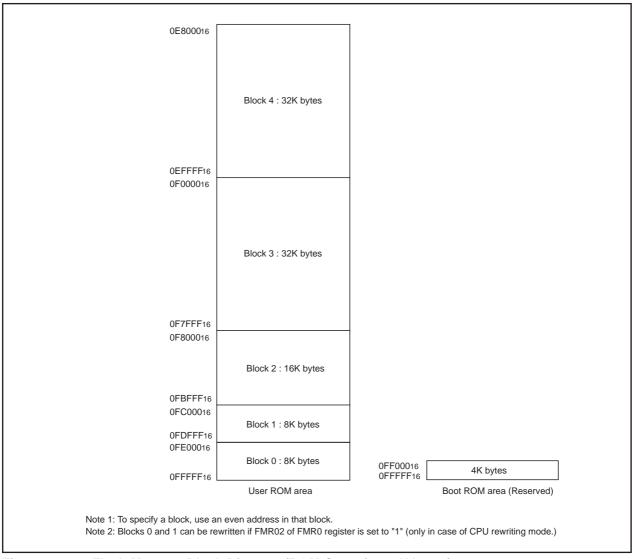

Figure 1.2.1 is a memory map of the M16C/6S group. The address space extends the 1M bytes from address 0000016 to FFFFF16.

The internal ROM is allocated in a lower address direction beginning with address FFFF16. For example, a 96-Kbyte internal ROM is allocated to the addresses from E800016 to FFFF16.

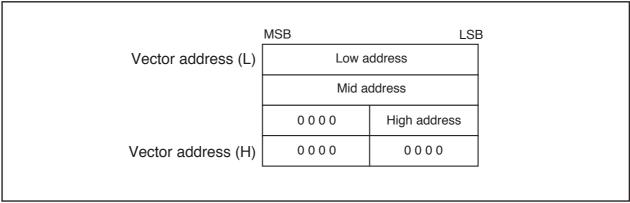

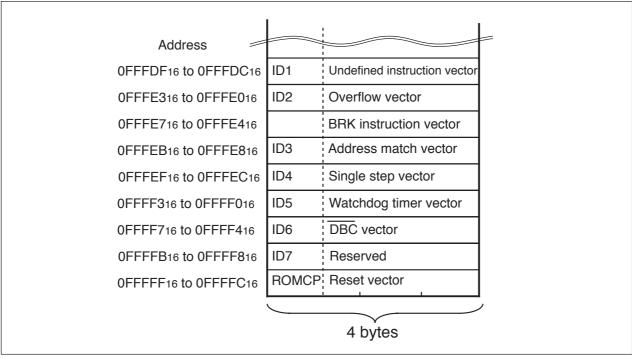

The fixed interrupt vector table is allocated to the addresses from FFFDC16 to FFFFF16. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 0040016. For example, a 24-Kbytes internal RAM is allocated to the addresses from 0040016 to 063FF16. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SRF is allocated to the addresses from 0000016 to 003FF16. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE0016 to FFFDB16. This vector is used by the JMPS or JSRS instruction. For details, refer to the "M16C/60 and M16C/20 Series Software Manual."

Figure 1.2.1. Memory Map

# **Central Processing Unit (CPU)**

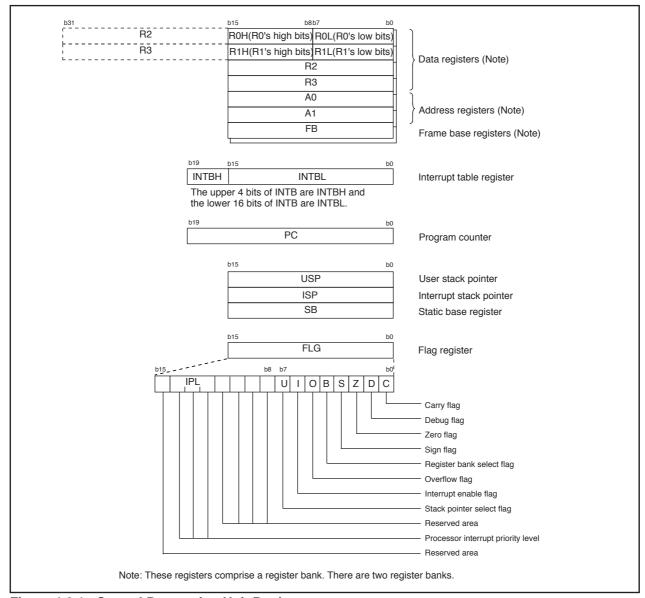

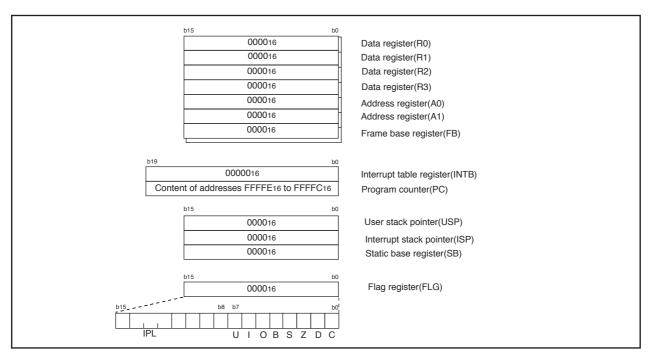

Figure 1.3.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. There are two register banks.

Figure 1.3.1. Central Processing Unit Register

# (1) Data Registers (R0, R1, R2 and R3)

The R0 register consists of 16 bits, and is used mainly for transfers and arithmetic/logic operations. R1 to R3 are the same as R0.

The R0 register can be separated between high (R0H) and low (R0L) for use as two 8-bit data registers. R1H and R1L are the same as R0H and R0L. Conversely, R2 and R0 can be combined for use as a 32-bit data register (R2R0). R3R1 is the same as R2R0.

#### (2) Address Registers (A0 and A1)

The register A0 consists of 16 bits, and is used for address register indirect addressing and address register relative addressing. They also are used for transfers and logic/logic operations. A1 is the same as A0.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

# (3) Frame Base Register (FB)

FB is configured with 16 bits, and is used for FB relative addressing.

## (4) Interrupt Table Register (INTB)

INTB is configured with 20 bits, indicating the start address of an interrupt vector table.

# (5) Program Counter (PC)

PC is configured with 20 bits, indicating the address of an instruction to be executed.

# (6) User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Stack pointer (SP) comes in two types: USP and ISP, each configured with 16 bits. Your desired type of stack pointer (USP or ISP) can be selected by the U flag of FLG.

## (7) Static Base Register (SB)

SB is configured with 16 bits, and is used for SB relative addressing.

## (8) Flag Register (FLG)

FLG consists of 11 bits, indicating the CPU status.

### Carry Flag (C Flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

#### Debug Flag (D Flag)

The D flag is used exclusively for debugging purpose. During normal use, it must be set to "0".

#### Zero Flag (Z Flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, it is "0".

#### Sign Flag (S Flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, it is "0".

# • Register Bank Select Flag (B Flag)

Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

#### Overflow Flag (O Flag)

This flag is set to "1" when the operation resulted in an overflow; otherwise, it is "0".

#### • Interrupt Enable Flag (I Flag)

This flag enables a maskable interrupt.

Maskable interrupts are disabled when the I flag is "0", and are enabled when the I flag is "1". The I flag is cleared to "0" when the interrupt request is accepted.

### Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is "0"; USP is selected when the U flag is "1".

The U flag is cleared to "0" when a hardware interrupt request is accepted or an INT instruction for software interrupt Nos. 0 to 31 is executed.

#### Processor Interrupt Priority Level (IPL)

IPL is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than IPL, the interrupt is enabled.

#### Reserved Area

When write to this bit, write "0". When read, its content is indeterminate.

# **SFR**

| Address                                  | Dogistor                                                  |         | Symbol     | After reset                  |

|------------------------------------------|-----------------------------------------------------------|---------|------------|------------------------------|

|                                          | Register                                                  |         | Symbol     | After reset                  |

| 000016<br>000116                         |                                                           |         |            |                              |

|                                          |                                                           |         |            |                              |

| 000216                                   |                                                           |         |            |                              |

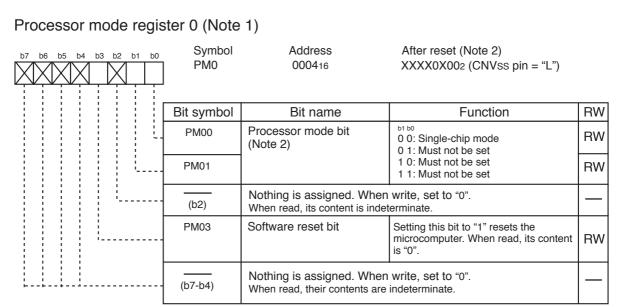

| 000316                                   | Dragger made register 0                                   | Note 2) | DMO        | XXXX0X002 (CNVss pin is "L") |

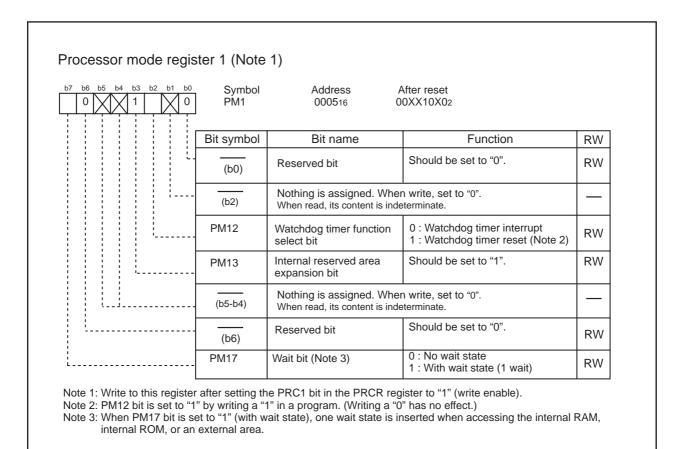

| 000416                                   |                                                           | Note 2) | PM0<br>PM1 | 00XX10X02                    |

| 000516                                   | Processor mode register 1 System clock control register 0 |         | CM0        | 010010002                    |

| 000616                                   | System clock control register 1                           |         | CM1        | 001000002                    |

| 000716                                   | System clock control register 1                           |         | CIVIT      | 001000002                    |

| 000816                                   | Address match interrupt enable register                   |         | AIER       | XXXXXX002                    |

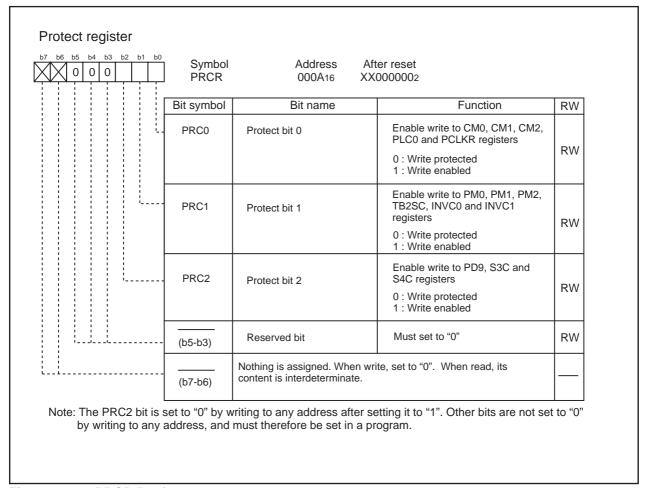

| 000916                                   | Protect register                                          |         | PRCR       | XX0000002                    |

| 000A16                                   | 1 Total Tagistal                                          |         | TROK       | 7770000002                   |

| 000B16                                   | Oscillation stop detection register (                     | Note 3) | CM2        | 0000X0002                    |

| 000C16                                   | Oscillation stop detection register                       | Note 3) | CIVIZ      | 000070002                    |

| 000D16                                   | Watchdog timer start register                             |         | WDTS       | ??16                         |

| 000E16                                   |                                                           |         | WDC        | 00??????2                    |

| 000F16                                   | Watchdog timer control register                           |         |            |                              |

| 001016                                   | Address match interrupt register 0                        |         | RMAD0      | 0016                         |

| 001116                                   |                                                           |         |            | 0016                         |

| 001216                                   |                                                           |         |            | X016                         |

| 001316                                   | Address motels intownist as sister 4                      | +       | DMAD4      | 0040                         |

| 001416                                   | Address match interrupt register 1                        |         | RMAD1      | 0016                         |

| 001516                                   |                                                           |         |            | 0016                         |

| 001616                                   |                                                           |         |            | X016                         |

| 001716                                   |                                                           | +       |            |                              |

| 001816                                   |                                                           |         |            |                              |

| 001916                                   |                                                           |         |            |                              |

| 001A16                                   |                                                           |         |            |                              |

| 001B16                                   |                                                           |         |            |                              |

| 001C16                                   |                                                           |         |            |                              |

| 001D <sub>16</sub><br>001E <sub>16</sub> | Drocessor mode register 2                                 |         | PM2        | XXX000002                    |

| 001E16                                   | Processor mode register 2                                 |         | FIVIZ      | XXX000002                    |

| 001F16                                   | DMA0 source pointer                                       |         | SAR0       | ??16                         |

| 002016                                   | Divino source pointer                                     |         | OAITO      | ??16                         |

| 002216                                   |                                                           |         |            | X?16                         |

| 002316                                   |                                                           |         |            | Χ:10                         |

| 002416                                   | DMA0 destination pointer                                  |         | DAR0       | ??16                         |

| 002516                                   | DIVIAO destination pointei                                |         | DAILO      | ??16                         |

| 002616                                   |                                                           |         |            | X?16                         |

| 002716                                   |                                                           |         |            | Λ:10                         |

| 002816                                   | DMA0 transfer counter                                     |         | TCR0       | ??16                         |

| 002916                                   | DW/ to transfer counter                                   |         | 10110      | ??16                         |

| 002A16                                   |                                                           |         |            | 1110                         |

| 002B16                                   |                                                           |         |            |                              |

| 002C16                                   | DMA0 control register                                     |         | DM0CON     | 00000?002                    |

| 002D16                                   | ····                                                      |         |            | 22200.002                    |

| 002E16                                   |                                                           |         |            |                              |

| 002F16                                   |                                                           |         |            |                              |

| 003016                                   | DMA1 source pointer                                       |         | SAR1       | ??16                         |

| 003116                                   | Divinat source political                                  |         | OAIVI      | ??16                         |

| 003216                                   |                                                           |         |            | X?16                         |

| 003316                                   |                                                           |         |            | A: 10                        |

| 003416                                   | DMA1 destination pointer                                  |         | DAR1       | ??16                         |

| 003516                                   | •                                                         |         |            | ??16                         |

| 003616                                   |                                                           |         |            | X?16                         |

| 003716                                   |                                                           |         |            | -                            |

| 003816                                   | DMA1 transfer counter                                     |         | TCR1       | ??16                         |

| 003916                                   | 2mm tradition counter                                     |         | 101(1      | ??16                         |

| 003A16                                   |                                                           |         |            | ::10                         |

| 003B <sub>16</sub>                       |                                                           |         |            |                              |

| 003C16                                   | DMA1 control register                                     |         | DM1CON     | 00000?002                    |

| 003D16                                   | 2 mil (1 control rogioto)                                 |         | DIVITOON   | 00000:002                    |

| 003E16                                   |                                                           |         |            |                              |

| 003F16                                   |                                                           |         |            |                              |

|                                          |                                                           |         |            |                              |

Note 1: The blank areas are reserved and cannot be used by users.

Note 2: The PM00 and PM01 bits do not change at software reset, watchdog timer reset and oscillation stop detection reset.

Note 3: The CM20, CM21, and CM27 bits do not change at oscillation stop detection reset.

X : Nothing is mapped to this bit ? : Undefined

| Address            | Register                                                                                                          | Symbol         | After reset            |

|--------------------|-------------------------------------------------------------------------------------------------------------------|----------------|------------------------|

| 004016             |                                                                                                                   |                |                        |

| 004116             |                                                                                                                   |                |                        |

| 004216             |                                                                                                                   |                |                        |

| 004316             | NITTO I I I I I I I I I I I I I I I I I I                                                                         | 11.17010       | )/)/aaaaa              |

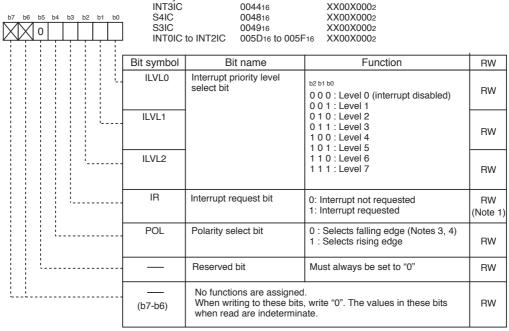

| 004416             | INT3 interrupt control register                                                                                   | INT3IC         | XX00?0002              |

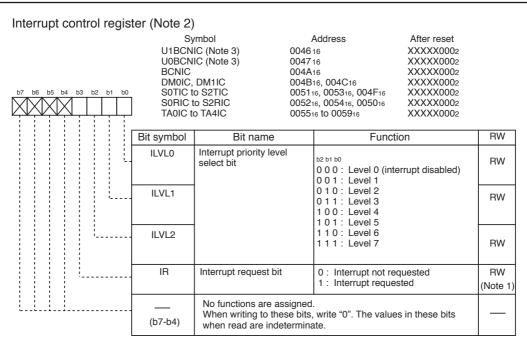

| 004516<br>004616   | LIADTA DUC collision detection interment control register                                                         | U1BCNIC        | XXXX?0002              |

| 004616             | UART1 BUS collision detection interrupt control register UART0 BUS collision detection interrupt control register | U0BCNIC        | XXXX?0002<br>XXXX?0002 |

| 004716             | SI/O4 interrupt control register (S4IC)                                                                           | S4IC           | XX00?0002              |

| 004916             | SI/O3 interrupt control register                                                                                  | S3IC           | XX00?0002              |

| 004A16             | UART2 Bus collision detection interrupt control register                                                          | BCNIC          | XXXX?0002              |

| 004B16             | DMA0 interrupt control register                                                                                   | DM0IC          | XXXX?0002              |

| 004C16             | DMA1 interrupt control register                                                                                   | DM1IC          | XXXX?0002              |

| 004D16             | •                                                                                                                 |                |                        |

| 004E <sub>16</sub> |                                                                                                                   |                |                        |

| 004F16             | UART2 transmit interrupt control register                                                                         | S2TIC          | XXXX?0002              |

| 005016             | UART2 receive interrupt control register                                                                          | S2RIC          | XXXX?0002              |

| 005116             | UART0 transmit interrupt control register                                                                         | SOTIC          | XXXX?0002              |

| 005216<br>005316   | UART0 receive interrupt control register UART1 transmit interrupt control register                                | S0RIC<br>S1TIC | XXXX?0002              |

| 005316             | UART1 transmit interrupt control register  UART1 receive interrupt control register                               | S1TIC<br>S1RIC | XXXX?0002<br>XXXX?0002 |

| 005416             | Timer A0 interrupt control register                                                                               | TAOIC          | XXXX?0002<br>XXXX?0002 |

| 005616             | Timer A1 interrupt control register                                                                               | TA1IC          | XXXX?0002<br>XXXX?0002 |

| 005716             | Timer A7 interrupt control register  Timer A2 interrupt control register                                          | TA2IC          | XXXX?0002<br>XXXX?0002 |

| 005816             | Timer A3 interrupt control register                                                                               | TA3IC          | XXXX?0002              |

| 005916             | Timer A4 interrupt control register                                                                               | TA4IC          | XXXX?0002              |

| 005A16             |                                                                                                                   |                |                        |

| 005B <sub>16</sub> |                                                                                                                   |                |                        |

| 005C16             |                                                                                                                   |                |                        |

| 005D16             | INTO interrupt control register                                                                                   | INTOIC         | XX00?0002              |

| 005E16             | INT1 interrupt control register                                                                                   | INT1IC         | XX00?0002              |

| 005F16             | INT2 interrupt control register                                                                                   | INT2IC         | XX00?0002              |

| 006016<br>006116   |                                                                                                                   |                |                        |

| 006216             |                                                                                                                   |                |                        |

| 006316             |                                                                                                                   |                |                        |

| 006416             |                                                                                                                   |                |                        |

| 006516             |                                                                                                                   |                |                        |

| 006616             |                                                                                                                   |                |                        |

| 006716             |                                                                                                                   |                |                        |

| 006816             |                                                                                                                   |                |                        |

| 006916             |                                                                                                                   |                |                        |

| 006A16             |                                                                                                                   |                |                        |

| 006B16<br>006C16   |                                                                                                                   |                |                        |

| 006C16             |                                                                                                                   |                |                        |

| 006E16             |                                                                                                                   |                |                        |

| 006F16             |                                                                                                                   |                |                        |

| 007016             |                                                                                                                   |                |                        |

| 007116             |                                                                                                                   |                |                        |

| 007216             |                                                                                                                   |                |                        |

| 007316             |                                                                                                                   |                |                        |

| 007416             |                                                                                                                   |                |                        |

| 007516             |                                                                                                                   |                |                        |

| 007616<br>007716   |                                                                                                                   |                |                        |

| 007716             |                                                                                                                   |                |                        |

| 007816             |                                                                                                                   |                |                        |

| 007916<br>007A16   |                                                                                                                   |                |                        |

| 007B16             |                                                                                                                   |                |                        |

| 007C16             |                                                                                                                   |                |                        |

| 007D16             |                                                                                                                   |                |                        |

| 0075               |                                                                                                                   |                |                        |

| 007E16             |                                                                                                                   |                |                        |

Note :The blank areas are reserved and cannot be used by users.

X : Nothing is mapped to this bit ? : Undefined

| Address         Register         Symbol         After reset           008016         008116         008216         008216         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008316         008 | ~   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 008116 008216 008316 008416 008416 008516 008616                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 008316 008416 008516 008616                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

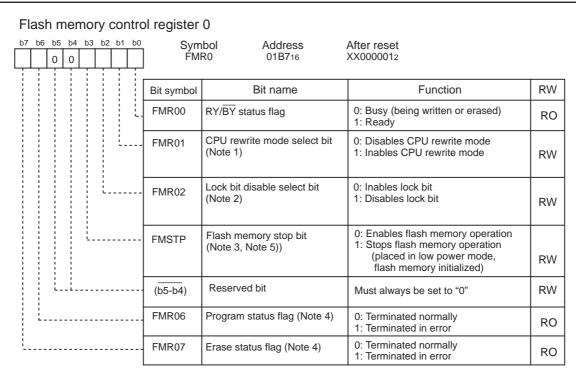

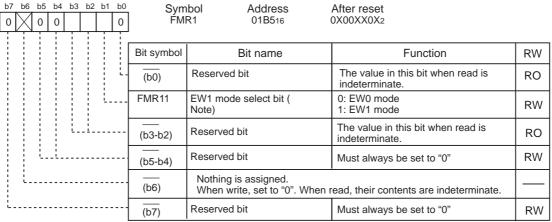

| 008316       008416         008516       008616         ∞       018016         01B116       01B216         01B316       01B316         01B516       Flash memory control register 1       (Note 2)       FMR1       0?00??07         01B616       01B716       Flash memory control register 0       (Note 2)       FMR0       ??000001         01B816       01B916       Address match interrupt register 2       RMAD2       0016         01B916       0016       0016       0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 008516<br>008616   □ 01B016<br>□ 01B116<br>□ 01B216<br>□ 01B216<br>□ 01B316<br>□ 01B316<br>□ 01B516 Flash memory control register 1 (Note 2) FMR1 0?00??0?<br>□ 01B616<br>□ 01B716 Flash memory control register 0 (Note 2) FMR0 ??000001<br>□ 01B816<br>□ 01B916 Address match interrupt register 2 RMAD2 0016<br>□ 01B916                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 018016  018016  018116  018216  018316  018416  018516  Flash memory control register 1 (Note 2) FMR1 0?00??07  018616  018716  Flash memory control register 0 (Note 2) FMR0 ??000001  018816  018916  Address match interrupt register 2 RMAD2 0016  0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 01B016 01B116 01B216 01B316 01B316 01B416 01B516 Flash memory control register 1 01B616 01B716 Flash memory control register 0 01B716 Flash memory control register 0 01B716 RMAD2 0016 0018916                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 01B016       01B116         01B216       01B216         01B316       01B416         01B516       Flash memory control register 1       (Note 2)       FMR1       0?00??07         01B616       01B716       Flash memory control register 0       (Note 2)       FMR0       ??000001         01B816       Address match interrupt register 2       RMAD2       0016         01B916       0016       0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 01B016       01B116         01B216       01B216         01B316       01B416         01B516       Flash memory control register 1       (Note 2)       FMR1       0?00??07         01B616       01B716       Flash memory control register 0       (Note 2)       FMR0       ??000001         01B816       Address match interrupt register 2       RMAD2       0016         01B916       0016       0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 01B116       01B216         01B316       01B316         01B416       01B516         01B516       Flash memory control register 1       (Note 2)       FMR1       0?00??07         01B616       01B716       Flash memory control register 0       (Note 2)       FMR0       ??000001         01B816       Address match interrupt register 2       RMAD2       0016         01B916       0016       0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 01B116       01B216         01B316       01B316         01B416       01B516         01B516       Flash memory control register 1       (Note 2)       FMR1       0?00??07         01B616       01B716       Flash memory control register 0       (Note 2)       FMR0       ??000001         01B816       Address match interrupt register 2       RMAD2       0016         01B916       0016       0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 01B216         01B316           01B316         01B416           01B516         Flash memory control register 1         (Note 2)         FMR1         0?00??0?           01B616         01B716         Flash memory control register 0         (Note 2)         FMR0         ??000001           01B816         Address match interrupt register 2         RMAD2         0016           01B916         0016         0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 01B316         01B416           01B516         Flash memory control register 1         (Note 2)         FMR1         0?00??0?           01B616         01B716         Flash memory control register 0         (Note 2)         FMR0         ??000001           01B816         Address match interrupt register 2         RMAD2         0016           01B916         0016         0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 01B416         01B516         Flash memory control register 1         (Note 2)         FMR1         0?00??07           01B616         01B716         Flash memory control register 0         (Note 2)         FMR0         ??000001           01B816<br>01B916         Address match interrupt register 2         RMAD2         0016<br>0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 01B516         Flash memory control register 1         (Note 2)         FMR1         0?00??07           01B616         01B716         Flash memory control register 0         (Note 2)         FMR0         ??000001           01B816<br>01B916         Address match interrupt register 2         RMAD2         0016<br>0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |