# SANYO Semiconductors **DATA SHEET**

# LV5050V — CMOS IC DC / DC Converter Controller

#### Overview

The LV5050V is a high efficiency DC/DC converter controller IC adopting a synchronous rectifying system. Incorporating numerous functions on a single chip with easy external setting, it can be used for a wide variety of applications. This device is optimal for use in internal power supply systems which are used in electronic devices, LCD-TVs, DVD recorders, etc.

#### **Functions**

- Step-down DC/DC converter controller with 1-channel

- Input UVLO circuit

- Built-in over current detection function

- Built-in soft-start/soft-stop function

- Built-in start-up delay circuit

- Built-in output voltage monitor function (Under voltage protection with power good and timer latch)

- Synchronized operation is possible between different devices.

### **Specifications**

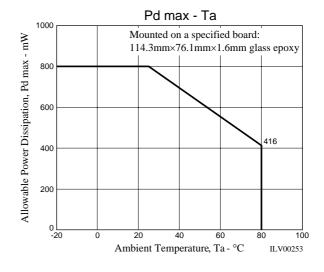

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol          | Conditions | Ratings     | Unit |

|-----------------------------|-----------------|------------|-------------|------|

| Supply voltage              | V <sub>IN</sub> |            | 18          | V    |

| Output peak current         | lout            |            | ±1.0        | Α    |

| Allowable power dissipation | Pd max          | Ta=25°C *1 | 800         | mW   |

| Operating temperature       | Topr            |            | -20 to 85   | °C   |

| Storage temperature         | Tstg            |            | -55 to +150 | °C   |

<sup>\*1:</sup> Board size: 114.3×76.1×1.6mm³, glass epoxy board.

Continued on next page.

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

Continued from preceding page.

| Allowa | Allowable terminal voltage *2 |  |  |           |   |  |  |

|--------|-------------------------------|--|--|-----------|---|--|--|

| 1      | HDRV                          |  |  | 28        | V |  |  |

|        | CBOOT                         |  |  |           |   |  |  |

| 2      | Between                       |  |  | 6.5       | V |  |  |

|        | HDRV, CBOOT and SW            |  |  |           |   |  |  |

| 3      | V <sub>IN</sub> , ILIM, RSNS, |  |  | 18        | V |  |  |

|        | SW, PGOOD                     |  |  |           |   |  |  |

| 4      | VLIN5                         |  |  | 6.5       | V |  |  |

|        | V <sub>DD</sub> , LDRV        |  |  |           |   |  |  |

| 5      | COMP, FB                      |  |  | VLIN5+0.3 | V |  |  |

|        | SS, UV_DELAY                  |  |  |           |   |  |  |

|        | TD, CT                        |  |  |           |   |  |  |

|        | CLKO                          |  |  |           |   |  |  |

<sup>\*2:</sup> The Allowable Terminal Voltage, the SGND+PGND pin becomes a standard except for No.2 of the allowable terminal voltage about No.2 of the allowable terminal voltage, the SW pin becomes a standard.

## Recommended Operating Condition at Ta = 25°C

| Parameter      | Symbol          | Conditions                             | Ratings    | Unit |

|----------------|-----------------|----------------------------------------|------------|------|

| Supply voltage | VIN             | V <sub>IN</sub> and VLIN5 pins opens   | 7.5 to 16  | V    |

| Supply voltage | V <sub>IN</sub> | V <sub>IN</sub> and VLIN5 pins shorted | 4.5 to 6.0 | V    |

## **Electrical Characteristics** at Ta = 25°C, $V_{\mbox{IN}} = 12V$ (Unless especially specified)

| D                                         | 0                   | 0 - 10                             | Ratings |       |       | 11.2 |  |

|-------------------------------------------|---------------------|------------------------------------|---------|-------|-------|------|--|

| Parameter                                 | Symbol              | Conditions                         | min     | typ   | max   | Unit |  |

| System                                    |                     |                                    |         |       |       |      |  |

| Reference voltage for comparing           | V <sub>REF</sub>    |                                    | 0.818   | 0.826 | 0.834 | ٧    |  |

| Supply current 1                          | I <sub>CC</sub> 1   | TD=5V (Except for the Ciss charge) |         | 2     | 4     | mA   |  |

| Supply current 2                          | I <sub>CC</sub> 2   | TD=0V                              | 0.3     | 0.6   | 1.2   | mA   |  |

| 5V supply voltage                         | VLIN5               | I <sub>VIN</sub> 5=0 to 10mA       | 4.75    | 5.00  | 5.25  | ٧    |  |

| Over-current sense comparator offset      | V <sub>CL</sub> OS  |                                    | -5      |       | +5    | mV   |  |

| Over-current sense reference current      | lCL                 | V <sub>IN</sub> =10 to 14V         | 7.47    | 8.30  | 9.13  | μА   |  |

| source                                    |                     |                                    |         |       |       |      |  |

| Soft start source current                 | I <sub>SS</sub> SC  | TD=5V                              | -1.8    | -3.5  | -7.0  | μΑ   |  |

| Soft start sink current                   | I <sub>SS</sub> SK  | TD=0V                              | 0.5     | 2.0   |       | mA   |  |

| Soft start clamp voltage                  | V <sub>SS</sub> T0  |                                    | 1.2     | 1.6   | 2.0   | V    |  |

| UV_DELAY source current                   | I <sub>SC</sub> UVD | UV_DELAY=2V                        | -4.3    | -8.6  | -17.2 | μΑ   |  |

| UV_DELAY sink current                     | I <sub>SK</sub> UVD | UV_DELAY=2V                        | 0.5     | 2     |       | mA   |  |

| UV_DELAY threshold voltage                | VUVD                |                                    | 1.5     | 2.4   | 3.5   | V    |  |

| UV_DELAY operating voltage                | VUVP                | 100%=V <sub>REF</sub>              | 87      | 92    | 97    | %    |  |

| VUVP detection hysteresis                 | ΔVUVP               |                                    |         | 1.5   |       | %    |  |

| Output discharge transistor ON resistance | V <sub>SW</sub> ON  |                                    | 5       | 10    | 20    | Ω    |  |

| Output part                               |                     |                                    |         |       |       |      |  |

| CBOOT leakage current                     | ICBOOT              | VCBOOT=VSW+6.5V                    |         |       | 10    | μА   |  |

| HDRV LDRV source current                  | I <sub>SC</sub> DRV |                                    |         | 1.0   |       | Α    |  |

| HDRV LDRV sink current                    | I <sub>SK</sub> DRV |                                    |         | 1.0   |       | Α    |  |

| HDRV lower ON resistance                  | R <sub>H</sub> DRV  |                                    |         | 1.5   |       | Ω    |  |

| LDRV lower ON resistance                  | R <sub>L</sub> DRV  |                                    |         | 1.5   |       | Ω    |  |

| Synchronous ON prevention dead time 1     | T <sub>dead</sub> 1 | LDRV OFF→HDRV ON                   |         | 70    |       | ns   |  |

| Synchronous ON prevention dead time 2     | T <sub>dead</sub> 2 | HDRV OFF→LDRV ON                   |         | 120   |       | ns   |  |

Continued on next page.

Continued from preceding page.

| 5                                     | 0                     | Sumbal Conditions                                   | Ratings  |      |          | 11.2 |  |

|---------------------------------------|-----------------------|-----------------------------------------------------|----------|------|----------|------|--|

| Parameter                             | Symbol                | Conditions                                          | min      | typ  | max      | Unit |  |

| Oscillator                            |                       |                                                     |          |      |          |      |  |

| Oscillation freaquency                | f <sub>osc</sub>      | CT=130pF                                            | 280      | 330  | 380      | kHz  |  |

| Oscillation frequency range           | f <sub>osc</sub> op   |                                                     | 250      |      | 1100     | kHz  |  |

| Maximum ON duty                       | D <sub>ON</sub> max   | CT=130pF                                            | 83       |      |          | %    |  |

| Minimum ON time                       | T <sub>ON</sub> min   | CT=130pF                                            |          | 100  |          | ns   |  |

| Upper-side voltage saw- tooth wave    | V <sub>saw</sub> H    | f <sub>OSC</sub> =300kHz                            |          | 2    | 2.6      | V    |  |

| Lower-side voltage saw-tooth wave     | V <sub>saw</sub> L    | f <sub>OSC</sub> =300kHz                            |          | 1    | 1.2      | V    |  |

| Error Amplifier                       |                       |                                                     |          |      |          |      |  |

| Error amplifier input current         | IFB                   |                                                     | -200     | -100 | 200      | nA   |  |

| COMP pin source current               | I <sub>COMP</sub> SC  |                                                     |          | -100 | -18      | μА   |  |

| COMP pin sink current                 | I <sub>COMP</sub> SK  |                                                     | 18       | 100  |          | μА   |  |

| Error amplifier gm                    | gm                    |                                                     | 500      | 700  | 900      | umho |  |

| Logic output                          | •                     |                                                     |          |      | •        |      |  |

| Power Good low level source current   | I <sub>pwrgd</sub> L  | V <sub>PGOOD</sub> =0.4V                            | 0.5      | 1.0  |          | mA   |  |

| Power Good high level leakage current | I <sub>pwrgd</sub> H  | V <sub>PGOOD</sub> =12V                             |          |      | 10       | μА   |  |

| TP pin threshold voltage              | V <sub>ON</sub> TD    | When the voltage of the TD pin rises                | 1.5      | 2.4  | 3.5      | V    |  |

| TP pin high impedance voltage         | V <sub>TD</sub> H     | When V <sub>IN</sub> and VLIN5 pins are set to open | 4.5      | 5.0  | 5.5      | V    |  |

| TD pin charge source current          | I <sub>TD</sub> SC    |                                                     | -1.8     | -3.5 | -7.0     | μА   |  |

| TD pin discharge sink current         | I <sub>TD</sub> SK    |                                                     | 0.2      | 1.0  |          | mA   |  |

| CLKO high level voltage               | VCLKOH                | I <sub>CLK</sub> 10=1mA                             | 0.7V5LIN |      |          | V    |  |

| CLKO low level voltage                | V <sub>CLKO</sub> L   | I <sub>CLK</sub> 10=1mA                             |          |      | 0.3V5LIN | V    |  |

| Protection function                   | Protection function   |                                                     |          |      |          |      |  |

| V <sub>IN</sub> UVLO Release voltage  | V <sub>UVLO</sub>     |                                                     | 3.5      | 4.1  | 4.3      | mA   |  |

| UVLO Hysteresis                       | $\Delta V_{\sf UVLO}$ |                                                     |          | 0.4  |          | μА   |  |

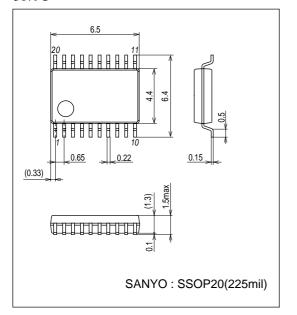

## **Package Dimensions**

unit : mm (typ) 3179C

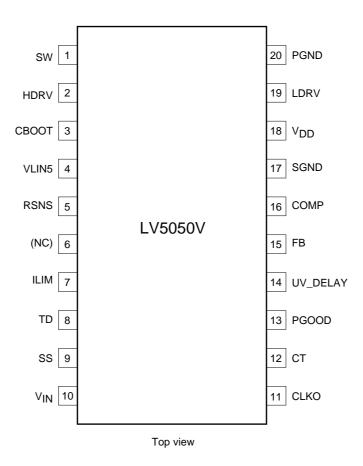

# Pin Assignment

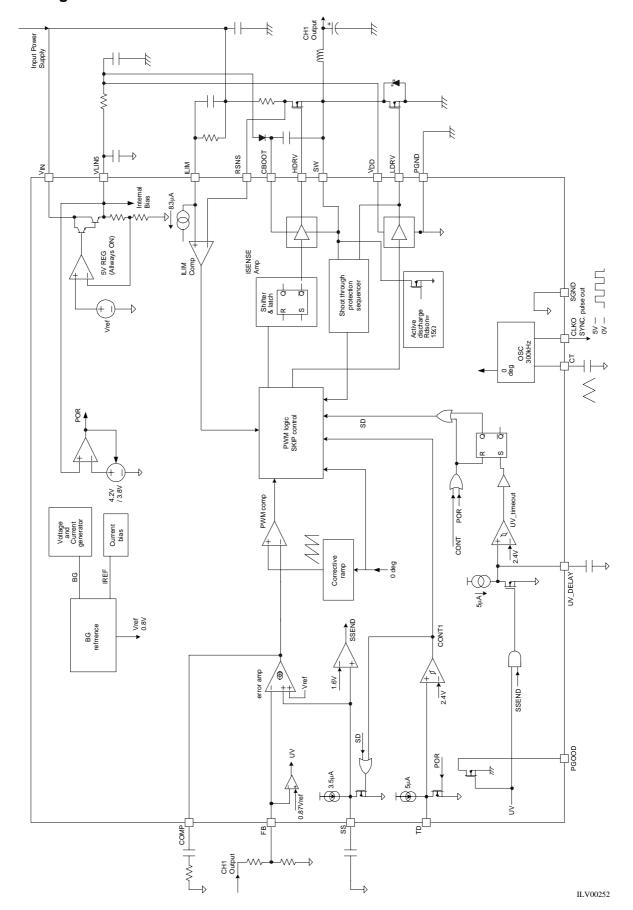

# **Block Diagram**

## **Pin Functions**

| Pin No. | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | sw       | This Pin is connected with the switching node. A source of an external upper side MOSFET and a drain of an external lower side MOSFET are connected with this pin. This pin becomes the return current path of the HDRV pin. This pin is connected with a transistor drain of the discharge MOSFET for SOFT STOP in the IC (typical $15\Omega$ ). Also, this pin has the signal output part for the short through prevention of both the upper and lower MOSFETs.  When this terminal voltage becomes 1V or less for PGND, the LDRV pin is turned on.           |

| 2       | HDRV     | The gate drive pin for an external upper side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | СВООТ    | The bootstrap capacity connection pin. The gate drive power of upper MOSFET is provided by this pin.  This pin is connected to the V <sub>DD</sub> pin through a diode and is connected to the SW pin through the bootstrap capacity.                                                                                                                                                                                                                                                                                                                           |

| 4       | VLIN5    | The output pin of an internal regulator of 5V. the current is provided by the VIN pin.  Also, power supply of the control circuit in the IC is provided by this pin.  Connect an output capacitor of 4.7µF between this pin and SGND.  A regulator of 5V operates, even if the IC is in the standby state.  This pin is monitored by an UVLO function and the IC starts by the voltage of 4.0V or more (the IC is off by the voltage of 3.8V or less.)                                                                                                          |

| 5       | RSNS     | The input pin of the over current detection comparator / the current detection amplifier  To detect resistance, this pin is connected to the under side of a resistor for the current detection between the V <sub>IN</sub> pin and the DRAIN of the upper MOSFET. Also, to use the ON resistance of MOSFET for the current detection, connect this pin to the SOURCE of the upper MOSFET. To prevent the common impedance of main current to the detection-voltage, this pin is connected by independent wiring.                                               |

| 6       | NC       | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7       | ILIM     | The pin to set the trip point for over current detection. Since the SINK current source of $8.3\mu A$ (ILIM) is connected in the IC, the over-current detection voltage (ILIM $\times$ RLIM) is generated by connecting a resistor RLIM between this pin and the V <sub>IN</sub> pin. The over-current is detected by comparing the voltage between the V <sub>IN</sub> pin and the ILIM pin to the current detection resistance RSNS or both end voltage of the upper MOSFET.                                                                                  |

| 8       | TD       | Start-up delay pin.  The time until the IC starts after releasing POR is set by connecting a capacitor between this pin and SGND.  After releasing POR, an external capacitor is charged up by the constant current source of 3.5µA in the IC. When this terminal voltage becomes 2.4V or more, The IC starts. Also, when this terminal voltage becomes 2.4V or less, The IC becomes the standby state. If external capacitor is not connected, the IC instantly starts after releasing POR.                                                                    |

| 9       | ss       | The pin to connect a capacitor for soft start. After releasing POR, when the voltage of the TD pin becomes 2.4V or more, the SS pin is charged by an internal constant current source of 3.5µA.  Since this pin is connected to the positive input of the transformer conductance amplifier, the ramp-up wave form of the SS pin becomes the ramp-up wave form of the output.  During POR operations and after the UV_DELAY time-out, the SS pin is discharged                                                                                                  |

| 10      | VIN      | Power supply pin of the IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11      | CLKO     | The clock output pin. The clock that synchronized to the oscillation waveform of the CT pin is output. To synchronize two or more LV5050Vs, the CLKO pin of the device that becomes a master is connected to the CT pin of the device that becomes a slave. When two or more the devices are synchronized and the start-up timing is changed by using the Td pin between each device, the earliest start-up device is determined as the master.                                                                                                                 |

| 12      | СТ       | The pin to connect an external capacitor for the oscillator. Connect a capacitor between this pin and SGND. When a capacitor of 130pF is connected between this pin and GND, the oscillation frequency can be set up by 330kHz. Also, this pin is applied by an external clock signal.  The PWM operation is performed by the frequency of applied clock signal.  When an external clock signal is applied, the rectangular wave of 0V in low level and from 3.3V to 5V in high level is applied. The rectangular wave source needs the fan-out of 1mA or more. |

| 13      | PGOOD    | The power good pin. The open drain MOSFET of the withstand of 28V is connected in the IC.  When the output voltage of channel 1 is less than -13% for the setup voltage, the low level is output.  This pin has hysteresis of about (VREF × 1.5%).                                                                                                                                                                                                                                                                                                              |

Continued on next page.

Continued from preceding page.

| Pin No.     | Pin name | Description                                                                                                |

|-------------|----------|------------------------------------------------------------------------------------------------------------|

| 14 UV_DELAY |          | UVP DELAY pin                                                                                              |

|             |          | By connecting a capacitor between this pin and SGND, the time until the IC latches off after detecting the |

|             |          | UVP state can be set. Also, after channel 1 terminated the soft-start function, when the output voltage    |

|             |          | becomes -80% or less for the setup voltage, an external capacitor is charged by the constant current       |

|             |          | source of 8.6μA in the IC.                                                                                 |

|             |          | When this terminal voltage becomes 2.4V or more, the IC is latched off.                                    |

|             |          | If an external capacitor is not connected, the IC is instantly latched off after detecting the UVP state.  |

|             |          | Also, when this pin is shorted to GND, the UV_DELAY function is not operated.                              |

| 15          | FB       | Feed back input pin. The minus terminal (-) of the trans conductance amplifier is connected.               |

|             |          | The voltage generated when the output voltage was divided by a resistor is input into this pin.            |

|             |          | The converter operates so that this pin becomes an internal reference voltage (V <sub>REF</sub> =0.836V).  |

|             |          | Also, this pin is monitored by the comparators UVP and OVP.                                                |

|             |          | When the voltage of this pin becomes less than 87% of the set voltage, the PGOOD pin is low level.         |

|             |          | A timer of the UV_DELAY function operates. Also, when the voltage of this pin becomes more than 117% of    |

|             |          | the set voltage, the IC latches off.                                                                       |

| 16          | COMP     | The pin to connect a capacitor and a resistor for phase compensation.                                      |

|             |          | The output of an internal transformer conductance amplifier is connected.                                  |

|             |          | Connect an external phase compensation circuit between this pin and SGND.                                  |

| 17          | SGND     | The system ground of the IC. The reference voltage is generated based on this pin.                         |

|             |          | This pin is connected to the power supply system ground.                                                   |

| 18          | $V_{DD}$ | Power supply pin for the gate drive of an external lower-side MOSFET.                                      |

|             |          | This pin is connected to the VLIN5 pin through a filter.                                                   |

| 19          | LDRV     | The gate drive pin of an external lower-side MOSFET.                                                       |

|             |          | This pin has the signal input part for prevention of short-through of both the upper and lower MOSFETs.    |

|             |          | When the voltage of this pin becomes less than 1V, the HDRV pin is turned on.                              |

| 20          | PGND     | Power ground pin. This pin becomes the return current path of the LDRV pin.                                |

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 2006. Specifications and information herein are subject to change without notice.