# Section I. HardCopy III Device Datasheet

This section provides the datasheet for the HardCopy® III device family. This section includes the following chapter:

■ Chapter 1, DC and Switching Characteristics of HardCopy III Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook.

# 1. DC and Switching Characteristics of HardCopy III Devices

HIII53001-2.0

## **Electrical Characteristics**

This chapter provides information about the absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for HardCopy® III devices. HardCopy III devices are offered in both commercial and industrial grades.

## **Operating Conditions**

When HardCopy III devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability, you must consider the operating requirements described in this chapter. HardCopy III devices are not speed binned like Stratix® III devices because HardCopy III devices are designed and built to function at a target frequency based on timing constraints, and operate at either commercial or industrial temperatures.

## **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for HardCopy III devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied by these conditions. Conditions beyond those listed in Table 1–1 can cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time can have adverse effects on the device.

**Table 1–1.** HardCopy III Device Absolute Maximum Ratings – Preliminary (Part 1 of 2) (Note 1)

| Symbol                 | Parameter                                                              | Minimum         | Maximum | Unit |

|------------------------|------------------------------------------------------------------------|-----------------|---------|------|

| V <sub>CCL</sub>       | Core voltage power supply                                              | -0.5            | 1.35    | V    |

| V <sub>cc</sub>        | I/O registers power supply                                             | -0.5            | 1.35    | V    |

| V <sub>CCD_PLL</sub>   | PLL digital power supply                                               | -0.5            | 1.35    | V    |

| V <sub>CCA_PLL</sub>   | PLL analog power supply                                                | -0.5            | 3.75    | V    |

| V <sub>CCPT</sub> (2)  | Power supply for the temperature sensing diode                         | -0.5            | 3.75    | V    |

| V <sub>CCPGM</sub>     | Configuration pins power supply                                        | -0.5            | 3.9     | V    |

| V <sub>CCPD</sub>      | I/O pre-driver power supply                                            | -0.5            | 3.9     | V    |

| V <sub>CCIO</sub>      | I/O power supply                                                       | -0.5            | 3.9     | V    |

| V <sub>CC_CLKIN</sub>  | Differential clock input power supply (top and bottom I/O banks only)  | -0.5            | 3.75    | V    |

| V <sub>CCBAT</sub> (3) | Battery back-up power supply for design security volatile key register | _               | _       | V    |

| Vi                     | DC input voltage                                                       | -0.5            | 4.0     | V    |

| T <sub>J</sub>         | Operating junction temperature                                         | <del>-</del> 55 | 125     | °C   |

| I <sub>оит</sub>       | DC output current, per pin                                             | -25             | 40      | mA   |

**Table 1–1.** HardCopy III Device Absolute Maximum Ratings – Preliminary (Part 2 of 2) (Note 1)

| Symbol           | Parameter                     | Minimum | Maximum | Unit |

|------------------|-------------------------------|---------|---------|------|

| T <sub>STG</sub> | Storage temperature (no bias) | -65     | 150     | °C   |

#### Notes to Table 1-1:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins and not the power supply.

- (2) In Stratix III devices, this power supply is also used for programmable power technology.

- (3) In HardCopy III devices, this power supply is not used.

### **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 1-2 and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

Table 1–2 lists the maximum allowed input overshoot voltage. The maximum allowed overshoot duration is specified as the percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

Table 1-2. Maximum Allowed Overshoot During Transitions – Preliminary

| Symbol   | Parameter                               | Condition | Overshoot<br>Duration as % of<br>High Time | Unit |

|----------|-----------------------------------------|-----------|--------------------------------------------|------|

|          |                                         | 4         | 100.000                                    | %    |

|          |                                         | 4.05      | 79.330                                     | %    |

|          |                                         | 4.1       | 46.270                                     | %    |

|          |                                         | 4.15      | 27.030                                     | %    |

|          |                                         | 4.2       | 15.800                                     | %    |

|          |                                         | 4.25      | 9.240                                      | %    |

|          |                                         | 4.3       | 5.410                                      | %    |

|          |                                         | 4.35      | 3.160                                      | %    |

| \(; (AO) | A O I I I I I I I I I I I I I I I I I I | 4.4       | 1.850                                      | %    |

| Vi (AC)  | AC Input Voltage                        | 4.45      | 1.080                                      | %    |

|          |                                         | 4.5       | 0.630                                      | %    |

|          |                                         | 4.55      | 0.370                                      | %    |

|          |                                         | 4.6       | 0.220                                      | %    |

|          |                                         | 4.65      | 0.130                                      | %    |

|          |                                         | 4.7       | 0.074                                      | %    |

|          |                                         | 4.75      | 0.043                                      | %    |

|          |                                         | 4.8       | 0.025                                      | %    |

|          |                                         | 4.85      | 0.015                                      | %    |

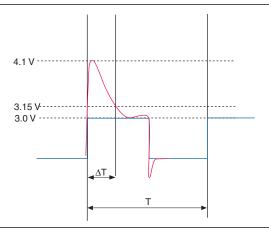

Figure 1–1 shows the methodology to determine the overshoot duration. The overshoot voltage is displayed in red and is present at the HardCopy III pin, up to 4.1 V. From Table 1–2, for an overshoot of up to 4.1 V, the percentage of high time for overshoot > 3.15 V can be as high as 46% over an 11.4 year period. The percentage of high-time is calculated as (delta T/T)  $\times$  100. This 11.4 year period assumes the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal. For lower I/O toggle rates and situations where the device is in an idle state, lifetimes are increased.

Figure 1-1. Overshoot Duration

## **Recommended Operating Conditions**

This section lists the functional operation limits for AC and DC parameters for HardCopy III devices. The steady-state voltage and current values expected from HardCopy III devices are provided in Table 1–3. All supplies are required to monotonically reach their full-rail values within  $t_{\text{RAMP}}$  maximum. Allowed ripple on power supplies is bounded by the minimum and maximum specifications listed in Table 1–3.

Table 1-3. HardCopy III Device Recommended Operating Conditions – Preliminary (Part 1 of 2)

| Symbol                   | Parameter                                                      | Conditions | Minimum | Typical | Maximum | Unit |

|--------------------------|----------------------------------------------------------------|------------|---------|---------|---------|------|

| V <sub>CCL</sub> (1)     | Core voltage power supply for internal logic and input buffers |            | 0.87    | 0.9     | 0.93    | V    |

| V <sub>cc</sub> (1)      | I/O registers power supply                                     | _          | 0.87    | 0.9     | 0.93    | V    |

| V <sub>CCD_PLL</sub> (1) | PLL digital power supply                                       | _          | 0.87    | 0.9     | 0.93    | V    |

| V <sub>CCA_PLL</sub>     | PLL analog power supply                                        | _          | 2.375   | 2.5     | 2.625   | V    |

| V <sub>CCPT</sub> (2)    | Power supply for the temperature sensing diode                 | _          | 2.375   | 2.5     | 2.625   | V    |

|                          | Configuration pins power supply, 3.0 V                         | —          | 2.85    | 3.0     | 3.15    | V    |

| V <sub>CCPGM</sub>       | Configuration pins power supply, 2.5 V                         |            | 2.375   | 2.5     | 2.625   | V    |

|                          | Configuration pins power supply, 1.8 V                         | _          | 1.71    | 1.8     | 1.89    | V    |

| Symbol                 | Parameter                                                              | Conditions               | Minimum | Typical | Maximum           | Unit |

|------------------------|------------------------------------------------------------------------|--------------------------|---------|---------|-------------------|------|

| V (2)                  | I/O pre-driver power supply, 3.0 V                                     | _                        | 2.85    | 3.0     | 3.15              | V    |

| V <sub>CCPD</sub> (3)  | I/O pre-driver power supply, 2.5 V                                     | _                        | 2.375   | 2.5     | 2.625             | V    |

|                        | I/O power supply, 3.0 V                                                | _                        | 2.85    | 3.0     | 3.15              | V    |

|                        | I/O power supply, 2.5 V                                                | _                        | 2.375   | 2.5     | 2.625             | V    |

| $V_{CCIO}$             | I/O power supply, 1.8 V                                                | _                        | 1.71    | 1.8     | 1.89              | V    |

|                        | I/O power supply, 1.5 V                                                | _                        | 1.425   | 1.5     | 1.575             | V    |

|                        | I/O power supply, 1.2 V                                                | _                        | 1.14    | 1.2     | 1.26              | V    |

| V <sub>CC_CLKIN</sub>  | Differential clock input power supply (top and bottom I/O banks only)  | _                        | 2.375   | 2.5     | 2.625             | V    |

| V <sub>CCBAT</sub> (4) | Battery back-up power supply for design security volatile key register | _                        | _       | _       | _                 | V    |

| Vı                     | DC input voltage                                                       | _                        | -0.3    | _       | 3.6               | V    |

| $V_0$                  | Output voltage                                                         | _                        | 0       | _       | V <sub>ccio</sub> | V    |

| Τ <sub>J</sub>         | Operating junction temperature                                         | For commercial use       | 0       | _       | 85                | °C   |

| • J                    |                                                                        | For industrial use       | -40     | _       | 100               | °C   |

| +                      | Power supply rame time                                                 | Normal POR<br>(PORSEL=0) | 50 μs   | _       | 300 ms            | _    |

| t <sub>ramp</sub>      | Power supply ramp time                                                 | Fast POR<br>(PORSEL=1)   | 50 μs   | _       | 12 ms             | _    |

**Table 1–3.** HardCopy III Device Recommended Operating Conditions – Preliminary (Part 2 of 2)

#### Notes to Table 1-3:

- (1) In Stratix III devices,  $V_{CCL}$  can also be 1.1 V, while  $V_{CCD}$  and  $V_{CCD\_PLL}$  are 1.1 V. In HardCopy III devices, all three supplies are 0.9 V.

- (2) In Stratix III devices, this power supply is also used for programmable power technology.

- (3)  $V_{CCPD}$  is either 2.5 V or 3.0 V. For a 3.0-V I/O standard,  $V_{CCPD} = 3.0$  V. For a 2.5 V or lower I/O standard,  $V_{CCPD} = 2.5$  V.

- (4) In HardCopy III devices, this power supply is not used.

#### **DC Characteristics**

This section lists the input pin capacitances, on-chip termination tolerance, and hot socketing specifications.

## **Supply Current**

Standby current is the current the device draws after the device enters user mode with no inputs/outputs toggling and no activity in the device. Since these currents vary largely with the resources used, use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design.

Table 1–4 lists supply current specifications for  $V_{CC\_CLKIN}$  and  $V_{CCPGM}$ . Use the EPE to get supply current estimates for the remaining power supplies.

**Table 1–4.** Supply Current Specifications for  $V_{CC}$  CLKIN and  $V_{CCPGM}$  – Preliminary (*Note 1*)

| Symbol             | Parameter                                    | Min | Max | Unit |

|--------------------|----------------------------------------------|-----|-----|------|

| I <sub>CLKIN</sub> | V <sub>CC_CLKIN</sub> current specifications | 0   | TBD | mA   |

| I <sub>PGM</sub>   | V <sub>CCPGM</sub> current specifications    | 0   | TBD | mA   |

#### Note to Table 1-4:

(1) Pending silicon characterization.

#### I/O Pin Leakage Current

Table 1–5 defines HardCopy III I/O pin leakage current specifications.

**Table 1–5.** HardCopy III I/O Pin Leakage Current – Preliminary (*Note 1*), (2)

| Symbol          | Parameter                          | Conditions                                   | Min | Тур | Max | Unit |

|-----------------|------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I,              | Input pin leakage current          | V <sub>I</sub> = V <sub>CCIOMAX</sub> to 0 V | -10 | _   | 10  | μΑ   |

| l <sub>oz</sub> | Tri-stated I/O pin leakage current | V <sub>0</sub> = V <sub>CCIOMAX</sub> to 0 V | -10 | _   | 10  | μА   |

#### Notes To Table 1-5:

- (1) This value is specified for normal device operation. The value may vary during power up. This applies for all  $V_{\text{CCIO}}$  settings (3.0, 2.5, 1.8, 1.5, and 1.2 V).

- (2) The 10 mA I/O leakage current limit is applicable when the internal clamping diode is off. A higher current is observed when the diode is on.

## **On-Chip Termination (OCT) Specifications**

If OCT calibration is enabled, calibration is automatically performed at power up for I/Os connected to the calibration block. Table 1–6 lists the HardCopy III OCT calibration block accuracy specifications.

Table 1–6. HardCopy III On-Chip Termination Calibration Accuracy Specifications – Preliminary (Part 1 of 2) (Note 1)

|                             |                                                                       |                               | Calibration Accuracy |            |      |

|-----------------------------|-----------------------------------------------------------------------|-------------------------------|----------------------|------------|------|

| Symbol                      | Description                                                           | Conditions                    | Commercial (2)       | Industrial | Unit |

| 25–Ω R <sub>s</sub> 3.0/2.5 | Internal series termination with calibration (25- $\Omega$ setting)   | V <sub>cc10</sub> = 3.0/2.5 V | TBD                  | _          | %    |

| 50–Ω R <sub>s</sub> 3.0/2.5 | Internal series termination with calibration (50- $\Omega$ setting)   | V <sub>CCIO</sub> = 3.0/2.5 V | TBD                  | _          | %    |

| 50–Ω R <sub>T</sub> 2.5     | Internal parallel termination with calibration (50- $\Omega$ setting) | V <sub>ccio</sub> = 2.5 V     | TBD                  | _          | %    |

| 25–Ω R <sub>s</sub> 1.8     | Internal series termination with calibration (25- $\Omega$ setting)   | V <sub>ccio</sub> = 1.8 V     | TBD                  | _          | %    |

| 50–Ω R <sub>s</sub> 1.8     | Internal series termination with calibration (50- $\Omega$ setting)   | V <sub>ccio</sub> = 1.8 V     | TBD                  | _          | %    |

| 50–Ω R <sub>T</sub> 1.8     | Internal parallel termination with calibration (50- $\Omega$ setting) | V <sub>ccio</sub> = 1.8 V     | TBD                  | _          | %    |

| 50–Ω R <sub>s</sub> 1.5     | Internal series termination with calibration (50- $\Omega$ setting)   | V <sub>ccio</sub> = 1.5 V     | TBD                  | _          | %    |

|                         |                                                                              |                           | Calibration Accuracy |            |      |

|-------------------------|------------------------------------------------------------------------------|---------------------------|----------------------|------------|------|

| Symbol                  | Description                                                                  | Conditions                | Commercial (2)       | Industrial | Unit |

| 50–Ω R <sub>τ</sub> 1.5 | Internal parallel termination with calibration (50- $\Omega$ setting)        | V <sub>ccio</sub> = 1.5 V | TBD                  | _          | %    |

| 50–Ω R <sub>s</sub> 1.2 | Internal series termination with calibration (50- $\Omega$ setting)          | V <sub>ccio</sub> = 1.2 V | TBD                  | _          | %    |

| 50–Ω R <sub>τ</sub> 1.2 | Internal parallel termination with calibration $(50-\Omega \text{ setting})$ | V <sub>CCIO</sub> = 1.2 V | TBD                  | _          | %    |

Table 1–6. HardCopy III On-Chip Termination Calibration Accuracy Specifications – Preliminary (Part 2 of 2) (Note 1)

#### Notes to Table 1-6

- (1) OCT calibration accuracy is valid at the time of calibration only.

- (2) Pending silicon characterization.

The accuracy listed in Table 1–6 is valid at the time of calibration. If the voltage or temperature changes, the termination resistance value varies. Table 1–7 lists the resistance tolerance for HardCopy III on-chip termination.

**Table 1–7.** On-Chip Termination Resistance Tolerance Specification for I/Os – Preliminary (Note 1)

|                        |                                                 | Resistance Tolerance |                |      |

|------------------------|-------------------------------------------------|----------------------|----------------|------|

| Symbol                 | Description                                     | Commercial Max       | Industrial Max | Unit |

| R <sub>OCT_UNCAL</sub> | Internal series termination without calibration | TBD                  | _              | %    |

| R <sub>OCT_CAL</sub>   | Internal series termination with calibration    | (2)                  | _              | %    |

#### Notes to Table 1-7:

- (1) Pending silicon characterization.

- (2) For resistance tolerance after power-up calibration, refer to Table 1–8.

Table 1–8 lists OCT variation with temperature and voltage after power-up calibration. Use Table 1–8 and Equation 1–1 to determine OCT variation without re-calibration.

#### Equation 1-1.

$$R_{OCT} = \ R_{CAL} \bigg( 1 + \frac{dR}{dT} \times \Delta T + \frac{dR}{dV} \times \Delta V \bigg)$$

Note that  $R_{\text{CAL}}$  is calibrated on-chip termination at power-up.  $\Delta T$  and  $\Delta V$  are variations in temperature and voltage ( $V_{\text{CCIO}}$ ) at power-up.

| Symbol | Description                                           | V <sub>ccio</sub> (V) | Commercial<br>Typical | Unit |

|--------|-------------------------------------------------------|-----------------------|-----------------------|------|

|        |                                                       | 3.0                   | TBD                   | %/mV |

|        | 00T                                                   | 2.5                   | TBD                   | %/mV |

| dR/dV  | OCT variation with voltage without re-calibration     | 1.8                   | TBD                   | %/mV |

|        |                                                       | 1.5                   | TBD                   | %/mV |

|        |                                                       | 1.2                   | TBD                   | %/mV |

|        |                                                       | 3.0                   | TBD                   | %/°C |

|        |                                                       | 2.5                   | TBD                   | %/°C |

| dR/dT  | OCT variation with temperature without re-calibration | 1.8                   | TBD                   | %/°C |

|        | To danstation                                         | 1.5                   | TBD                   | %/°C |

|        |                                                       | 1.2                   | TBD                   | %/°C |

**Table 1–8.** On-Chip Termination Variation after Power-up Calibration – Preliminary (Note 1), (2)

#### Note to Table 1-8:

- (1) Valid for  $V_{\text{CCIO}}$  range of  $\pm$  5% and temperature range of 0° to 85° C.

- (2) Pending silicon characterization.

## Pin Capacitance

Table 1–9 shows the HardCopy III device family pin capacitance.

**Table 1–9.** HardCopy III Device Capacitance – Preliminary (*Note 1*)

| Symbol                                                                             | Parameter                                                        | Typical | Unit |

|------------------------------------------------------------------------------------|------------------------------------------------------------------|---------|------|

| С <sub>іотв</sub>                                                                  | Input capacitance on top and bottom I/O pins                     | TBD     | pF   |

| C <sub>IOLR</sub>                                                                  | Input capacitance on left and right I/O pins                     | TBD     | pF   |

| Сськтв                                                                             | Input capacitance on top and bottom dedicated clock input pins   | TBD     | pF   |

| C <sub>CLKLR</sub>                                                                 | Input capacitance on left and right dedicated clock input pins   | TBD     | pF   |

| $C_{outfb}$                                                                        | Input capacitance on dual-purpose clock output and feedback pins | TBD     | pF   |

| C <sub>CLK1</sub> , C <sub>CLK3</sub> , C <sub>CLK8</sub> , and C <sub>CLK10</sub> | Input capacitance for dedicated clock input pins                 | TBD     | pF   |

### Note to Table 1-9:

(1) Pending silicon characterization.

### **Hot Socketing**

Table 1–10 lists the hot socketing specifications for HardCopy III devices.

**Table 1–10.** HardCopy III Hot Socketing Specifications – Preliminary (Note 1)

| Symbol                 | Parameter              | Maximum          |

|------------------------|------------------------|------------------|

| I <sub>IOPIN(DC)</sub> | DC current per I/O pin | 300 μΑ           |

| I <sub>IOPIN(AC)</sub> | AC current per I/O pin | 8 mA for ≤ 10 ns |

#### Note to Table 1-10:

(1) Pending silicon characterization.

### Internal Weak Pull-Up Resistor

Table 1–11 lists the weak pull-up resistor values for HardCopy III devices.

**Table 1–11.** HardCopy III Internal Weak Pull-Up Resistor – Preliminary (Note 1), (2)

| Symbol          | Parameter                                                              | Conditions                             | Min | Тур | Max | Unit |

|-----------------|------------------------------------------------------------------------|----------------------------------------|-----|-----|-----|------|

|                 |                                                                        | $V_{CCIO} = 3.0 \text{ V} \pm 5\% (3)$ | _   | 25  | _   | kΩ   |

|                 | Value of I/O pin pull-up resistor                                      | $V_{CCIO} = 2.5 \text{ V} \pm 5\% (3)$ | _   | 25  | _   | kΩ   |

| $R_{\text{PU}}$ | before and during user mode, if the pull-up resistor option is enabled | $V_{CCIO} = 1.8 \text{ V} \pm 5\% (3)$ | _   | 25  | _   | kΩ   |

|                 | pun-up resistor option is enabled                                      | $V_{CCIO} = 1.5 \text{ V} \pm 5\% (3)$ | _   | 25  | _   | kΩ   |

|                 |                                                                        | $V_{CCIO} = 1.2 \text{ V} \pm 5\% (3)$ | _   | 25  | _   | kΩ   |

#### Notes to Table 1-11:

- (1) Pending silicon characterization.

- (2) All I/O pins have an option to enable weak pull-up except test and JTAG pins.

- (3) Pin pull-up resistance values may be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

## I/O Standard Specifications

Table 1–12 through Table 1–17 list input voltage sensitivities ( $V_{\rm IH}$  and  $V_{\rm IL}$ ), output voltage ( $V_{\rm OH}$  and  $V_{\rm OL}$ ), and current drive characteristics ( $I_{\rm OH}$  and  $I_{\rm OL}$ ) for all I/O standards supported by HardCopy III devices. Refer to Table 1–33 on page 1–21 for an explanation of terms used in Table 1–12 through Table 1–17.  $V_{\rm OL}$  and  $V_{\rm OH}$  values are valid at the corresponding  $I_{\rm OL}$  and  $I_{\rm OH}$ , respectively.

**Table 1–12.** Single-Ended I/O Standards Specifications — Preliminary

|                        |       | V <sub>cc io</sub> (V) |       | V <sub>IL</sub> | (V)                        | V <sub>IH</sub>             | (V)                     | <b>V</b> <sub>0L</sub> ( <b>V</b> ) | V <sub>OH</sub> (V)         |          |                      |

|------------------------|-------|------------------------|-------|-----------------|----------------------------|-----------------------------|-------------------------|-------------------------------------|-----------------------------|----------|----------------------|

| I/O Standard           | Min   | Тур                    | Max   | Min             | Max                        | Min                         | Max                     | Max                                 | Min                         | I₀. (mA) | I <sub>OH</sub> (mA) |

| 3.0-V LVTTL            | 2.85  | 3                      | 3.15  | -0.3            | 0.8                        | 1.7                         | 3.6                     | 0.4                                 | 2.4                         | 2        | -2                   |

| 3.0-V<br>LVCMOS        | 2.85  | 3                      | 3.15  | -0.3            | 0.8                        | 1.7                         | 3.6                     | 0.2                                 | V <sub>cc10</sub> - 0.2     | 0.1      | -0.1                 |

| 0.57/17/17/1           | 2.375 | 2.5                    | 2.625 | -0.3            | 0.7                        | 1.7                         | 3.6                     | 0.2                                 | 2.1                         | 0.1      | -0.1                 |

| 2.5V LVTTL/<br>LVCMOS  |       | 2.5                    | 2.625 | -0.3            | 0.7                        | 1.7                         | 3.6                     | 0.4                                 | 2                           | 1        | -1                   |

| LVOIMOO                |       | 2.5                    | 2.625 | -0.3            | 0.7                        | 1.7                         | 3.6                     | 0.7                                 | 1.7                         | 2        | -2                   |

| 1.8V LVTTL/<br>LVCMOS  | 1.71  | 1.8                    | 1.89  | -0.3            | 0.35 × V <sub>ccio</sub>   | 0.65 ×<br>V <sub>cc10</sub> | V <sub>ccio</sub> + 0.3 | 0.45                                | V <sub>cc10</sub> - 0.45    | 2        | -2                   |

| 1.5 V LVTTL/<br>LVCMOS | 1.425 | 1.5                    | 1.575 | -0.3            | 0.35 × V <sub>ccio</sub>   | 0.65 ×<br>V <sub>cc10</sub> | V <sub>ccio</sub> + 0.3 | 0.25 ×<br>V <sub>ccio</sub>         | 0.75 ×<br>V <sub>cc10</sub> | 2        | -2                   |

| 1.2V LVTTL/<br>LVCMOS  | 1.14  | 1.2                    | 1.26  | -0.3            | 0.35 × V <sub>ccio</sub>   | 0.65 ×<br>V <sub>cc10</sub> | V <sub>ccio</sub> + 0.3 | 0.25 ×<br>V <sub>ccio</sub>         | 0.75 × V <sub>cc10</sub>    | 2        | -2                   |

| 3.0-V PCI              | 2.85  | 3                      | 3.15  | _               | 0.3 ×<br>V <sub>ccio</sub> | 0.5 ×<br>V <sub>cc10</sub>  | 3.6                     | 0.1 ×<br>V <sub>cc10</sub>          | 0.9 ×<br>V <sub>CC10</sub>  | 1.5      | -0.5                 |

| 3.0-V PCI-X            | 2.85  | 3                      | 3.15  | _               | 0.35 × V <sub>ccio</sub>   | 0.5 ×<br>V <sub>cc10</sub>  | _                       | 0.1 ×<br>V <sub>ccio</sub>          | 0.9 ×<br>V <sub>CC10</sub>  | 1.5      | -0.5                 |

Electrical Characteristics

Refer to Figure 1–6 in the row "Single-Ended Voltage Referenced I/O Standard" in Table 1–33 for an example of a voltage referenced receiver input waveform and explanation of terms used in Table 1–13.

Table 1–13.

Single-Ended SSTL and HSTL I/O Reference Voltage Specifications – Preliminary

|                     |       | V <sub>ccio</sub> (V) |       | V <sub>REF</sub> (V)        |                            |                              |                          | Vπ (V)               |                          |

|---------------------|-------|-----------------------|-------|-----------------------------|----------------------------|------------------------------|--------------------------|----------------------|--------------------------|

| I/O Standard        | Min   | Тур                   | Max   | Min                         | Тур                        | Max                          | Min                      | Тур                  | Max                      |

| SSTL-2 CLASS I, II  | 2.375 | 2.5                   | 2.625 | 0.49 ×<br>V <sub>cc10</sub> | 0.5 ×<br>V <sub>ccio</sub> | 0.51 ×<br>V <sub>cc io</sub> | V <sub>REF</sub> – 0.04  | $V_{REF}$            | V <sub>REF</sub> + 0.04  |

| SSTL-18 CLASS I, II | 1.71  | 1.8                   | 1.89  | 0.833                       | 0.9                        | 0.969                        | V <sub>REF</sub> – 0.04  | $V_{REF}$            | V <sub>REF</sub> + 0.04  |

| SSTL-15 CLASS I, II | 1.425 | 1.5                   | 1.575 | 0.47 × V <sub>cc10</sub>    | 0.5 ×<br>V <sub>ccio</sub> | 0.53 ×<br>V <sub>cc io</sub> | 0.47 × V <sub>ccio</sub> | $V_{REF}$            | 0.53 × V <sub>cc10</sub> |

| HSTL-18 CLASS I, II | 1.71  | 1.8                   | 1.89  | 0.85                        | 0.9                        | 0.95                         | _                        | V <sub>cc10</sub> /2 | _                        |

| HSTL-15 CLASS I, II | 1.425 | 1.5                   | 1.575 | 0.68                        | 0.75                       | 0.9                          | _                        | V <sub>cc10</sub> /2 | _                        |

| HSTL-12 CLASS I, II | 1.14  | 1.2                   | 1.26  | 0.47 × V <sub>cc10</sub>    | 0.5 ×<br>V <sub>ccio</sub> | 0.53 ×<br>V <sub>cc io</sub> | _                        | V <sub>cc10</sub> /2 | _                        |

**Table 1–14.** Single-Ended SSTL and HSTL I/O Standards Signal Specifications – Preliminary (Part 1 of 2)

|                  | VLO  | ;) <b>(V)</b>            | V <sub>IH (D</sub>       | <sub>c)</sub> (V)       | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>ol</sub> (V)        | V <sub>OH</sub> (V)        |          |                      |

|------------------|------|--------------------------|--------------------------|-------------------------|--------------------------|--------------------------|----------------------------|----------------------------|----------|----------------------|

| I/O Standard     | Min  | Max                      | Min                      | Max                     | Max                      | Min                      | Max                        | Min                        | I₀L (mA) | I <sub>OH</sub> (mA) |

| SSTL-2 CLASS I   | -0.3 | V <sub>REF</sub> − 0.15  | V <sub>ref</sub> + 0.15  | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.31  | V <sub>REF</sub> + 0.31  | VTT –<br>0.57              | VTT +<br>0.57              | 8.1      | -8.1                 |

| SSTL-2 CLASS II  | -0.3 | V <sub>REF</sub> − 0.15  | V <sub>REF</sub> + 0.15  | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.31  | V <sub>REF</sub> + 0.31  | VTT –<br>0.76              | VTT +<br>0.76              | 16.2     | -16.2                |

| SSTL-18 CLASS I  | -0.3 | V <sub>REF</sub> − 0.125 | V <sub>REF</sub> + 0.125 | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | VTT –<br>0.475             | VTT +<br>0.475             | 6.7      | -6.7                 |

| SSTL-18 CLASS II | -0.3 | V <sub>REF</sub> − 0.125 | V <sub>REF</sub> + 0.125 | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | 0.28                       | V <sub>ccio</sub> – 0.28   | 13.4     | -13.4                |

| SSTL-15 CLASS I  | -0.3 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | 0.2 ×<br>V <sub>ccio</sub> | 0.8 ×<br>V <sub>ccio</sub> | 8        | -8                   |

| SSTL-15 CLASS II | -0.3 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | 0.2 ×<br>V <sub>ccio</sub> | 0.8 ×<br>V <sub>ccio</sub> | 16       | -16                  |

| HSTL-18 CLASS I  | -0.3 | V <sub>REF</sub> − 0.1   | V <sub>REF</sub> + 0.1   | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>ccio</sub> – 0.4    | 8        | -8                   |

| HSTL-18 CLASS II | -0.3 | V <sub>REF</sub> − 0.1   | V <sub>REF</sub> + 0.1   | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>ccio</sub> – 0.4    | 16       | -16                  |

| HSTL-15 CLASS I  | -0.3 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | V <sub>cc10</sub> + 0.3 | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>ccio</sub> – 0.4    | 8        | -8                   |

| HSTL-15 CLASS II | -0.3 | V <sub>REF</sub> – 0.1   | V <sub>ref</sub> + 0.1   | V <sub>CC10</sub> + 0.3 | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>ccio</sub> – 0.4    | 16       | -16                  |

|                  | VLO   | c) (V)                  | VIH(D                   | <sub>c)</sub> (V)        | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | $V_{oL}(V)$                 | V <sub>OH</sub> (V)         |          |                      |

|------------------|-------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|-----------------------------|-----------------------------|----------|----------------------|

| I/O Standard     | Min   | Max                     | Min                     | Max                      | Max                     | Min                     | Max                         | Min                         | I₀∟ (mA) | I <sub>OH</sub> (mA) |

| HSTL-12 CLASS I  | -0.15 | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>ccio</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | 0.25 ×<br>V <sub>ccio</sub> | 0.75 ×<br>V <sub>ccio</sub> | 8        | -8                   |

| HSTL-12 CLASS II | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>cc10</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | 0.25 ×<br>V <sub>ccio</sub> | 0.75 × V <sub>ccio</sub>    | 16       | -16                  |

Table 1-14. Single-Ended SSTL and HSTL I/O Standards Signal Specifications - Preliminary (Part 2 of 2)

Refer to Figure 1–2 in the row "Differential I/O Standards" in Table 1–33 for receiver input and transmitter output waveforms, and for all differential I/O standards (LVDS, mini-LVDS, RSDS).  $V_{\text{CC\_CLKIN}}$  is the power supply for differential column clock input pins.  $V_{\text{CCPD}}$  is the power supply for row I/Os and all other column I/Os.

Table 1-15. Differential SSTL I/O Standard Specifications - Preliminary

|                                 |       | V <sub>ccio</sub> (V) |       | Vswing | (DC) <b>(V)</b>         |                                    | V <sub>x (AC)</sub> (V) |                                    | V <sub>swing</sub> | (AC) <b>(V)</b>            |                                    | V <sub>OX (AC)</sub> (V | )                                  |

|---------------------------------|-------|-----------------------|-------|--------|-------------------------|------------------------------------|-------------------------|------------------------------------|--------------------|----------------------------|------------------------------------|-------------------------|------------------------------------|

| I/O Standard                    | Min   | Тур                   | Max   | Min    | Max                     | Min                                | Тур                     | Max                                | Min                | Max                        | Min                                | Тур                     | Max                                |

| SSTL-2<br>CLASS I,<br>CLASS II  | 2.375 | 2.5                   | 2.625 | 0.3    | V <sub>ccio</sub> + 0.6 | V <sub>ccio</sub> /2<br>-0.2       | _                       | V <sub>ccro</sub> /2<br>+ 0.2      | 0.6                | V <sub>ccio</sub><br>+ 0.6 | V <sub>ccio</sub> /2<br>- 0.15     | _                       | V <sub>ccro</sub> /2<br>+ 0.15     |

| SSTL-18<br>CLASS I,<br>CLASS II | 1.71  | 1.8                   | 1.89  | 0.3    | V <sub>ccio</sub> + 0.6 | V <sub>ccio</sub> /2<br>-<br>0.175 | _                       | V <sub>ccro</sub> /2<br>+<br>0.175 | 0.5                | V <sub>ccio</sub> + 0.6    | V <sub>ccio</sub> /2<br>-<br>0.125 | _                       | V <sub>ccio</sub> /2<br>+<br>0.125 |

| SSTL-15<br>CLASS I,<br>CLASS II | 1.425 | 1.5                   | 1.575 | 0.2    | _                       | _                                  | V <sub>cc10</sub> /2    | _                                  | 0.4                | _                          | _                                  | V <sub>cc10</sub> /2    |                                    |

Table 1–16. Differential HSTL I/O Standards Specifications – Preliminary

|                        | V <sub>CC10</sub> (V) |     |       | <b>V</b> <sub>DIF(D</sub> | $V_{DIF(DC)}(V)$ $V_{x(AC)}(V)$ |      |                            | V <sub>CM(DC)</sub> (V) |                            |                            |                            | V <sub>DIF(AC)</sub> (V) |                             |  |

|------------------------|-----------------------|-----|-------|---------------------------|---------------------------------|------|----------------------------|-------------------------|----------------------------|----------------------------|----------------------------|--------------------------|-----------------------------|--|

| I/O Standard           | Min                   | Тур | Max   | Min                       | Max                             | Min  | Тур                        | Max                     | Min                        | Тур                        | Max                        | Min                      | Max                         |  |

| HSTL-18<br>CLASS I, II | 1.71                  | 1.8 | 1.89  | 0.2                       | _                               | 0.78 | _                          | 1.12                    | 0.78                       | _                          | 1.12                       | 0.4                      | _                           |  |

| HSTL-15<br>CLASS I, II | 1.425                 | 1.5 | 1.575 | 0.2                       | _                               | 0.68 | _                          | 0.9                     | 0.68                       | _                          | 0.9                        | 0.4                      | _                           |  |

| HSTL-12<br>CLASS I, II | 1.14                  | 1.2 | 1.26  | 0.16                      | V <sub>ccio</sub> + 0.3         | _    | 0.5 ×<br>V <sub>ccio</sub> | _                       | 0.4 ×<br>V <sub>cc10</sub> | 0.5 ×<br>V <sub>ccio</sub> | 0.6 ×<br>V <sub>CC10</sub> | 0.3                      | V <sub>ccio</sub> +<br>0.48 |  |

**Table 1–17.** Differential I/O Standard Specifications – Preliminary (Part 1 of 2)

|              | V <sub>cc10</sub> (V) V <sub>10</sub> (mV) V <sub>10 M(0C)</sub> (V) |     |       |     | V <sub>10</sub> (mV)    |     |                    |                           | 1                  | V <sub>∞</sub> (V) <i>(1</i> | )   | V <sub>OCM</sub> (V) (1) |       |      |       |

|--------------|----------------------------------------------------------------------|-----|-------|-----|-------------------------|-----|--------------------|---------------------------|--------------------|------------------------------|-----|--------------------------|-------|------|-------|

| I/O Standard | Min                                                                  | Тур | Max   | Min | Condition               | Max | Min                | Condition                 | Max                | Min                          | Тур | Max                      | Min   | Тур  | Max   |

| 2.5V LVDS    | 2.375                                                                | 2.5 | 2.625 | 100 | V <sub>CM</sub> = 1.25V | _   | 0.05<br>(2)        | <i>Dmax</i> ≤ 700<br>Mbps | 1.8<br>(2)         | 0.247                        | _   | 0.6                      | 1.125 | 1.25 | 1.375 |

| (Row I/0)    | 2.375                                                                | 2.5 | 2.625 | 100 | V <sub>CM</sub> = 1.25V | _   | 1.05<br><i>(2)</i> | Dmax > 700<br>Mbps        | 1.55<br><i>(2)</i> | _                            | _   | _                        | _     |      | _     |

|                              |              | V <sub>ccio</sub> (V) |              |     | V <sub>10</sub> (mV)    |     |                    | $\mathbf{V}_{\scriptscriptstyle{ICM(DC)}}(\mathbf{V})$ |                    | ,     | V <sub>∞</sub> (V) <i>(1</i> | )   | ١ ١ | <b>/</b> <sub>осм</sub> (V) <i>(</i> 1 | )   |

|------------------------------|--------------|-----------------------|--------------|-----|-------------------------|-----|--------------------|--------------------------------------------------------|--------------------|-------|------------------------------|-----|-----|----------------------------------------|-----|

| I/O Standard                 | Min          | Тур                   | Max          | Min | Condition               | Max | Min                | Condition                                              | Max                | Min   | Тур                          | Max | Min | Тур                                    | Max |

| 2.5V LVDS<br>(Column         | 2.375        | 2.5                   | 2.625        | 100 | V <sub>CM</sub> = 1.25V | _   | 0.05<br><i>(2)</i> | <i>Dmax</i> ≤ 700 Mbps                                 | 1.8<br><i>(2)</i>  | 0.247 |                              | 0.6 | 1.0 | 1.25                                   | 1.5 |

| 1/0)                         | 2.375        | 2.5                   | 2.625        | 100 | V <sub>CM</sub> = 1.25V | _   | 1.05<br><i>(2)</i> | Dmax > 700<br>Mbps                                     | 1.55<br><i>(2)</i> | _     |                              | _   | _   | _                                      | 1.5 |

| RSDS<br>(Row I/O)            | 2.375        | 2.5                   | 2.625        | 100 | V <sub>CM</sub> = 1.25V | _   | 0.3                | _                                                      | 1.4                | 0.1   | 0.2                          | 0.6 | 0.5 | 1.2                                    | 1.4 |

| RSDS<br>(Column<br>I/O)      | 2.375        | 2.5                   | 2.625        | 100 | V <sub>CM</sub> = 1.25V | _   | 0.3                | _                                                      | 1.4                | 0.1   | 0.2                          | 0.6 | 0.5 | 1.2                                    | 1.5 |

| Mini-LVDS<br>(Row I/O)       | 2.375        | 2.5                   | 2.625        | 200 | _                       | 600 | 0.4                | _                                                      | 1.325              | 0.25  | -                            | 0.6 | 0.5 | 1.2                                    | 1.4 |

| Mini-LVDS<br>(Column<br>I/O) | 2.375        | 2.5                   | 2.625        | 200 | _                       | 600 | 0.4                | _                                                      | 1.325              | 0.25  | _                            | 0.6 | 0.5 | 1.2                                    | 1.5 |

| LVPECL (3)                   | 2.375<br>(4) | 2.5<br>(4)            | 2.625<br>(4) | 300 | _                       | _   | 0.6                | Dmax ≤ 700<br>Mbps                                     | 1.8<br><i>(5)</i>  | _     | _                            | _   | _   | _                                      | _   |

| LVI LUL (3)                  | _            | _                     | _            | _   | _                       | _   | 0.6                | <i>Dmax</i> ≤ 700 Mbps                                 | 1.6<br><i>(5)</i>  | _     | _                            | _   | _   | _                                      | _   |

**Table 1–17.** Differential I/O Standard Specifications – Preliminary (Part 2 of 2)

#### Notes to Table 1-17:

- (1)  $R_1$  range:  $90 \le R_1 \le 110 \Omega$ .

- (2) For data rate:  $D_{max} > 700$  Mbps, the minimum input voltage is 1.0 V, the maximum input voltage is 1.6 V. For  $D_{max} \le 700$  Mbps, the minimum input voltage is 0 V, the maximum input voltage is 1.85 V.

- (3) Column and Row I/O banks support LVPECL I/O standards for input operation only on dedicated clock input pins. Differential clock inputs in column I/O use V<sub>CC\_CLKIN</sub> which should be powered by 2.5 V. Differential clock inputs in row I/Os are powered by V<sub>CCPD</sub>.

- (4) Power supply for column I/O LVPECL differential clock input buffer is  $V_{CC\_CLKIN}$ .

- (5) For data rate  $D_{max} > 700$  Mbps, the minimum input voltage is 0.85 V, and the maximum input voltage is 1.75 V. For data rate  $D_{max} \le 700$  Mbps, the minimum input voltage is 0.45 V, and the maximum input voltage is 1.95 V.

## **Power Consumption**

Altera offers two ways to estimate power for a design: the Excel-based Early Power Estimator and the Quartus® II PowerPlay Power Analyzer feature.

Use the interactive Excel-based Early Power Estimator prior to designing in order to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after the place-and-route is complete. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

See Table 1–4 on page 1–5 for supply current estimates for  $V_{\text{CCPGM}}$  and  $V_{\text{CC\_CLKIN}}$ . Use the EPE and PowerPlay Power Analyzer for current estimates of the remaining power supplies.

For more information about power estimation tools, refer to the *Power Play Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Device Handbook*.

## **Switching Characteristics**

This section provides performance characteristics of HardCopy III core and periphery blocks for commercial grade devices. HardCopy III devices are designed to meet, at minimum, the –3 speed grade of the Stratix III devices. Silicon characterization determines the actual performance of the HardCopy III devices. These characteristics can be designated as **Preliminary** or **Final**, as defined below.

- Preliminary—Preliminary characteristics are created using simulation results, process data, and other known parameters.

- **Final**—Final numbers are based on actual silicon characterization and testing. These numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions.

## **Core Performance Specifications**

This sections describes the clock tree, phase-locked loop (PLL), digital signal processing (DSP), TriMatrix, configuration, and JTAG specifications.

## **Clock Tree Specifications**

Table 1–18 lists clock tree performance specifications for the logic array, DSP blocks, and TriMatrix Memory blocks for HardCopy III devices.

| Davis -                        | 0                              |          |

|--------------------------------|--------------------------------|----------|

| Table 1–18. HardCopy III Clock | Tree Performance – Preliminary | (Note 1) |

| Device | Commercial Grade (MHz) | Unit |

|--------|------------------------|------|

| HC311  | 500                    | MHz  |

| HC321  | 500                    | MHz  |

| HC322  | 500                    | MHz  |

| HC331  | 500                    | MHz  |

| HC332  | 500                    | MHz  |

| HC351  | 500                    | MHz  |

| HC352  | 500                    | MHz  |

| HC361  | 500                    | MHz  |

| HC362  | 500                    | MHz  |

| HC372  | 500                    | MHz  |

#### Note to Table 1–18:

(1) Pending silicon characterization.

## **PLL Specifications**

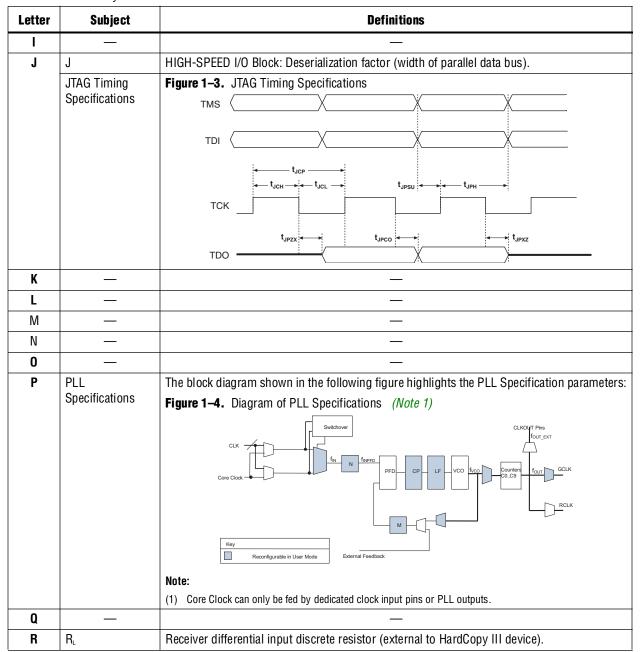

Table 1–19 describes the HardCopy III PLL specifications when operating in both the commercial junction temperature range (0° to 85° C) and the industrial junction temperature range ( $-40^{\circ}$  to  $100^{\circ}$ C). Refer to Figure 1–4 in the "PLL Specifications" row in Table 1–33 for a PLL block diagram.

**Table 1–19.** HardCopy III PLL Specifications – Preliminary (Part 1 of 2) (Note 1)

| Symbol                     | Parameter                                                                                                | Min | Тур | Max     | Unit           |

|----------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|---------|----------------|

| f <sub>IN</sub>            | Input clock frequency                                                                                    | 5   | _   | 717 (2) | MHz            |

| f <sub>INPFD</sub>         | Input frequency to the PFD                                                                               | 5   | _   | 325     | MHz            |

| f <sub>vco</sub>           | PLL VCO operating range                                                                                  | 600 | _   | 1300    | MHz            |

| teinduty                   | Input clock or external feedback clock input duty cycle                                                  | 40  | _   | 60      | %              |

| f <sub>out</sub>           | Output frequency for internal global or regional clock                                                   | _   | _   | 717 (3) | MHz            |

| f <sub>out_ext</sub>       | Output frequency for external clock output                                                               | _   | _   | 717 (3) | MHz            |

| toutduty                   | Duty cycle for external clock output (when set to 50%)                                                   | 45  | 50  | 55      | %              |

| t <sub>FCOMP</sub>         | External feedback clock compensation time                                                                | _   | _   | 10      | ns             |

| tconfigple                 | Time required to reconfigure PLL scan chain                                                              | _   | _   | _       | scanclk cycles |

| tconfighase                | Time required to reconfigure phase shift                                                                 | _   | _   | _       | scanclk cycles |

| f <sub>SCANCLK</sub>       | scanclk frequency                                                                                        | _   | _   | 100     | MHz            |

| t <sub>lock</sub>          | Time required to lock from end of device power up (4)                                                    | _   | _   | _       | ms             |

| t <sub>dlock</sub>         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) | _   | _   | _       | ms             |

| f <sub>CLBW</sub>          | PLL closed-loop low bandwidth                                                                            | _   | _   | _       | MHz            |

|                            | PLL closed-loop medium bandwidth                                                                         | _   | _   | _       | MHz            |

|                            | PLL closed-loop high bandwidth (5)                                                                       | _   | _   | _       | MHz            |

| t <sub>PLL_PSERR</sub>     | Accuracy of PLL phase shift                                                                              | _   | _   | _       | ps             |

| tareset                    | Minimum pulse width on areset signal                                                                     | 10  | _   | _       | ns             |

| t <sub>INCCJ</sub> (4)     | Input clock cycle to cycle jitter ( $F_{REF} \ge 100 \text{ MHz}$ )                                      | _   | _   | _       | UI (p-p)       |

|                            | Input clock cycle to cycle jitter (F <sub>REF</sub> < 100 MHz)                                           | -   | _   | _       | ps (p-p)       |

| t <sub>outpj_dc</sub> (6)  | Period jitter for dedicated clock output (F <sub>OUT</sub> ≥ 100 MHz)                                    | _   | _   | _       | ps (p-p)       |

|                            | Period jitter for dedicate clock output (F <sub>OUT</sub> < 100 MHz)                                     | _   | _   | _       | mUI (p-p)      |

| t <sub>outccj_dc</sub> (6) | Cycle to cycle jitter for dedicated clock output ( $F_{OUT} \ge 100 \text{ MHz}$ )                       | -   | _   | _       | ps (p-p)       |

|                            | Cycle to cycle jitter for dedicated clock output (F <sub>OUT</sub> < 100 MHz)                            | _   | _   | _       | mUI (p-p)      |

| t <sub>outpj_i0</sub> (6)  | Period jitter for clock output on regular I/O ( $F_{OUT} \ge 100 \text{ MHz}$ )                          | _   | _   | _       | ps (p-p)       |

|                            | Period jitter for clock output on regular I/O (F <sub>OUT</sub> < 100 MHz)                               | _   | _   | _       | mUI (p-p)      |

| t <sub>outccj_io</sub> (6) | Cycle to cycle jitter for clock output on regular I/O ( $F_{OUT} \ge 100 \text{ MHz}$ )                  | _   | _   | _       | ps (p-p)       |

|                            | Cycle to cycle jitter for clock output on regular I/O (F <sub>OUT</sub> < 100 MHz)                       | _   | _   | _       | mUI (p-p)      |

**Table 1–19.** HardCopy III PLL Specifications – Preliminary (Part 2 of 2) (Note 1)

| Symbol             | Parameter                                                       | Min | Тур | Max | Unit |

|--------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| f <sub>DRIFT</sub> | Frequency drift after PFDENA is disabled for duration of 100 ms | _   | _   | _   | %    |

#### Notes to Table 1-19:

- (1) Pending silicon characterization.

- (2) This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (3) This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $f_{OUT}$  of the PLL.

- (4) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source, which is less than 200 ps.

- (5) High bandwidth PLL settings are not supported in external feedback mode.

- (6) Peak-to-peak jitter with a probability level of 10<sup>-12</sup>(14 sigma, 99.999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied.

## **DSP Block Specifications**

Table 1–20 describes the HardCopy III DSP performance specifications.

**Table 1–20.** HardCopy III DSP Block Performance Specifications – Preliminary (Note 1), (2)

| Mode                                                         | Number of Multipliers | Max | Unit |

|--------------------------------------------------------------|-----------------------|-----|------|

| $9 \times 9$ -bit multiplier (a, c, e, g) (3)                | 1                     | 365 | MHz  |

| $9 \times 9$ -bit multiplier (b, d, f, h) (3)                | 1                     | 410 | MHz  |

| 12 × 12-bit multiplier (a, e) (4)                            | 1                     | 365 | MHz  |

| $12 \times 12$ -bit multiplier (b, d, f, h) (4)              | 1                     | 410 | MHz  |

| 18 x 18-bit multiplier                                       | 1                     | 495 | MHz  |

| 36 × 36-bit multiplier                                       | 1                     | 365 | MHz  |

| Double mode                                                  | 1                     | 365 | MHz  |

| 18 x 18-bit multiply adder                                   | 2                     | 405 | MHz  |

| 18 x 18-bit multiply adder                                   | 4                     | 405 | MHz  |

| $18 \times 18$ -bit multiply adder with loop back (5)        | 2                     | 405 | MHz  |

| 18 x 18-bit multiply accumulator                             | 4                     | 390 | MHz  |

| 18 x 18-bit multiply adder with chainout                     | 4                     | 390 | MHz  |

| Input Cascade Independent output of 4 18 × 18 bit multiplier | 4                     | 455 | MHz  |

| 36-bit shift (32 bit data)                                   | 1                     | 390 | MHz  |

### Notes to Table 1-20:

- (1) Maximum is for fully pipelined block with round and saturation disabled.

- (2) Pending silicon characterization.

- (3) The DSP block implements eight independent 9 × 9-bit multipliers using a, b, c, and d for the top half of the DSP block and e, f, g, and h for the bottom DSP half block multipliers.

- (4) The DSP block implements six independent 12 × 12-bit multipliers using a, b, and d for the top half of the DSP half block and e, f, and h for the bottom DSP half block multipliers.

- (5) Maximum for non-pipelined block with loopback input registers disabled with round and saturation disabled.

## **TriMatrix Memory Block Specifications**

Table 1–21 describes the HardCopy III TriMatrix memory block specifications.

Table 1–21.

HardCopy III TriMatrix Memory Block Performance Specifications – Preliminary (Part 1 of 2) (Note 1)

| Memory<br>Block Type | Mode                                                                                                                                    | TriMatrix<br>Memory | Max | Unit |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|------|

|                      | Single port 16 × 10                                                                                                                     | 1                   | 500 | MHz  |

| MLAB                 | Simple dual-port 16 × 20 single clock                                                                                                   | 1                   | 500 | MHz  |

| IVILAD               | ROM 64 × 10                                                                                                                             | 1                   | 500 | MHz  |

|                      | ROM 32 × 20                                                                                                                             | 1                   | 500 | MHz  |

|                      | Single-port 8K × 1                                                                                                                      | 1                   | 465 | MHz  |

|                      | Single-port 4K × 2 or 2K × 4                                                                                                            | 1                   | 485 | MHz  |

|                      | Single-port 1K × 9, 512 × 18, or 256 × 36                                                                                               | 1                   | 475 | MHz  |

|                      | Simple dual-port, 8K × 1 single clock                                                                                                   | 1                   | 460 | MHz  |

|                      | Simple dual-port, 4K × 2 or 2K × 4, single clock                                                                                        | 1                   | 480 | MHz  |

|                      | Simple dual-port, $1K \times 9$ , $512 \times 18$ , or $256 \times 36$ , single clock                                                   | 1                   | 475 | MHz  |

|                      | Simple dual-port, $8K \times 1$ , $4K \times 2$ , or $2K \times 4$ single clock, with the read-during-write option set to "Old Data"    | 1                   | 312 | MHz  |

|                      | Simple dual-port, 1K $\times$ 9, 512 $\times$ 18, or 256 $\times$ 36, single clock, with the read-during-write option set to "Old Data" | 1                   | 312 | MHz  |

|                      | True dual-port, 8K × 1 single clock                                                                                                     | 1                   | 440 | MHz  |

| M9K                  | True dual-port, 4K × 2 or 2K × 4, single clock                                                                                          | 1                   | 480 | MHz  |

|                      | True dual-port, 1K × 9 or 512 × 18, single clock                                                                                        | 1                   | 460 | MHz  |

|                      | True dual-port, $8K \times 1$ , $4K \times 2$ , or $2K \times 4$ , single clock, with the read-during-write option set to "Old Data"    | 1                   | 295 | MHz  |

|                      | True dual-port, 1K $\times$ 9 or 512 $\times$ 18, single clock, with the read-during-write option set to "Old Data"                     | 1                   | 285 | MHz  |

|                      | ROM 1P, 8K $\times$ 1, 4K $\times$ 2, or 2K $\times$ 4, single clock, with the read-during-write option set to "Old Data"               | 1                   | 485 | MHz  |

|                      | ROM 1P, 1K $\times$ 9, 512 $\times$ 18, single clock, with the read-during-write option set to "Old Data"                               | 1                   | 485 | MHz  |

|                      | ROM 2P, 8K × 1, 4K × 2, or 2K × 4                                                                                                       | 1                   | 485 | MHz  |

|                      | ROM 2P, 1K × 9, or 512 × 18                                                                                                             | 1                   | 485 | MHz  |

|                      | Min Pulse Width (Clock High Time)                                                                                                       | _                   | 800 | ps   |

| Memory<br>Block Type | Mode                                                                                                                                                   | TriMatrix<br>Memory | Max  | Unit |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|

|                      | True dual-port 16K × 9 or 8K × 18, dual clock                                                                                                          | 1                   | 300  | MHz  |

|                      | True dual-port 4K × 36 dual clock                                                                                                                      | 1                   | 430  | MHz  |

|                      | Simple dual-port 16K × 9 or 8K × 18, dual clock                                                                                                        | 1                   | 300  | MHz  |

|                      | Simple dual-port 4K × 36 or 2K × 72, dual clock                                                                                                        | 1                   | 470  | MHz  |

|                      | ROM 1 Port                                                                                                                                             | 1                   | 500  | MHz  |

|                      | ROM 2 Port                                                                                                                                             | 1                   | 450  | MHz  |

| M144K                | Single-port 16K × 9 or 8K × 18                                                                                                                         | 1                   | 330  | MHz  |

|                      | Single-port 4K × 36                                                                                                                                    | 1                   | 500  | MHz  |

|                      | True dual-port 16K $\times$ 9, 8K $\times$ 18, or 4K $\times$ 36, dual clock with the read-during-write option set to "Old Data"                       | 1                   | 270  | MHz  |

|                      | Simple dual-port $16K \times 9$ , $8K \times 18$ , $4K \times 36$ , or $2K \times 72$ , dual clock with the read-during-write option set to "Old Data" | 1                   | 292  | MHz  |

|                      | Simple dual-port 2K × 64 dual clock (with ECC)                                                                                                         | 1                   | 210  | MHz  |

|                      | Min Pulse Width (Clock High Time)                                                                                                                      | _                   | 1000 | ps   |

**Table 1–21.** HardCopy III TriMatrix Memory Block Performance Specifications – Preliminary (Part 2 of 2) (Note 1)

#### Note to Table 1-21:

## **JTAG Specifications**

Table 1–22 shows the JTAG timing parameters and values for HardCopy III devices. Refer to Figure 1–3 in the "HIGH-SPEED I/O Block" row in Table 1–33 for JTAG timing requirements.

**Table 1–22.** HardCopy III JTAG Timing Parameters and Values – Preliminary

| Symbol                  | Parameter                                | Min | Max | Unit |

|-------------------------|------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>        | TCK clock period                         | 30  | _   | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14  | _   | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14  | _   | ns   |

| t <sub>JPSU</sub> (TDI) | JTAG port setup time for TDI             | 1   | _   | ns   |

| t <sub>JPSU</sub> (TMS) | JTAG port setup time for TMS             | 3   | _   | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5   | _   | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |     | 11  | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output | _   | 14  | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _   | 14  | ns   |

## **Periphery Performance**

This section describes the periphery performance, including high-speed I/O, external memory interface, and OCT calibration block specifications.

<sup>(1)</sup> Pending silicon characterization.

## **High-Speed I/O Specifications**

Refer to Table 1–33 for definitions of high-speed timing specifications.

Table 1–23 shows the high-speed I/O timing for HardCopy III devices.

**Table 1–23.** High Speed I/O Specifications – Preliminary (Note 1), (2), (3)

| ck boost factor W = 2 to 32 (4) ck boost factor W = 1 (SERDES bypassed) ck boost factor W = 1 (SERDES used) RDES factor J = 3 to 10 RDES factor J = 2, uses DDR registers RDES factor J = 1, uses SDR register ———————————————————————————————————— | 5<br>5<br>150<br>150<br>————————————————————————————                                   |                                                                                                                                                       | 625<br>600<br>717<br>1250<br>TBD (5)<br>TBD (5)                                                        | MHz<br>MHz<br>MHz<br>Mbps<br>Mbps |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------|

| ck boost factor W = 1 (SERDES used)  RDES factor J = 3 to 10  RDES factor J = 2, uses DDR registers                                                                                                                                                 | 150<br>150<br>—                                                                        | _                                                                                                                                                     | 717<br>1250<br>TBD <i>(5)</i>                                                                          | MHz<br>Mbps<br>Mbps               |

| RDES factor J = 3 to 10 RDES factor J = 2, uses DDR registers                                                                                                                                                                                       | 150<br>—<br>—                                                                          | _                                                                                                                                                     | 1250<br>TBD <i>(5)</i>                                                                                 | Mbps<br>Mbps                      |

| RDES factor J = 2, uses DDR registers                                                                                                                                                                                                               | _<br>_                                                                                 | _                                                                                                                                                     | TBD (5)                                                                                                | Mbps                              |

|                                                                                                                                                                                                                                                     | —<br>—<br>150                                                                          |                                                                                                                                                       | ` '                                                                                                    |                                   |

| RDES factor J = 1, uses SDR register  —  — — — —                                                                                                                                                                                                    | 150                                                                                    | _                                                                                                                                                     | TBD (5)                                                                                                | Mhns                              |

| _<br>                                                                                                                                                                                                                                               | 150                                                                                    | _                                                                                                                                                     |                                                                                                        | Mbps                              |

| <del>-</del>                                                                                                                                                                                                                                        |                                                                                        |                                                                                                                                                       | 1250                                                                                                   | Mbps                              |

| <u>—</u>                                                                                                                                                                                                                                            | -                                                                                      | _                                                                                                                                                     | 340                                                                                                    | Mbps                              |