### **DATA SHEET**

**JULY 2005**

#### DESCRIPTION

The 78P2343JAT is a low-power, 3-port DS3/E3/STS1 Line Interface Unit (LIU) with integrated Jitter Attenuator (JAT). It includes all the required clock recovery and transmitter pulse shaping functions for applications using 75-ohm coaxial cable at distances up to 1350 feet. These applications include DSLAMs, T1,3/E1,3 digital multiplexers, SONET Add/Drop multiplexers, PDH equipment, DS3 to Fiber optic and microwave modems and ATM WAN access for routers and switches.

The receiver recovers clock and data from a B3ZS or HDB3 coded AMI signal. It can compensate for over 12dB of cable and 6dB of flat loss. The transmitter generates a signal that meets the standard pulse shape requirements. The 78P2343JAT includes optional B3ZS/HDB3 ENDEC with a receive line code violation detector, loop-back modes, Loss of Signal detector, clock polarity selection, and the ability to receive a DSX3 monitor signal.

#### **STANDARDS**

- Telcordia GR-499-CORE and GR-253-CORE

- ITU-T G.823, G.824, G.775, and G.703

- ETSI TBR-24, ETS 300 686, ETS 300 687, and ETS EN 300 689

- ANSI T1.102-1993, T1.231-1997, T1.404-1994, and T1.105.03b

#### **FEATURES**

- Transmit and receive interfaces for E3, DS3 and STS-1 applications

- Designed for use with 75 ohm coaxial cable lengths up to 1350 ft

- Receives DS3-high and DSX3 monitor signals

- Local and Remote loopbacks

- Selectable B3ZS/HDB3 ENDEC with line code violation detector

- Standards-based LOS detector

- Optional serial-port based mode selection and channel status monitoring

- Adaptive digital clock recovery (uses line-rate reference clock input)

- Receive output clock maintains nominal line-rate frequency at all times

- Fully integrated Jitter Attenuation function provided for all line rates (no external VCXO required)

- Jitter Attenuator configurable for transmit or receive path

- Transmit line fault monitor

- Requires no external current-setting resistor or loop filter components

- Single 3.3V supply operation

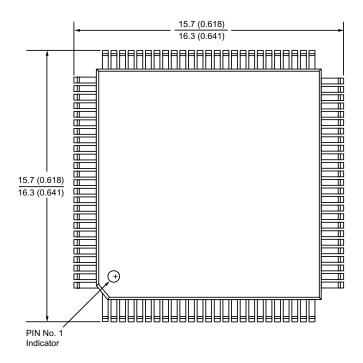

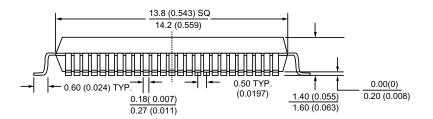

- Standard and exposed pad 100-pin JEDEC LQFP package options available

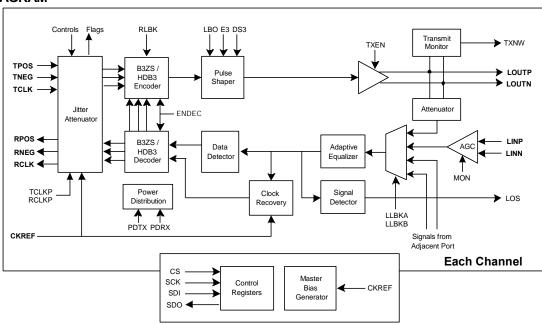

#### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The 78P2343JAT contains all the necessary transmit and receive circuitry for connection between E3, DS3, or STS-1 line interfaces and digital Framer/Mapper ICs.

#### **OPERATING RATE**

The Master Control Register (MSCR) determines which mode the device operates in according to the table below. The MSL0 pin is also provided for mode selection in applications without a serial control interface. Upon power-up or reset, the state of the MSL0 pin is sensed and mapped into the DS3 and E3 register bits representing the appropriate mode of operation. After power-up/reset, the state of the MSL0 pin is ignored.

| Standard | MSL0 pin | DS3 bit | E3 bit |  |

|----------|----------|---------|--------|--|

| E3       | L        | 0       | 1      |  |

| DS3      | Н        | 1       | 0      |  |

| STS-1    | Z        | 0       | 0      |  |

| STS-1    | Z        | 1       | 1      |  |

#### RECEIVER OPERATION

The receiver input is either transformer-coupled or capacitor-coupled to the line signal. In applications where the highest performance and isolation are required, a 1:1 transformer is used in the receive path. In applications where isolation is provided elsewhere in the circuit, capacitor coupling can be used. The receiver input should be line terminated externally with a termination resistor.

The AMI signal first enters an AGC, which has a selectable gain range setting. In normal operation, the AGC can compensate for signals with up to 6dB of flat loss. When Receiver Monitor Mode is enabled, the AGC can compensate for a DSX3 monitor signal with 16 to 20 dB of flat loss. The signal then enters a high performance adaptive equalizer. The equalizer is designed to overcome inter-symbol interference caused by long cable lengths. Because the equalizer is adaptive, the circuit will work with all square-shaped signals such as DS3-high or 34.368 Mbit/s E3. The variable gain differential amplifier automatically controls the gain to maintain a constant voltage level output regardless of the input voltage level.

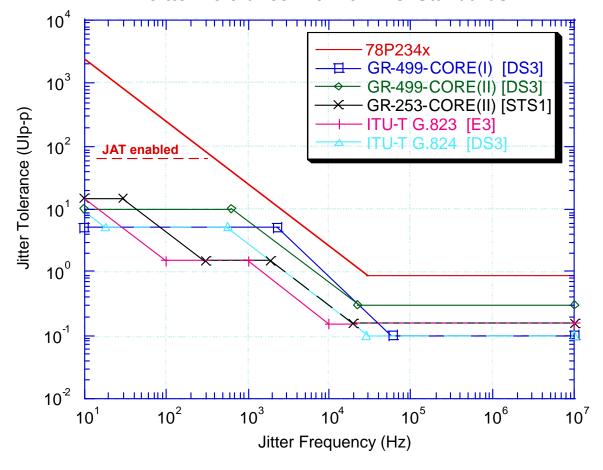

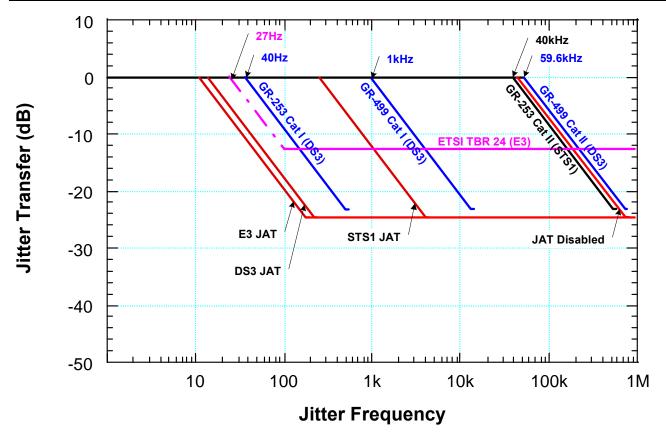

The jitter tolerance of 78P2343JAT meets the requirements of ITU-T G.823 for E3 rates; the requirements of ITU-T G.824 and Telcordia GR-499 (Cat I and II) for DS3 rates; and the requirements of Telcordia GR-253 for STS1 rates.

With the Jitter Attenuator disabled, the jitter transfer function meets the requirements of GR-499 for Category II DS3 interfaces.

When the Jitter Attenuator is enabled, the 78P2343JAT meets the requirements of GR-499 and GR-253 for all categories of DS3/STS1 equipment and the ETSI TBR-24 requirements for E3 rates. To check conformance with other standards, please refer to the JITTER ATTENUATOR TRANSFER FUNCTION section for more detailed info.

#### **RECEIVER MONITOR MODE**

When in monitor mode, 20dB of flat gain is applied to the incoming signal before it is fed to the receive equalizer. This mode is controlled by the MON bit in the Mode Control Register.

#### SIGNAL DETECT

When the received signal is below a minimum threshold, the corresponding LOS signal (bit) is asserted. A time delay is provided before this output is active so that transient interruptions do not cause false indications. The LOS signal can also be used to trigger an interrupt on the INTRx pin when serial interface control is not available. This is controlled by setting the RXER bit in the Interrupt Control Register (INTC).

Note: In DS3 or STS-1 mode, when LBO is not enabled, the transmitters have to be properly terminated to ensure reliable LOS detection. If a transmitter is not terminated, the resultant 2x signal is large enough to couple to the neighboring receivers through the ESD diodes, causing false Signal Detect indication.

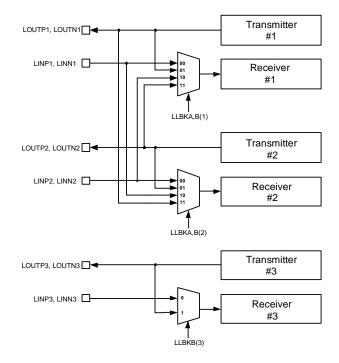

#### LOCAL LOOPBACK AND REDUNDANCY MUX

Receivers 1 and 2 have a 4-input MUX as shown in the adjacent figure. In multiport applications where redundant channels are required, the receiver MUX can be configured to provide the necessary multiplexing functions. This allows the user to use one port as a redundant monitor for the other port. The tables below show the register settings for selecting the desired receiver input source.

| LLBKA<br>(Port 1) | LLBKB<br>(Port 1) | Receiver #1 Input<br>Source |

|-------------------|-------------------|-----------------------------|

| 0                 | 0                 | LINP1/LINN1                 |

| 0                 | 1                 | LOUTP1/LOUTN1               |

| 1                 | 0                 | LINP2/LINN2                 |

| 1                 | 1                 | LOUTP2/LOUTN2               |

| LLBKA<br>(Port 2) | LLBKB<br>(Port 2) | Receiver #2 Input<br>Source |

|-------------------|-------------------|-----------------------------|

| 0                 | 0                 | LINP2/LINN2                 |

| 0                 | 1                 | LOUTP2/LOUTN2               |

| 1                 | 0                 | LINP1/LINN1                 |

| 1                 | 1                 | LOUTP1/LOUTN1               |

| LLBKB<br>(Port 3) | Receiver #3 Input<br>Source |  |  |

|-------------------|-----------------------------|--|--|

| 0                 | LINP3/LINN3                 |  |  |

| 1                 | LOUTP3/LOUTN3               |  |  |

Note: The LLBKA and LLBKB bits are located in the Mode Control Register (MDCR). The Register Control bit, REGEN, should be enabled when using the register settings to avoid conflict with external loopback setting pins.

When serial interface control is not available, the respective LPBKx pin for each of the channels can also be used to activate local loopback mode as shown below. Note that redundant channel modes can only be activated using the serial interface.

| LPBKx<br>pin | Loopback Mode                                     |  |

|--------------|---------------------------------------------------|--|

| L            | Normal Operation<br>Same as LLBKA,B = '00'        |  |

| Z            | Remote (Digital) Loopback<br>Same as RLBK = '1'   |  |

| Н            | Local (Analog) Loopback<br>Same as LLBKA,B = '01' |  |

# B3ZS/HDB3 ENDEC WITH LINE CODE VIOLATION DETECT

The 78P2343JAT includes a selectable B3ZS/HDB3 Encoder/Decoder (ENDEC). The ENDEC function can be enabled or disabled through pin selection or register setting as shown below.

| ENDECB<br>bit/pin | RPOSx        | RNEGx                                    |

|-------------------|--------------|------------------------------------------|

| 0/L               | NRZ data     | Receive Line Code<br>Violation Indicator |

| 1 / H             | Positive AMI | Negative AMI                             |

When the ENDEC is enabled, the decoder generates a composite NRZ logic data stream following the B3ZS (for DS3/STS-1) or HDB3 (for E3) substitution codes via the RPOSx pins:

The decoder also detects Receive Line Code Violations (RLCV) and outputs a pulse via the RNEG pin. Three different classes of line code violations are detected.

- 1) Too many zeros: More than two (three) consecutive zeros in B3ZS (HDB3) mode.

- 2) Not enough zeros between bipolar pulse (B) and bipolar violation pulse (V): (B,V) for B3ZS. (B,V) or (B,0,V) for HDB3.

- Code violation: Even number of bipolar pulses

(B) detected between bipolar violation pulses

(V).

When the ENDEC is disabled, the 78P2343JAT outputs a dual rail data stream via the RPOSx and RNEGx pins. In this mode, the Framer/Mapper providing the ENDEC function typically detects Line Code Violations.

On the transmit side, when the ENDEC is enabled, NRZ input data is encoded to Positive and Negative AMI logic data following the B3ZS (for DS3/STS-1) or HDB3 (for E3) substitution codes. The NRZ data is input to the TPOS pin as shown below:

| ENDECB<br>bit/pin | TPOSx        | TNEGx        |

|-------------------|--------------|--------------|

| 0 / L             | NRZ data     | 'Don't Care' |

| 1 / H             | Positive AMI | Negative AMI |

#### TRANSMITTER OPERATION

Transmitters 1-3 are enabled by their corresponding TXEN bit. When enabled, each transmitter accepts logic level clock and data signals and generates current pulses on the LOUTPx and LOUTNx pins. When properly connected to a 1:2CT center-tapped transformer, a standards compliant AMI pulse is generated which can drive a  $75\Omega$  coaxial cable.

When the recommended transformer is used and when DS3 mode is selected, the transmitted pulse shape at the end of the  $75\Omega$  terminated cable of 0 to 450 feet will fit the DS3 template in ANSI T1.102-1993 and Telcordia GR-499-CORE. For STS-1 applications, the transmitted pulse for a short cable meets the requirements of Telcordia GR-253-CORE. For E3 applications, the transmitted pulse for a short cable meets the requirements of ITU-T G.703.

In either DS3 and STS-1 modes, the LBOx pin or LBO bit should be set high for short cable (< 225 ft), and should be set low for long cable (> 225 ft). The LBO settings are ignored in E3 mode.

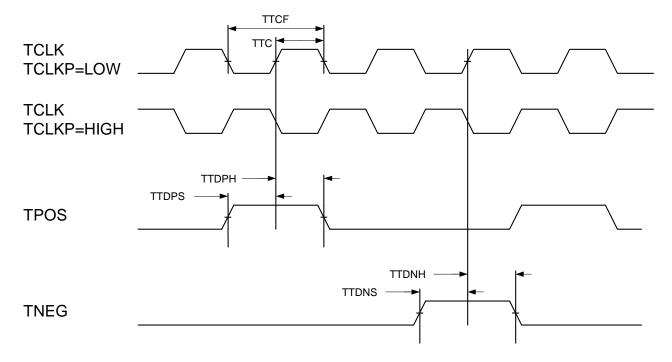

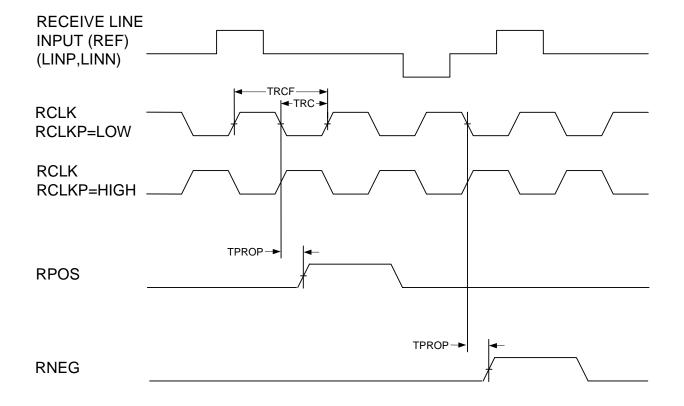

#### RCLK/TCLK POLARITY REVERSAL

To simplify the interface with various framer circuitry, TCLK polarity can be internally inverted by setting the TCLKP bit, and RCLK polarity can be inverted by setting the RCLKP bit. Both bits are located in the Master Control Register (MSCR).

#### REMOTE (DIGITAL) LOOPBACK

When the Register Control bit, REGEN, is disabled and the LPBKx pin is floating; or when the Register Control bit, REGEN, is enabled and the RLBK bit is set, RCLKx, RNEGx, and RPOSx outputs are internally looped back to the TCLKx, TNEGx, and TPOSx inputs respectively.

#### LINE BUILD-OUT

The Line Build-Out (LBO) function controls the transmit amplitude and pulse shape in DS3 and STS-1 modes. The selection of LBO depends on the amount of cable the transmitter is connected to. When less than 225 ft of cable is used, the corresponding LBOx pin or LBO bit should be high. When 225ft or more cable is used the corresponding LBO setting (LBOx pin or LBO bit) should be low. LBO can be controlled either from pins or from register settings, depending on the status of the Register Control bit, REGEN.

#### TRANSMIT ENABLE

The TXEN bit in the Mode Control Register controls the transmitter output. When logic zero, the transmitter output is disabled. This feature is used to disable ports as well as to multiplex two or more transceivers to one port. The transmitter of any port can also be disabled by floating the respective LBOx pin, in which case it will also power-down the entire transmitter. See section on the Power-Down Function for more info.

#### TRANSMIT MONITOR

The transmit monitor function detects activity on the transmitter output at the LOUTPx and LOUTNx pins. When there is a transmitter fault, in the case of an open or short on the chip, the transformer, or the circuit board, the transmit signal amplitude will be altered. The transmit monitor detects the amplitude of the driven signal. The TXNW signal (bit) goes high when the amplitude of the transmit signal is outside a valid amplitude range. When the signal amplitude is either too high or too low for longer than a specified duration, the TXNW bit goes high (See Transmit Monitor Specifications, pg.28). The TXNW signal can be also used to trigger an interrupt on the INTRx pin when serial interface control is not available.

#### JITTER ATTENUATOR

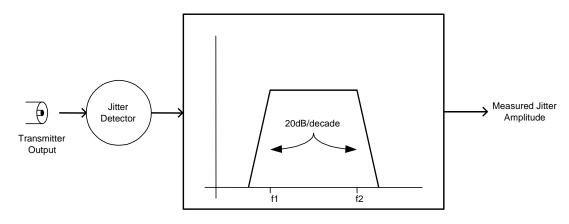

Jitter Attenuation function is provided on-chip. The Jitter Attenuator can be configured to be in the transmit or the receive path. When configured in the transmit path, the input clock at TCLK pin is passed through a very low bandwidth digital PLL. The corresponding transmit data is buffered into a FIFO and clocked out using the de-jittered output clock of the PLL. When configured in the receive path, the recovered clock is passed through the low bandwidth digital PLL, and the corresponding receive data is buffered into the FIFO and clocked out using the de-jittered clock.

The Jitter Attenuator can be configured independently for each channel by writing to the Jitter Attenuator Control Register (JACR) as follows:

| JAEN<br>bit | JASL<br>bit | Jitter Attenuator Mode                                  |  |  |

|-------------|-------------|---------------------------------------------------------|--|--|

| 0           | Х           | Jitter Attenuator disabled                              |  |  |

| 1           | 0           | Jitter Attenuator configured to be in the receive path  |  |  |

| 1           | 1           | Jitter Attenuator configured to be in the transmit path |  |  |

When serial interface control is not available, the MSL1 pin is provided for global Jitter Attenuator mode selection. Upon power-up or reset, the state of the MSL1 pin is sensed and mapped into the JAEN and JASL register bits for all channels, representing the appropriate mode of operation. After power-up or reset, the state of the MSL1 pin is ignored. The state of the MSL1 pin, and the corresponding Jitter Attenuator configuration is shown below.

| MSL1 pin | Jitter Attenuator Mode             |  |  |

|----------|------------------------------------|--|--|

| L        | Jitter Attenuator in receive path  |  |  |

| Н        | Jitter Attenuator in transmit path |  |  |

| Z        | Jitter Attenuator disabled         |  |  |

#### **PLL Bandwidth**

A PLL response with effectively one pole below 27 Hz is adequate to meet the ETSI TBR24 E3 standards. A PLL response with one pole below 40 Hz is adequate to meet the GR-499 (Cat I) DS3 standards. One of two bandwidths can be selected via register settings. The PLL bandwidth is proportional to the data rate as follows:

| Line Rate | JABW bit | PLL Bandwidth (Hz) |  |  |

|-----------|----------|--------------------|--|--|

| E3        | 0        | *13                |  |  |

|           | 1        | 188                |  |  |

| DS3       | 0        | *17                |  |  |

| D33       | 1        | 245                |  |  |

| STS1      | 0        | 20                 |  |  |

| 3131      | 1        | *283               |  |  |

\*The default state of the JABW bit depends on which line-rate is selected through the MSL0 pin. If E3 or DS3 mode is selected, the default state is '0'. If STS1 mode is selected, the default state is '1'.

#### **Elastic Store Depth**

To optimize the trade-off between data latency and clock wander tolerance, the FIFO elastic store depth can be selected through the serial port by writing to the Jitter Attenuator Control Register (JACR) as follows:

| ESP[1:0]<br>bits | Elastic Store Depth |  |

|------------------|---------------------|--|

| 00               | Pass-Through mode   |  |

| 01               | 16 UI               |  |

| 10               | 32 UI               |  |

| 11               | 64 UI (default)     |  |

The Elastic Store Depth selects the nominal FIFO read pointer address. The total or maximum elastic store depth is set to be twice as deep as the nominal pointer address. The circular buffer length is always twice as long as the nominal pointer address.

#### POWER-DOWN FUNCTION

Power-down control is provided to allow the transceivers to be shut off individually. Transmit and receive power-down can be set independently via the PDTX and PDRX bits in the Mode Control Register. Floating the respective LBOx pin can also set PDTX for each channel. The Serial Control Interface and Configuration Registers are not affected by power-down.

#### **INTERNAL POWER-ON RESET**

The 78P2343JAT includes on-chip Power-On Reset (POR) function to ensure the serial-port registers are initialized to known default states upon power-up. Roughly 50us after Vcc reaches 2.4V at power up, reset is released. This reset signal also sets all state machines within the LIU to nominal operational states. The internal reset signal is also brought out to the PORB pin. This pin is a multi-function pin that allows for the following:

- 1) Override the internal POR signal by driving in an external active-low reset signal;

- 2) Monitor the state of the internal POR signal (for test and debug only);

- Add external capacitor to delay the release of the internal power-on reset signal to allow the MSL0 pin to stabilize prior to release of reset (approximately 8µs per nF added).

The internal resistance of the PORB pin is approximately  $5k\Omega$ .

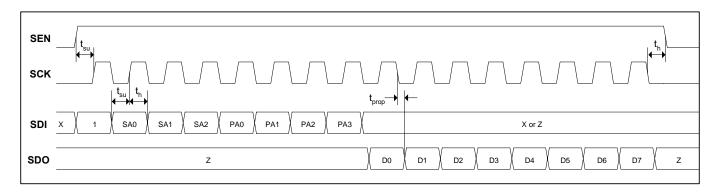

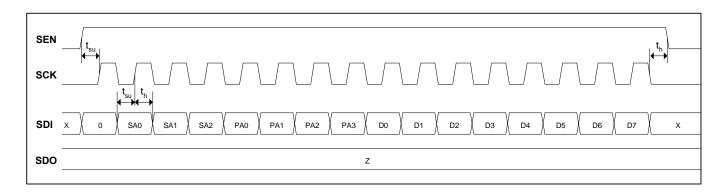

#### SERIAL CONTROL INTERFACE

The serial port controlled register allows a generic controller to interface with the 78P2343JAT. It is used for mode settings, diagnostics and test, and the retrieval of status and performance information.

The serial interface consists of four pins: Chip Select (CS), Serial Clock (SCK), Serial Data In (SDI), and Serial Data Out (SDO). The CS pin initiates the read and write operations. It can also be used to select a particular device allowing SCK, SDI and SDO to be bussed together. SCK is the clock input that times the data on SDI and SDO. Data on SDI is latched in on the rising-edge of SCK, and data on SDO is clocked out using the falling edge of SCK.

SDI is used to insert mode, address, and register data into the chip. Address and Data information are input least significant bit (LSB) first.

SDO is a tristate capable output. It is used to output register data during a read operation. SDO output is normally high impedance, and is enabled only during the duration when register data is being clocked out. Read data is clocked out least significant bit (LSB) first.

If SDI coming out of the micro-controller chip is also tristate capable, SDI and SDO can be connected together to simplify connections.

The maximum clock frequency for register access is 20MHz.

<u>Note</u>: To allow equipment to power up in a known state, some register defaults are set by their corresponding pin control at power-up.

#### **REGISTER DESCRIPTION**

#### **REGISTER ADDRESSING**

| Address Bits | Bit 7                              | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0          |

|--------------|------------------------------------|-------|-------|-------|-------|------------|-------|----------------|

|              | Port Address                       |       |       |       | S     | Sub-Addres | S     | Read/<br>Write |

| Assignment   | Assignment PA[3] PA[2] PA[1] PA[0] |       |       |       |       | SA[1]      | SA[0] | R/W*           |

#### **REGISTER TABLE**

#### a) PA[3:0] = 0: Global Registers

| Sub<br>Addr | Reg.<br>Name  | Description       | Bit 7        | Bit 6          | Bit 5         | Bit 4         | Bit 3        | Bit 2        | Bit 1       | Bit 0       |

|-------------|---------------|-------------------|--------------|----------------|---------------|---------------|--------------|--------------|-------------|-------------|

| 0           | MSCR<br>(R/W) | Master Control    | REGEN<br><0> | DS3<br><x></x> | E3<br><x></x> | ENDECB<br><0> | RCLKP<br><0> | TCLKP<br><0> |             | SRST<br><0> |

| 1           | INTC<br>(R/W) | Interrupt Control | INPOL<br><0> |                |               |               |              | JAER<br><0>  | RXER<br><1> | TXER<br><1> |

| 2           | RSVD          | Reserved          | -            |                |               |               |              |              |             |             |

| 3           | RSVD          | Reserved          | <0>          | <0>            | <0>           | <0>           | <0>          | <0>          | <0>         | <0>         |

| 4           | RSVD          | Reserved          |              |                |               |               |              |              |             |             |

| 5           | RSVD          | Reserved          |              |                |               |               |              |              |             |             |

| 6           | RSVD          | Reserved          | <0>          | <0>            | <0>           | <0>           | <0>          | <0>          | <0>         | <0>         |

| 7           | RSVD          | Reserved          | <0>          | <0>            | <0>           | <0>           | <0>          | <0>          | <0>         | <0>         |

#### b) PA[3:0] = 1-3: Port-Specific Registers

| Sub<br>Addr | Reg.<br>Name  | Description                  | Bit 7           | Bit 6           | Bit 5       | Bit 4        | Bit 3         | Bit 2         | Bit 1      | Bit 0           |

|-------------|---------------|------------------------------|-----------------|-----------------|-------------|--------------|---------------|---------------|------------|-----------------|

| 0           | MDCR<br>(R/W) | Mode Control                 | PDTX<br><0>     | PDRX<br><0>     | LBO<br><1>  | LLBKA<br><0> | LLBKB<br><0>  | RLBK<br><0>   | MON<br><0> | TXEN<br><1>     |

| 1           | STAT<br>(R/O) | Status Monitor               | FERR            | -               |             |              | LOS           | TXNW          |            | SGLO            |

| 2           | RSVD          | Reserved                     | <1>             | <1>             | <0>         | <1>          | <0>           | <1>           | <0>        | <0>             |

| 3           | JACR<br>(R/W) | Jitter Attenuator<br>Control | JAEN<br><x></x> | JASL<br><x></x> | JLBK<br><0> | <0>          | ESP[1]<br><1> | ESP[0]<br><1> | <0>        | JABW<br><x></x> |

| 4           | RSVD          | Reserved                     | -               | 1               | I           | 1            | 1             | ı             | ı          |                 |

| 5           | RSVD          | Reserved                     | <0>             | 1               | I           | <0>          | <0>           | <0>           | <0>        | <0>             |

| 6           | RSVD          | Reserved                     |                 | 1               | 1           |              |               | ı             | ı          |                 |

| 7           | RSVD          | Reserved                     | <0>             | <0>             | <0>         | <0>          | <0>           | <0>           | <0>        | <0>             |

<u>Note:</u> Shaded registers in Register Table are reserved for Teridian internal use only. Accessing reserved or undefined registers may cause undesirable operation.

## **REGISTER DESCRIPTION** (continued)

#### **LEGEND**

| TYPE | DESCRIPTION | TYPE | DESCRIPTION   |

|------|-------------|------|---------------|

| R/O  | Read only   | R/W  | Read or Write |

#### **GLOBAL REGISTERS**

#### ADDRESS 0-0: MASTER CONTROL REGISTER

| ВІТ | NAME    | TYPE  | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                    |

|-----|---------|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         |       |               | Register Control Enable:                                                                                                                                       |

| 7   | REGEN   | R/W   | 0             | 0: Pin selection overrides register settings                                                                                                                   |

| '   | INLOLIN | 17/77 | U             | 1: Device is controlled via register set.                                                                                                                      |

|     |         |       |               | NOTE: Pin 15 (ENDECB) must be tied low when REGEN is enabled.                                                                                                  |

|     |         |       |               | Line Speed Selection:                                                                                                                                          |

| 6   | DS3     | R/W   | X             | Selects the line speed of all channels as well as the input clock frequency at the CKREF pin.                                                                  |

|     |         |       |               | [DS3 E3] = 00 : STS-1 (51.840MHz)                                                                                                                              |

|     |         |       |               | 01: E3 (34.368MHz)                                                                                                                                             |

|     |         |       |               | 10 : DS3 (44.736MHz)                                                                                                                                           |

| 5   | E3      | R/W   | X             | 11 : STS-1 (51.840MHz)                                                                                                                                         |

|     |         |       |               | NOTE: The default values of these register bits depend on the state of the MSL0 pin upon power-up or reset.                                                    |

|     |         |       |               | Encoder/Decoder Disable:                                                                                                                                       |

|     | ENDECB  |       |               | 0 : selects NRZ digital data interface                                                                                                                         |

| 4   |         | R/W   | 0             | 1 : selects AMI digital data interface                                                                                                                         |

|     |         |       |               | NOTE: Relevant only when the REGEN bit is set. Otherwise, ENDECB pin selection prevails.                                                                       |

|     |         |       |               | RCLK Polarity Selection:                                                                                                                                       |

| 3   | RCLKP   | R/W   | 0             | 0: Receive Data clocked out on the falling-edge of RCLK                                                                                                        |

|     |         |       |               | 1: Receive Data clocked out on the rising-edge of RCLK                                                                                                         |

|     |         |       |               | TCLK Polarity Selection:                                                                                                                                       |

| 2   | TCLKP   | R/W   | 0             | 0: Transmit Data clocked in on the rising-edge of TCLK                                                                                                         |

|     |         |       |               | 1: Transmit Data clocked in on the falling-edge of TCLK                                                                                                        |

| 1   | RSVD    | R/O   |               | Reserved                                                                                                                                                       |

|     |         |       |               | Register Soft-Reset:                                                                                                                                           |

| 0   | SRST    | R/W   | 0             | When this bit is set, all registers are reset to their default values. Also resets Jitter Attenuator to "centered" states. This register bit is self-clearing. |

### **REGISTER DESCRIPTION** (continued)

#### ADDRESS 0-1: INTERRUPT CONTROL REGISTER

This register selects the events that would cause the respective interrupt pin (INTRx) for each of the ports to be activated. User may set as many bits as required.

| BIT | NAME  | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                    |

|-----|-------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | INPOL | R/W  | 0             | Interrupt Pin Polarity Selection:  0 : Interrupt output is active-low  1 : Interrupt output is active-high                                     |

| 6:3 | RSVD  | R/O  |               | Reserved                                                                                                                                       |

| 2   | JAER  | R/W  | 0             | Jitter Attenuator Error Event:  When set, JAT FIFO overflow or underflow (as indicated by the FERR bit) will cause an interrupt to be flagged. |

| 1   | RXER  | R/W  | 1             | Receiver Error Event:  When set, loss of receive signal (as indicated by the LOS bit) will cause an interrupt to be flagged.                   |

| 0   | TXER  | R/W  | 1             | Transmitter Error Event:  When set, transmitter fault (as indicated by the TXNW bit) will cause an interrupt to be flagged.                    |

### **REGISTER DESCRIPTION** (continued)

#### **PORT-SPECIFIC REGISTERS**

For PA[3:0] = N = 1-3 only. Accessing a register with port address greater than 3 constitutes an invalid command, and the read/write operation will be ignored.

#### ADDRESS N-0: MODE CONTROL REGISTER

| BIT | NAME  | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                                                                                                    |

|-----|-------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PDTX  | R/W  | 0             | Transmitter Power-Down:  0: Normal Operation  1: Power-Down  NOTE: Relevant only when the REGEN bit is set. Otherwise, LBOx pin selection prevails.                                                                                            |

| 6   | PDRX  | R/W  | 0             | Receiver Power-Down: 0: Normal Operation 1: Power-Down                                                                                                                                                                                         |

| 5   | LBO   | R/W  | 1             | Transmitter Line Build-Out (DS3 and STS-1 only):  0: ≥ 225ft of cable attached to the cross-connect  1: < 225ft of cable attached to the cross-connect  NOTE: Relevant only when the REGEN bit is set. Otherwise, LBOx pin selection prevails. |

| 4   | LLBKA | R/W  | 0             | Local (Analog) Loopback Mode Selection:  [LLBKA: LLBKB] = 00: Normal operation  01: Local (Analog) Loopback                                                                                                                                    |

| 3   | LLBKB | R/W  | 0             | 10 : Adjacent receiver input (see page 3) 11 : Adjacent transmitter loopback (see page 3)  NOTE: Relevant only when the REGEN bit is set. Otherwise, LPBKx pin selection prevails.                                                             |

| 2   | RLBK  | R/W  | 0             | Remote (Digital) Loopback Enable:  0: Normal Operation  1: Loops RCLK, RPOS, and RNEG back onto TCLK, TPOS, and TNEG  NOTE: Relevant only when the REGEN bit is set. Otherwise, LPBKx pin selection prevails.                                  |

| 1   | MON   | R/W  | 0             | Monitor Mode Enable: Used for reception of split-off signals that are flat attenuated by at least 16dB but no more than 20dB.  0: Disable 1: Enable                                                                                            |

| 0   | TXEN  | R/W  | 1             | Transmitter Output Enable:  0 : Transmit driver is disabled. Output is tri-stated.  1 : Normal Operation  NOTE: Relevant only when the REGEN bit is set. Otherwise, LBOx pin selection prevails.                                               |

### **REGISTER DESCRIPTION** (continued)

#### **ADDRESS N-1: STATUS MONITOR REGISTER**

| BIT | NAME | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                                                                                            |

|-----|------|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | FERR | R/O  | Х             | Jitter Attenuator FIFO Error Flag: This bit is set whenever a FIFO overflow or underflow occurred. It is reset after a read operation to this register.  0: Proper Operation 1: FIFO Overflow/Underflow                                |

| 6:4 | RSVD | R/O  | Х             | Reserved                                                                                                                                                                                                                               |

| 3   | LOS  | R/O  | Х             | Loss-of-Signal Indication:  0: Signal Detector detecting a valid receive input signal  1: Standards-based Loss-of-Signal indication  NOTE: RPOSx and RNEGx are forced low when LOS='1'. RCLK will continue to output a line rate clock |

| 2   | TXNW | R/O  | Х             | Transmitter Not-Working Indication:  0: Transmitter OK  1: Transmitter not working                                                                                                                                                     |

| 1   | RSVD | R/O  | Х             | Reserved                                                                                                                                                                                                                               |

| 0   | SGLO | R/O  | Х             | Signal Low Indication:  0 : Receive signal level OK  1 : Receive signal level too low / Loss of signal                                                                                                                                 |

## **REGISTER DESCRIPTION** (continued)

#### ADDRESS N-3: JITTER ATTENUATOR CONTROL REGISTER

| ВІТ | NAME         | TYPE | DFLT<br>VALUE | DESCRIPTION                                                                                                                                                                                                   |

|-----|--------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |              |      |               | Jitter Attenuator Enable: 0: Disables jitter attenuation function                                                                                                                                             |

| 7   | JAEN         | R/W  | X             | 1 : Enables jitter attenuation function                                                                                                                                                                       |

|     |              |      |               | NOTE: The default values of these register bits depend on the state of the MSL1 pin upon power-up or reset.                                                                                                   |

|     |              |      |               | Jitter Attenuation Selection:                                                                                                                                                                                 |

|     |              |      |               | 0: Jitter Attenuator on the receive path                                                                                                                                                                      |

| 6   | JASL         | R/W  | Х             | 1: Jitter Attenuator on the transmit path                                                                                                                                                                     |

|     |              |      |               | NOTE: The default values of these register bits depend on the state of the MSL1 pin upon power-up or reset.                                                                                                   |

|     |              |      |               | Jitter Attenuator Local Loopback Enable:                                                                                                                                                                      |

|     |              |      |               | 0 : Normal Operation                                                                                                                                                                                          |

| 5   | JLBK         | R/W  | 0             | 1 : TCLKx, TPOSx, TNEGx connected to JAT input and RCLKx, RPOSx, RNEGx connected to JAT output                                                                                                                |

|     |              |      |               | NOTE: If both RLBK and JLBK bits are set, RLBK mode takes priority.                                                                                                                                           |

| 4   | RSVD         | R/W  | 0             | Reserved. Must be set to zero.                                                                                                                                                                                |

|     |              |      |               | FIFO Elastic Store Pointer Selection:                                                                                                                                                                         |

|     | FOD          |      |               | ESP[1:0] = 00 : Pass-through                                                                                                                                                                                  |

| 3:2 | ESP<br>[1:0] | R/W  | 11            | 01: 8 UI                                                                                                                                                                                                      |

|     | [1.0]        |      |               | 10: 16 UI                                                                                                                                                                                                     |

|     |              |      |               | 11:32 UI (default)                                                                                                                                                                                            |

| 1   | RSVD         | R/W  | 0             | Reserved. Must be set to zero.                                                                                                                                                                                |

|     |              |      |               | Jitter Attenuator Bandwidth Selection:                                                                                                                                                                        |

|     |              |      |               | 0 : Low bandwidth                                                                                                                                                                                             |

|     |              |      |               | 1:High bandwidth                                                                                                                                                                                              |

| 0   | JABW         | R/W  | Х             | (see JAT Bandwidth Selection Table on page 5)                                                                                                                                                                 |

|     |              |      |               | NOTE: The default values of these register bits depend on the state of                                                                                                                                        |

|     |              |      |               | the MSL0 pin upon power-up or reset. If the state of the MSL0 pin selects E3 or DS3 mode, the default value of JABW is '0'. If the state of the MSL0 pin selects STS1 mode, the default value of JABW is '1'. |

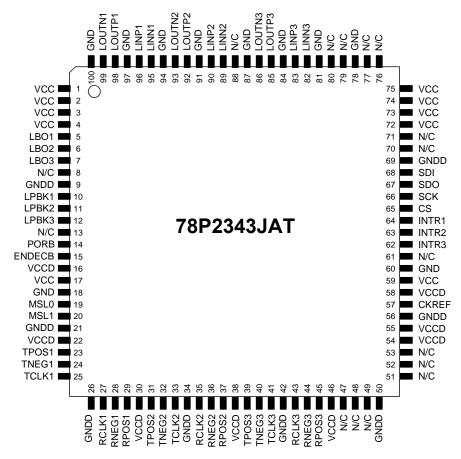

### **PIN DESCRIPTION**

#### **LEGEND**

| TYPE | DESCRIPTION                     | TYPE | DESCRIPTION                  |

|------|---------------------------------|------|------------------------------|

| Α    | Analog Pin                      | CIT  | CMOS 3-State Input           |

| CI   | CMOS Digital Input              | CO   | CMOS Digital Output          |

| CIU  | CMOS Digital Input w/ Pull-up   | COZ  | CMOS Tristate Digital Output |

| CID  | CMOS Digital Input w/ Pull-down | S    | Supply                       |

| CIS  | CMOS Schmitt Trigger Input      | G    | Ground                       |

#### TRANSMITTER PINS

| NAME    | PIN          | TYPE | DESCRIPTION                                                                                                                                                          |

|---------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |              | СІ   | Transmit Positive Data/Transmit NRZ:                                                                                                                                 |

| TPOSx   | 23, 31<br>39 |      | When ENDECB ='1', a logic one on this pin generates a positive AMI pulse on the coax. This pin should not be high at the same time that corresponding TNEGx is high. |

|         |              |      | When ENDECB ='0', data on this pin is encoded and converted into positive and negative AMI pulses.                                                                   |

|         |              |      | Transmit Negative Data:                                                                                                                                              |

| TNEGx   | 24, 32<br>40 | CI   | When ENDECB ='1', a logic one on this pin generates a negative AMI pulse on the coax. This pin should not be high at the same time that corresponding TPOSx is high. |

|         |              |      | When ENDECB ='0', this pin is ignored.                                                                                                                               |

|         | 25, 33       |      | Transmitter Clock Input:                                                                                                                                             |

| TCLKx   | 41           | CIS  | This signal is used to latch the respective TPOSx and TNEGx signals into the 78P2343JAT.                                                                             |

| LOUTE   | 98, 92       |      |                                                                                                                                                                      |

| LOUTPx  | 85           |      | Line Out:                                                                                                                                                            |

|         |              | Α    | Differential AMI Outputs. Requires a 1:2CT center-tapped                                                                                                             |

| LOUTNx  | 99, 93       |      | transformer and a shunt termination resistor. See APPLICATION INFORMATION section for more info.                                                                     |

| 2001110 | 86           |      |                                                                                                                                                                      |

## PIN DESCRIPTION (continued)

#### **RECEIVER PINS**

| NAME   | PIN          | TYPE | DESCRIPTION                                                                                                                                                    |

|--------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |              |      | Reference Clock Input:                                                                                                                                         |

| CKREF  | 57           | CIS  | This clock should be from a clean source (± 20 ppm) and match the selected line-rate frequency as follows:  E3: 34.368 MHz  DS3: 44.736 MHz  STS-1: 51.840 MHz |

|        |              |      | Receive Clock:                                                                                                                                                 |

| RCLKx  | 27, 35       | со   | Recovered receive clock output.                                                                                                                                |

| TOLIV. | 43           |      | NOTE: During LOS conditions, RCLKx will continue to output a line rate clock                                                                                   |

|        |              | со   | Receive Negative Data:                                                                                                                                         |

| DNEO   | 28, 36<br>44 |      | When ENDECB ='1', this pin indicates reception of a negative AMI pulse on the coax.                                                                            |

| RNEGx  |              |      | When ENDECB ='0', this pin outputs a one when a Receive Line Code Violation (RLCV) is detected.                                                                |

|        |              |      | NOTE: During LOS conditions, RNEGx output is squelched                                                                                                         |

|        |              |      | Receive Positive Data/NRZ Data:                                                                                                                                |

| RPOSx  | 29, 37       | СО   | When ENDECB ='1', this pin indicates reception of a positive AMI pulse on the coax cable.                                                                      |

|        | 45           |      | When ENDECB ='0', it outputs decoded NRZ data.                                                                                                                 |

|        |              |      | NOTE: During LOS conditions, RPOSx output is squelched                                                                                                         |

| LIND   | 96, 90       |      |                                                                                                                                                                |

| LINPx  | 83           |      | Line In:                                                                                                                                                       |

|        |              | Α    | Differential AMI Inputs. Should be 1:1 transformer-coupled and terminated with a shunt resistor. See APPLICATION INFORMATION                                   |

| LINNx  | 95, 89       |      | section for more info.                                                                                                                                         |

|        | 82           |      |                                                                                                                                                                |

### PIN DESCRIPTION (continued)

#### **CONTROL AND STATUS PINS**

| NAME   | PIN          | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                      |

|--------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSL0   | 19           | CIT  | Data-Rate Mode Selection:  Low = E3 mode  High = DS3 mode  Float = STS-1 mode  NOTE: Pin state is latched-in on rising-edge of PORB signal. Pin state is ignored after reset.                                                                                                    |

| MSL1   | 20           | CIT  | Jitter Attenuator Mode Selection:  Low = JAT in Receive path  High = JAT in Transmit path  Float = JAT is bypassed  NOTE: Pin state is latched-in on rising-edge of PORB signal. Pin state is ignored after reset.                                                               |

|        |              |      | Chip Reset (active-low):                                                                                                                                                                                                                                                         |

| PORB   | 14           | Α    | Forces hardware reset on device. See description on <i>Internal Power-on Reset</i> for complete use of this pin.                                                                                                                                                                 |

|        |              |      | ENDEC Enable (active-low):                                                                                                                                                                                                                                                       |

| ENDECB | 15           | CID  | Set high to disable internal ENDEC function. See description on B3ZS/HDB3 ENDEC with Line Code Violation Detect for complete use of this pin.                                                                                                                                    |

|        |              |      | NOTE: Relevant only when the REGEN bit is '0'. <i>Pin must be held low when the REGEN bit is set.</i>                                                                                                                                                                            |

| LBOx   | 5, 6<br>7    | CIT  | Line Build-Out:  Low = Used with 225ft or more of cable.  High = Used with less than 225ft of cable.  Float = Disable and power down transmitter. [TXEN=0; PDTX=1]  NOTE: LBO control relevant only when the REGEN bit is '0'. Pin state sampled approximately once every 0.5ms. |

| LPBKx  | 10, 11<br>12 | CIT  | Loopback Enable: Low = Normal Operation High = Local Loopback. Transmitter looped back to Receiver Float = Remote Loopback. Receiver looped back to Transmitter NOTE: Relevant only when the REGEN bit is '0'. Pin state sampled approximately once every 0.5ms.                 |

| INTRx  | 64, 63<br>62 | со   | Interrupt Flag: This pin is normally high when the INPOL bit is '0' (default), and normally low when the INPOL bit is '1'. When an interrupt event occurs (as defined in the Interrupt Control Register description), the respective INTRx pin will change state.                |

### PIN DESCRIPTION (continued)

#### **SERIAL-PORT PINS**

| NAME | PIN    | TYPE | DESCRIPTION                                                                                                                                                        |  |  |

|------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |        |      | Chip Select:                                                                                                                                                       |  |  |

| cs   | 65     | CI   | High during write and read operations. Low disables the serial port. While CS is low, SDO remains in high impedance state, and SDI and SCK activities are ignored. |  |  |

| SCK  | 66     | CIS  | Serial Clock:                                                                                                                                                      |  |  |

| SCK  | 66 CIS |      | Controls the timing of SDI and SDO.                                                                                                                                |  |  |

|      |        |      | Serial Data Input:                                                                                                                                                 |  |  |

| SDI  | 68     | CI   | Inputs mode and address information. Also inputs register data during a Write operation. Both address and data are input least significant bif first.              |  |  |

|      |        |      | Serial Data Output:                                                                                                                                                |  |  |

| SDO  | 67     | COZ  | Outputs register information during a Read operation. Data is output least significant bit first.                                                                  |  |  |

#### **POWER AND GROUND PINS**

It is recommended that all supply pins be connected to a single power supply plane and all ground pins be connected to a single ground plane.

| NAME | PINS                                       | TYPE | DESCRIPTION          |

|------|--------------------------------------------|------|----------------------|

| VCC  | 1, 2, 3, 4, 17, 59,<br>72, 73, 74, 75      | S    | Analog Power Supply  |

| GND  | 18, 60, 78, 81, 84,<br>87, 91, 94, 97, 100 | S    | Analog Ground        |

| VCCD | 16, 22, 30, 38, 46,<br>54, 55, 58          | S    | Digital Power Supply |

| GNDD | 9, 21, 26, 34, 42,<br>50, 56, 69           | S    | Digital Ground       |

### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation beyond these limits may permanently damage the device.

| PARAMETER                    | RATING                |

|------------------------------|-----------------------|

| Supply Voltage (VCC/VCCD)    | -0.5 to 4.0 VDC       |

| Storage Temperature          | -65 to 150 °C         |

| Junction Temperature         | -40 to 125 °C         |

| Pin Voltage (LOUTPx, LOUTNx) | VCC + 1.5 VDC         |

| Pin Voltage (all other pins) | -0.3 to (VCC+0.6) VDC |

| Pin Current                  | ±100 mA               |

#### **RECOMMENDED OPERATING CONDITIONS**

Unless otherwise noted all specifications are valid over these temperatures and supply voltage ranges.

| PARAMETER                     | RATING       |

|-------------------------------|--------------|

| DC Voltage Supply (VCC/VCCD)  | 3.0 to 3.6 V |

| Ambient Operating Temperature | -40 to 85°C  |

#### **DC CHARACTERISTICS:**

| PARAMETER                                                                   | SYMBOL | CONDITIONS                                   | MIN | NOM        | MAX        | UNIT |

|-----------------------------------------------------------------------------|--------|----------------------------------------------|-----|------------|------------|------|

| Supply Current All channels enabled; LBO=0                                  | ldd    | DS3/E3 mode  JAT Enabled:  JAT Disabled:     |     | 265<br>246 | 288<br>267 | mA   |

| Receive-only Supply Current All channels PDTX = 1                           | lddr   | DS3/E3 mode  JAT Enabled:  JAT Disabled:     |     | 118<br>97  | 128<br>105 | mA   |

| Transmit-only Supply Current All channels PDRX = 1; LBO=0                   | lddt   | DS3/E3 mode<br>JAT Enabled:<br>JAT Disabled: |     | 195<br>165 |            | mA   |

| Supply Current per Port (including transmitter current through transformer) | lddx   | DS3/E3 mode  JAT Enabled:  JAT Disabled:     |     | 82<br>76   |            | mA   |

| Power-Down Current                                                          | Iddq   | PDTX = 1, PDRX = 1                           |     | 20         | 30         | mA   |

### **ELECTRICAL SPECIFICATIONS** (continued)

#### **ANALOG PINS CHARACTERISTICS:**

The following table is provided for informative purpose only. Not tested in production.

| PARAMETER                                    | SYMBOL | CONDITIONS       | MIN | NOM  | MAX | UNIT |

|----------------------------------------------|--------|------------------|-----|------|-----|------|

| LINPx and LINNx<br>Common-Mode Bias Voltage  | Vblin  | Ground reference | 1.9 | 2.25 | 2.6 | V    |

| LINPx and LINNx Differential Input Impedance | Rilin  |                  |     | 10   |     | kΩ   |

| PORB Input Impedance                         | Ripor  |                  |     | 5    |     | kΩ   |

#### **DIGITAL I/O CHARACTERISTICS:**

#### Pins of type CI, CIU, CID:

| PARAMETER            | SYMBOL   | CONDITIONS    | MIN | NOM | MAX | UNIT |

|----------------------|----------|---------------|-----|-----|-----|------|

| Input Voltage Low    | Vil      |               |     |     | 0.8 | V    |

| Input Voltage High   | Vih      |               | 2.0 |     |     | V    |

| Input Current        | lil, lih |               | -1  |     | 1   | μΑ   |

| Pull-up Resistance   | Rpu      | Type CIU only | 32  | 56  | 84  | kΩ   |

| Pull-down Resistance | Rpd      | Type CID only | 32  | 56  | 84  | kΩ   |

| Input Capacitance    | Cin      |               |     | 8   |     | pF   |

#### Pins of type CIS:

| PARAMETER             | SYMBOL   | CONDITIONS | MIN | NOM | MAX | UNIT |

|-----------------------|----------|------------|-----|-----|-----|------|

| Low-to-High Threshold | Vt+      |            | 1.3 |     | 1.7 | V    |

| High-to-Low Threshold | Vt-      |            | 0.8 |     | 1.2 | V    |

| Input Current         | lil, lih |            | -1  |     | 1   | μΑ   |

| Input Capacitance     | Cin      |            |     | 8   |     | pF   |

### Pins of type CIT:

| PARAMETER                                           | SYMBOL | CONDITIONS | MIN | NOM | MAX | UNIT |

|-----------------------------------------------------|--------|------------|-----|-----|-----|------|

| Input Voltage Low                                   | Vtil   |            |     |     | 0.8 | V    |

| Input Voltage High                                  | Vtih   |            | 2.0 |     |     | V    |

| Minimum impedance to be considered as "float" state | Rtiz   |            | 30  |     |     | kΩ   |

#### Pins of type CO and COZ:

| PARAMETER                          | SYMBOL | CONDITIONS                      | MIN | NOM | MAX | UNIT |

|------------------------------------|--------|---------------------------------|-----|-----|-----|------|

| Output Voltage Low                 | Vol    | IoI = 8mA                       |     |     | 0.4 | V    |

| Output Voltage High                | Voh    | Ioh = -8mA                      | 2.4 |     |     | V    |

| Output Transition Time             | Tt     | C <sub>L</sub> = 20pF; (20-80%) |     |     | 6   | ns   |

| Pin Capacitance                    | Cout   |                                 |     | 8   |     | pF   |

| Effective Source Impedance         | Rsrc   |                                 |     | 30  |     | Ω    |

| Tristate Output Leakage<br>Current | lz     | Type COZ only                   | -1  |     | 1   | μΑ   |

### **ELECTRICAL SPECIFICATIONS** (continued)

#### **SERIAL-PORT TIMING CHARACTERISTICS:**

| PARAMETER                    | SYMBOL            | CONDITION | MIN | TYP | MAX | UNIT |

|------------------------------|-------------------|-----------|-----|-----|-----|------|

| CS or SDI to SCK setup time  | t <sub>su</sub>   |           | 4   |     |     | ns   |

| CS or SDI to SCK hold time   | t <sub>h</sub>    |           | 4   |     |     | ns   |

| SCK to SDO propagation delay | t <sub>prop</sub> |           | 5   |     | 12  | ns   |

| SCK Frequency                | SCK               |           |     |     | 20  | MHz  |

### **Read Operation**

**Write Operation**

#### TRANSMIT TIMING CHARACTERISTICS:

| PARAMETER        | SYMBOL   | CONDITIONS | MIN | NOM | MAX | UNIT |

|------------------|----------|------------|-----|-----|-----|------|

| Clock Duty Cycle | TTC/TTCF |            | 40  |     | 60  | %    |

| Setup Time       | TTDxS    |            | 2.5 |     |     | ns   |

| Hold Time        | TTDxH    |            | 2.5 |     |     | ns   |

#### TIMING DIAGRAM: Transmitter Waveforms (E3/DS3/STS-1)

#### **RECEIVE TIMING CHARACTERISTICS:**

| PARAMETER                               | SYMBOL   | CONDITIONS                 | MIN  | NOM | MAX | UNIT |

|-----------------------------------------|----------|----------------------------|------|-----|-----|------|

| CKREF Duty Cycle                        |          |                            | 40   |     | 60  | %    |

| CKREF Frequency Stability               |          | w.r.t. line-rate frequency | -20  |     | +20 | ppm  |

| RCLK Duty Cycle                         | TRC/TRCF |                            | 40   |     | 60  | %    |

| Data Propagation Delay                  | TPROP    |                            | -0.3 |     | 3   | ns   |

| Descive Loss of Signal                  |          | E3 mode                    | 10   | 140 | 255 | UI   |

| Receive Loss of Signal Assert Timing    |          | DS3 mode                   | 100  | 150 | 250 | UI   |

| Assert filling                          |          | STS1 mode                  | 2.3  | 3   | 100 | μS   |

|                                         |          | E3 mode                    | 10   | 130 | 255 | UI   |

| Receive Loss of Signal De-assert Timing |          | DS3 mode                   | 100  | 130 | 250 | UI   |

|                                         |          | STS1 mode, see<br>Note 1   | 2.3  | 3   | 250 | μS   |

Note 1: At least a  $100\mu S$  of software delay must be added after STS-1 LOS de-assertion to be compliant with the ANSI T1.231 requirement of 100 to  $250\mu S$ .

#### TIMING DIAGRAM: Receive Waveforms (E3/DS3/STS-1)

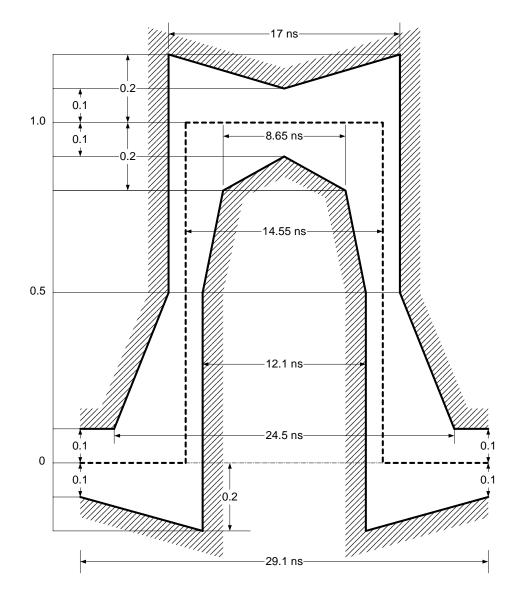

#### **E3 - TRANSMITTER SPECIFICATIONS**

| PARAMETER                       | CONDITION (see timing diagram)                                                   | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Transmitter Amplitude           | Measured at 0ft of terminated 75ohm cable.                                       | 900  | 1000 | 1100 | mVpk |

| Transmitter Amplitude Mismatch  | Ratio of amplitudes of positive and negative pulses measured at pulse centers    | 0.95 |      | 1.05 |      |

| Transmitter Pulsewidth Mismatch | Ratio of widths of positive and negative pulses measured at pulse half amplitude | 0.95 |      | 1.05 |      |

| Transmitter Pulsewidth          | Measured at 0ft of terminated 75ohm cable.                                       | 12.1 | 14.8 | 17   | ns   |

#### **DS3 - TRANSMITTER SPECIFICATIONS**

| PARAMETER                       | CONDITION                                                                    | MIN  | TYP | MAX  | UNIT |

|---------------------------------|------------------------------------------------------------------------------|------|-----|------|------|

| Transmitter Amplitude           | Measured at Oft of terminated 75ohm cable with LBO pin held high (enabled).  | 700  | 800 | 850  | mVpk |

| Transmitter Amplitude Mismatch  | Ratio of amplitudes of positive and negative pulses measured at pulse peaks. | 0.9  |     | 1.1  |      |

| Transmitter Power at 22.368 MHz | All ones pattern, 3kHz bandwidth                                             | -1.8 |     | +5.7 | dBm  |

| Harmonic Power<br>at 44.736 MHz | All ones pattern<br>Power below fundamental at<br>22.368MHz                  |      |     | -20  | dBm  |

#### **STS-1 - TRANSMITTER SPECIFICATIONS**

| PARAMETER                      | CONDITION                                                                    | MIN  | TYP | MAX  | UNIT |

|--------------------------------|------------------------------------------------------------------------------|------|-----|------|------|

| Transmitter Amplitude          | Measured at 0ft of terminated 75ohm cable with LBO pin held high (enabled).  | 700  | 825 | 950  | mVpk |

| Transmitter Amplitude Mismatch | Ratio of amplitudes of positive and negative pulses measured at pulse peaks. | 0.9  |     | 1.1  |      |

| Transmitter Power              | PRBS15 pattern band-limited to 207.36MHz.                                    | -2.7 |     | +4.7 | dBm  |

#### **E3 TRANSMIT PULSE TEMPLATE**

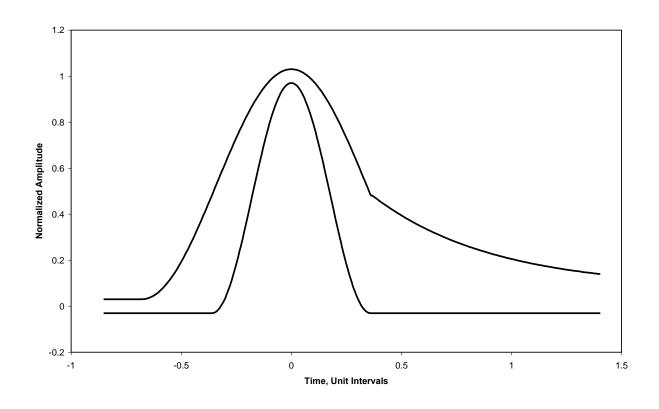

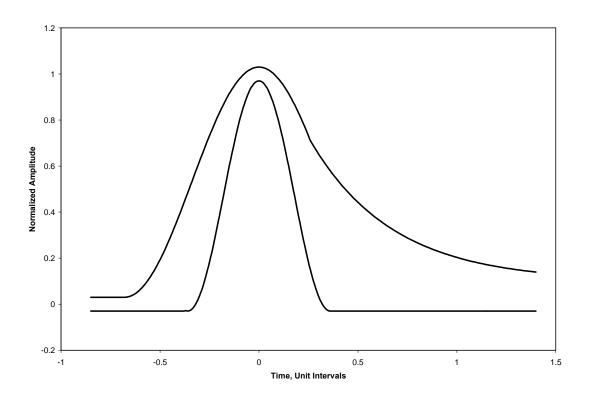

#### **DS3 TRANSMIT PULSE TEMPLATE**

| Time axis range (UI)                  | Normalized amplitude equation               |  |  |  |

|---------------------------------------|---------------------------------------------|--|--|--|

| UPPER CURVE                           |                                             |  |  |  |

| -0.85 <u>&lt;</u> T <u>&lt;</u> -0.68 | 0.03                                        |  |  |  |

| -0.68 <u>&lt;</u> T <u>&lt;</u> 0.36  | $0.03 + 0.5\{1+\sin[(pi/2)(1+T/0.34)]\}$    |  |  |  |

| 0.36 ≤ T ≤ 1.4                        | 0.08+0.407 e <sup>-1.84(T-0.36)</sup>       |  |  |  |

|                                       | LOWER CURVE                                 |  |  |  |

| -0.85 <u>&lt;</u> T <u>&lt;</u> -0.36 | -0.03                                       |  |  |  |

| -0.36 <u>&lt;</u> T <u>&lt;</u> 0.36  | $-0.03 + 0.5\{1+\sin[(pi/2)(1 + T/0.18)]\}$ |  |  |  |

| 0.36 ≤ T ≤ 1.4                        | -0.03                                       |  |  |  |

### **ELECTRICAL SPECIFICATIONS** (continued)

#### **STS-1 TRANSMIT PULSE TEMPLATE**

#### STS-1 (Transmit template specs)

| Time axis range (T)                   | Normalized amplitude equation (A)      |  |  |  |

|---------------------------------------|----------------------------------------|--|--|--|

| UPPER CURVE                           |                                        |  |  |  |

| -0.85 <u>&lt;</u> T <u>&lt;</u> -0.68 | 0.03                                   |  |  |  |

| -0.68 ≤ T ≤ 0.26                      | 0.03 + 0.5{1+sin[(pi/2)(1+T/0.34)]}    |  |  |  |

| 0.26 <u>&lt;</u> T <u>&lt;</u> 1.4    | 0.1+0.61 e <sup>-2.4(T-0.26)</sup>     |  |  |  |

|                                       | LOWER CURVE                            |  |  |  |

| -0.85 ≤ T ≤ -0.38                     | -0.03                                  |  |  |  |

| -0.38 ≤ T ≤ 0.36                      | -0.03 + 0.5{1+sin[(pi/2)(1 + T/0.18)]} |  |  |  |

| 0.36 <u>&lt;</u> T <u>&lt;</u> 1.4    | -0.03                                  |  |  |  |

#### TRANSMITTER OUTPUT JITTER

The transmit jitter specification ensures compliance with ITU-T G.823 and G.824, Telcordia GR-499 CORE(I) and GR-253-CORE, and ANSI T1.102-1993 for all supported rates. Transmit output jitter is guaranteed only if a clean SONET quality transmit clock source is used.

| PARAMETER                 | CONDITION         | MIN | NOM | MAX  | UNIT |

|---------------------------|-------------------|-----|-----|------|------|

| Transmitter Output Jitter | 10 Hz to 800 kHz  |     |     | 0.15 | Ulpp |

|                           | 10 kHz to 800 kHz |     |     | 0.08 | Ulpp |

Note: Filters defined by standards are used for all testing

#### **ELECTRICAL SPECIFICATIONS** (continued)

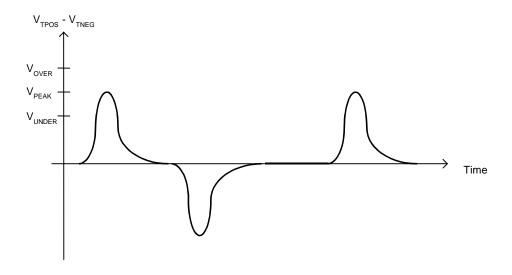

#### TRANSMIT MONITOR SPECIFICATIONS

The transmit monitor function looks at the signals on the LOUTPx and LOUTNx pins and checks for the existence of a valid signal. The monitor detects the peak of the transmitted signal at the LOUTPx and LOUTNx pins and checks that it is between  $V_{\text{UNDER}}$  and  $V_{\text{OVER}}$  at all times. If the peak level is within the voltage threshold window, the TXNW signal is low. If the peak level falls outside of the threshold limits for more than approximately 25 bit times, the TXNW signal goes high.

| PARAMETER          | CONDITION                              | MIN | TYP  | MAX | UNIT |

|--------------------|----------------------------------------|-----|------|-----|------|

| V <sub>UNDER</sub> | DS3/STS-1 mode with LBOx=1             |     | 450  |     | mVpk |

|                    | E3 mode;<br>DS3/STS-1 mode with LBOx=0 |     | 550  |     | mVpk |

| V <sub>OVER</sub>  | DS3/STS-1 mode with LBOx=1             |     | 1050 |     | mVpk |

|                    | E3 mode;<br>DS3/STS-1 mode with LBOx=0 |     | 1480 |     | mVpk |

DS3/STS-1 -- RECEIVER SPECIFICATIONS (Transformer-coupled)

| PARAMETER                  | CONDITION                                  | MIN | TYP | MAX  | UNIT   |

|----------------------------|--------------------------------------------|-----|-----|------|--------|

|                            | MON=0;                                     |     |     |      |        |

|                            | Signal at DSX is 360-850 mVpk.             | 90  |     | 850  | mVpk   |

| Peak Differential Input    | (see Note 2)                               |     |     |      |        |

| Amplitude, LINPx and LINNx | MON=1                                      | 25  |     | 80   | m\/nlc |

| (see Note 1)               | (see Note 3)                               | 25  |     | 80   | mVpk   |

|                            | MON=0; DS3-HIGH                            | 00  |     | 1200 | m\/nlc |

|                            | (see Note 4)                               | 90  |     | 1200 | mVpk   |

| Clat loss Telerones        | MON=0.                                     | 0   |     | 6    | dB     |

| Flat-loss Tolerance        | All valid cable lengths.                   |     |     | 6    | uБ     |

|                            | DS3 mode with 10 Hz - 400 kHz              |     |     |      |        |

| Receive Clock Jitter       | a) Normal receive mode                     |     |     | 0.1  | Ulpp   |

|                            | b) Remote loopback mode                    |     |     | 0.06 | Ulpp   |

| Interfering Tone Tolerance | Maximum ratio of Interference Power        |     |     |      |        |

| (see Note 5)               | to Signal Power for BER < 10 <sup>-8</sup> |     |     |      |        |

|                            | a) With 0ft cable from DSX                 |     | -9  |      | dB     |

|                            | b) With 450ft cable from DSX               |     | -10 |      | dB     |

- Note 1: Signal source should meet DS3 template of ANSI-T102.1993 Figure 4 and STS-1 template of ANSI-T102.1993 Figure 5. Loss characteristics of the WE728A or RG59B cable should be better than Figure C2 of ANSI-T102.1993.

- Note 2: Min spec corresponds to minimum DSX amplitude, 5.5dB of cable loss (450ft) and 6dB of flat attenuation. Error-free receiver performance is guaranteed for up to 600ft of cable from DSX cross-connect. Typical part can handle up to 900ft.

- Note 3: Min spec corresponds to amplitude of 425mVpk at DSX, 5.5dB of cable loss (450ft) and 20dB of flat attenuation. In monitor mode, interfering tone performance is not guaranteed.

- Note 4: In this mode, <u>no</u> noise, jitter, or interfering tone impairments should be added for guaranteed receiver performance.

- Note 5: Interfering signal is a non-synchronous sinusoidal tone of 22.368MHz for DS3 or 25.92MHz for STS-1. Data is a PRBS15 (2<sup>15</sup>-1) pattern.

#### **ELECTRICAL SPECIFICATIONS** (continued)

#### E3 - RECEIVER SPECIFICATIONS (Transformer-coupled)

| PARAMETER                               | CONDITION                                                                      | MIN | TYP | MAX  | UNIT   |

|-----------------------------------------|--------------------------------------------------------------------------------|-----|-----|------|--------|

|                                         | MON=0                                                                          | 120 |     | 1200 | m\/nlc |

| Peak Differential Input                 | (See Note 1)                                                                   | 120 |     | 1200 | mVpk   |

| Amplitude, LINPx and LINNx              | MON=1                                                                          | 25  |     | 100  | m\/nlc |

|                                         | (See Note 2)                                                                   | 25  |     | 100  | mVpk   |

| Flat-loss Tolerance                     | MON=0.                                                                         | 0   |     | 6    | dB     |

| l lat-1033 l'olerance                   | All valid cable lengths.                                                       | U   |     | O    | uБ     |

|                                         | With 100Hz-800kHz filter:                                                      |     |     |      |        |

| Receive Clock Jitter                    | a) Normal receive mode                                                         |     |     | 0.1  | Ulpp   |

|                                         | b) Remote loopback mode                                                        |     |     | 0.06 | Ulpp   |