# Charge Pump, 7-Channel Fun Lighting LED Driver

**ADP8863**

#### **FEATURES**

Automated blinking and funlight timing for each LED driver 16 programmable fade in and fade out times

0.1 sec to 5.5 sec

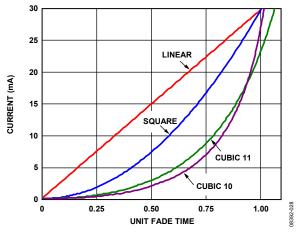

Selectable linear, square, or cubic fade rates

7 independent and programmable LED drivers

7 drivers capable of 30 mA (maximum)

1 driver also capable of 60 mA (maximum)

Programmable maximum current limit (128 levels)

Separate and independent controls for backlight LEDs

**Backlight fade override**

Up to two built-in comparator inputs with programmable modes for ambient light sensing

Charge pump with automatic gain selection of  $1\times$ ,  $1.5\times$ , and  $2\times$  for maximum efficiency

Standby mode for <1 µA current consumption

I<sup>2</sup>C-compatible interface for all programming

Dedicated reset pin and built-in power-on reset (POR)

Short-circuit, overvoltage, and overtemperature protection

Internal soft start to limit inrush currents

Input-to-output isolation during faults or shutdown

Operation down to  $V_{\text{IN}} = 2.5 \, \text{V}$  with undervoltage lockout

(UVLO) at  $V_{IN} = 2.0 \text{ V}$

Small lead frame chip scale package (LFCSP)

#### **APPLICATIONS**

LED indication

Funlight indicator lighting

Keypad backlighting

RGB LED color generation and mixing

General backlighting of small format displays

#### **GENERAL DESCRIPTION**

The ADP8863 combines a powerful charge pump driver with advanced autonomous LED lighting features. It allows as many as seven LEDs to be independently driven up to 30 mA (maximum). The seventh LED can also be driven to 60 mA (maximum). All LEDs are programmable for maximum current and fade in/fade out times via the I<sup>2</sup>C interface.

Additionally, automated blinking routines can be independently programmed and enabled for all seven LED channels. These LEDs can also be combined into groups to reduce the processor instructions.

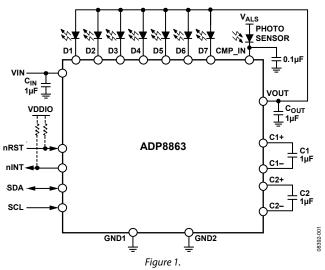

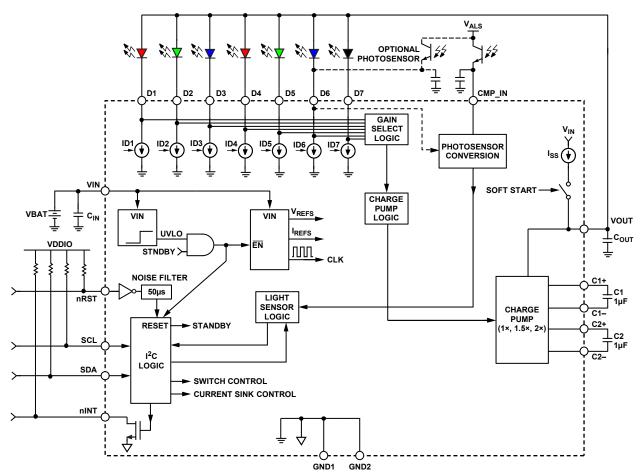

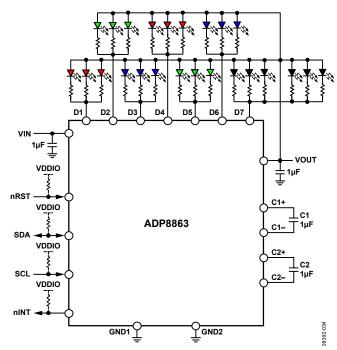

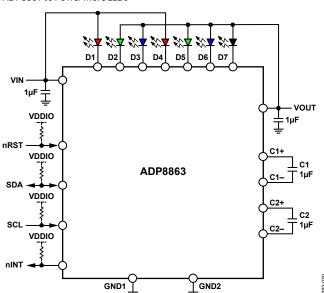

#### TYPICAL OPERATING CIRCUIT

This entire configuration is driven by a two-capacitor charge pump with gains of  $1\times$ ,  $1.5\times$ , and  $2\times$ . The charge pump is capable of driving a maximum  $I_{OUT}$  of 240 mA from a supply of 2.5 V to 5.5 V. The device includes a variety of safety features including short-circuit, overvoltage, and overtemperature protection. These features allow easy implementation of a safe and robust design. Additionally, input inrush currents are limited via an integrated soft start combined with controlled input-to-output isolation.

The ADP8863 is available in a compact lead frame chip scale package (LFCSP).

# **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Typical Operating Circuit                   | 1 |

| General Description                         | 1 |

| Revision History                            | 2 |

| Specifications                              | 3 |

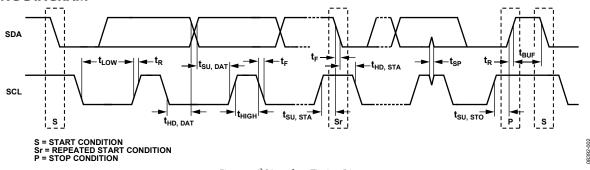

| I <sup>2</sup> C Timing Diagram             | 4 |

| Absolute Maximum Ratings                    | 5 |

| Maximum Temperature Ranges                  | 5 |

| Thermal Resistance                          | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

| Typical Performance Characteristics         | 7 |

| Theory of Operation1                        | 1 |

| Power Stage1                                | 2 |

| Operating Modes1                            | 3 |

| LED Groupings1                              | 4 |

| LED Current Settings1                       | 4 |

| Automated Fade In and Fade Out1             | 4 |

| Independent Sink Control1                   | 5 |

| RGB Color Generation1                       | 5 |

| Automated RGB Color Fades                        |

|--------------------------------------------------|

| Backlight Operating Levels                       |

| Backlight Turn On/Turn Off/Dim16                 |

| Automatic Dim and Turn Off Timers                |

| Fade Override                                    |

| Ambient Light Sensing17                          |

| Automatic Backlight Adjustment                   |

| Using the ADP8863 to Drive Additional LEDs 19    |

| Operating LEDs from Alternative Supplies         |

| Short-Circuit Protection Mode21                  |

| Overvoltage Protection                           |

| Thermal Shutdown/Overtemperature Protection      |

| Interrupts21                                     |

| Applications Information                         |

| Layout Guidelines                                |

| I <sup>2</sup> C Programming and Digital Control |

| Backlight Register Descriptions                  |

| Independent Sink Register Descriptions           |

| Comparator Register Descriptions                 |

| Outline Dimensions                               |

| Ordering Guide48                                 |

# **REVISION HISTORY**

4/10—Revision 0: Initial Version

# **SPECIFICATIONS**

VIN = 3.6 V, SCL = 2.7 V, SDA = 2.7 V, nINT = open, nRST = 2.7 V, CMP\_IN = 0 V,  $V_{Dl:D7}$  = 0.4 V, Capacitor C1 = 1  $\mu$ F, Capacitor C2 = 1  $\mu$ F, Capacitor C2 = 1  $\mu$ F, typical values are at  $T_A$  = 25°C and are not guaranteed, minimum and maximum limits are guaranteed from  $T_A$  = -40°C to +85°C, unless otherwise noted.

Table 1.

| Parameter                                           | Symbol                  | Test Conditions/Comments                                                               | Min   | Тур  | Max  | Unit  |

|-----------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|-------|------|------|-------|

| SUPPLY                                              |                         |                                                                                        |       | •    |      |       |

| Input Voltage                                       |                         |                                                                                        |       |      |      |       |

| Operating Range                                     | $V_{IN}$                |                                                                                        | 2.5   |      | 5.5  | V     |

| Start-Up Level                                      | V <sub>IN(START)</sub>  | V <sub>IN</sub> increasing                                                             |       | 2.05 | 2.30 | V     |

| Low Level                                           | V <sub>IN(STOP)</sub>   | V <sub>IN</sub> decreasing                                                             | 1.75  | 1.97 |      | V     |

| V <sub>IN(START)</sub> Hysteresis                   | V <sub>IN(HYS)</sub>    | After startup                                                                          |       | 80   |      | mV    |

| UVLO Noise Filter                                   | t <sub>UVLO</sub>       |                                                                                        |       | 10   |      | μs    |

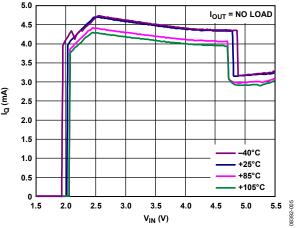

| Quiescent Current                                   | lo                      |                                                                                        |       |      |      |       |

| Prior to V <sub>IN(START)</sub>                     | I <sub>Q(START)</sub>   | $V_{IN} = V_{IN(START)} - 100 \text{ mV}$                                              |       | 10   |      | μΑ    |

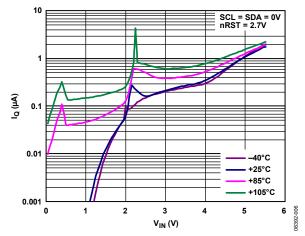

| During Standby                                      | I <sub>O(STBY)</sub>    | $V_{IN} = 3.6 \text{ V}$ , Bit nSTBY = 0, SCL = SDA = 0 V                              |       | 0.3  | 1.0  | μΑ    |

| After Startup and Switching                         | I <sub>Q(ACTIVE)</sub>  | $V_{IN} = 3.6 \text{ V, Bit nSTBY} = 1$ , $I_{OUT} = 0 \text{ mA}$ , $gain = 2 \times$ |       | 4.5  | 7.2  | mA    |

| OSCILLATOR                                          |                         |                                                                                        |       |      |      |       |

| Switching Frequency                                 | f <sub>sw</sub>         |                                                                                        | 0.8   | 1    | 1.32 | MHz   |

| Duty Cycle                                          | D                       |                                                                                        |       | 50   |      | %     |

| OUTPUT CURRENT CONTROL                              |                         |                                                                                        |       |      |      |       |

| Maximum Drive Current                               | I <sub>D1:D7(MAX)</sub> | $V_{D1:D7} = 0.4 \text{ V}$                                                            |       |      |      |       |

| D1 to D7                                            |                         | Bit SCR = 0 in the ISC7 register                                                       |       |      |      |       |

| T <sub>1</sub> = 25°C                               |                         |                                                                                        | 26.2  | 30   | 34.1 | mA    |

| $T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                         |                                                                                        | 24.4  |      | 34.1 | mA    |

| D7 Only (60 mA Setting)                             | I <sub>D7(60 mA)</sub>  | $V_{D7} = 0.4 \text{ V}$ , Bit SCR = 1 in the ISC7 register                            |       |      |      |       |

| T <sub>1</sub> = 25°C                               | 57(001111)              |                                                                                        | 52.5  | 60   | 67   | mA    |

| $T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                         |                                                                                        | 48.8  |      | 67   | mA    |

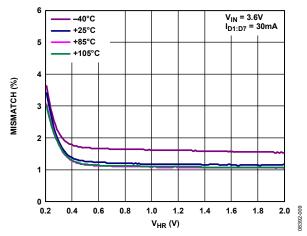

| LED Current Source Matching <sup>1</sup>            | I <sub>MATCH</sub>      |                                                                                        | 10.00 |      |      |       |

| All Current Sinks                                   | I <sub>MATCH7</sub>     | $V_{D1:D7} = 0.4 \text{ V}$                                                            |       | 2.0  |      | %     |

| D2 to D7 Current Sinks                              | I <sub>MATCH6</sub>     | $V_{D2:D7} = 0.4 \text{ V}$                                                            |       | 1.5  |      | %     |

| Leakage Current on LED Pins                         | I <sub>D1:D7(LKG)</sub> | $V_{IN} = 5.5 \text{ V}, V_{D1:D7} = 2.5 \text{ V}, \text{ Bit nSTBY} = 1$             |       |      | 0.5  | μΑ    |

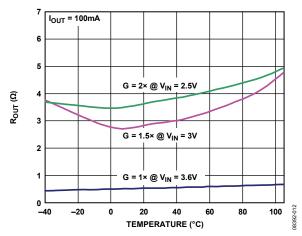

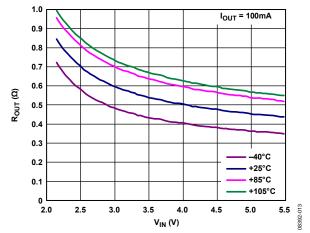

| Equivalent Output Resistance                        | Rout                    |                                                                                        |       |      | 0.0  | P., . |

| Gain = $1\times$                                    | 1.001                   | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 100 mA                                     |       | 0.5  |      | Ω     |

| Gain = $1.5 \times$                                 |                         | $V_{IN} = 3.1 \text{ V, } I_{OUT} = 100 \text{ mA}$                                    |       | 3.0  |      | Ω     |

| Gain = 2×                                           |                         | $V_{IN} = 2.5 \text{ V, } I_{OUT} = 100 \text{ mA}$                                    |       | 3.8  |      | Ω     |

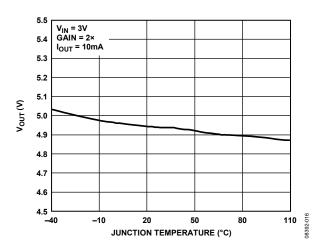

| Regulated Output Voltage                            | V <sub>OUT(REG)</sub>   | $V_{IN} = 3 \text{ V, gain} = 2 \times \text{, } I_{OUT} = 10 \text{ mA}$              | 4.3   | 4.9  | 5.5  | V     |

| AUTOMATIC GAIN SELECTION                            | - 001(1120)             |                                                                                        |       |      |      |       |

| Minimum Voltage                                     |                         |                                                                                        |       |      |      |       |

| Gain Increases                                      | V <sub>HR(UP)</sub>     | Decrease V <sub>D1:D7</sub> until the gain switches up                                 | 162   | 200  | 276  | mV    |

| Minimum Current Sink Headroom<br>Voltage            | V <sub>HR(MIN)</sub>    | $I_{DX} = I_{DX(MAX)} \times 95\%$                                                     |       | 180  | 2, 0 | mV    |

| Gain Delay                                          | t <sub>GAIN</sub>       | The delay after gain has changed and before gain is allowed to change again            |       | 100  |      | μs    |

| AMBIENT LIGHT SENSING                               |                         |                                                                                        |       |      |      |       |

| COMPARATORS                                         |                         |                                                                                        |       |      |      |       |

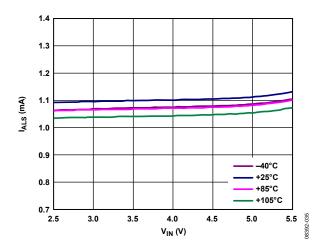

| Ambient Light Sensor Current                        | I <sub>ALS</sub>        | $CMP_IN = V_{D6} = 2.8 \text{ V, Bit CMP2\_SEL} = 1$                                   | 0.70  | 1.08 | 1.33 | mA    |

| DAC Bit Step                                        |                         |                                                                                        |       |      |      |       |

| Threshold L2 Level                                  | I <sub>L2BIT</sub>      | $I_{L2BIT} = I_{ALS}/250$                                                              |       | 4.3  |      | μΑ    |

| Threshold L3 Level                                  | I <sub>L3BIT</sub>      | $I_{L3BIT} = I_{ALS}/2000$                                                             |       | 0.54 |      | μΑ    |

| FAULT PROTECTION                                    |                         |                                                                                        |       |      |      |       |

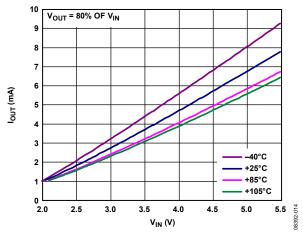

| Start-Up Charging Current Source                    | Iss                     | $V_{IN} = 3.6 \text{ V, } V_{OUT} = 0.8 \times V_{IN}$                                 | 2.5   | 3.75 | 5.5  | mΑ    |

| Parameter                                               | Symbol                  | Test Conditions/Comments                                        | Min                     | Тур                  | Max | Unit |

|---------------------------------------------------------|-------------------------|-----------------------------------------------------------------|-------------------------|----------------------|-----|------|

| Output Voltage Threshold                                | Vout                    |                                                                 |                         |                      |     |      |

| Exit Soft Start                                         | V <sub>OUT(START)</sub> | V <sub>OUT</sub> rising                                         |                         | $0.92 \times V_{IN}$ |     | V    |

| Short-Circuit Protection                                | V <sub>OUT(SC)</sub>    | V <sub>OUT</sub> falling                                        |                         | $0.55 \times V_{IN}$ |     | V    |

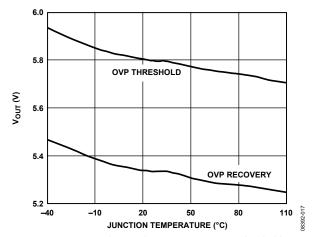

| Output Overvoltage Protection                           | V <sub>OVP</sub>        |                                                                 |                         |                      |     |      |

| Activation Level                                        |                         |                                                                 |                         | 5.8                  |     | V    |

| <b>OVP Recovery Hysteresis</b>                          | $V_{\text{OVP(HYS)}}$   |                                                                 |                         | 500                  |     | mV   |

| Thermal Shutdown                                        |                         |                                                                 |                         |                      |     |      |

| Threshold                                               | TSD                     |                                                                 |                         | 150                  |     | °C   |

| Hysteresis                                              | TSD <sub>(HYS)</sub>    |                                                                 |                         | 20                   |     | °C   |

| Isolation from Input to Output<br>During Fault          | loutlkg                 | $V_{IN} = 5.5 \text{ V, } V_{OUT} = 0 \text{ V, Bit nSTBY} = 0$ |                         |                      | 1.5 | μΑ   |

| Time to Validate a Fault                                | t <sub>FAULT</sub>      |                                                                 |                         | 2                    |     | μs   |

| I <sup>2</sup> C INTERFACE                              |                         |                                                                 |                         |                      |     |      |

| Operating V <sub>DDIO</sub> Voltage                     | $V_{\text{DDIO}}$       |                                                                 |                         |                      | 5.5 | V    |

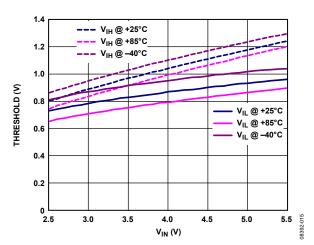

| Logic Low Input <sup>2</sup>                            | V <sub>IL</sub>         | $V_{IN} = 3.6 \text{ V}$                                        |                         |                      | 0.6 | V    |

| Logic High Input <sup>3</sup>                           | V <sub>IH</sub>         | $V_{IN} = 3.6 \text{ V}$                                        | 1.30                    |                      |     | V    |

| I <sup>2</sup> C TIMING SPECIFICATIONS                  |                         | Guaranteed by design                                            |                         |                      |     |      |

| Delay from Reset Deassertion to I <sup>2</sup> C Access | t <sub>RESET</sub>      |                                                                 |                         |                      | 20  | μs   |

| SCL Frequency                                           | f <sub>SCL</sub>        |                                                                 |                         |                      | 400 | kHz  |

| SCL High Time                                           | t <sub>HIGH</sub>       |                                                                 | 0.6                     |                      |     | μs   |

| SCL Low Time                                            | t <sub>LOW</sub>        |                                                                 | 1.3                     |                      |     | μs   |

| Setup Time                                              |                         |                                                                 |                         |                      |     |      |

| Data                                                    | t <sub>SU, DAT</sub>    |                                                                 | 100                     |                      |     | ns   |

| Repeated Start                                          | t <sub>SU, STA</sub>    |                                                                 | 0.6                     |                      |     | μs   |

| Stop Condition                                          | t <sub>SU, STO</sub>    |                                                                 | 0.6                     |                      |     | μs   |

| Hold Time                                               |                         |                                                                 |                         |                      |     |      |

| Data                                                    | t <sub>HD, DAT</sub>    |                                                                 | 0                       |                      | 0.9 | μs   |

| Start/Repeated Start                                    | <b>t</b> HD, STA        |                                                                 | 0.6                     |                      |     | μs   |

| Bus Free Time (Stop and Start Conditions)               | t <sub>BUF</sub>        |                                                                 | 1.3                     |                      |     | μs   |

| Rise Time (SCL and SDA)                                 | t <sub>R</sub>          |                                                                 | 20 + 0.1 C <sub>B</sub> |                      | 300 | ns   |

| Fall Time (SCL and SDA)                                 | t <sub>F</sub>          |                                                                 | 20 + 0.1 C <sub>B</sub> |                      | 300 | ns   |

| Pulse Width of Suppressed Spike                         | t <sub>SP</sub>         |                                                                 | 0                       |                      | 50  | ns   |

| Capacitive Load per Bus Line                            | $C_B$                   |                                                                 |                         |                      | 400 | рF   |

<sup>&</sup>lt;sup>1</sup> Current source matching is calculated by dividing the difference between the maximum and minimum current from the sum of the maximum and minimum. <sup>2</sup> V<sub>IL</sub> is a function of the input voltage. See Figure 15 in the Typical Performance Characteristics section for typical values over operating ranges. <sup>3</sup> V<sub>IH</sub> is a function of the input voltage. See Figure 15 in the Typical Performance Characteristics section for typical values over operating ranges.

# I<sup>2</sup>C TIMING DIAGRAM

Figure 2. I<sup>2</sup>C Interface Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| VIN, VOUT                            | −0.3 V to +6 V  |

| D1, D2, D3, D4, D5, D6, and D7       | −0.3 V to +6 V  |

| CMP_IN                               | −0.3 V to +6 V  |

| nINT, nRST, SCL, and SDA             | −0.3 V to +6 V  |

| Output Short-Circuit Duration        | Indefinite      |

| Operating Ambient Temperature Range  | -40°C to +85°C1 |

| Operating Junction Temperature Range | −40°C to +125°C |

| Storage Temperature Range            | −65°C to +150°C |

| Soldering Conditions                 | JEDEC J-STD-020 |

| ESD (Electrostatic Discharge)        |                 |

| Human Body Model (HBM)               | ±3 kV           |

| Charged Device Model (CDM)           | ±1.5 kV         |

$<sup>^1</sup>$  The maximum operating junction temperature ( $T_{\text{J(MAX)}}$ ) takes precedence over the maximum operating ambient temperature ( $T_{\text{A(MAX)}}$ ). See the Maximum Temperature Ranges section for more information.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all voltages are referenced to ground.

#### **MAXIMUM TEMPERATURE RANGES**

The maximum operating junction temperature  $(T_{J(MAX)})$  takes precedence over the maximum operating ambient temperature  $(T_{A(MAX)})$ . Therefore, in situations where the ADP8863 is exposed to poor thermal resistance and high power dissipation  $(P_D)$ , the maximum ambient temperature may need to be derated. In these cases, the maximum ambient temperature can be calculated with the following equation:

$$T_{A(MAX)} = T_{I(MAX)} - (\theta_{IA} \times P_{D(MAX)})$$

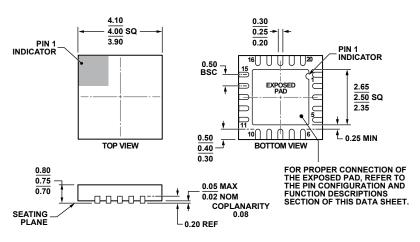

#### THERMAL RESISTANCE

$\theta_{JA}$  (junction to air) is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. The  $\theta_{JA}$ ,  $\theta_{JB}$  (junction to board), and  $\theta_{JC}$  (junction to case) are determined according to JESD51-9 on a 4-layer printed circuit board (PCB) with natural convection cooling. For the LFCSP package, the exposed pad must be soldered to the GND1 and/or GND2 terminal(s) on the board.

**Table 3. Thermal Resistance**

| Package Type     | θ <sub>JA</sub> | θις | Unit |

|------------------|-----------------|-----|------|

| 20-Lead LFCSP_WQ | 49.5            | 5.3 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

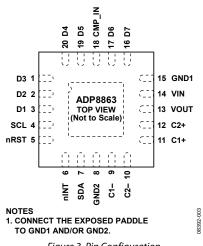

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                      |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | VIN      | Input Voltage, 2.5 V to 5.5 V.                                                                                                                   |

| 3       | D1       | LED Sink 1.                                                                                                                                      |

| 2       | D2       | LED Sink 2.                                                                                                                                      |

| 1       | D3       | LED Sink 3.                                                                                                                                      |

| 20      | D4       | LED Sink 4.                                                                                                                                      |

| 19      | D5       | LED Sink 5.                                                                                                                                      |

| 17      | D6       | LED Sink 6. This pin can also be selected as a comparator input for the second phototransistor.                                                  |

| 16      | D7       | LED Sink 7.                                                                                                                                      |

| 18      | CMP_IN   | Comparator Input for Phototransistor. When using this function, a capacitor (0.1 $\mu$ F recommended) must be connected from this pin to ground. |

| 13      | VOUT     | Charge Pump Output.                                                                                                                              |

| 11      | C1+      | Charge Pump C1+.                                                                                                                                 |

| 9       | C1-      | Charge Pump C1–.                                                                                                                                 |

| 12      | C2+      | Charge Pump C2+.                                                                                                                                 |

| 10      | C2-      | Charge Pump C2–.                                                                                                                                 |

| 15      | GND1     | Ground. Connect the exposed pad to GND1 and/or GND2.                                                                                             |

| 8       | GND2     | Ground. Connect the exposed pad to GND1 and/or GND2.                                                                                             |

| 6       | nINT     | Processor Interrupt (Active Low). Requires an external pull-up resistor. If this pin is not used, it can be left floating.                       |

| 5       | nRST     | Hardware Reset (Active Low). This pin resets the device to the default conditions. If not used, this pin must be tied above VIH(MIN).            |

| 7       | SDA      | I <sup>2</sup> C Serial Data. Requires an external pull-up resistor.                                                                             |

| 4       | SCL      | I <sup>2</sup> C Clock. Requires an external pull-up resistor.                                                                                   |

| 21      | EPAD     | Exposed Paddle. Connect the exposed paddle to GND1 and/or GND2.                                                                                  |

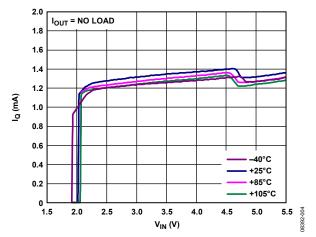

# TYPICAL PERFORMANCE CHARACTERISTICS

$VIN = 3.6 \text{ V}, SCL = 2.7 \text{ V}, SDA = 2.7 \text{ V}, nRST = 2.7 \text{ V}, V_{D1:D7} = 0.4 \text{ V}, C_{IN} = 1 \text{ }\mu\text{F}, Capacitor C1 = 1 \text{ }\mu\text{F}, Capacitor C2 = 1 \text{ }\mu\text{F}, Cout = 1 \text{ }\mu\text{F}, Cout = 1 \text{ }\mu\text{F}, Capacitor C2 = 1 \text{ }\mu\text{F}, Capacitor C3 = 1 \text{ }\mu\text{F}, Capacitor C4 = 1 \text{ }\mu\text{F}, Capacitor C4 = 1 \text{ }\mu\text{F}, Capacitor C5 = 1 \text{ }\mu\text{F}, Capacitor C6 = 1 \text{ }\mu\text{F}, Capacitor C7 = 1 \text{ }\mu\text{F}, Capacitor C7 = 1 \text{ }\mu\text{F}, Capacitor C8 = 1 \text{ }\mu\text{F}, Capacitor C9 =$

Figure 4. Typical Quiescent Current,  $G = 1 \times$

Figure 5. Typical Quiescent Current,  $G = 2 \times$ ,  $I_{Q(ACTIVE)}$

Figure 6. Typical Standby  $I_Q$  vs.  $V_{IN}$

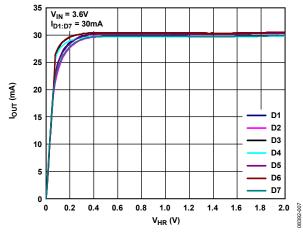

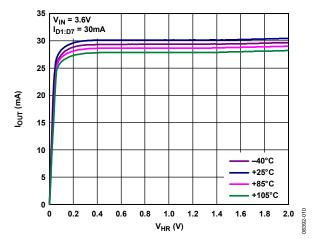

Figure 7. Typical Diode Current vs. Current Sink Headroom Voltage (VHR)

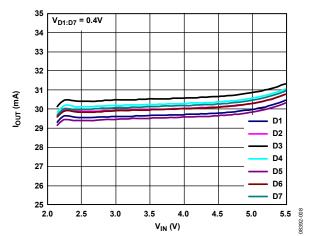

Figure 8. Typical Diode Matching vs. V<sub>IN</sub>

Figure 9. Typical Diode Matching vs. Current Sink Headroom Voltage ( $V_{HR}$ )

Figure 10. Typical Diode Current vs. Current Sink Headroom Voltage (V<sub>HR</sub>)

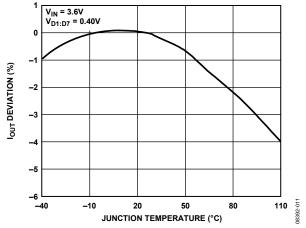

Figure 11. Typical Change In Diode Current vs. Temperature

Figure 12. R<sub>OUT</sub> vs. Temperature

Figure 13. Typical  $R_{OUT}$  ( $G = 1 \times$ ) vs.  $V_{IN}$

Figure 14. Typical Output Soft Start Current, Iss

Figure 15. Typical  $I^2C$  Thresholds,  $V_{IH}$  and  $V_{IL}$

Figure 16. Typical ALS Current, IALS

Figure 17. Typical Regulated Output Voltage ( $V_{OUT(REG)}$ )

Figure 18. Typical Overvoltage Protection (OVP) Threshold

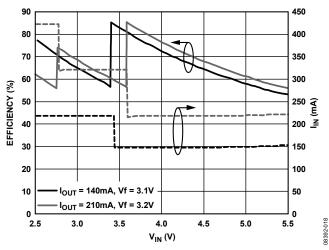

Figure 19. Typical Efficiency (Low Vf Diode)

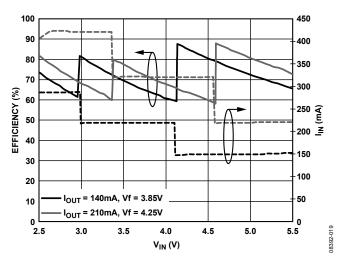

Figure 20. Typical Efficiency (High Vf Diode)

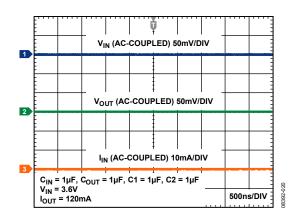

Figure 21. Typical Operating Waveforms,  $G = 1 \times$

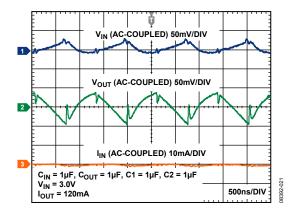

Figure 22. Typical Operating Waveforms,  $G = 1.5 \times$

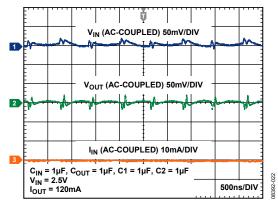

Figure 23. Typical Operating Waveforms,  $G = 2 \times$

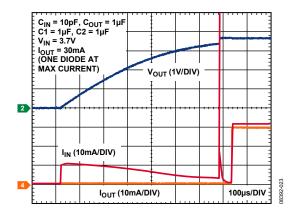

Figure 24. Typical Start-Up Waveform

# THEORY OF OPERATION

The ADP8863 combines a powerful LED charge pump driver with independent control of up to seven LEDs. These LED drivers can sink up to 30 mA (typical) on six channels. The seventh LED can also be driven to 60 mA (typical). All LEDs can be individually programmed or combined into a group to

operate backlight LEDs. A full set of safety features, including short-circuit, overvoltage, and overtemperature protection with input-to-output isolation, allows for a robust and safe design. The integrated soft start limits inrush currents at startup, restart attempts, and gain transitions.

Figure 25. Detailed Block Diagram

#### **POWER STAGE**

Because typical white LEDs require up to 4 V to drive them, some form of boosting is required over the typical variation in battery voltage. The ADP8863 accomplishes this with a high efficiency charge pump capable of producing a maximum  $\rm I_{OUT}$  of 240 mA over the entire input voltage range (2.5 V to 5.5 V). Charge pumps use the basic principle that a capacitor stores charge based on the voltage applied to it, as shown in the following equation:

$$Q = C \times V \tag{1}$$

By charging the capacitors in different configurations, the charge, and therefore the gain, can be optimized to deliver the voltage required to power the LEDs. Because a fixed charging and discharging combination must be used, only certain multiples of gain are available. The ADP8863 is capable of automatically optimizing the gain (G) from 1×, 1.5×, and 2×. These gains are accomplished with two capacitors (labeled C1 and C2 in Figure 25) and an internal switching network.

In  $G=1\times$  mode, the switches are configured to pass VIN directly to VOUT. In this mode, several switches are connected in parallel to minimize the resistive drop from input to output. In  $G=1.5\times$  and  $2\times$  modes, the switches alternatively charge from the battery and discharge into the output. For  $G=1.5\times$ , the capacitors are charged from  $V_{\rm IN}$  in series and are discharged to  $V_{\rm OUT}$  in parallel. For  $G=2\times$ , the capacitors are charged from  $V_{\rm IN}$

in parallel and are discharged to  $V_{\text{OUT}}$  in parallel. In certain fault modes, the switches are opened and the output is physically isolated from the input.

#### **Automatic Gain Selection**

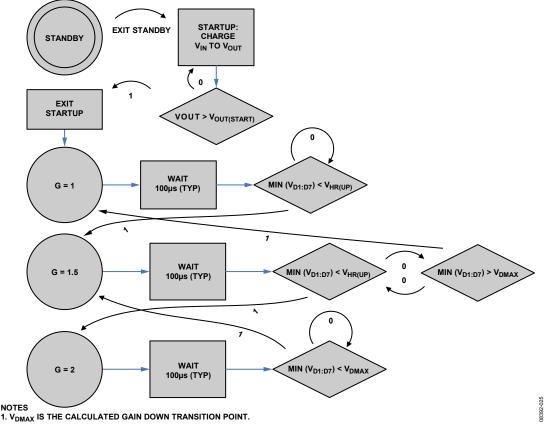

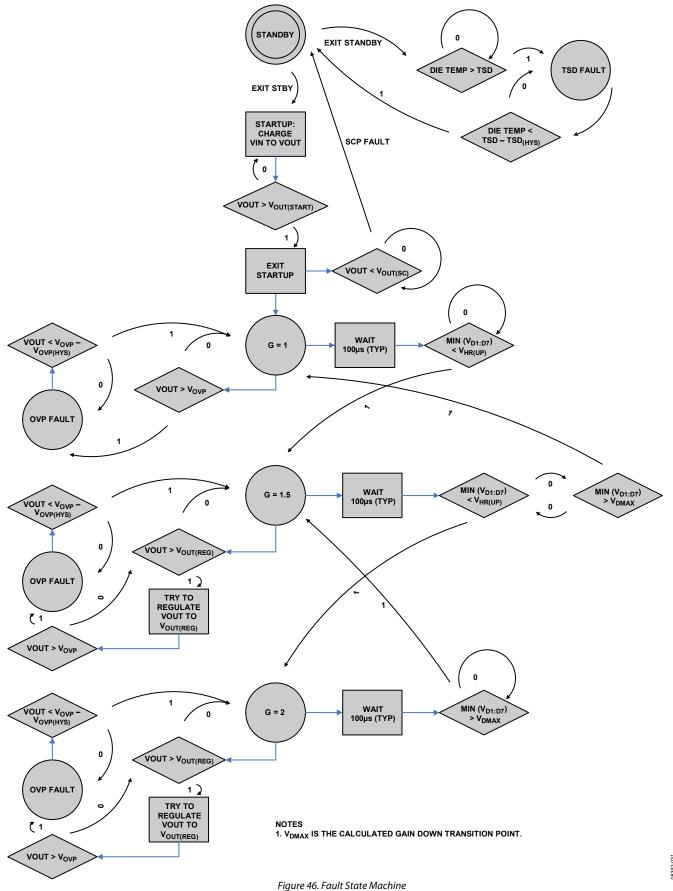

Each LED that is driven requires a current source. The voltage on this current source must be greater than a minimum headroom voltage (200 mV typical) to maintain accurate current regulation. The gain is automatically selected based on the minimum voltage (V<sub>DX</sub>) at all of the current sources. At startup, the device is placed into  $G = 1 \times \text{mode}$  and the output charges to  $V_{\text{IN}}$ . If any  $V_{\text{DX}}$  level is less than the required headroom (200 mV), the gain is increased to the next step ( $G = 1.5 \times$ ). A 100 µs delay is allowed for the output to stabilize prior to the next gain switching decision. If there remains insufficient current sink headroom, then the gain is increased again to  $2\times$ . Conversely, to optimize efficiency, it is not desirable for the output voltage to be too high. Therefore, the gain reduces when the headroom voltage is great enough. This point (labeled V<sub>DMAX</sub> in Figure 26) is internally calculated to ensure that the lower gain still results in ample headroom for all the current sinks. The entire cycle is illustrated in Figure 26.

Note that the gain selection criteria apply only to active current sources. If current sources have been deactivated through an I<sup>2</sup>C command (for example, only five LEDs are used), then the voltages on the deactivated current sources are ignored.

Figure 26. State Diagram for Automatic Gain Selection

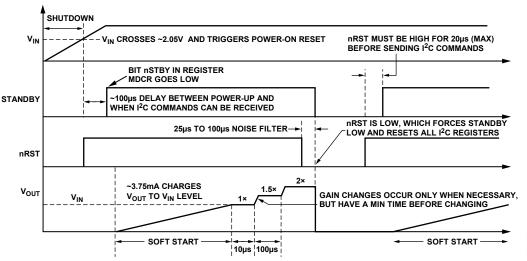

#### **Soft Start Feature**

At startup (either from UVLO activation or fault/standby recovery), the output is first charged by  $I_{SS}$  (3.75 mA typical) until it reaches about 92% of  $V_{\rm IN}$ . This soft start feature reduces the inrush current that is otherwise present when the output capacitance is initially charged to  $V_{\rm IN}$ . When this point is reached, the controller enters  $G=1\times$  mode. If the output voltage is not sufficient, then the automatic gain selection determines the optimal point as defined in the Automatic Gain Selection section.

#### **OPERATING MODES**

There are four different operating modes: active, standby, shutdown, and reset.

#### **Active Mode**

In active mode, all circuits are powered up and in a fully operational state. This mode is entered when Bit nSTBY (in Register MDCR) is set to 1.

### Standby Mode

Standby mode disables all circuitry except for the  $I^2C$  receivers. Current consumption is reduced to less than 1  $\mu A.$  This mode is entered when the nSTBY bit is set to 0 or when the nRST pin is held low for more than 100  $\mu s$  (maximum). When standby is exited, a soft start sequence is performed.

#### Shutdown Mode

Shutdown mode disables all circuitry, including the  $I^2C$  receivers. Shutdown occurs when  $V_{\rm IN}$  is below the undervoltage thresholds. When  $V_{\rm IN}$  rises above  $V_{\rm IN(START)}$  (2.05 V typical), all registers are reset and the part is placed into standby mode.

#### **Reset Mode**

In reset mode, all registers are set to their default values and the part is placed into standby. There are two ways to reset the part: by power-on reset (POR) or using the nRST pin. POR is activated any time that the part exits shutdown mode. After a POR sequence is complete, the part automatically enters standby mode.

After startup, the part can be reset by pulling the nRST pin low. As long as the nRST pin is low, the part is held in a standby state, but no  $\rm I^2C$  commands are acknowledged (all registers are kept at their default values). After releasing the nRST pin, all registers remain at their default values, and the part remains in standby; however, the part does accept  $\rm I^2C$  commands.

The nRST pin has a 50  $\mu$ s (typical) noise filter to prevent inadvertent activation of the reset function. The nRST pin must be held low for this entire time to activate reset.

The operating modes function according to the timing diagram in Figure 27.

Figure 27. Typical Timing Diagram

#### **LED GROUPINGS**

Each LED can respond individually or be grouped together into the backlight controls. By default, all LEDs are set to be part of the backlight. This is changed by setting Bits[6:0] in Register 0x05. LEDs that are set up as independent sinks can be enabled individually in Register 0x10. They can also all be enabled simultaneously via the SIS\_EN bit in Register 0x01. Any LEDs configured for the backlight can only be enabled via the BL\_EN bit in Register 0x01.

#### **LED CURRENT SETTINGS**

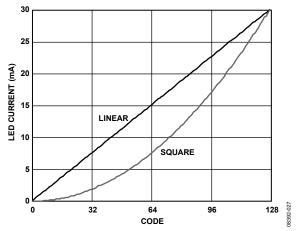

Any of the LED outputs (Pin D1 to Pin D7) can be used to drive any color of LED at 0 mA to 30 mA, provided that the LED's Vf is less than 4.1 V. Additionally, the D7 sink can regulate up to 60 mA. The current settings are determined by a 7-bit code programmed by the user into Register 0x14 through Register 0x1A (for the independent sinks) and Register 0x09 to Register 0x0E (for the backlight sinks). The 7-bit resolution allows the user to set the LED to one of 128 different levels.

The ADP8863 can implement two distinct algorithms to achieve a linear or a nonlinear relationship between input code and diode output current. The law and SC\_LAW bits in Register 0x04 and Register 0x0F, respectively, are used to change between these algorithms.

By default, the ADP8863 uses a linear algorithm (law and SC\_LAW = 00), where the LED current increases linearly for a corresponding increase in input code. LED current (in milliamperes) is determined by the following equation:

$$LED\ Current\ (mA) = Code \times (Full-Scale\ Current/127)$$

(2)

where:

Code is the input code programmed by the user. Full-Scale Current is the maximum sink current allowed per LED (typically 30 mA).

The ADP8863 can also implement a nonlinear (square approximation) relationship between input code and LED current. In this case (law and  $SC_LAW = 01, 10, or 11$ ), the LED current (in milliamperes) is determined by the following equation:

$$LED Current (mA) = \left(Code \times \frac{\sqrt{Full - Scale Current}}{127}\right)^{2}$$

(3)

Figure 28 shows the LED current level vs. input code for both the linear and square law algorithms.

Figure 28. LED Current vs. Input Code

#### **AUTOMATED FADE IN AND FADE OUT**

The LED drivers are easily configured for automated fade in and fade out. Sixteen fade in and fade out rates can be selected via the I<sup>2</sup>C interface. Fade in and fade out rates range from 0.0 sec to 5.5 sec (per full-scale current, either 30 mA or 60 mA). The backlight LEDs have separate fade in and fade out time controls from the independent sink LEDs.

Table 5. Available Fade In and Fade Out Rates

| Code | Fade Rate (in sec per Full-Scale Curi | ent) |

|------|---------------------------------------|------|

| 0000 | 0.0 (disabled)                        |      |

| 0001 | 0.3                                   |      |

| 0010 | 0.6                                   |      |

| 0011 | 0.9                                   |      |

| 0100 | 1.2                                   |      |

| 0101 | 1.5                                   |      |

| 0110 | 1.8                                   |      |

| 0111 | 2.1                                   |      |

| 1000 | 2.4                                   |      |

| 1001 | 2.7                                   |      |

| 1010 | 3.0                                   |      |

| 1011 | 3.5                                   |      |

| 1100 | 4.0                                   |      |

| 1101 | 4.5                                   |      |

| 1110 | 5.0                                   |      |

| 1111 | 5.5                                   |      |

The fade profile is based on the transfer law selected (linear, square, Cubic 10, or Cubic 11) and the delta between the actual current and the target current. Smaller changes in current reduce the fade time. For linear and square law fades, the fade time is given by

$$Fade\ Time = Fade\ Rate \times (Code/127) \tag{4}$$

where the Fade Rate is shown in Table 5.

The Cubic 10 and Cubic 11 laws also use the square law LED currents derived from Equation 3; however, the time between each step is varied to produce a steeper slope at higher currents and a shallower slope at lower currents (see Figure 29).

Figure 29. Comparison of the Dimming Transfers Laws

Each LED can be enabled independently and has its own current level, but all LEDs share the same fade in rates, fade out rates, and fade law.

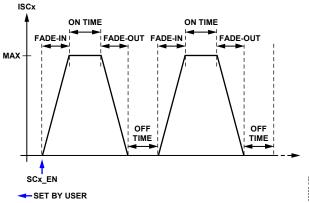

### INDEPENDENT SINK CONTROL

Each of the seven LEDs can be configured (in Register 0x05) to operate as either part of the backlight or to operate as an independent sink current (ISC). Each ISC can be enabled independently and has its own current level. All ISCs share the same fade in rates, fade out rates, and fade law.

The ISCs have additional timers to facilitate blinking functions. A shared on timer (SCON) in conjunction with the off timer of each ISC (SC1OFF, SC2OFF, SC3OFF, SC4OFF, SC5OFF, SC6OFF, and SC7OFF) allows the LED current sinks to be configured in various blinking modes. The on timer can be set to one of four different settings: 0.2 sec, 0.6 sec, 0.8 sec, or 1.2 sec. The off timers have four different settings: disabled, 0.6 sec, 1.2 sec, and 1.8 sec. Blink mode is activated by setting the off timers to any setting other than disabled.

Program all fade, on, and off timers before enabling any of the LED current sinks. If ISCx is on during a blink cycle and SCx\_EN is cleared, the LED turns off (or fades to off if fade out is enabled). If ISCx is off during a blink cycle and SCx\_EN is cleared, it stays off.

Figure 30. Independent Sink Blink Mode with Fading

#### **RGB COLOR GENERATION**

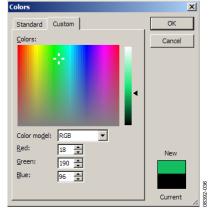

The ADP8863 is easily programmed to generate any color with an RGB LED. To configure this feature, connect each LED in a standard RGB diode to a separate driver on the ADP8863. Because each channel can be programmed for a different current level, setting the currents for all three LEDs generates the desired color. To set the current levels, use a simple RGB color selector (see Figure 31).

Figure 31. Standard RGB Color Generator

The example in Figure 31 shows a color of green, which is generated with a red content of 18 (out of 255), a green content of 190, and a blue content of 96. All numbers are out of a maximum of 255. Thus, the percentage of red is 7.1%, the percentage of green is 74.5%, and the percentage of blue is 37.6%. To generate the color with the ADP8863, scale this value to each of the current drivers.

#### **AUTOMATED RGB COLOR FADES**

The ADP8863 is easily programmed to cycle through RGB generated colors. This can be either a repeating or a random pattern of one color fading into the other. To execute this cycle autonomously, set up the RGB LEDs as described in the RGB Color Generation section and program the on, off, fading times, and current intensities. Adjusting the fading time in particular can create any pattern from a fast, striking effect to a soothing slow color change.

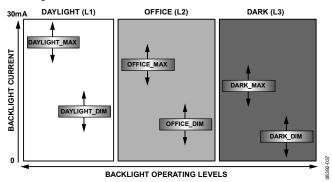

#### **BACKLIGHT OPERATING LEVELS**

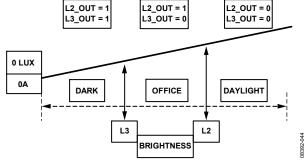

Backlight brightness control operates at three distinct levels: daylight (L1), office (L2), and dark (L3). The BLV bits in Register 0x04 control the specific level at which the backlight operates. These bits can be changed manually or, if in automatic mode (CMP\_AUTOEN is set high in Register 0x01), by the ambient light sensor (see the Ambient Light Sensing section).

By default, the backlight operates at daylight level (BLV = 00), where the maximum brightness is set using Register 0x09 (BLMX1). A daylight dim setting can also be set using Register 0x0A (BLDM1). When operating at office level (BLV = 01), the backlight maximum and dim brightness settings are set using Register 0x0B (BLMX2) and Register 0x0C (BLDM2). When operating at the dark level (BLV = 10), the backlight maximum and dim brightness settings are set using Register 0x0D (BLMX3) and Register 0x0E (BLDM3).

Figure 32. Backlight Operating Levels

#### **BACKLIGHT TURN ON/TURN OFF/DIM**

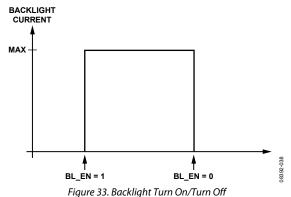

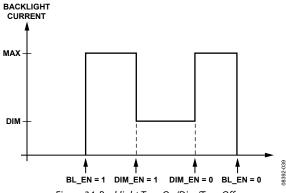

With the device in active mode (nSTBY = 1), the backlight can be turned on using the BL\_EN bit in Register 0x01. Before turning on the backlight, select the level (daylight (L1), office (L2), or dark (L3)) to operate in and ensure that maximum and dim settings are programmed for that level. The backlight turns on when BL\_EN = 1. The backlight turns off when BL\_EN = 0.

While the backlight is on (BL\_EN = 1), the user can change to the dim setting by programming DIM\_EN = 1 in Register 0x01. If DIM\_EN = 0, the backlight reverts to its maximum setting.

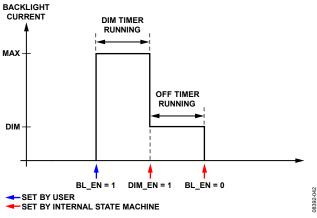

Figure 34. Backlight Turn On/Dim/Turn Off

The maximum and dim settings can be set from 0 mA to 30 mA; therefore, it is possible to program a dim setting that is greater than a maximum setting. For normal expected operation, ensure that the dim setting is programmed to be less than the maximum setting.

#### **AUTOMATIC DIM AND TURN OFF TIMERS**

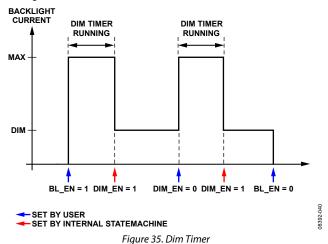

The user can program the backlight to dim automatically by using the DIMT bits in Register 0x07. The dim timer has 127 settings ranging from 1 sec to 127 sec. Program the dim timer (DIMT) before turning on the backlight. If BL\_EN = 1, the backlight turns on to its maximum setting and the dim timer starts counting. When the dim timer expires, the internal state machine sets DIM\_EN = 1, and the backlight enters its dim setting.

If the user clears the DIM\_EN bit, the backlight reverts to its maximum setting and the dim timer begins counting again. When the dim timer expires, the internal state machine again sets DIM\_EN = 1, and the backlight enters its dim setting. The backlight can be turned off at any point during the dim timer countdown by clearing BL\_EN.

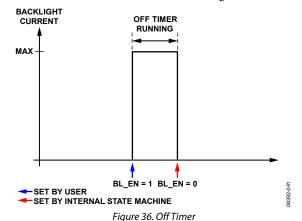

The user can also program the backlight to turn off automatically by using the OFFT bits in Register 0x06. The off timer has 127 settings ranging from 1 sec to 127 sec. Program the off timer (OFFT) before turning on the backlight. If  $BL_EN = 1$ , the backlight turns on to its maximum setting and the off timer

starts counting. When the off timer expires, the internal state machine clears the BL\_EN bit, and the backlight turns off.

The backlight can be turned off at any point during the off timer countdown by clearing BL\_EN.

The dim timer and off timer can be used together for sequential maximum-to-dim-to-off functionality. With both the dim and off timers programmed, and BL\_EN asserted, the backlight turns on to its maximum setting, and when the dim timer expires, the backlight changes to its dim setting. When the off timer expires, the backlight turns off.

Figure 37. Dim and Off Timers Used Together

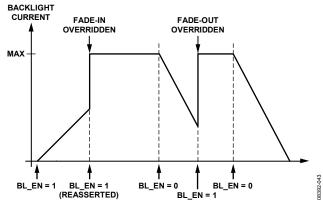

#### **FADE OVERRIDE**

A fade override feature (FOVR in Register CFGR (0x04)) enables the host to override the preprogrammed fade in or fade out settings. If FOVR is set and the backlight is enabled in the middle of a fade out process, the backlight instantly (within approximately 100 ms) returns to its maximum setting. Alternatively, if the backlight is fading in, reasserting BL\_EN overrides the programmed fade in time, and the backlight instantly goes to its final fade value. This is useful for situations in which a key is pressed during a fade sequence. However, if FOVR is cleared and the backlight is enabled in the middle of a fade process, the backlight gradually brightens from where it was interrupted (it does not go down to 0 and then comes back on).

Figure 38. Fade Override Function (FOVR Is High)

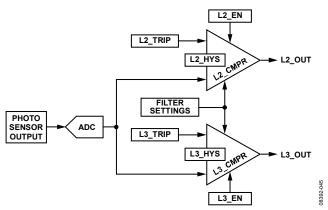

#### AMBIENT LIGHT SENSING

The ADP8863 integrates two ambient light sensing comparators. One of the ambient light sensing comparator pins (CMP\_IN) is always available. The second pin (D6) has an ambient light sensor comparator (CMP\_IN2) that can be activated rather than connecting an LED to D6. Activating the CMP\_IN2 function of the pin is accomplished through the CMP2\_SEL bit in Register CFGR. Therefore, when the CMP2\_SEL bit is set to 0, Pin D6 is programmed as a current sink. When the CMP2\_SEL bit is set to 1, Pin D6 becomes the input for a second phototransistor.

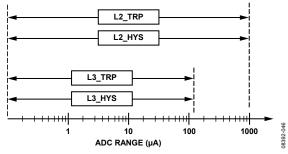

These comparators have two programmable trip points (L2 and L3) that select one of the three backlight operation modes (daylight, office, and dark) based on the ambient lighting conditions.

The L3 comparator controls the dark-to-office mode transition. The L2 comparator controls the office-to-daylight transition (see Figure 39). The currents for the different lighting modes are defined in the BLMXx and BLDMx registers (see the Backlight Operating Levels Section).

Figure 39. Light Sensor Modes Based on the Detected Ambient Light Level

Each light sensor comparator uses an external capacitor together with an internal reference current source to form an analog-to-digital converter (ADC) that samples the output of the external photosensor. The ADC result is fed into two programmable trip comparators. The ADC has an input range of 0  $\mu A$  to 1080  $\mu A$  (typical).

Figure 40. Ambient Light Sensing and Trip Comparators

The L2 comparator, L2\_CMPR, detects when the photosensor output has dropped below the programmable L2\_TRP point (Register 0x1D). If this event occurs, then the L2\_OUT status signal is set. L2\_CMPR contains programmable hysteresis, meaning that the photosensor output must rise above L2\_TRP + L2\_HYS before L2\_OUT clears. L2\_CMPR is enabled via the L2\_EN bit. The L2\_TRP and L2\_HYS values of L2\_CMPR can be set between 0  $\mu A$  and 1080  $\mu A$  (typical) in steps of 4.3  $\mu A$  (typical).

The L3 comparator, L3\_CMPR, detects when the photosensor output drops below the programmable L3\_TRP point (Register 0x1F). If this event occurs, the L3\_OUT status signal is set. L3\_CMPR contains programmable hysteresis, meaning that the photosensor output must rise above L3\_TRP + L3\_HYS before L3\_OUT clears. L3\_CMPR is enabled via the L3\_EN bit. The L3\_TRP and L3\_HYS values of L3\_CMPR can be set between 0  $\mu A$  and 137.7  $\mu A$  (typical) in steps of 0.54  $\mu A$  (typical).

Figure 41. Comparator Ranges

Note that the full-scale value of the L2\_TRP and L2\_HYS registers is 250 (decimal). Therefore, if the value of L2\_TRP + L2\_HYS exceeds 250, the comparator output is unable to deassert. For example, if L2\_TRP is set to 204 (80% of the full-scale value, or approximately 0.80  $\times$  1080  $\mu A = 864~\mu A), then L2_HYS must be set to less than 46 (250 <math display="inline">-$  204 = 46). If it is not, then L2\_HYS + L2\_TRP exceeds 250 and the L2\_CMPR comparator is never allowed to go low.

When both phototransistors are enabled and programmed in automatic mode (through Bit CMP\_AUTOEN in Register 0x01), the user application must determine which comparator outputs to use, by selecting Bit SEL\_AB in Register 0x04 for automatic light sensing transitions. For example, the user soft-

ware may select the comparator of the phototransistor that is exposed to higher light intensity to control the transition between the programmed backlight intensity levels.

The L2\_CMPR and L3\_CMPR comparators can be enabled independently of each other, or they can operate simultaneously. A single conversion from each ADC takes 80 ms (typical). When CMP\_AUTOEN is set for automatic backlight adjustment (see the Automatic Backlight Adjustment section), the ADC and comparators run continuously. If the backlight is disabled and at least one independent sink is enabled, it is possible to use the light sensor comparators in a single-shot mode. A single-shot read of the photocomparators is performed by setting the FORCE\_RD bit in Register 0x1B. After the single-shot measurement is completed, the internal state machine clears the FORCE\_RD bit.

The interrupt flags (CMP\_INT and CMP\_INT2) can be used to notify the system when either L2 or L3 changes state. See the Interrupts section for more information.

#### **AUTOMATIC BACKLIGHT ADJUSTMENT**

The ambient light sensor comparators can automatically transition the backlight between one of its three operating levels. To enable this mode, set the CMP\_AUTOEN bit in Register 0x01.

When I<sup>2</sup>C selection is enabled, the internal state machine takes control of the BLV bits and changes them based on the L2\_OUT and L3\_OUT status bits. When L2\_OUT is set high, it indicates that the ambient light conditions have dropped below the L2\_TRP point and that the backlight should move to its office (L2) level. When L3\_OUT is set high, it indicates that ambient light conditions have dropped below the L3\_TRP point and that the backlight should move to its dark (L3) level. Table 6 shows the relationship between backlight operation and the ambient light sensor comparator outputs.

The L3\_OUT status bit has greater priority; therefore, if L3\_OUT is set, the backlight operates at L3 (dark) even if L2\_OUT is also set.

Filter times from 80 ms to 10 sec can be programmed for the comparators (Register 0x1B and Register 0x1C) before they change state.

**Table 6. Comparator Output Truth Table**

| CMP_AUTOEN | L3_OUT         | L2_OUT         | Backlight Operation                           |

|------------|----------------|----------------|-----------------------------------------------|

| 0          | X <sup>1</sup> | X <sup>1</sup> | BLV can be manually set by the user           |

| 1          | 0              | 0              | BLV = 00, backlight operates at L1 (daylight) |

| 1          | 0              | 1              | BLV = 01, backlight operates at L2 (office)   |

| 1          | 1              | X <sup>1</sup> | BLV = 10, backlight operates at L3 (dark)     |

<sup>&</sup>lt;sup>1</sup> X is the don't care bit.

#### **USING THE ADP8863 TO DRIVE ADDITIONAL LEDS**

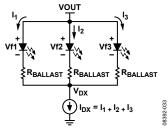

In some situations, it may be desirable to drive more than seven LEDs. This can be done in one of two ways: paralleling LEDs using ballast resistors, or using the ADP8863 to power additional LED drivers.

#### **Ballast Resistors**

In the first method, multiple LEDs can be attached to any one LED driver with the use of ballast resistors.

Figure 42. Ballast Resistor Arrangement

Ballast resistors attempt to compensate for the forward voltage (Vf) mismatch inherent in any parallel combination of LEDs. The choice of a ballasting resistor is a trade-off between the efficiency and the current matching of the LEDs in parallel. Smaller ballast resistors give better efficiency. Larger ballast resistors gives better current matching, because the resistor balances out the current differences for a voltage drop. The relationship is summarized with the following:

$$R_{BALLAST} \approx \frac{\Delta V f}{\Delta I}$$

(5)

where:

$\Delta V\!f$  is the difference between the maximum Vf and the minimum Vf of the LEDs in parallel.

$\Delta I$  is the difference between the parallel LED currents.

The addition of the ballast resistor brings the effective Vf of the LED to

$$Vf(eff) = Vf(LED) + I_{LED} \times R_{BALLAST}$$

(6)

The  $I_{LED} \times R_{BALLAST}$  term forces the charge pump to work a little harder for this additional voltage drop. Furthermore, for guaranteed operation with the ADP8863, the total Vf(eff) should never exceed  $V_{OUT(REG)} - V_{HR(UP)}$  (see Table 1).

Figure 43. Powering Additional LEDs with Ballast Resistors

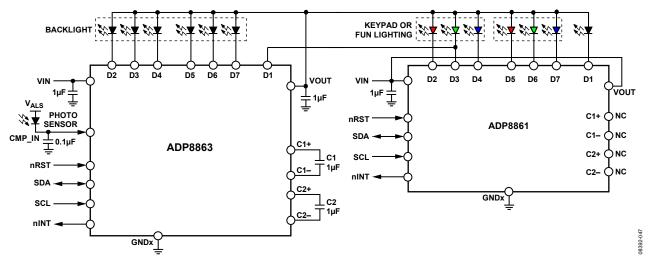

#### **Adding Additional Parallel Sinks**

The ballast resistor's compromises of efficiency and matching are not suitable for many applications. Therefore, another option is to use the ADP8863 charge pump to power additional current sinks. First, the charge pump must be optimized for this option by setting the GDWN\_DIS bit in Register 0x01, which prevents the charge pump from switching back down in gain, and thus stabilizes it against the unknown loads that the additional current sinks present.

To use the sinks, turn the ADP8863 charge pump on before activating the additional sinks. If the additional sinks are activated first, the ADP8863 soft start may not complete.

The ADP8863 can be set up with an ADP8860 or ADP8861. An example using the ADP8861 is shown in Figure 44.

Figure 44. Connecting the ADP8863 to an ADP8861 to Power More LEDs

### **OPERATING LEDS FROM ALTERNATIVE SUPPLIES**

For some applications, it is advantageous to operate the LEDs from a voltage source other than the ADP8863 charge pump output. For example, it may be possible to operate a red LED over the entire battery voltage range without any charge pump boosting. For a charge pump,

$$I_{IN} = Gain \times I_{OUT} \tag{7}$$

Therefore, operating the red LEDs directly from the battery removes output current of the red LEDs from the charge pump draw. This in turn reduces the total input current by (Gain  $-1)\times I_{\rm OUT(red)}$ .

However, care must be taken when selecting LEDs to operate from a different voltage input. Specifically, the voltage source must at least be able to support the maximum forward voltage (Vf) of the LED plus the maximum  $V_{\rm HR(UP)}$  (276 mV, given in Table 1). Additionally, operating an LED from an independent voltage source may interfere with the ADP8863's gain selection algorithm. This algorithm selects the optimal gain for the charge pump based on all seven diodes. By operating one or more of the diodes from another supply, the algorithm may not switch the gain back down to a lower state until the LEDs are disabled or the part enters standby.

Figure 45. Alternate Schematic for Low Vf LEDs

#### SHORT-CIRCUIT PROTECTION MODE

The ADP8863 can protect against short circuits on the output (VOUT). Short-circuit protection (SCP) is activated at the point when VOUT < 55% of  $V_{\rm IN}$ . Note that SCP sensing is disabled during both startup and restart attempts (fault recovery). SCP sensing is reenabled 4 ms (typical) after activation. During a short-circuit fault, the device enters a low current consumption state and an interrupt flag is set. The device can be restarted at any time after receiving a short-circuit fault by rewriting nSTBY = 1. It then repeats another complete soft start sequence. Note that the value of the output capacitance ( $C_{\rm OUT}$ ) should be small enough to allow VOUT to reach approximately 55% (typical) of  $V_{\rm IN}$  within the 4 ms (typical) time. If  $C_{\rm OUT}$  is too large, the device inadvertently enters short-circuit protection.

### **OVERVOLTAGE PROTECTION**

Overvoltage protection (OVP) is implemented on the output. There are two types of overvoltage events: normal (no fault) and abnormal (from a fault or sudden load change).

### **Normal Overvoltage**

In a normal (no fault) overvoltage, the output voltage approaches  $V_{\rm OUT(REG)}$  (4.9 V typical) during normal operation. This is not caused by a fault or load change, but is simply a consequence of the input voltage times the gain reaching the same level as the clamped output voltage ( $V_{\rm OUT(REG)}$ ). To prevent this type of overvoltage, the ADP8863 detects when the output voltage rises to  $V_{\rm OUT(REG)}$ . It then increases the effective  $R_{\rm OUT}$  of the gain stage to reduce the voltage that is delivered. This effectively regulates  $V_{\rm OUT}$  to  $V_{\rm OUT(REG)}$ ; however, there is a limit to the effect that this system can have on regulating  $V_{\rm OUT}$ . It is designed only for normal operation and it is not intended to protect against faults or sudden load changes. When the output voltage is regulated to  $V_{\rm OUT(REG)}$ , no interrupt is set and the operation is transparent to the LEDs and the overall application.

#### Abnormal Overvoltage

Because of the open-loop behavior of the charge pump as well as how the gain transitions are computed, a sudden load change or fault can abnormally force  $V_{\rm OUT}$  beyond 6 V. This causes an abnormal overvoltage situation. If the event happens slowly enough, the system first tries to regulate the output to 4.9 V as in a normal overvoltage scenario. However, if this is not sufficient, or if the event happens too quickly, the ADP8863 enters overvoltage protection (OVP) mode when  $V_{\rm OUT}$  exceeds the OVP threshold (typically 5.8 V). In OVP mode, only the charge pump is disabled to prevent  $V_{\rm OUT}$  from rising too high. The

current sources and all other device functionality remain intact. When the output voltage falls by about 500 mV (to 5.3 V typical), the charge pump resumes operation. If the fault or load event recurs, the process may repeat. An interrupt flag is set at each OVP instance.

# THERMAL SHUTDOWN/OVERTEMPERATURE PROTECTION

If the die temperature of the ADP8863 rises above a safe limit (150°C typical), the controllers enter thermal shutdown (TSD) protection mode. In this mode, most of the internal functions shut down, the part enters standby, and the TSD\_INT interrupt (Register 0x02) is set. When the die temperature decreases below ~130°C, the part can be restarted. To restart the part, remove it from standby. No interrupt is generated when the die temperature falls below 130°C. However, if the software clears the pending TSD\_INT interrupt and the temperature remains above 130°C, another interrupt is generated.

The complete state machine for these faults (SCP, OVP, and TSD) is shown in Figure 46.

#### **INTERRUPTS**

There are five interrupt sources available on the ADP8863 in Register 0x02.

- Main light sensor comparator: The CMP\_INT interrupt sets every time the main light sensor comparator detects a threshold (L2 or L3) transition (rising or falling condition).

- Sensor Comparator 2: The CMP2\_INT interrupt works

the same way as CMP\_INT, except that the sensing input

derives from the second light sensor. The programmable

thresh-olds are the same as for the main light sensor

comparator.

- Overvoltage protection: OVP\_INT is generated when the output voltage exceeds 5.8 V (typical).

- Thermal shutdown circuit: an interrupt (TSD\_INT) is generated when entering overtemperature protection.

- Short-circuit detection: SHORT\_INT is generated when the device enters short-circuit protection mode.

The interrupt (if any) that appears on the nINT pin is determined by the bits mapped in Register INTR\_EN (0x03). To clear an interrupt, write a 1 to the interrupt in the MDCR2 register (0x02) or reset the part. Reading the interrupt, or writing a 0, has no effect.

Rev. 0 | Page 22 of 48

# APPLICATIONS INFORMATION

The ADP8863 allows the charge pump to operate efficiently with a minimum of external components. Specifically, the user must select an input capacitor ( $C_{\rm IN}$ ), output capacitor ( $C_{\rm OUT}$ ), and two charge pump fly capacitors (C1 and C2).  $C_{\rm IN}$  should be 1  $\mu F$  or greater. The value must be high enough to produce a stable input voltage signal at the minimum input voltage and maximum output load. A 1  $\mu F$  capacitor for  $C_{\rm OUT}$  is recommended. Larger values are permissible, but care must be exercised to ensure that VOUT charges above 55% (typical) of  $V_{\rm IN}$  within 4 ms (typical). See the Short-Circuit Protection Mode section for more details.

For best practice, it is recommended that the two charge pump fly capacitors be 1  $\mu F$ ; larger values are not recommended, and smaller values may reduce the ability of the charge pump to deliver maximum current. For optimal efficiency, the charge pump fly capacitors should have low equivalent series resistance (ESR). Low ESR X5R or X7R capacitors are recommended for all four components. The use of fly capacitors sized 0402 and smaller is allowed, but the GDWN\_DIS bit in Register 0x01 must be set. Minimum voltage ratings should adhere to the guidelines in Table 7.

Table 7. Capacitor Stress in Each Charge Pump Gain State

| Capacitor        | Gain = 1×       | Gain = 1.5×                        | Gain = 2×                          |

|------------------|-----------------|------------------------------------|------------------------------------|

| C <sub>IN</sub>  | V <sub>IN</sub> | V <sub>IN</sub>                    | V <sub>IN</sub>                    |

| C <sub>OUT</sub> | V <sub>IN</sub> | $V_{IN} \times 1.5$ (max of 5.5 V) | $V_{IN} \times 2.0$ (max of 5.5 V) |

| C1               | None            | V <sub>IN</sub> /2                 | V <sub>IN</sub>                    |

| C2               | None            | V <sub>IN</sub> /2                 | V <sub>IN</sub>                    |

If one or both ambient light sensor comparator inputs (CMP\_IN and D6) are used, a small capacitor (0.1  $\mu F$  is recommended) must be connected from the input to ground.

Any color LED can be used if the Vf (forward voltage) is less than 4.1 V. However, using lower Vf LEDs reduces the input power consumption by allowing the charge pump to operate at lower gain states.

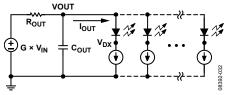

The equivalent circuit model for a charge pump is shown in Figure 47.

Figure 47. Charge Pump Equivalent Circuit Model

The input voltage is multiplied by the gain (G) and delivered to the output through an effective resistance ( $R_{\text{OUT}}$ ). The output current flows through  $R_{\text{OUT}}$  and produces an IR drop to yield

$$V_{OUT} = G \times V_{IN} - I_{OUT} \times R_{OUT}(G)$$

(8)

The  $R_{OUT}$  term is a combination of the  $R_{DSON}$  resistance for the switches used in the charge pump and a small resistance that accounts for the effective dynamic charge pump resistance. The  $R_{OUT}$  level changes based upon the gain (the configuration of the switches). Typical  $R_{OUT}$  values are given in Table 1, Figure 12, and Figure 13.  $V_{OUT}$  is also equal to the largest Vf of the LEDs used plus the

voltage drop across the regulating current source. This gives

$$V_{OUT} = V f_{(MAX)} + V_{DX} \tag{9}$$

Combining Equation 8 and Equation 9 gives

$$V_{IN} = (Vf_{(MAX)} + V_{DX} + I_{OUT} \times R_{OUT}(G))/G$$

(10)

Equation 10 is useful for calculating approximate bounds for the charge pump design.

### **Determining the Transition Point of the Charge Pump**

Consider the following design example, where:

$Vf_{(MAX)} = 3.7 \text{ V}$

$I_{OUT} = 140 \text{ mA} (7 \text{ LEDs at } 20 \text{ mA each})$

$R_{OUT}(G = 1.5 \times) = 3 \Omega$  (obtained from Figure 12)

At the point of a gain transition,  $V_{DX} = V_{HR(UP)}$ . Table 1 gives the typical value of  $V_{HR(UP)}$  as 0.2 V. Therefore, the input voltage level when the gain transitions from  $1.5\times$  to  $2\times$  is

$$V_{IN} = (3.7 \text{ V} + 0.2 \text{ V} + 140 \text{ mA} \times 3 \Omega)/1.5 = 2.88 \text{ V}$$

#### **LAYOUT GUIDELINES**

Note the following layout guidelines:

- For optimal noise immunity, place the C<sub>IN</sub> and C<sub>OUT</sub> capacitors as close as possible to their respective pins. These capacitors should share a short ground trace. If the LEDs are a significant distance from the VOUT pin, another capacitor on VOUT, placed closer to the LEDs, is advisable.

- For optimal efficiency, place the charge pump fly capacitors (C1 and C2) as close to the part as possible.

- The ADP8863 does not distinguish between power ground and analog ground. Therefore, both ground pins can be connected directly together. It is recommended that these ground pins be connected at the ground for the input and output capacitors.

- The LFCSP package requires the exposed pad to be soldered at the board to the GND1 and/or GND2 pin(s).

- Unused diode pins (Pin D1 to Pin D7) can be connected to ground or to VOUT, or remain floating. However, the unused diode current sinks must be disabled by setting them as independent sinks in Register 0x05 and then disabling them in Register 0x10. If they are not disabled, the charge pump efficiency may suffer.

- If the CMP\_IN phototransistor input is not used, it can be connected to ground or remain floating.

- If the interrupt pin (nINT) is not used, connect it to ground or leave it floating. Never connect it to a voltage supply, except through a ≥1 kΩ series resistor.

- The ADP8863 has an integrated noise filter on the nRST pin. Under normal conditions, it is not necessary to filter the reset line. However, if the part is exposed to an unusually noisy signal, it is beneficial to add a small RC filter or bypass capacitor on this pin. If the nRST pin is not used, it must be pulled well above the V<sub>IH(MIN)</sub> level (see Table 1). Do not allow the nRST pin to float.

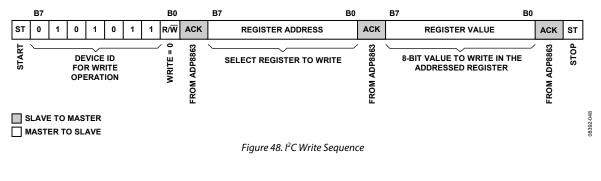

# I<sup>2</sup>C Programming and Digital Control

The ADP8863 provides full software programmability to facilitate its adoption in various product architectures. The  $I^2C$  address is 0101011x (x = 0 during write, x = 1 during read). Therefore, the write address is 0x56 and the read address is 0x57.

Note the following general behavior of registers:

- All registers are set to their default values during reset or after a UVLO event.

- All registers are read/write unless otherwise specified.

- Unused bits are read as zero.

■ MASTER TO SLAVE

Table 8 to Table 84 provide register and bit descriptions. The reset value for all bits in the bit map tables is all 0s, except in Table 10 (see Table 10 for its unique reset value). Wherever the acronym N/A appears in the tables, it means not applicable.

В7 R0 B7 B7 B7 B0 ST 0 0 0 R/W ACK REGISTER ADDRESS ACK RS 0 0 1 0 R/W ACK REGISTER VALUE ACK ST WRITE = 0 FROM ADP8863 FROM ADP8863 FROM ADP8863 READ = 1 FROM MASTER REPEATED START DEVICE ID FOR WRITE DEVICE ID FOR READ 8-BIT VALUE TO WRITE IN THE ADDRESSED REGISTER SELECT REGISTER TO WRITE OPERATION OPERATION SLAVE TO MASTER

Figure 49. I<sup>2</sup>C Read Sequence

**Table 8. Register Set Definitions**

| Address (Hex) | Register Name | Description                                                   |

|---------------|---------------|---------------------------------------------------------------|

| 0x00          | MFDVID        | Manufacturer and device ID                                    |

| 0x01          | MDCR          | Device mode and status                                        |

| 0x02          | MDCR2         | Device mode and Status Register 2                             |

| 0x03          | INTR_EN       | Interrupts enable                                             |

| 0x04          | CFGR          | Configuration register                                        |

| 0x05          | BLSEN         | Sink enable, backlight or independent                         |

| 0x06          | BLOFF         | Backlight off timeout                                         |

| 0x07          | BLDIM         | Backlight dim timeout                                         |

| 0x08          | BLFR          | Backlight fade in and fade out rates                          |

| 0x09          | BLMX1         | Backlight (brightness Level 1—daylight) maximum current       |

| 0x0A          | BLDM1         | Backlight (brightness Level 1—daylight) dim current           |

| 0x0B          | BLMX2         | Backlight (brightness Level 2—office) maximum current         |

| 0x0C          | BLDM2         | Backlight (brightness Level 2—office) dim current             |

| 0x0D          | BLMX3         | Backlight (brightness Level 3—dark) maximum current           |

| 0x0E          | BLDM3         | Backlight (brightness Level 3—dark) dim current               |

| 0x0F          | ISCFR         | Independent sink current fade control register                |

| 0x10          | ISCC          | Independent sink current control register                     |

| 0x11          | ISCT1         | Independent sink current timer register, LED[7:5]             |

| 0x12          | ISCT2         | Independent sink current timer register, LED[4:1]             |

| 0x13          | ISCF          | Independent sink current fade register                        |

| 0x14          | ISC7          | Independent sink current, LED7                                |

| 0x15          | ISC6          | Independent sink current, LED6                                |

| 0x16          | ISC5          | Independent sink current, LED5                                |

| 0x17          | ISC4          | Independent sink current, LED4                                |

| 0x18          | ISC3          | Independent sink current, LED3                                |

| 0x19          | ISC2          | Independent sink current, LED2                                |

| 0x1A          | ISC1          | Independent sink current, LED1                                |

| 0x1B          | CCFG          | Comparator configuration                                      |

| 0x1C          | CCFG2         | Second comparator configuration                               |

| 0x1D          | L2_TRP        | L2 comparator reference                                       |

| 0x1E          | L2_HYS        | L2 hysteresis                                                 |

| 0x1F          | L3_TRP        | L3 comparator reference                                       |

| 0x20          | L3_HYS        | L3 hysteresis                                                 |

| 0x21          | PH1LEVL       | First phototransistor ambient light level—low byte register   |

| 0x22          | PH1LEVH       | First phototransistor ambient light level—high byte register  |

| 0x23          | PH2LEVL       | Second phototransistor ambient light level—low byte register  |

| 0x24          | PH2LEVH       | Second phototransistor ambient light level—high byte register |

Table 9. Register Map

| Addr<br>(Hex) | Reg. Name | Bit 7      | Bit 6           | Bit 5    | Bit 4     | Bit 3    | Bit 2      | Bit 1      | Bit 0   |

|---------------|-----------|------------|-----------------|----------|-----------|----------|------------|------------|---------|

| 0x00          | MFDVID    | DIC 7      | Manufacturer ID |          |           | Dit 5    |            | evice ID   | Dico    |

| 0x01          | MDCR      | Reserved   | INT_CFG         | nSTBY    | DIM_EN    | GDWN_DIS | SIS_EN     | CMP_AUTOEN | BL_EN   |

| 0x02          | MDCR2     | Heservea   | Reserved        | 113131   | SHORT_INT | TSD_INT  | OVP_INT    | CMP2_INT   | CMP_INT |

| 0x03          | INTR_EN   |            | Reserved        |          | SHORT_IEN | TSD_IEN  | OVP_IEN    | CMP2_IEN   | CMP_IEN |

| 0x04          | CFGR      | Reserved   | SEL_AB          | CMP2_SEL | BL\       |          | 011_1211   | Law        | FOVR    |

| 0x05          | BLSEN     | Reserved   | D7EN            | D6EN     | D5EN      | D4EN     | D3EN       | D2EN       | D1EN    |

| 0x06          | BLOFF     | Reserved   |                 | I.       | l         | OFFT     | 1          | <u> </u>   |         |

| 0x07          | BLDIM     | Reserved   |                 |          |           | DIMT     |            |            |         |

| 0x08          | BLFR      |            |                 | BL_FO    |           |          |            | BL_FI      |         |

| 0x09          | BLMX1     | Reserved   |                 |          |           | BL1_MC   |            |            |         |

| 0x0A          | BLDM1     | Reserved   |                 |          |           | BL1_DC   |            |            |         |

| 0x0B          | BLMX2     | Reserved   |                 |          |           | BL2_MC   |            |            |         |

| 0x0C          | BLDM2     | Reserved   |                 |          |           | BL2_DC   |            |            |         |