12V Micro TLynx<sup>TM</sup>: Non-Isolated DC-DC Power Modules 4.5Vdc –14Vdc input; 0.69Vdc to 5.5Vdc output; 12A Output Current

# Applications

- Distributed power architectures

- Intermediate bus voltage applications

- Telecommunications equipment

- Servers and storage applications

- Networking equipment

- Industrial equipment

#### **Features**

- Compliant to RoHS EU Directive 2002/95/EC (Z versions)

- Compatible in a Pb-free or SnPb reflow environment (Z versions)

- Wide Input voltage range (4.5Vdc-14Vdc)

- Output voltage programmable from 0.69Vdc to 5.5 Vdc via external resistor

- Tunable Loop<sup>TM</sup> to optimize dynamic output voltage response

- Flexible output voltage sequencing EZ-SEQUENCE (APTS versions)

- Fixed switching frequency and ability to synchronize with external clock

- Output overcurrent protection (non-latching)

- Overtemperature protection

- Remote On/Off

- Remote Sense

- Power Good signal

- Fixed switching frequency

- Ability to sink and source current

- Small size: 20.3 mm x 11.4 mm x 8.5 mm (0.8 in x 0.45 in x 0.334 in)

- Wide operating temperature range [-40°C to 105°C(Ruggedized: -D), 85°C(Regular)]

- Ruggedized (-D) version able to withstand high levels of shock and vibration

- UL\* 60950-1Recognized, CSA<sup>†</sup> C22.2 No. 60950-1-03 Certified, and VDE<sup>‡</sup> 0805:2001-12 (EN60950-1) Licensed

- ISO\*\* 9001 and ISO 14001 certified manufacturing facilities

#### **Description**

The 12V Micro TLynx<sup>TM</sup> series of power modules are non-isolated dc-dc converters that can deliver up to 12A of output current. These modules operate over a wide range of input voltage ( $V_{IN} = 4.5 \text{Vdc}-14 \text{Vdc}$ ) and provide a precisely regulated output voltage from 0.69Vdc to 5.5Vdc, programmable via an external resistor. The new Ruggedized version (-D) is capable of operation up to 105°C and can withstand high levels of shock and vibration. Features include frequency synchronization, remote On/Off, adjustable output voltage, over current and overtemperature protection, power good and output voltage sequencing. A new feature, the Tunable Loop<sup>TM</sup>, allows the user to optimize the dynamic response of the converter to match the load with reduced amount of output capacitance leading to savings on cost and PWB area.

- \* UL is a registered trademark of Underwriters Laboratories, Inc.

- † CSA is a registered trademark of Canadian Standards Association.

- <sup>‡</sup> VDE is a trademark of Verband Deutscher Elektrotechniker e.V.

- \*\* ISO is a registered trademark of the International Organization of Standards

### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability.

| Parameter                            | Device     | Symbol            | Min  | Max             | Unit |

|--------------------------------------|------------|-------------------|------|-----------------|------|

| Input Voltage                        | All        | V <sub>IN</sub>   | -0.3 | 15              | Vdc  |

| Continuous                           |            |                   |      |                 |      |

| Voltage on SEQ terminal              | All        | $V_{SEQ}$         | -0.3 | V <sub>IN</sub> | Vdc  |

| Voltage on SYNC terminal             | All        | V <sub>SYNC</sub> | -0.3 | 12              | Vdc  |

| Voltage on PG terminal               | All        | $V_{PG}$          | -0.3 | 6               | Vdc  |

| Operating Ambient Temperature        | All        | T <sub>A</sub>    | -40  | 85              | °C   |

| (see Thermal Considerations section) | -D version | T <sub>A</sub>    | -40  | 105             | °C   |

| Storage Temperature                  | All        | T <sub>stg</sub>  | -55  | 125             | °C   |

#### **Electrical Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions.

| Parameter                                                                                                                                                                        | Device                 | Symbol                   | Min | Тур  | Max  | Unit             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|-----|------|------|------------------|

| Operating Input Voltage                                                                                                                                                          | All                    | V <sub>IN</sub>          | 4.5 | _    | 14.0 | Vdc              |

| Maximum Input Current                                                                                                                                                            | All                    | I <sub>IN,max</sub>      |     |      | 11.5 | Adc              |

| $(V_{IN}=4.5V \text{ to } 14V, I_{O}=I_{O, max})$                                                                                                                                |                        |                          |     |      |      |                  |

| Input No Load Current                                                                                                                                                            |                        |                          |     |      |      |                  |

| $(V_{IN} = 10.0 \text{Vdc}, I_O = 0, \text{ module enabled})$                                                                                                                    | $V_{O,set}$ = 0.69 Vdc | I <sub>IN,No load</sub>  |     | 26   |      | mA               |

| $(V_{IN} = 12.0 \text{Vdc}, I_O = 0, \text{ module enabled})$                                                                                                                    | $V_{O,set}$ = 3.3Vdc   | I <sub>IN,No load</sub>  |     | 60   |      | mA               |

| Input Stand-by Current                                                                                                                                                           | All                    | I <sub>IN,stand-by</sub> |     | 1.2  |      | mA               |

| (V <sub>IN</sub> = 12.0Vdc, module disabled)                                                                                                                                     |                        |                          |     |      |      |                  |

| Inrush Transient                                                                                                                                                                 | All                    | l <sup>2</sup> t         |     |      | 1    | A <sup>2</sup> s |

| Input Reflected Ripple Current, peak-to-peak (5Hz to 20MHz, 1 $\mu$ H source impedance; V <sub>IN</sub> =0 to 14V, I <sub>O</sub> = I <sub>Omax</sub> ; See Test Configurations) | All                    |                          |     | 12.4 |      | mAp-p            |

| Input Ripple Rejection (120Hz)                                                                                                                                                   | All                    |                          |     | 45   |      | dB               |

#### CAUTION: This power module is not internally fused. An input line fuse must always be used.

This power module can be used in a wide variety of applications, ranging from simple standalone operation to an integrated part of sophisticated power architecture. To preserve maximum flexibility, internal fusing is not included; however, to achieve maximum safety and system protection, always use an input line fuse. The safety agencies require a fast-acting fuse with a maximum rating of 15A (see Safety Considerations section). Based on the information provided in this data sheet on inrush energy and maximum dc input current, the same type of fuse with a lower rating can be used. Refer to the fuse manufacturer's data sheet for further information.

# **Electrical Specifications** (continued)

| Parameter                                                                                                                                                       | Device                        | Symbol              | Min  | Тур  | Max  | Unit                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|------|------|------|-----------------------|

| Output Voltage Set-point                                                                                                                                        | All                           | V <sub>O, set</sub> | -1.5 |      | +1.5 | % V <sub>O, set</sub> |

| Output Voltage                                                                                                                                                  | All                           | V <sub>O, set</sub> | -2.5 | _    | +2.5 | % V <sub>O, set</sub> |

| (Over all operating input voltage, resistive load, and temperature conditions until end of life)                                                                |                               |                     |      |      |      |                       |

| Adjustment Range (elected by an external resistor) (Some output voltages may not be possible depending on the input voltage – see Feature Descriptions Section) | All                           | Vo                  | 0.69 |      | 5.5  | Vdc                   |

| Output Regulation (for V <sub>0</sub> ≥ 2.5Vdc)                                                                                                                 |                               |                     |      |      |      |                       |

| Line $(V_{IN}=V_{IN, min} \text{ to } V_{IN, max})$                                                                                                             | All                           |                     |      | _    | +0.4 | $\% V_{O,  set}$      |

| Load ( $I_O = I_{O, min}$ to $I_{O, max}$ )                                                                                                                     | All                           |                     |      |      | 10   | mV                    |

| Output Regulation (for V <sub>O</sub> < 2.5Vdc)                                                                                                                 |                               |                     |      |      |      |                       |

| Line $(V_{IN}=V_{IN, min} \text{ to } V_{IN, max})$                                                                                                             | All                           |                     |      | _    | 10   | mV                    |

| Load ( $I_O = I_{O, min}$ to $I_{O, max}$ )                                                                                                                     | All                           |                     |      | _    | 5    | mV                    |

| Temperature ( $T_{ref}=T_{A, min}$ to $T_{A, max}$ )                                                                                                            | All                           |                     |      |      | 0.5  | $\% V_{O, set}$       |

| Remote Sense Range                                                                                                                                              | All                           |                     |      |      | 0.5  | Vdc                   |

| Output Ripple and Noise on nominal output                                                                                                                       |                               |                     |      |      |      |                       |

| ( $V_{IN}=V_{IN,nom}$ and $I_O=I_{O,min}$ to $I_{O,max}$ Co = 0.1 $\mu$ F // 10 $\mu$ F ceramic capacitors)                                                     |                               |                     |      |      |      |                       |

| Peak-to-Peak (5Hz to 20MHz bandwidth)                                                                                                                           | All                           |                     | _    | 65   | 80   | $mV_{pk-pk}$          |

| RMS (5Hz to 20MHz bandwidth)                                                                                                                                    | All                           |                     | _    | 23   | 28   | $mV_{rms}$            |

| External Capacitance <sup>1</sup>                                                                                                                               |                               |                     |      |      |      |                       |

| Without the Tunable Loop $^{TM}$                                                                                                                                |                               |                     |      |      |      |                       |

| ESR ≥ 1 mΩ                                                                                                                                                      | All                           | $C_{\text{O, max}}$ | 0    | _    | 100  | μF                    |

| With the Tunable Loop $^{TM}$                                                                                                                                   |                               |                     |      |      |      |                       |

| ESR ≥ $0.15 \text{ m}\Omega$                                                                                                                                    | All                           | $C_{\text{O, max}}$ | 0    | _    | 1000 | μF                    |

| ESR ≥ 10 mΩ                                                                                                                                                     | All                           | $C_{\text{O, max}}$ | 0    | _    | 5000 | μF                    |

| Output Current                                                                                                                                                  | All                           | I <sub>o</sub>      | 0    |      | 12   | Adc                   |

| Output Current Limit Inception (Hiccup Mode )                                                                                                                   | All                           | $I_{O, lim}$        |      | 150  |      | % I <sub>o,max</sub>  |

| Output Short-Circuit Current                                                                                                                                    | All                           | I <sub>O, s/c</sub> |      | 2    |      | Adc                   |

| (V <sub>o</sub> ≤250mV) ( Hiccup Mode )                                                                                                                         |                               |                     |      |      |      |                       |

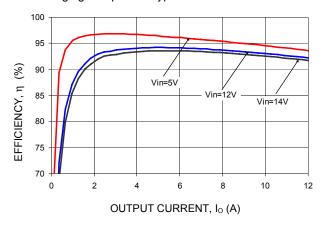

| Efficiency                                                                                                                                                      |                               |                     |      |      |      |                       |

| V <sub>IN</sub> = 10Vdc, T <sub>A</sub> =25°C                                                                                                                   | V <sub>O, set</sub> = 0.69Vdc | η                   |      | 76.0 |      | %                     |

| V <sub>IN</sub> = 12Vdc, T <sub>A</sub> =25°C                                                                                                                   | V <sub>O, set</sub> = 1.2Vdc  | η                   |      | 83.0 |      | %                     |

| $I_{O}=I_{O, max}, V_{O}=V_{O, set}$                                                                                                                            | V <sub>O,set</sub> = 1.8Vdc   | η                   |      | 87.6 |      | %                     |

|                                                                                                                                                                 | V <sub>O,set</sub> = 2.5Vdc   | η                   |      | 90.2 |      | %                     |

|                                                                                                                                                                 | $V_{O,set}$ = 3.3Vdc          | η                   |      | 92.2 |      | %                     |

|                                                                                                                                                                 | $V_{O,set} = 5.0Vdc$          | η                   |      | 94.3 |      | %                     |

External capacitors may require using the new Tunable Loop<sup>TM</sup> feature to ensure that the module is stable as well as getting the best transient response. See the Tunable Loop<sup>TM</sup> section for details.

# **Electrical Specifications (continued)**

| Parameter                                                               | Device                  | Symbol               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------|-------------------------|----------------------|-----|-----|-----|------|

| Switching Frequency                                                     | All                     | $f_{sw}$             |     | 500 | _   | kHz  |

| Frequency Synchronization                                               |                         |                      |     |     |     |      |

| Synchronization Frequency Range                                         |                         |                      | 520 |     | 600 | kHz  |

| High-Level Input Voltage                                                | All                     | $V_{IH}$             | 2.5 |     |     | V    |

| Low-Level Input Voltage                                                 | All                     | $V_{IL}$             |     |     | 0.8 | V    |

| Input Current, SYNC                                                     | V <sub>SYNC</sub> =2.5V | I <sub>SYNC</sub>    |     |     | 1   | mA   |

| Minimum Pulse Width, SYNC                                               | All                     | t <sub>SYNC</sub>    | 250 |     |     | ns   |

| Minimum Setup/Hold Time, SYNC <sup>2</sup>                              | All                     | t <sub>SYNC_SH</sub> | 250 |     |     | ns   |

| Dynamic Load Response                                                   |                         |                      |     |     |     |      |

| $(dlo/dt=1A/\mu s; V_{IN} = V_{IN, nom}; T_A=25^{\circ}C)$              |                         |                      |     |     |     |      |

| Load Change from lo= 50% to 100% of lo,max; 1µF ceramic// 10 µF ceramic |                         |                      |     |     |     |      |

| Peak Deviation                                                          | All                     | $V_{pk}$             | _   | 360 |     | mV   |

| Settling Time (Vo<10% peak deviation)                                   | All                     | $t_s$                | _   | 50  | _   | μs   |

| $(dlo/dt=1A/\mu s; V_{IN} = V_{IN, nom}; T_A=25^{\circ}C)$              |                         |                      |     |     |     |      |

| Load Change from lo= 100% to 50%of lo,max: 1µF ceramic// 10 µF ceramic  |                         |                      |     |     |     |      |

| Peak Deviation                                                          | All                     | $V_{pk}$             | _   | 400 |     | mV   |

| Settling Time (Vo<10% peak deviation)                                   | All                     | ts                   | _   | 50  | _   | μs   |

<sup>&</sup>lt;sup>2</sup> To meet set up time requirements for the synchronization circuit, the logic low width of the pulse must be greater than 100 ns wide.

# **General Specifications**

| Parameter                                                                                  | Min | Тур          | Max | Unit    |

|--------------------------------------------------------------------------------------------|-----|--------------|-----|---------|

| Calculated MTBF ( $I_0$ =0.8 $I_{O, max}$ , $T_A$ =40°C) Telcordia Issue 2 Method 1 Case 3 |     | 16,250,892   |     | Hours   |

| Weight                                                                                     |     | 3.68 (0.130) |     | g (oz.) |

# **Feature Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                                                                                                                                                                                                        | Device | Symbol     | Min                 | Тур  | Max           | Unit                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|---------------------|------|---------------|-----------------------|

| On/Off Signal Interface                                                                                                                                                                                                          |        |            |                     |      |               |                       |

| $(V_{IN}=V_{IN,min}$ to $V_{IN,max}$ ; open collector or equivalent,                                                                                                                                                             |        |            |                     |      |               |                       |

| Signal referenced to GND)                                                                                                                                                                                                        |        |            |                     |      |               |                       |

| Device is with suffix "4" – Positive Logic (See Ordering Information)                                                                                                                                                            |        |            |                     |      |               |                       |

| Logic High (Module ON)                                                                                                                                                                                                           |        |            |                     |      |               |                       |

| Input High Current                                                                                                                                                                                                               | All    | Іін        | _                   |      | 25            | μA                    |

| Input High Voltage                                                                                                                                                                                                               | All    | ViH        | V <sub>IN</sub> – 1 |      | $V_{IN,max}$  | V                     |

| Logic Low (Module OFF)                                                                                                                                                                                                           |        |            |                     |      |               |                       |

| Input Low Current                                                                                                                                                                                                                | All    | lıL        | _                   |      | 3             | mA                    |

| Input Low Voltage                                                                                                                                                                                                                | All    | VIL        | _                   | _    | 3.5           | V                     |

| Device Code with no suffix – Negative Logic (See Ordering Information)                                                                                                                                                           |        |            |                     |      |               |                       |

| (On/OFF pin is open collector/drain logic input with                                                                                                                                                                             |        |            |                     |      |               |                       |

| external pull-up resistor; signal referenced to GND)                                                                                                                                                                             |        |            |                     |      |               |                       |

| Logic High (Module OFF)                                                                                                                                                                                                          |        |            |                     |      |               |                       |

| Input High Current                                                                                                                                                                                                               | All    | lıн        | _                   | _    | 1             | mA                    |

| Input High Voltage                                                                                                                                                                                                               | All    | VIH        | 2.0                 | _    | $V_{IN, max}$ | Vdc                   |

| Logic Low (Module ON)                                                                                                                                                                                                            |        |            |                     |      |               |                       |

| Input low Current                                                                                                                                                                                                                | All    | lıL        | _                   | _    | 10            | μA                    |

| Input Low Voltage                                                                                                                                                                                                                | All    | VIL        | 0                   | _    | 1             | Vdc                   |

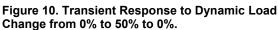

| Turn-On Delay and Rise Times                                                                                                                                                                                                     |        |            |                     |      |               |                       |

| $(V_{IN}=V_{IN, nom}, I_O=I_{O, max}, V_O)$ to within ±1% of steady state)<br>Case 1: On/Off input is enabled and then input power is applied (delay from instant at which $V_{IN}=V_{IN, min}$ until $V_O=10\%$ of $V_O$ , set) | All    | Tdelay     | _                   | 2    | _             | msec                  |

| Case 2: Input power is applied for at least one second and then the On/Off input is enabled (delay from instant at which Von/Off is enabled until $V_0 = 10\%$ of $V_{0, set}$ )                                                 | All    | Tdelay     | _                   | 2    | _             | msec                  |

| Output voltage Rise time (time for V <sub>0</sub> to rise from 10% of V <sub>0</sub> , set to 90% of V <sub>0</sub> , set)                                                                                                       | All    | Trise      | _                   | 5    | _             | msec                  |

| Output voltage overshoot (T <sub>A</sub> = 25°C                                                                                                                                                                                  |        |            |                     |      | 3.0           | % V <sub>O, set</sub> |

| $V_{IN} = V_{IN, min}$ to $V_{IN, max}$ , $I_O = I_{O, min}$ to $I_{O, max}$ )                                                                                                                                                   |        |            |                     |      |               |                       |

| With or without maximum external capacitance                                                                                                                                                                                     |        |            |                     |      |               |                       |

| Over Temperature Protection                                                                                                                                                                                                      | All    | $T_{ref}$  |                     | 133  |               | °C                    |

| (See Thermal Considerations section)                                                                                                                                                                                             |        |            |                     |      |               |                       |

| Sequencing Delay time                                                                                                                                                                                                            |        |            |                     |      |               |                       |

| Delay from $V_{\text{IN, min}}$ to application of voltage on SEQ pin                                                                                                                                                             | All    | TsEQ-delay | 10                  |      |               | msec                  |

| Tracking Accuracy (Power-Up: 0.5V/ms)                                                                                                                                                                                            | All    | VSEQ -Vo   |                     |      | 100           | mV                    |

| (Power-Down: 0.5V/ms)                                                                                                                                                                                                            | All    | VSEQ -Vo   |                     |      | 150           | mV                    |

| $(V_{\text{IN, min}} \text{ to } V_{\text{IN, max}};  I_{\text{O, min}} \text{ to } I_{\text{O, max}}  \text{VSEQ} < V_0)$                                                                                                       |        |            |                     |      |               |                       |

| Input Undervoltage Lockout                                                                                                                                                                                                       |        |            |                     |      |               |                       |

| Turn-on Threshold                                                                                                                                                                                                                | All    |            |                     | 4.45 |               | Vdc                   |

| Turn-off Threshold                                                                                                                                                                                                               | All    |            |                     | 4.2  |               | Vdc                   |

| Hysteresis                                                                                                                                                                                                                       | All    |            |                     | 0.25 |               | Vdc                   |

# **Feature Specifications (continued)**

| Parameter                                               | Device | Symbol | Min | Тур   | Max | Units         |

|---------------------------------------------------------|--------|--------|-----|-------|-----|---------------|

| PGOOD (Power Good)                                      |        |        |     |       |     |               |

| Signal Interface Open Drain, V <sub>supply</sub> ≤ 6VDC |        |        |     |       |     |               |

| Overvoltage threshold for PGOOD                         |        |        |     | 110.8 |     | $%V_{O, set}$ |

| Undervoltage threshold for PGOOD                        |        |        |     | 89.1  |     | $%V_{O, set}$ |

| Pulldown resistance of PGOOD pin                        | All    |        |     | 7     | 50  | Ω             |

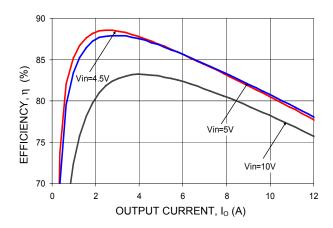

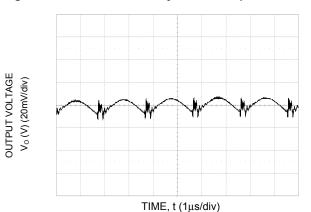

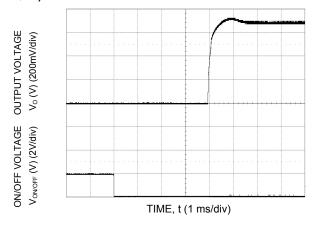

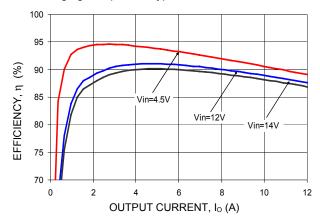

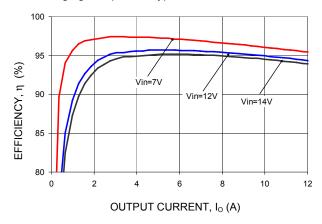

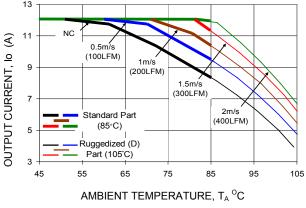

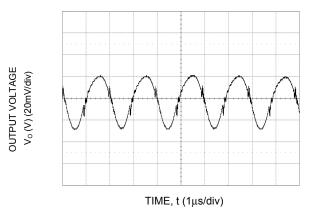

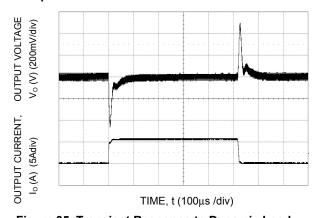

#### **Characteristic Curves**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 0.69Vo and at 25°C.

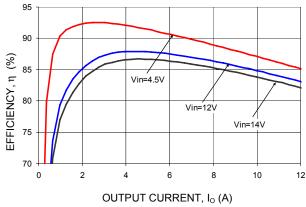

Figure 1. Converter Efficiency versus Output Current.

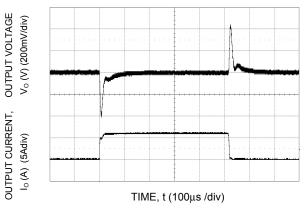

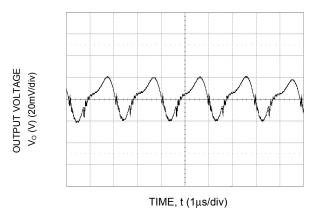

Figure 3. Typical output ripple and noise ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

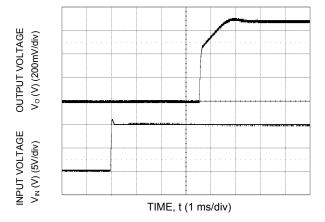

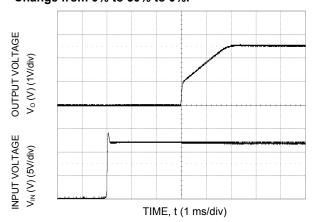

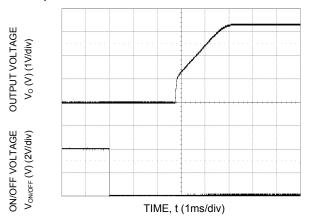

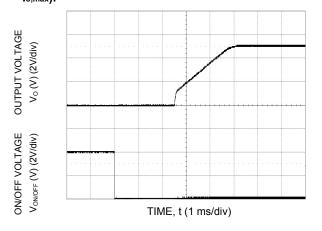

Figure 5. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

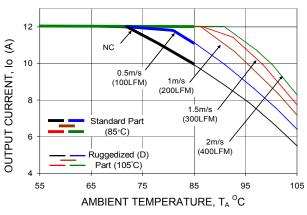

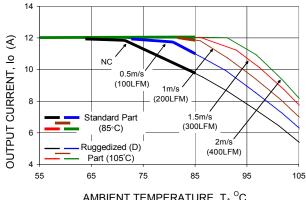

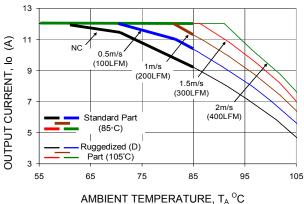

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

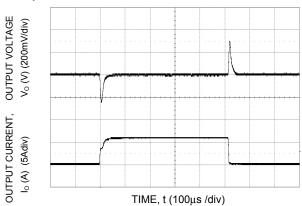

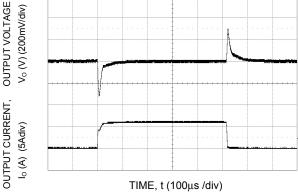

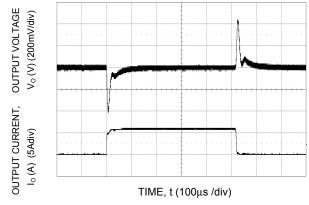

Figure 4. Transient Response to Dynamic Load Change from 0% to 50% to 0%.

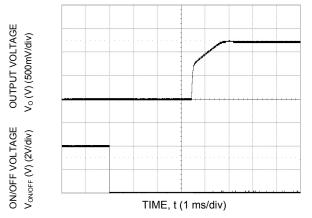

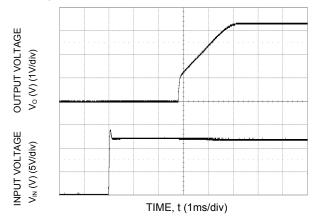

Figure 6. Typical Start-up Using Input Voltage ( $V_{IN} = 10V$ ,  $I_0 = I_{o,max}$ ).

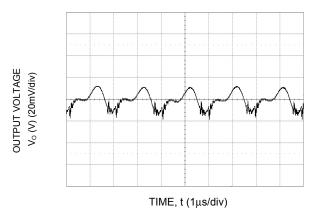

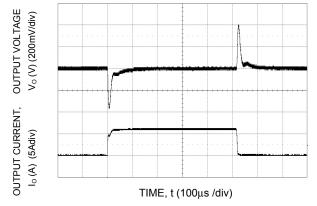

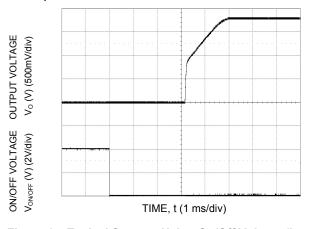

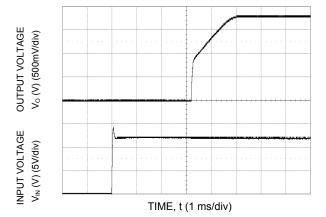

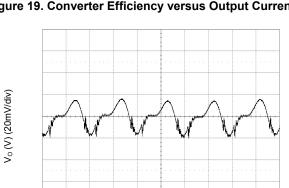

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 1.2Vo and at 25°C.

OUTPUT CURRENT, I<sub>O</sub> (A)

AMBIENT TEMPERATURE, T<sub>A</sub> °C

Figure 7. Converter Efficiency versus Output Current.

Figure 8. Derating Output Current versus Ambient

OUTPUT VOLTAGE

Vo. (V) (20mV/div)

TIME' t (1/ms/qiv)

Temperature and Airflow.

Figure 9. Typical output ripple and noise ( $V_{IN}$  = 12 $V_{t}$ ,  $I_{o}$  =  $I_{o,max}$ ).

INPUT VOLTAGE

V<sub>IN</sub> (V) (5V/div)

V<sub>O</sub> (V) (500mV/div)

TIME' t (1 ms/qiv)

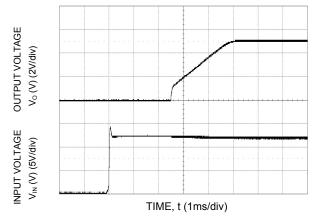

Figure 11. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 12. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

14

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 1.8Vo and at 25°C.

NC 0.5m/s (100LFM) 1m/s 8 8 (200LFM) (200LFM) 2m/s (400LFM) 4 55 65 75 85 95 105 AMBIENT TEMPERATURE, T<sub>A</sub> °C

Figure 13. Converter Efficiency versus Output Current.

Figure 14. Derating Output Current versus Ambient Temperature and Airflow.

Figure 15. Typical output ripple and noise ( $V_{IN}$  = 12V,  $I_{o}$  =  $I_{o,max}$ ).

Figure 16. Transient Response to Dynamic Load Change from 0% to 50% to 0%.

Figure 17. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 18. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

**OUTPUT VOLTAGE**

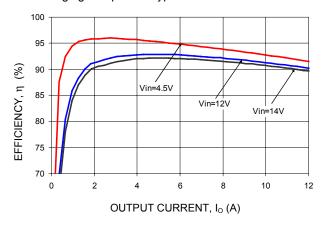

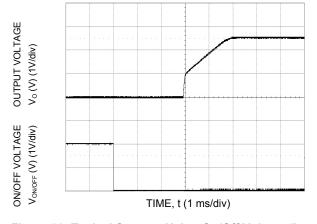

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 2.5Vo and at 25°C.

Figure 19. Converter Efficiency versus Output Current.

TIME, t (1µs/div)

Figure 21. Typical output ripple and noise (VIN = 12V, Io  $= I_{o,max}$ ).

Figure 23. Typical Start-up Using On/Off Voltage (Io = lo,max).

Figure 20. Derating Output Current versus Ambient Temperature and Airflow.

Figure 22. Transient Response to Dynamic Load Change from 0% to 50% to 0%.

Figure 24. Typical Start-up Using Input Voltage (VIN = 12V,  $I_0 = I_{0,max}$ ).

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 3.3Vo and at 25°C.

Figure 25. Converter Efficiency versus Output Current.

Figure 26. Derating Output Current versus Ambient Temperature and Airflow.

Figure 27. Typical output ripple and noise ( $V_{IN}$  = 12V,  $I_{o}$  =  $I_{o,max}$ ).

Figure 28. Transient Response to Dynamic Load Change from 0% 50% to 0%.

Figure 29. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 30. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

## **Characteristic Curves (continued)**

The following figures provide typical characteristics for the 12V Micro TLynx<sup>TM</sup> at 5Vo and at 25°C.

Figure 31. Converter Efficiency versus Output Current.

Figure 34. Derating Output Current versus Ambient Temperature and Airflow.

Figure 32. Typical output ripple and noise ( $V_{IN} = 12V$ ,  $I_o = I_{o,max}$ ).

Figure 35. Transient Response to Dynamic Load Change from 0% 50% to 0%.

Figure 33. Typical Start-up Using On/Off Voltage ( $I_0 = I_{0,max}$ ).

Figure 36. Typical Start-up Using Input Voltage ( $V_{IN} = 12V$ ,  $I_0 = I_{0,max}$ ).

## **Test Configurations**

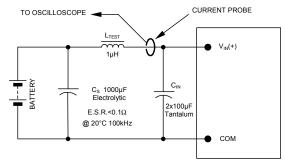

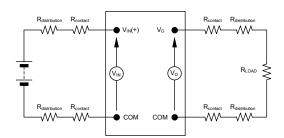

NOTE: Measure input reflected ripple current with a simulated source inductance ( $L_{TEST}$ ) of 1 $\mu$ H. Capacitor  $C_S$  offsets possible battery impedance. Measure current as shown above

# Figure 37. Input Reflected Ripple Current Test Setup.

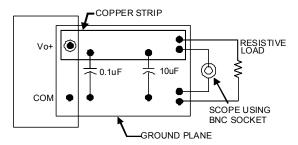

NOTE: All voltage measurements to be taken at the module terminals, as shown above. If sockets are used then Kelvin connections are required at the module terminals to avoid measurement errors due to socket contact resistance.

Figure 38. Output Ripple and Noise Test Setup.

NOTE: All voltage measurements to be taken at the module terminals, as shown above. If sockets are used then Kelvin connections are required at the module terminals to avoid measurement errors due to socket contact resistance.

Figure 39. Output Voltage and Efficiency Test Setup.

Efficiency

$$\eta = \frac{V_{0.} I_{0}}{V_{IN.} I_{IN}} \times 100 \%$$

### **Design Considerations**

#### **Input Filtering**

The 12V Micro TLynx<sup>TM</sup> module should be connected to a low ac-impedance source. A highly inductive source can affect the stability of the module. An input capacitance must be placed directly adjacent to the input pin of the module, to minimize input ripple voltage and ensure module stability.

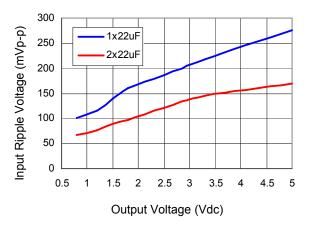

To minimize input voltage ripple, ceramic capacitors are recommended at the input of the module. Figure 40 shows the input ripple voltage for various output voltages at 6A of load current with 1x22  $\mu$ F or 2x22  $\mu$ F ceramic capacitors and an input of 12V.

Figure 40. Input ripple voltage for various output voltages with 1x22  $\mu$ F or 2x22  $\mu$ F ceramic capacitors at the input (12A load). Input voltage is 12V.

## **Output Filtering**

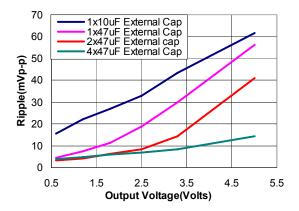

The 12V Micro TLynx  $^{TM}$  modules are designed for low output ripple voltage and will meet the maximum output ripple specification with 0.1  $\mu$ F ceramic and 10  $\mu$ F ceramic capacitors at the output of the module. However, additional output filtering may be required by the system designer for a number of reasons. First, there may be a need to further reduce the output ripple and noise of the module. Second, the dynamic response characteristics may need to be customized to a particular load step change.

To reduce the output ripple and improve the dynamic response to a step load change, additional capacitance at the output can be used. Low ESR polymer and ceramic capacitors are recommended to improve the dynamic response of the module. Figure 41 provides output ripple information for different external capacitance values at various Vo and for full load currents of 12A. For stable operation of the module, limit the capacitance to less than the maximum output capacitance as specified in the electrical specification table. Optimal performance of the module can be

achieved by using the Tunable Loop<sup>TM</sup> feature described later in this data sheet.

Figure 41. Output ripple voltage for various output voltages with external 1x10  $\mu$ F, 1x47  $\mu$ F, 2x47  $\mu$ F or 4x47  $\mu$ F ceramic capacitors at the output (12A load). Input voltage is 12V.

## **Safety Considerations**

For safety agency approval the power module must be installed in compliance with the spacing and separation requirements of the end-use safety agency standards, i.e., UL 60950-1, CSA C22.2 No. 60950-1-03, and VDE 0850:2001-12 (EN60950-1) Licensed.

For the converter output to be considered meeting the requirements of safety extra-low voltage (SELV), the input must meet SELV requirements. The power module has extra-low voltage (ELV) outputs when all inputs are ELV.

The input to these units is to be provided with a fastacting fuse with a maximum rating of 15A in the positive input lead.

## **Feature Descriptions**

#### **Remote Enable**

The 12V Micro TLynx<sup>TM</sup> modules feature an On/Off pin for remote On/Off operation. Two On/Off logic options are available. In the Positive Logic On/Off option, (device code suffix "4" see Ordering Information), the module turns ON during a logic High on the On/Off pin and turns OFF during a logic Low. With the Negative Logic On/Off option, (no device code suffix see Ordering Information), the module turns OFF during logic High and ON during logic Low. The On/Off signal is always referenced to ground. For either On/Off logic option, leaving the On/Off pin disconnected will turn the module ON when input voltage is present.

For positive logic modules, the circuit configuration for using the On/Off pin is shown in Figure 42. When the external transistor Q1 is in the OFF state, the internal PWM Enable signal is pulled high through an internal 24.9k $\Omega$  resistor and the external pullup resistor and the module is ON. When transistor Q1 is turned ON, the On/Off pin is pulled low and the module is OFF. A suggested value for  $R_{\text{pullup}}$  is  $20k\Omega$ .

Figure 42. Circuit configuration for using positive On/Off logic.

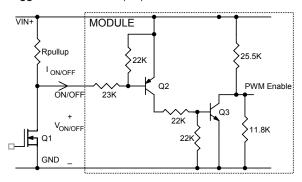

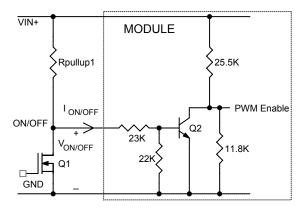

For negative logic On/Off modules, the circuit configuration is shown in Fig. 43. The On/Off pin should be pulled high with an external pull-up resistor (suggested value for the 4.5V to 14V input range is 20Kohms). When transistor Q1 is in the OFF state, the On/Off pin is pulled high, internal transistor Q2 is turned ON and the module is OFF. To turn the module ON, Q1 is turned ON pulling the On/Off pin low, turning transistor Q2 OFF resulting in the PWM Enable pin going high and the module turning ON.

#### **Overcurrent Protection**

To provide protection in a fault (output overload) condition, the unit is equipped with internal current-limiting circuitry and can endure current limiting continuously. At the point of current-limit inception, the unit enters hiccup mode. The unit operates normally once the output current is brought back into its specified range.

Figure 43. Circuit configuration for using negative On/Off logic.

#### **Over Temperature Protection**

To provide protection in a fault condition, the unit is equipped with a thermal shutdown circuit. The unit will shutdown if the overtemperature threshold of  $133^{\circ}$ C is exceeded at the thermal reference point  $T_{ref.}$  The thermal shutdown is not intended as a guarantee that the unit will survive temperatures beyond its rating. Once the unit goes into thermal shutdown it will then wait to cool before attempting to restart.

#### Input Undervoltage Lockout

At input voltages below the input undervoltage lockout limit, the module operation is disabled. The module will begin to operate at an input voltage above the undervoltage lockout turn-on threshold.

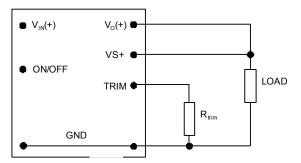

#### **Output Voltage Programming**

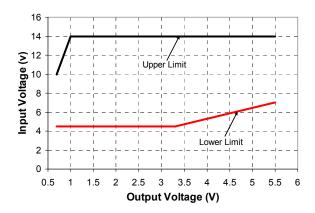

The output voltage of the 12V Micro TLynx<sup>TM</sup> module can be programmed to any voltage from 0.69dc to 5.5Vdc by connecting a resistor between the Trim and GND pins of the module. Certain restrictions apply on the output voltage set point depending on the input voltage. These are shown in the Output Voltage vs. Input Voltage Set Point Area plot in Fig. 44. The Upper Limit curve shows that for output voltages of 0.9V and lower, the input voltage must be lower than the maximum of 14V. The Lower Limit curve shows that for output voltages of 3.3V and higher, the input voltage needs to be larger than the minimum of 4.5V.

Without an external resistor between Trim and GND pins, the output of the module will be 0.69Vdc. To calculate the value of the trim resistor, *Rtrim* for a desired output voltage, use the following equation:

$$Rtrim = \left[ \frac{6.9}{(Vo - 0.69)} \right] k\Omega$$

Rtrim is the external resistor in  $k\Omega$ , and  $\mathit{Vo}$  is the desired output voltage.

Figure 44. Output Voltage vs. Input Voltage Set Point Area plot showing limits where the output voltage can be set for different input voltages.

Table 1 provides Rtrim values required for some common output voltages.

Table 1

| V <sub>O, set</sub> (V) | Rtrim (KΩ) |

|-------------------------|------------|

| 0.7                     | 690        |

| 1.0                     | 22.26      |

| 1.2                     | 13.53      |

| 1.5                     | 8.519      |

| 1.8                     | 6.216      |

| 2.5                     | 3.812      |

| 3.3                     | 2.644      |

| 5.0                     | 1.601      |

By using a  $\pm 0.5\%$  tolerance trim resistor with a TC of  $\pm 100$ ppm, a set point tolerance of  $\pm 1.5\%$  can be achieved as specified in the electrical specification.

#### **Remote Sense**

The 12V Micro TLynx<sup>TM</sup> power modules have a Remote Sense feature to minimize the effects of distribution losses by regulating the voltage between the VS+ and VS- pins. The voltage between the VS- and GND pins of the module must not drop below -0.2V. If Remote Sense is being used, the voltage between VS+ and VS-cannot be more than 0.5V larger than the voltage between VOUT and GND. Note that the output voltage of the module cannot exceed the specified maximum value. When the Remote Sense feature is not being used, connect the VS+ pin to the VOUT pin and the VS-pin to the GND pin.

#### **Monotonic Start-up and Shutdown**

The 12V Micro TLynx<sup>TM</sup> modules have monotonic startup and shutdown behavior for any combination of rated input voltage, output current and operating temperature range.

Figure 45. Circuit configuration for programming output voltage using an external resistor.

## **Startup into Pre-biased Output**

The 12V Micro TLynx<sup>TM</sup> 12A modules can start into a prebiased output as long as the prebias voltage is 0.5V less than the set output voltage. Note that prebias operation is not supported when output voltage sequencing is used.

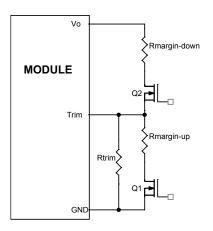

#### **Voltage Margining**

Output voltage margining can be implemented in the 12V Micro TLynx<sup>TM</sup> modules by connecting a resistor, R<sub>margin-up</sub>, from the Trim pin to the ground pin for margining-up the output voltage and by connecting a resistor, R<sub>margin-down</sub>, from the Trim pin to output pin for margining-down. Figure 46 shows the circuit configuration for output voltage margining. The Lynx Programming Tool, available at www.lineagepower.com under the Design Tools section, also calculates the values of R<sub>margin-up</sub> and R<sub>margin-down</sub> for a specific output voltage and % margin Please consult your local Lineage Power technical representative for additional details.

#### **Output Voltage Sequencing**

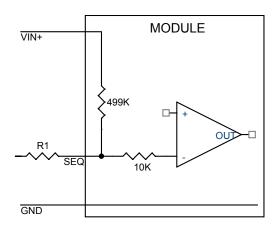

The 12V Micro TLynx<sup>TM</sup> modules include a sequencing feature, EZ-SEQUENCE that enables users to implement various types of output voltage sequencing in their applications. This is accomplished via an additional sequencing pin. When not using the sequencing feature, either tie the SEQ pin to VIN or leave it unconnected.

When an analog voltage is applied to the SEQ pin, the output voltage tracks this voltage until the output reaches the set-point voltage. The final value of the SEQ voltage must be set higher than the set-point voltage of the module. The output voltage follows the voltage on the SEQ pin on a one-to-one volt basis. By connecting multiple modules together, multiple modules can track their output voltages to the voltage applied on the SEQ pin.

Figure 46. Circuit Configuration for margining Output voltage

For proper voltage sequencing, first, input voltage is applied to the module. The On/Off pin of the module is left unconnected (or tied to GND for negative logic modules or tied to VIN for positive logic modules) so that the module is ON by default. After applying input voltage to the module, a minimum 10msec delay is required before applying voltage on the SEQ pin. During this time, a voltage of 50mV (± 20 mV) is maintained on the SEQ pin.

This can be done by applying the sequencing voltage through a resistor R1connected in series with the SEQ pin. This delay gives the module enough time to complete its internal power-up soft-start cycle. During the delay time, the SEQ pin should be held close to ground (nominally  $50\text{mV} \pm 20\text{ mV}$ ). This is required to keep the internal op-amp out of saturation thus preventing output overshoot during the start of the sequencing ramp. By selecting resistor R1 (see fig. 47) according to the following equation

$$R1 = \frac{24950}{V_{IN} - 0.05} \text{ ohms,}$$

the voltage at the sequencing pin will be 50mV when the sequencing signal is at zero.

After the 10msec delay, an analog voltage is applied to the SEQ pin and the output voltage of the module will track this voltage on a one-to-one volt bases until the output reaches the set-point voltage. To initiate simultaneous shutdown of the modules, the SEQ pin voltage is lowered in a controlled manner. The output voltage of the modules tracks the voltages below their set-point voltages on a one-to-one basis. A valid input voltage must be maintained until the tracking and output voltages reach ground potential.

Figure 47. Circuit showing connection of the sequencing signal to the SEQ pin.

When using the EZ-SEQUENCE<sup>™</sup> feature to control start-up of the module, pre-bias immunity during start-up is disabled. The pre-bias immunity feature of the module relies on the module being in the diode-mode during start-up. When using the EZ-SEQUENCE" feature, modules goes through an internal set-up time of 10msec, and will be in synchronous rectification mode when the voltage at the SEQ pin is applied. This will result in the module sinking current if a pre-bias voltage is present at the output of the module. When pre-bias immunity during start-up is required, the EZ-SEQUENCE<sup>TM</sup> feature must be disabled. For additional guidelines on using the  $\mathsf{EZ}\text{-}\mathsf{SEQUENCE}^\mathsf{TM}$ feature please refer to Application Note AN04-008 "Application Guidelines for Non-Isolated Converters: Guidelines for Sequencing of Multiple Modules", or contact the Lineage Power technical representative for additional information.

#### **Power Good**

The 12V Mlcro TLynx<sup>TM</sup> 12A modules provide a Power Good (PGOOD) signal that is implemented with an open-drain output to indicate that the output voltage is within the regulation limits of the power module. The PGOOD signal will be de-asserted to a low state if any condition such as overtemperature, overcurrent or loss of regulation occurs that would result in the output voltage going  $\pm 11\%$  outside the setpoint value. The PGOOD terminal should be connected through a pullup resistor (suggested value  $100 \text{K}\Omega$ ) to a source of 6VDC or less.

#### **Synchronization**

The 12V Micro TLynx<sup>TM</sup> series of modules can be synchronized using an external signal. Details of the SYNC signal are provided in the Electrical Specifications table. If the synchronization function is not being used, leave the SYNC pin floating.

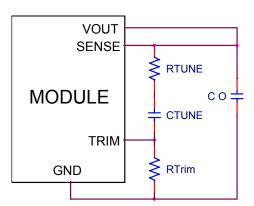

## Tunable Loop<sup>™</sup>

The 12V Micro TLynx<sup>TM</sup> 12A modules have a new feature that optimizes transient response of the module called Tunable Loop<sup>TM</sup>.

External capacitors are usually added to the output of the module for two reasons: to reduce output ripple and noise (see Figure 41) and to reduce output voltage deviations from the steady-state value in the presence of dynamic load current changes. Adding external capacitance however affects the voltage control loop of the module, typically causing the loop to slow down with sluggish response. Larger values of external capacitance could also cause the module to become unstable.

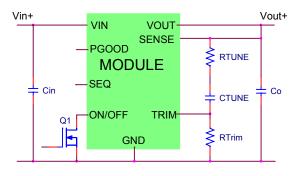

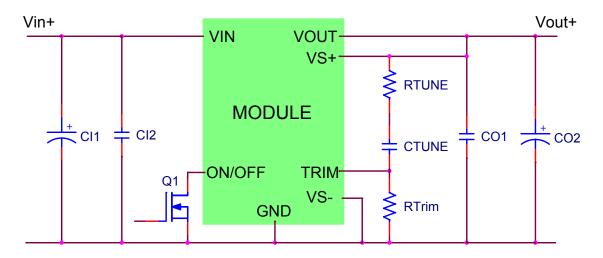

The Tunable Loop<sup>TM</sup> allows the user to externally adjust the voltage control loop to match the filter network connected to the output of the module. The Tunable Loop<sup>TM</sup> is implemented by connecting a series R-C between the SENSE and TRIM pins of the module, as shown in Fig. 48. This R-C allows the user to externally adjust the voltage loop feedback compensation of the module.

Recommended values of  $R_{TUNE}$  and  $C_{TUNE}$  for different output capacitor combinations are given in Tables 2 and 3. Table 2 shows the recommended values of  $R_{TUNE}$  and  $C_{TUNE}$  for different values of ceramic output capacitors up to  $940\mu F$  that might be needed for an application to meet output ripple and noise requirements. Selecting  $R_{TUNE}$  and  $C_{TUNE}$  according to Table 2 will ensure stable operation of the module

Figure. 48. Circuit diagram showing connection of  $R_{\text{TUME}}$  and  $C_{\text{TUNE}}$  to tune the control loop of the module.

In applications with tight output voltage limits in the presence of dynamic current loading, additional output capacitance will be required. Table 3 lists recommended values of  $R_{\text{TUNE}}$  and  $C_{\text{TUNE}}$  in order to meet 2% output voltage deviation limits for some common output voltages in the presence of a 6A to 12A step change (50% of full load), with an input voltage of 12V.

Please contact your Lineage Power technical representative to obtain more details of this feature as well as for guidelines on how to select the right value of

external R-C to tune the module for best transient performance and stable operation for other output capacitance values or input voltages other than 12V.

Table 2. General recommended values of of  $R_{\text{TUNE}}$  and  $C_{\text{TUNE}}$  for Vin=12V and various external ceramic capacitor combinations.

| I | Со                | 1x47μF | 2x47μF | 4x47μF | 10x47μF | 20x47μF |

|---|-------------------|--------|--------|--------|---------|---------|

| Ī | R <sub>TUNE</sub> | 470    | 270    | 150    | 150     | 150     |

| Ī | C <sub>TUNE</sub> | 1000pF | 3300pF | 4700pF | 8200pF  | 12nF    |

Table 3. Recommended values of  $R_{TUNE}$  and  $C_{TUNE}$  to obtain transient deviation of 2% of Vout for a 6A step load with Vin=12V.

| Vo                | 5V       | 3.3V    | 2.5V    | 1.8V    | 1.2V    | 0.69V   |

|-------------------|----------|---------|---------|---------|---------|---------|

|                   |          | 1x47μF  | 2x47μF  | 6x47μF  | 6x47μF  | 4x47μF  |

| Co                | 4x47μF   | +       | +       | +       | +       | +       |

|                   | 1χ 17 μι | 330μF   | 330μF   |         | 2x330μF |         |

|                   |          | Polymer | Polymer | Polymer | Polymer | Polymer |

| R <sub>TUNE</sub> | 270      | 220     | 220     | 220     | 150     | 150     |

| C <sub>TUNE</sub> | 3300pF   | 4700pF  | 6800pF  | 18nF    | 33nF    | 100nF   |

| ΔV                | 91mV     | 60mV    | 47mV    | 35mV    | 23mV    | 12mV    |

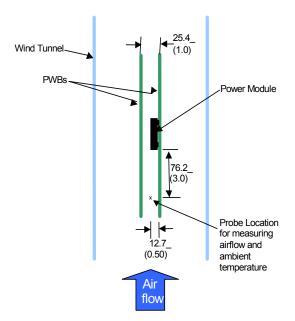

#### **Thermal Considerations**

Power modules operate in a variety of thermal environments; however, sufficient cooling should always be provided to help ensure reliable operation.

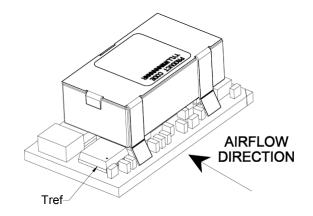

Considerations include ambient temperature, airflow, module power dissipation, and the need for increased reliability. A reduction in the operating temperature of the module will result in an increase in reliability. The thermal data presented here is based on physical measurements taken in a wind tunnel. The test set-up is shown in Figure 49. The preferred airflow direction for the module is in Figure 50. The derating data applies to airflow in either direction of the module's short axis.

Figure 49. Thermal Test Setup.

The thermal reference points,  $T_{ref}$  used in the specifications are also shown in Figure 50. For reliable operation the temperatures at these points should not exceed 125°C. The output power of the module should not exceed the rated power of the module (Vo,set x lo,max).

Please refer to the Application Note "Thermal Characterization Process For Open-Frame Board-Mounted Power Modules" for a detailed discussion of thermal aspects including maximum device temperatures.

Figure 50. Preferred airflow direction and location of hot-spot of the module (Tref).

Modules marked ruggedized with a "D" suffix operate up to an ambient of 105°C. For the remaining types derating curves for individual output voltages meet existing specifications up to 85°C.

#### **Shock and Vibration**

The ruggedized (-D version) of the modules are designed to withstand elevated levels of shock and vibration to be able to operate in harsh environments. The ruggedized modules have been successfully tested to the following conditions:

#### Non operating random vibration:

Random vibration tests conducted at 25C, 10 to 2000Hz, for 30 minutes each level, starting from 30Grms (Z axis) and up to 50Grms (Z axis). The units were then subjected to two more tests of 50Grms at 30 minutes each for a total of 90 minutes.

#### Operating shock to 40G per Mil Std. 810F, Method 516.4 Procedure I:

The modules were tested in opposing directions along each of three orthogonal axes, with waveform and amplitude of the shock impulse characteristics as follows:

All shocks were half sine pulses, 11 milliseconds (ms) in duration in all 3 axes.

Units were tested to the Functional Shock Test of MIL-STD-810, Method 516.4, Procedure I - Figure 516.4-4. A shock magnitude of 40G was utilized. The operational units were subjected to three shocks in each direction along three axes for a total of eighteen shocks.

#### Operating vibration per Mil Std 810F, Method 514.5 Procedure I:

The ruggedized (-D version) modules are designed and tested to vibration levels as outlined in MIL-STD-810F, Method 514.5, and Procedure 1, using the Power Spectral Density (PSD) profiles as shown in Table 1 and Table 2 for all axes. Full compliance with performance specifications was required during the performance test. No damage was allowed to the module and full compliance to performance specifications was required when the endurance environment was removed. The module was tested per MIL-STD-810, Method 514.5, Procedure I, for functional (performance) and endurance random vibration using the performance and endurance levels shown in Table 1 and Table 2 for all axes. The performance test has been split, with one half accomplished before the endurance test and one half after the endurance test (in each axis). The duration of the performance test was at least 16 minutes total per axis and at least 120 minutes total per axis for the endurance test. The endurance test period was 2 hours minimum per axis.

Table 1: Performance Vibration Qualification - All Axes

| Table 1.1 offermation vibration Qualification. All Acco |                      |                   |                      |                   |                      |  |  |  |

|---------------------------------------------------------|----------------------|-------------------|----------------------|-------------------|----------------------|--|--|--|

| Frequency<br>(Hz)                                       | PSD Level<br>(G2/Hz) | Frequency<br>(Hz) | PSD Level<br>(G2/Hz) | Frequency<br>(Hz) | PSD Level<br>(G2/Hz) |  |  |  |

| 10                                                      | 1.14E-03             | 170               | 2.54E-03             | 690               | 1.03E-03             |  |  |  |

| 30                                                      | 5.96E-03             | 230               | 3.70E-03             | 800               | 7.29E-03             |  |  |  |

| 40                                                      | 9.53E-04             | 290               | 7.99E-04             | 890               | 1.00E-03             |  |  |  |

| 50                                                      | 2.08E-03             | 340               | 1.12E-02             | 1070              | 2.67E-03             |  |  |  |

| 90                                                      | 2.08E-03             | 370               | 1.12E-02             | 1240              | 1.08E-03             |  |  |  |

| 110                                                     | 7.05E-04             | 430               | 8.84E-04             | 1550              | 2.54E-03             |  |  |  |

| 130                                                     | 5.00E-03             | 490               | 1.54E-03             | 1780              | 2.88E-03             |  |  |  |

| 140                                                     | 8.20E-04             | 560               | 5.62E-04             | 2000              | 5.62E-04             |  |  |  |

**Table 2: Endurance Vibration Qualification - All Axes**

| Frequency<br>(Hz) | PSD Level<br>(G2/Hz) | Frequency<br>(Hz) | PSD Level<br>(G2/Hz) | Frequency<br>(Hz) | PSD Level<br>(G2/Hz) |

|-------------------|----------------------|-------------------|----------------------|-------------------|----------------------|

| 10                | 0.00803              | 170               | 0.01795              | 690               | 0.00727              |

| 30                | 0.04216              | 230               | 0.02616              | 800               | 0.05155              |

| 40                | 0.00674              | 290               | 0.00565              | 890               | 0.00709              |

| 50                | 0.01468              | 340               | 0.07901              | 1070              | 0.01887              |

| 90                | 0.01468              | 370               | 0.07901              | 1240              | 0.00764              |

| 110               | 0.00498              | 430               | 0.00625              | 1550              | 0.01795              |

| 130               | 0.03536              | 490               | 0.01086              | 1780              | 0.02035              |

| 140               | 0.0058               | 560               | 0.00398              | 2000              | 0.00398              |

## **Example Application Circuit**

#### **Requirements:**

Vin: 12V Vout: 1.8V

lout: 9.0A max., worst case load transient is from 6A to 9A  $\Delta$ Vout: 1.5% of Vout (27mV) for worst case load transient

Vin, ripple 1.5% of Vin (180mV, p-p)

CI1 22µF/16V ceramic capacitor (e.g. Murata GRM32ER61C226KE20)

CI2 100µF/16V bulk electrolytic

CO1 6 x 47μF/6.3V ceramic capacitor (e.g. Murata GRM31CR60J476ME19)

CO2 330μF/6.3V Polymer (e.g. Sanyo, Poscap)

CTune 15nF ceramic capacitor (can be 1206, 0805 or 0603 size)

RTune 150 ohms SMT resistor (can be 1206, 0805 or 0603 size)

RTrim 6.19k $\Omega$  SMT resistor (can be 1206, 0805 or 0603 size, recommended tolerance of 0.1%)

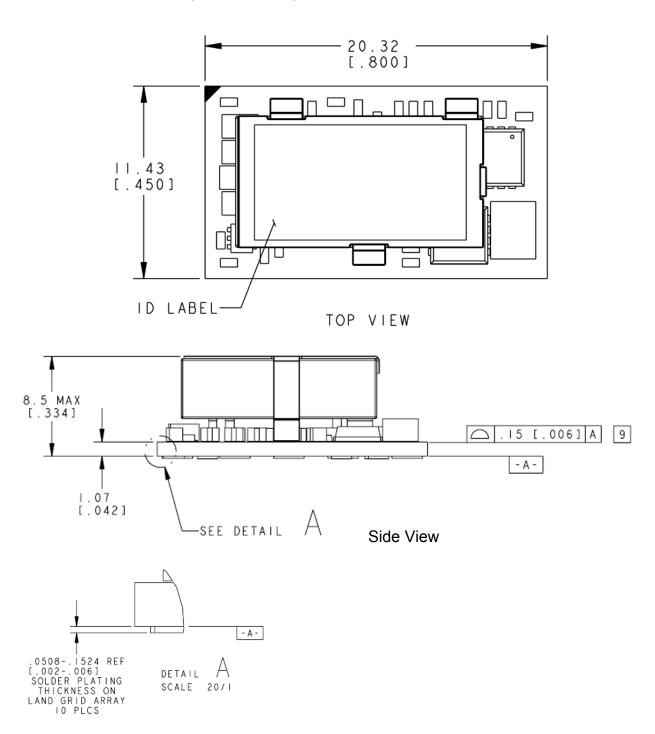

#### **Mechanical Outline**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated] x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

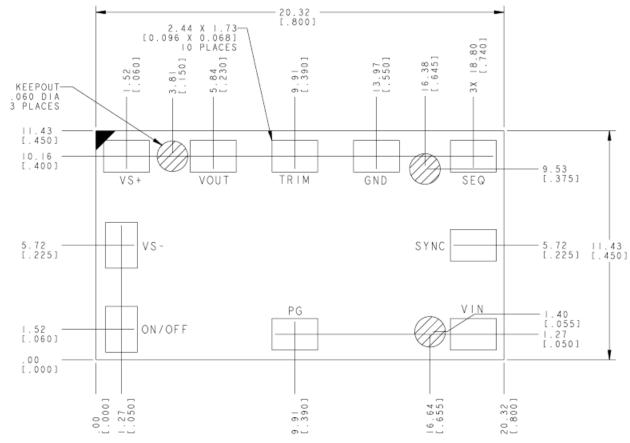

## **Recommended Pad Layout**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated] x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

RECOMMENDED FOOTPRINT -THROUGH THE BOARD-

| PIN | FUNCTION |  |  |  |

|-----|----------|--|--|--|

| 1   | ON/OFF   |  |  |  |

| 2   | VIN      |  |  |  |

| 3   | SEQ      |  |  |  |

| 4   | GND      |  |  |  |

| 5   | TRIM     |  |  |  |

| 6   | VOUT     |  |  |  |

| 7   | VS+      |  |  |  |

| 8   | VS-      |  |  |  |

| 9   | PG       |  |  |  |

| 10  | SYNC     |  |  |  |

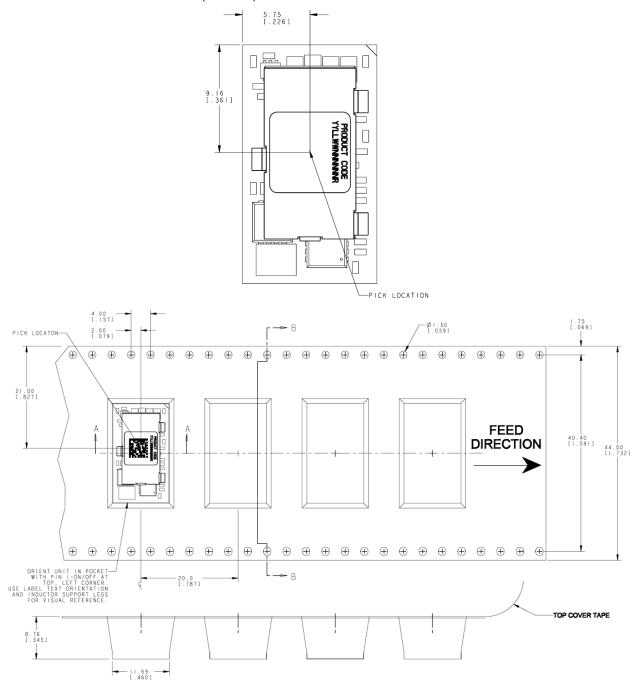

## **Packaging Details**

The 12V Micro TLynx<sup>TM</sup> modules are supplied in tape & reel as standard. Modules are shipped in quantities of 250 modules per reel.

All Dimensions are in millimeters and (in inches).

Reel Dimensions:

Outside Dimensions: 330.2 mm (13.00)

Inside Dimensions: 177.8 mm (7.00")

Tape Width: 44.00 mm (1.732")

# Surface Mount Information Pick and Place

The 12V Micro TLynx<sup>TM</sup> modules use an open frame construction and are designed for a fully automated assembly process. The modules are fitted with a label designed to provide a large surface area for pick and place operations. The label meets all the requirements for surface mount processing, as well as safety standards, and is able to withstand reflow temperatures of up to 300°C. The label also carries product information such as product code, serial number and the location of manufacture.

#### **Nozzle Recommendations**

The module weight has been kept to a minimum by using open frame construction. Variables such as nozzle size, tip style, vacuum pressure and placement speed should be considered to optimize this process. The minimum recommended inside nozzle diameter for reliable operation is 3mm. The maximum nozzle outer diameter, which will safely fit within the allowable component spacing, is 7 mm.

#### **Lead Free Soldering**

The 12V Micro TLynx<sup>TM</sup> modules are lead-free (Pb-free) and RoHS compliant and fully compatible in a Pb-free soldering process. Failure to observe the instructions below may result in the failure of or cause damage to the modules and can adversely affect long-term reliability.

#### **Pb-free Reflow Profile**

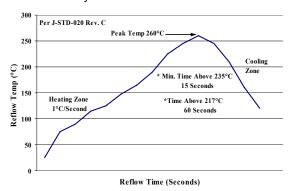

Power Systems will comply with J-STD-020 Rev. C (Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices) for both Pb-free solder profiles and MSL classification procedures. This standard provides a recommended forced-air-convection reflow profile based on the volume and thickness of the package (table 4-2). The suggested Pb-free solder paste is Sn/Ag/Cu (SAC). The recommended linear reflow profile using Sn/Ag/Cu solder is shown in Fig. 51. Soldering outside of the recommended profile requires testing to verify results and performance.

#### **MSL** Rating

The 12V Micro TLynx $^{\text{TM}}$  modules have a MSL rating of 2.

#### **Storage and Handling**

The recommended storage environment and handling procedures for moisture-sensitive surface mount packages is detailed in J-STD-033 Rev. A (Handling, Packing, Shipping and Use of Moisture/Reflow

Sensitive Surface Mount Devices). Moisture barrier bags (MBB) with desiccant are required for MSL ratings of 2 or greater. These sealed packages should not be broken until time of use. Once the original package is broken, the floor life of the product at conditions of  $\leq 30^{\circ}\text{C}$  and 60% relative humidity varies according to the MSL rating (see J-STD-033A). The shelf life for dry packed SMT packages will be a minimum of 12 months from the bag seal date, when stored at the following conditions:  $< 40^{\circ}\text{ C}, < 90\%$  relative humidity.

Figure 51. Recommended linear reflow profile using Sn/Ag/Cu solder.

# Post Solder Cleaning and Drying Considerations

Post solder cleaning is usually the final circuit-board assembly process prior to electrical board testing. The result of inadequate cleaning and drying can affect both the reliability of a power module and the testability of the finished circuit-board assembly. For guidance on appropriate soldering, cleaning and drying procedures, refer to *Board Mounted Power Modules: Soldering and Cleaning* Application Note (AN04-001).

## **Ordering Information**

Please contact your Lineage Power Sales Representative for pricing, availability and optional features.

**Table 4. Device Codes**

| Device Code        | Input<br>Voltage Range | Output<br>Voltage | Output<br>Current | On/Off<br>Logic | Connector<br>Type | Comcodes    |

|--------------------|------------------------|-------------------|-------------------|-----------------|-------------------|-------------|

| APTS012A0X3-SRZ    | 4.5 – 14Vdc            | 0.69 – 5.5Vdc     | 12A               | Negative        | SMT               | CC109126042 |

| APTS012A0X43-SRZ   | 4.5 – 14Vdc            | 0.69 – 5.5Vdc     | 12A               | Positive        | SMT               | CC109126050 |

| APTS012A0X3-25SRZ* | 4.5 – 14Vdc            | 0.69 – 5.5Vdc     | 12A               | Negative        | SMT               | CC109142171 |

| APTS012A0X3-SRDZ   | 4.5 – 14Vdc            | 0.69 – 5.5Vdc     | 12A               | Negative        | SMT               | CC109150224 |

#### \* Special codes, consult factory before ordering

Table 5. Coding Scheme

| TLynx family | Sequencing feature.        | Input<br>voltage<br>range | Output<br>current | Output<br>voltage       | On/Off<br>logic                     | Options                                  |                                                                                    | ROHS<br>Compliance |

|--------------|----------------------------|---------------------------|-------------------|-------------------------|-------------------------------------|------------------------------------------|------------------------------------------------------------------------------------|--------------------|

| AP           | T                          | S                         | 012A0             | X                       | 4                                   | -SR                                      | -D                                                                                 | Z                  |

|              | T = with Seq. X = w/o Seq. | S = 4.5 -<br>14V          | 12.0A             | X = programmable output | 4 = positive<br>No entry = negative | S = Surface<br>Mount<br>R =<br>Tape&Reel | D = 105C<br>operating<br>ambient, 40G<br>operating<br>shock as per<br>MIL Std 810F | Z = ROHS6          |

World Wide Headquarters

Lineage Power Corporation

3000 Skyline Drive, Mesquite, TX 75149, USA

+1-800-526-7819

(Outside U.S.A.: +1-972-284-2626)

www.lineagepower.com

e-mail: techsupport1@lineagepower.com

Asia-Pacific Headquarters Tel: +65 6416 4283

**Europe, Middle-East and Africa Headquarters** Tel: +49 898 780 672 80

India Headquarters Tel: +91 80 28411633

Lineage Power reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

© 2008 Lineage Power Corporation, (Mesquite, Texas) All International Rights Reserved.

LINEAGE POWER 26

Document No: DS06-137 ver. 1.15 PDF name: APTS012A0X\_DS.pdf