# TMC1103 Triple Video A/D Converter with Clamps 8-Bit, 50Msps

#### Features

- 8-bit resolution

- 50 Msps conversion rate

- Low power: 100mW per channel @ 20 Msps

- Integral track/hold

- Independent Input Clamps

- Independent clock inputs

- Integral and differential linearity error 0.5 LSB

- Differential phase 0.7 degree

- Differential gain 1.8%

- Single +5V power supply

- Three-state TTL/CMOS-compatible outputs

- Low cost

## Description

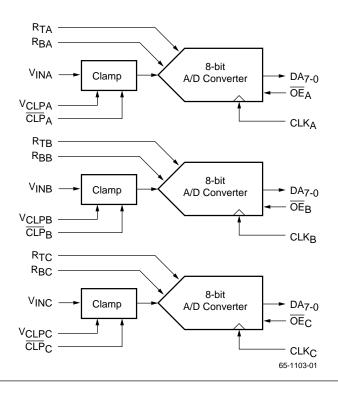

Incorporated into the TMC1103 are three analog-to-digital (A/D) converters, each with an independent clock, reference voltage and input clamp. Analog signals are converted to Triple 8-bit digital words at sample rates up to 50 Msps (Megasamples per second) per channel.

Integral Track/Hold circuits deliver excellent performance on signals with full-scale spectral components up to 12 MHz. Innovative two-step conversion architecture and

#### **Applications**

- Video digitizing (composite and Y-C)

- VGA and CCD digitizing

- LCD projection panels

- Image scanners

- Personal computer video boards

- Multimedia systems

- Low cost, high speed data conversion

submicron CMOS technology reduce typical power dissipation to 100 mW per converter.

Power is derived from a single +5 Volt power supply. Outputs are three-state outputs and TTL/CMOS-compatible.

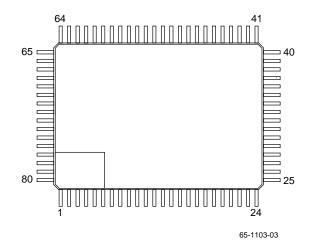

TMC1103 package is a 80-lead Metric Quad Flat Pack (MQFP). Performance specifications are guaranteed from 0°C to 70°C.

### **Block Diagram**

## **Circuit Function**

Within the TMC1103 are three 8-bit A/D converters, each employing two-step architecture to convert an analog input to a digital output at rates up to 50 Msps. Input signals are held in integral track/hold stages during the conversion process. Operation is pipelined, with one input sample taken and one output word provided for each CLKx cycle.

Each of the three converters function identically. In the following descriptions 'X' refers to a generic input/output or clock where 'X' is equivalent to A, B or C.

The first step in the conversion process is a coarse 4-bit quantization. This determines the range of the subsequent fine 4-bit quantization step. To eliminate spurious codes, the fine 4-bit A/D quantizer output is gray-coded and converted to binary before it is combined with the coarse result to form a complete 8-bit result.

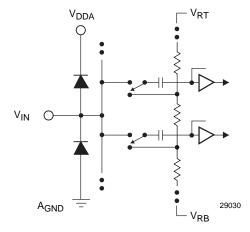

#### **Analog Input and Voltage References**

Each A/D accepts analog signals in the range  $R_{BX}$  to  $R_{TX}$  into digital data. Input signals outside this range produce "saturated" 00h or FFh output codes. The device will not be damaged by signals within the range AGND to VDDA.

Input range is very flexible and extends from the +5 Volt power supply to ground. Nominal input range is 2 Volts, extending from 0.6V to 2.6V. Characterization and performance is specified over this range. However, the part will function with a full-scale range from 1.0V to 5.0V. A smaller input range may simplify analog signal conditioning circuitry, at the expense of additional noise sensitivity and some reduced differential linearity performance.

External voltage reference sources are connected to the  $R_{TX}$  and  $R_{BX}$  pins.  $R_{BX}$  can be grounded. Within each A/D converter is a reference resistor ladder comprising 255 resistors that are accessed by the TMC1103 comparators.  $R_{TX}$  is connected to the top of the ladder,  $R_{BX}$  to the bottom. Gain and offset errors are directly related to the accuracy and stability of the applied reference voltages.

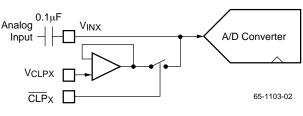

#### **Input Clamps**

A clamp circuit is connected to the input pin V<sub>INX</sub> of each of the three A/D converters. With  $\overline{\text{CLP}_X}$  LOW, the input pin is clamped to the voltage at V<sub>CLPX</sub>. If  $\overline{\text{CLP}_X}$  is HIGH, the input pin is high impedance. Clamping adds an offset voltage to an AC coupled signal to adjust this signal's amplitude to the A/D converter input voltage range.

The analog input is corrected through a  $0.1\mu$ F capacitor to V<sub>INX</sub>. The source impedance of the analog source should be less than 50 Ohms. Current pulses through the capacitor over several clamp cycles until the voltage across the capacitor equals the difference between V<sub>CLPX</sub> and the voltage at the analog source during the clamping period. When the switch is open, the voltage on the coupling capacitor is added to the analog input, producing a a DC offset input signal.

Input Clamp Circuit

#### **Digital Inputs and Outputs**

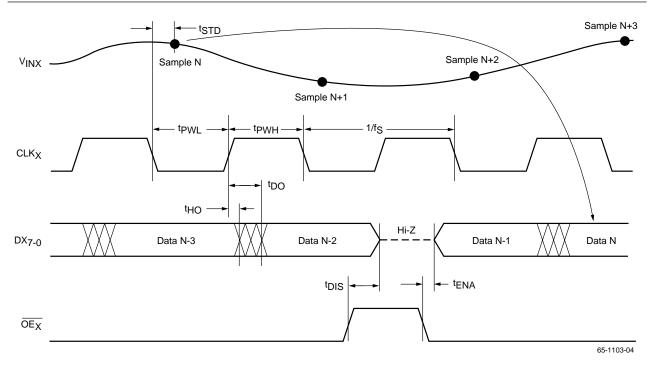

Sampling of the applied input signal occurs on the falling edge of the CLK<sub>X</sub> signal (Figure 1). Output data is delayed by 2 1/2 CLK<sub>X</sub> cycles and is valid following the rising edge of CLK<sub>X</sub>. Previous output data remains valid for t<sub>HO</sub> (Output Hold Time). New data becomes valid t<sub>D</sub> (Output Delay Time) after this rising edge of CLK<sub>X</sub>.

Whenever the analog input signal is sampled and found to be at a level beyond the A/D conversion range, the output limits at 00h or FFh, as appropriate.

| Input Voltage             | Output |

|---------------------------|--------|

| RTX + 1 LSB               | FF     |

| RTX                       | FF     |

| RTX - 1 LSB               | FE     |

| •••                       | • • •  |

| R <sub>BX</sub> + 128 LSB | 80     |

| R <sub>BX</sub> + 127 LSB | 7F     |

| •••                       | • • •  |

| R <sub>BX</sub> + 1 LSB   | 01     |

| R <sub>BX</sub>           | 00     |

| R <sub>BX</sub> - 1 LSB   | 00     |

#### Table 1. A/D Output Coding

Note: 1 LSB = (RTX - RBX) / 255

The outputs of the TMC1103 are CMOS- and TTL-compatible, and are capable of driving four low-power Schottky TTL loads. An Output Enable control,  $\overline{OE}_X$ , places the A/D outputs in a high-impedance state when HIGH. The outputs are enabled when  $\overline{OE}_X$  is LOW.

#### **Power and Ground**

The TMC1103 operates from a single +5 Volt power supply. For optimum performance, an analog ground plane should be placed under the TMC1103 the A<sub>GND</sub> and D<sub>GND</sub> pins should be connected to the system analog ground plane.

## **Pin Assignments**

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | NC              | 21  | DGND            | 41  | DC7             | 61  | Vdd             |

| 2   | DA <sub>5</sub> | 22  | DGND            | 42  | OEC             | 62  | OEB             |

| 3   | DA <sub>6</sub> | 23  | NC              | 43  | V <sub>DD</sub> | 63  | DB7             |

| 4   | DA <sub>7</sub> | 24  | NC              | 44  | V <sub>DD</sub> | 64  | DB <sub>6</sub> |

| 5   | OEA             | 25  | DGND            | 45  | CLKC            | 65  | DB5             |

| 6   | VDD             | 26  | DGND            | 46  | NC              | 66  | DB4             |

| 7   | VDD             | 27  | VDD             | 47  | Vdda            | 67  | DB <sub>3</sub> |

| 8   | NC              | 28  | CLPA            | 48  | VINC            | 68  | DB <sub>2</sub> |

| 9   | CLKA            | 29  | CLPB            | 49  | AGND            | 69  | DB <sub>1</sub> |

| 10  | NC              | 30  | CLPC            | 50  | RTC             | 70  | DB <sub>0</sub> |

| 11  | Vdda            | 31  | NC              | 51  | RBC             | 71  | DGND            |

| 12  | VINA            | 32  | DGND            | 52  | R <sub>BB</sub> | 72  | DGND            |

| 13  | AGND            | 33  | DGND            | 53  | R <sub>TB</sub> | 73  | NC              |

| 14  | R <sub>TA</sub> | 34  | DC <sub>0</sub> | 54  | AGND            | 74  | DGND            |

| 15  | R <sub>BA</sub> | 35  | DC <sub>1</sub> | 55  | VINB            | 75  | DGND            |

| 16  | VCLPA           | 36  | DC <sub>2</sub> | 56  | Vdda            | 76  | DA <sub>0</sub> |

| 17  | VCLPB           | 37  | DC <sub>3</sub> | 57  | NC              | 77  | DA1             |

| 18  | VCLPC           | 38  | DC4             | 58  | CLKB            | 78  | DA <sub>2</sub> |

| 19  | DGND            | 39  | DC <sub>5</sub> | 59  | NC              | 79  | DA <sub>3</sub> |

| 20  | DGND            | 40  | DC <sub>6</sub> | 60  | V <sub>DD</sub> | 80  | DA <sub>4</sub> |

## **Pin Descriptions**

| Pin Name               | Pin Number                                                          | Value                                 | Pin Function Description                                                                                                                              |

|------------------------|---------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D Converters         | •                                                                   |                                       |                                                                                                                                                       |

| Vina, Vinb,<br>Vinc    | 12, 55, 48                                                          | RTX to<br>RBX                         | <b>Analog Inputs.</b> The input voltage conversion range lies between the voltage applied to the RTX and RBX pins.                                    |

| RTA, RTB, RTC          | 14, 53, 50                                                          | 2.6V                                  | <b>Reference Voltage, Top Inputs.</b> DC voltages applied to $R_{TA}$ , $R_{TB}$ and $R_{TC}$ define highest value of $V_{INX}$ .                     |

| RBA, RBB, RBC          | 15, 52, 51                                                          | 0.6V                                  | Reference Voltage, Bottom Inputs. DC voltages applied to R <sub>BA</sub> , R <sub>BB</sub> and R <sub>BC</sub> define lowest value of $V_{INX}$ .     |

| CLKA, CLKB,<br>CLKC    | 9, 58, 45                                                           | CMOS                                  | <b>Clock Inputs.</b> CMOS-compatible. VINX is sampled on the falling edge of CLKX.                                                                    |

| DA <sub>7-0</sub>      | 4, 3, 2, 80, 79,<br>78, 77, 76                                      | CMOS/<br>TTL                          | <b>Data outputs, Converter A (D7 = MSB).</b> Eight-bit CMOS- and TTL-compatible digital outputs. Valid data is output on the rising edge of CLKx.     |

| DB7-0                  | 63, 64, 65, 66,<br>67, 68, 69, 70                                   | CMOS/<br>TTL                          | <b>Data outputs, Converter B (D7 = MSB).</b> Eight-bit CMOS- and TTL-compatible digital outputs. Valid data is output on the rising edge of $CLK_X$ . |

| DC7-0                  | 41, 40, 39, 38,<br>37, 36, 35, 34                                   | CMOS/<br>TTL                          | <b>Data outputs, Converter C (D7 = MSB).</b> Eight-bit CMOS- and TTL-compatible digital outputs. Valid data is output on the rising edge of $CLK_X$ . |

| OEA, OEB, OEC          | 5, 62, 42                                                           | CMOS                                  | <b>Output Enable Inputs.</b> CMOS-compatible. When LOW, the A/D output is enabled. When HIGH, the output is in a high-impedance state.                |

| Clamps                 | •                                                                   |                                       |                                                                                                                                                       |

| VCLPA, VCLPB,<br>VCLPB | 16, 17, 18                                                          | R <sub>TX</sub> to<br>R <sub>BX</sub> | Clamp Reference Voltage. One reference for each clamp. A V <sub>INX</sub> input is clamped to $V_{CLPX}$ when $\overline{CLP}_X$ is low.              |

| CLPA, CLPB,<br>CLPC    | 28, 29, 30                                                          | CMOS                                  | <b>Clamp Pulse Inputs.</b> One input for each A/D clamp. When $\overline{\text{CLP}}_X$ is low, the VINX input is clamped to the VCLPX clamp voltage. |

| Power                  |                                                                     |                                       |                                                                                                                                                       |

| VDDA                   | 11, 47, 56                                                          | +5V                                   | <b>Analog Supply Voltage.</b> +5 Volt power inputs. These should come from the same power source and be decoupled to AGND.                            |

| VDD                    | 6, 7, 27, 28, 29,<br>30, 43, 44, 60,<br>61                          | +5V                                   | <b>Digital Supply Voltage.</b> +5 Volt power inputs. These should come from the same power source and be decoupled to AGND.                           |

| Agnd                   | 13, 49, 54                                                          | 0.0V                                  | <b>Analog Ground.</b> Ground connections. These pins should be connected to the system analog ground plane.                                           |

| D <sub>GND</sub>       | 16, 17, 18, 19,<br>20, 21, 22, 25,<br>26, 32, 33, 71,<br>72, 74, 75 | 0.0V                                  | <b>Digital Ground.</b> Ground connections. These pins should be connected to the system analog ground plane.                                          |

| No Connect             |                                                                     |                                       |                                                                                                                                                       |

| N/C                    | 1, 8, 10, 23, 24,<br>31, 46, 57, 59,<br>73                          | open                                  | Not Connected.                                                                                                                                        |

Figure 1. Timing

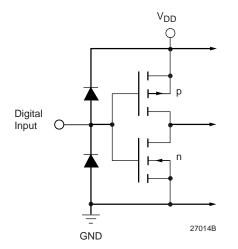

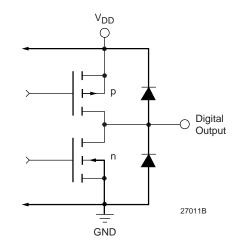

## **Equivalent Circuits and Threshold Levels**

Figure 2. Equivalent Digital Input Circuit

Figure 3. Equivalent Digital Output Circuit

#### Equivalent Circuits and Threshold Levels (continued)

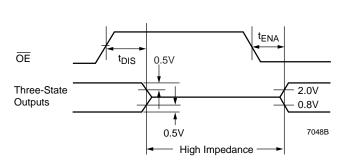

Figure 5. Threshold Levels for Three-State Measurements

| Parameter               | Condition                              | Min   | Тур | Max                   | Unit |

|-------------------------|----------------------------------------|-------|-----|-----------------------|------|

| Power Supply Voltages   |                                        |       |     |                       |      |

| VDDA                    | Measured to AGND                       | -0.5  |     | +7.0                  | V    |

| VDD                     | Measured to DGND                       | -0.5  |     | +7.0                  | V    |

| VDDA                    | Measured to V <sub>DD</sub>            | -0.5  |     | +0.5                  | V    |

| AGND                    | Measured to DGND                       | -0.5  |     | +0.5                  | V    |

| Digital Inputs          |                                        |       |     | •                     |      |

| Applied Voltage         | Measured to DGND                       | -0.5  |     | VDD + 0.5             | V    |

| Forced current          |                                        | -10.0 |     | +10.0                 | mA   |

| Analog Inputs           |                                        |       |     |                       |      |

| Applied Voltage         | Measured to AGND                       | -0.5  |     | VDDA+0.5              | V    |

| Forced current          |                                        | -10.0 |     | +10.0                 | mA   |

| Digital Outputs         |                                        |       |     |                       |      |

| Applied voltage         | Measured to D <sub>GND</sub>           | -0.5  |     | V <sub>DD</sub> + 0.5 | V    |

| Forced current          |                                        | -6.0  |     | +6.0                  | mA   |

| Short circuit duration  | Single output in HIGH state to ground) |       |     | 1 second              |      |

| Temperature             |                                        |       |     |                       |      |

| Operating, ambient      |                                        | -20   |     | 110                   | °C   |

| Junction                |                                        |       |     | +150                  | °C   |

| Lead, soldering         | 10 seconds                             |       |     | +300                  | °C   |

| Vapor Phase soldering   | 1 minute                               |       |     | +220                  | °C   |

| Storage                 |                                        | -65   |     | +150                  | °C   |

| Electrostatic Discharge | EIAJ test method                       |       |     | ±150                  | V    |

| Absolute Maximum Ratings | (beyond which the device may be damaged) <sup>1</sup> |

|--------------------------|-------------------------------------------------------|

|--------------------------|-------------------------------------------------------|

#### Notes:

1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

| Parameter |                                         |         | Nom | Max.                | Units |

|-----------|-----------------------------------------|---------|-----|---------------------|-------|

| Vdd, Vdda | Power Supply Voltage                    | 4.75    | 5.0 | 5.25                | V     |

| Agnd      | Analog Ground (Measured to DGND)        | -0.1    | 0   | 0.1                 | V     |

| VRTX      | Reference Voltage, Top                  |         | 2.6 | Vdda                | V     |

| Vrbx      | Reference Voltage, Bottom               | 0       | 0.6 |                     | V     |

| VRTX-VRBX | Reference Voltage Differential          | 1.0     | 2.0 | 5.0                 | V     |

| VINX      | Analog Input Range                      | Vrb     |     | Vrt                 | V     |

| VCLPX     | Clamp Reference Voltage, 50Ω max source | 0       |     |                     | V     |

| VIH       | Input Voltage, Logic HIGH               | 0.7 VDD |     | Vdd                 | V     |

| VIL       | Input Voltage, Logic LOW                | GND     |     | 0.3 V <sub>DD</sub> | V     |

| ЮН        | Output Current, Logic HIGH              |         |     | -4.0                | mA    |

| IOL       | Output Current, Logic LOW               |         |     | 4.0                 | mA    |

| TA        | Ambient Temperature, Still Air          | 0       |     | 70                  | °C    |

## **Operating Conditions**

## **Electrical Characteristics**

| Parameter |                                             | Conditions                                                | Min. | Typ <sup>1</sup> | Max. | Units |

|-----------|---------------------------------------------|-----------------------------------------------------------|------|------------------|------|-------|

| IDD       | Power Supply Current <sup>1</sup>           | $C_{LOAD} = 35 pF$ , fCK = fS (3 A/Ds)                    |      |                  |      |       |

|           |                                             | f <sub>S</sub> = 20 Msps                                  |      | 70               | 90   | mA    |

|           |                                             | fs = 40 Msps                                              |      | 94               | 120  | mA    |

|           |                                             | f <sub>S</sub> = 50 Msps                                  |      | 105              | 135  | mA    |

| IDDQ      | Power Supply Current,<br>Quiescent          | VDD = VDDA = Max.                                         |      |                  |      |       |

|           |                                             | $CLK_X = LOW$                                             |      | 29               | 55   | mA    |

|           |                                             | CLK <sub>X</sub> = HIGH                                   |      | 45               | 65   | mA    |

| PD        | Total Power Dissipation <sup>1</sup>        | $C_{LOAD} = 35 pF$ , $f_{CK} = f_S (3 A/Ds)$              |      |                  |      |       |

|           |                                             | f <sub>S</sub> = 20 Msps                                  |      | 300              | 470  | mW    |

|           |                                             | fs = 40 Msps                                              |      | 425              | 630  | mW    |

|           |                                             | fs = 50 Msps                                              |      | 490              | 710  | mW    |

| CAI       | Input Capacitance, Analog                   | CLKX = LOW                                                |      | 4                |      | pF    |

|           |                                             | $CLK_X = HIGH$                                            |      | 12               |      | pF    |

| Rin       | Input Resistance                            |                                                           | 500  |                  |      | kΩ    |

| RREF      | Reference Resistance                        |                                                           | 200  | 270              | 340  | Ω     |

| ICB       | Input Current, Analog                       |                                                           |      |                  | ±5   | μA    |

| IIН       | Input Current, HIGH                         | V <sub>DD</sub> = Max., V <sub>IN</sub> = V <sub>DD</sub> |      |                  | ±5   | μΑ    |

| ١L        | Input Current, LOW                          | VDD = Max., VIN = 0V                                      |      |                  | ±5   | μA    |

| Iozh      | Hi-Z Output Leakage Current,<br>Output HIGH | V <sub>DD</sub> = Max., V <sub>IN</sub> = V <sub>DD</sub> |      |                  | ±5   | μΑ    |

| Iozl      | Hi-Z Output Leakage Current,<br>Output LOW  | V <sub>DD</sub> = Max., V <sub>IN</sub> = V <sub>DD</sub> |      |                  | ±5   | μA    |

| los       | Short-Circuit Current                       |                                                           |      |                  | 35   | mA    |

#### Electrical Characteristics (continued)

| Parameter |                            | Conditions               | Min. | Typ <sup>1</sup> | Max. | Units |

|-----------|----------------------------|--------------------------|------|------------------|------|-------|

| Vон       | Output Voltage, HIGH       | I <sub>OH</sub> = -2.5mA | 3.5  |                  |      | V     |

|           |                            | IOH = Max.               | 2.4  |                  |      | V     |

| Vol       | Output Voltage, LOW        | I <sub>OL</sub> = Max.   |      |                  | 0.4  | V     |

| CDI       | Digital Input Capacitance  |                          |      | 4                | 10   | pF    |

| CDO       | Digital Output Capacitance |                          |      | 10               |      | pF    |

Note:

1. Typical values with  $V_{DD} = V_{DDA} = Nom$  and  $T_A = Nom$ , Maximum values with  $V_{DD} = V_{DDA} = Max$ . and  $T_A = Min$ .

## **Switching Characteristics**

| Parame | eter                           | Conditions       | Min. | Тур. | Max. | Units |

|--------|--------------------------------|------------------|------|------|------|-------|

| fS     | Conversion Rate                |                  |      |      |      |       |

|        | TMC1103-20                     |                  |      |      | 20   | Msps  |

|        | TMC1103-40                     |                  |      |      | 40   | Msps  |

|        | TMC1103-50                     |                  |      |      | 50   | Msps  |

| tPWH   | CLKX Pulsewidth, HIGH          |                  |      |      |      |       |

|        | TMC1103-20                     |                  | 14   |      |      | ns    |

|        | TMC1103-40                     |                  | 14   |      |      | ns    |

|        | TMC1103-50                     |                  | 13   |      |      | ns    |

| tpwL   | CLKX Pulsewidth, LOW           |                  |      |      |      |       |

|        | TMC1103-20                     |                  | 8    |      |      | ns    |

|        | TMC1103-40                     |                  | 8    |      |      | ns    |

|        | TMC1103-50                     |                  | 7    |      |      | ns    |

| EAP    | Aperture Error                 |                  |      | 30   |      | ps    |

| tSTO   | Sampling Time Offset           |                  | 1    | 2    | 5    | ns    |

| tsts   | Sampling Time Skew             |                  |      | 150  | 400  | ps    |

| tCPW   | Clamp Pulse Width <sup>1</sup> | +20 < TA < +70°C | 2    |      |      | μS    |

| tCDLY  | Clamp Delay Time               |                  | 100  |      | 300  | ns    |

| tHO    | Output Hold Time               | CLOAD = 15pF     | 9    |      |      | ns    |

| tDO    | Output Delay Time              |                  |      |      | 14   | ns    |

| tENA   | Output Enable Time             |                  |      |      | 27   | ns    |

| tDIS   | Output Disable Time            |                  |      |      | 42   | ns    |

## System Performance Characteristics

| Parameter |                                                                               | Conditions                                                                                                                                | Min.       | Тур. | Max. | Units |  |

|-----------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|-------|--|

| ELI       | Integral Linearity Error,<br>Independent                                      | V <sub>RT</sub> = 2.6V                                                                                                                    |            | ±0.5 |      | LSB   |  |

| Eld       | Differential Linearity Error                                                  | VRB = 0.6V                                                                                                                                |            | ±0.5 |      | LSB   |  |

| BW        | Bandwidth <sup>1</sup>                                                        | TMC1203-20                                                                                                                                |            |      | 10   | MHz   |  |

|           |                                                                               | TMC1203-40                                                                                                                                |            |      | 12   | MHz   |  |

|           |                                                                               | TMC1203-50                                                                                                                                |            |      | 12   | MHz   |  |

| Еот       | Offset Voltage, Top<br>( $R_T - V_{IN}$ for most positive<br>code transition) | VRT = 2.6V, VRB = 0.6V                                                                                                                    | -40        |      | 80   | mV    |  |

| Еов       | Offset Voltage, Bottom<br>(RB – VIN for most negative<br>code transition)     | VRT = 2.6V, VRB = 0.6V                                                                                                                    | -95        |      | -30  | mV    |  |

| OFFCL     | Offset Voltage, Clamp                                                         |                                                                                                                                           |            |      | ±20  | mV    |  |

| dg        | Differential Gain                                                             |                                                                                                                                           |            | 1.8  |      | %     |  |

| dp        | Differential Phase                                                            | fs = 14.3Msps<br>NTSC 40 IRE Mod Ramp<br>V <sub>DDA</sub> = +5.0V, T <sub>A</sub> =25°C<br>V <sub>RT</sub> = 2.6V, V <sub>RB</sub> = 0.6V |            | 0.7  |      | deg   |  |

| XTALK     | Channel Crosstalk                                                             | f <sub>N</sub> = 5.0 MHz                                                                                                                  |            | 45   |      | dB    |  |

| SNR       | Signal-to-Noise Ratio                                                         | f <sub>S</sub> = 20Msps, V <sub>RT</sub> = 2.6V, V <sub>RB</sub> = 0.6V                                                                   |            |      |      |       |  |

|           |                                                                               | f <sub>N</sub> = 1.24MHz                                                                                                                  |            | 46   |      | dB    |  |

|           |                                                                               | f <sub>N</sub> = 2.48MHz                                                                                                                  |            | 46   |      | dB    |  |

|           |                                                                               | f <sub>N</sub> = 6.98MHz                                                                                                                  |            | 45   |      | dB    |  |

|           |                                                                               | f <sub>N</sub> = 10.0MHz                                                                                                                  |            | 45   |      | dB    |  |

|           |                                                                               | fs = 40Msps, V <sub>RT</sub> = 2.6V, V                                                                                                    | 'RB = 0.6V | ,    |      |       |  |

|           |                                                                               | $f_N = 1.24 MHz$                                                                                                                          |            | 42   |      | dB    |  |

|           |                                                                               | $f_N = 6.98MHz$                                                                                                                           |            | 41   |      | dB    |  |

|           |                                                                               | $f_N = 12.0MHz$                                                                                                                           |            | 40   |      | dB    |  |

|           |                                                                               | $f_S = 50Msps, V_{RT} = 2.6V, V$                                                                                                          | RB = 0.6V  |      |      |       |  |

|           |                                                                               | f <sub>N</sub> = 1.24MHz                                                                                                                  |            | 40   |      | dB    |  |

|           |                                                                               | f <sub>N</sub> = 6.98MHz                                                                                                                  |            | 40   |      | dB    |  |

|           |                                                                               | f <sub>N</sub> = 12.0MHz                                                                                                                  |            | 40   |      | dB    |  |

| Parameter |                             | Conditions               | Min. | Тур. | Max. | Units |

|-----------|-----------------------------|--------------------------|------|------|------|-------|

| SFDR      | Spurious-Free Dynamic Range | fs = 20Msps, VIN = 2V p- | р    |      | •    |       |

|           |                             | f <sub>N</sub> = 1.24MHz |      | 53   |      | dB    |

|           |                             | f <sub>N</sub> = 2.48MHz |      | 48   |      | dB    |

|           |                             | f <sub>N</sub> = 6.98MHz |      | 44   |      | dB    |

|           |                             | f <sub>N</sub> = 10.0MHz |      | 40   |      | dB    |

|           |                             | fs = 40Msps, VIN = 2V p- | р    |      | •    |       |

|           |                             | f <sub>N</sub> = 1.24MHz |      | 49   |      | dB    |

|           |                             | f <sub>N</sub> = 6.98MHz |      | 44   |      | dB    |

|           |                             | f <sub>N</sub> = 12.0MHz |      | 38   |      | dB    |

|           |                             | fs = 50Msps, VIN = 2V p- | р    |      | •    |       |

|           |                             | f <sub>N</sub> = 1.24MHz |      | 46   |      | dB    |

|           |                             | f <sub>N</sub> = 6.98MHz |      | 40   |      | dB    |

|           |                             | f <sub>N</sub> = 12.0MHz |      | 37   |      | dB    |

#### System Performance Characteristics (continued)

Notes:

1. Bandwidth is the frequency up to which a full-scale sinewave can be digitized without spurious codes.

2. Values shown in Typ. column are typical for V\_DD = V\_DDA = +5V and TA = 25°C.

3. SNR values do not include the harmonics of the fundamental frequency.

4. SFDR is the ratio in dB of fundamental amplitude to the harmonic with the highest amplitude.

5. Characteristics specified for  $V_{RT} = 2.6V$ ,  $V_{RB} = 0.6V$ .

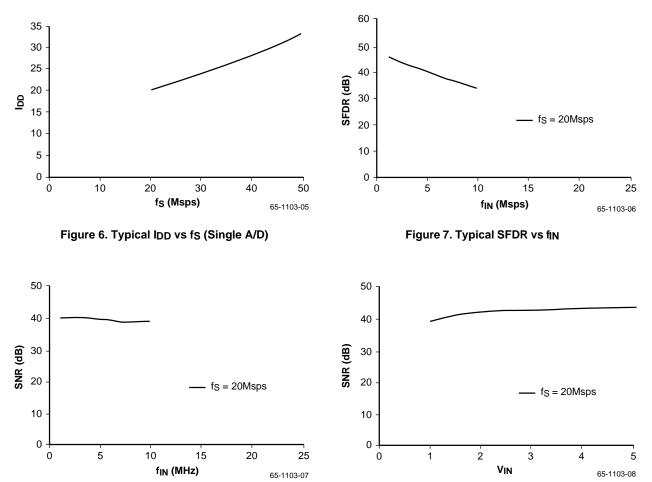

## **Typical Performance Characteristics**

Figure 8. Typical SNR vs fIN

Figure 9. Typical SNR vs Full Scale Input Range

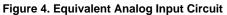

### **Application Notes**

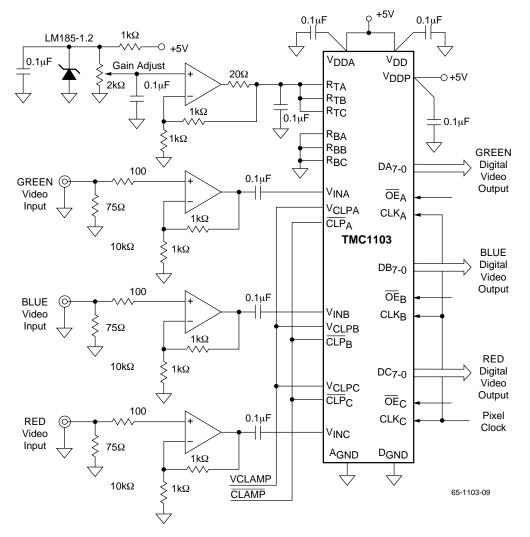

The circuit in Figure 10 employs a band-gap reference to generate a variable R<sub>TX</sub> reference voltages for the TMC1103 as well as a bias voltage to offset the wideband input amplifiers to mid-range. The operational amplifier in the reference circuitry is a standard 741-type.

The voltage reference at  $R_{TX}$  can be adjusted from 0.0 to 2.4 volts while  $R_{BX}$  is grounded. Schottky diodes can be used at  $V_{INX}$  to restrict the wideband amplifier output to between -0.3V and  $V_{DD}$  +0.3V. Diode protection is good practice to limit the analog input voltage at  $V_{INX}$  to the safe operating range.

Figure 10. Typical Interface Circuit – High Performance

#### Grounding

The TMC1103 has separate analog and digital circuits. To keep digital system noise from the A/D converter, it is recommended that power supply voltages (V<sub>DD</sub> and V<sub>DDA</sub>) come from the same source, and that ground connections (D<sub>GND</sub> and A<sub>GND</sub>) be made to the analog ground plane, and as close as possible to the device pins. Power supply pins should be individually decoupled at the pin. The digital circuitry that gets its input from the TMC1103 should be referred to the system digital ground plane.

#### **Printed Circuit Board Layout**

Designing with high performance mixed-signal circuits demands printed circuits with ground planes. Overall system performance is strongly influenced by the board layout. Capacitive coupling from digital to analog circuits may result in poor A/D conversion. Consider the following suggestions when doing the layout:

Keep the critical analog traces (V<sub>N</sub>, R<sub>TX</sub>, R<sub>BX</sub>) as short as possible and as far as possible from all digital signals. The TMC1103 should be located close to the analog input connectors.

- 2. Segregate traces:

- A/D analog

- D/A analog

- Clocks

- Digital

Treat analog inputs as transmission lines. Cleanly route traces over the ground plane bearing in mind that the return currents will flow through the ground plane beneath the traces. Do not route digital traces nearby. A few inches of digital trace less than a few line widths from an analog trace will cross-couple noise into adjacent analog circuits.

- 3. The power plane for the TMC1103 should be separate from that which supplies the rest of the digital circuitry. A single power plane should be used for all of the  $V_{DD}$  pins. If the power supply for the TMC1103 is the same as that of the system's digital circuitry, power to the TMC1103 should be decoupled with ferrite beads and  $0.1\mu$ F capacitors to reduce noise.

- 4. The ground plane should be solid, not cross-hatched. Connections to the ground plane should have very short leads.

- 5. Decoupling capacitors should be applied liberally to VDD pins. Remember that not all power supply pins are created equal. They supply different circuits on the integrated circuit, each of which generate varying amounts and types of noise. For best results, use 0.1µF ceramic capacitors. Lead lengths should be minimized.

- CLKx should be handled carefully. Jitter and noise on this clock may degrade performance. Terminate the clock line, if needed, to eliminate overshoot and ringing.

#### **Related Products**

- TMC1175A, TMC1275 8-Bit Video A/D Converters

- TMC1173A, TMC1273 3V, Low-Power 8-Bit Video A/D Converters

- TMC1203 Triple 8-bit A/D Converter

- TMC3003/TMC3503 Triple Video D/A Converters

- TMC2242B/TMC2243/TMC2246A Digital Filters

#### Notes:

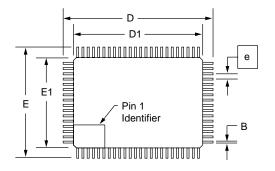

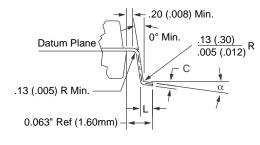

#### Mechanical Dimensions – 80-Lead MQFP Package

| Symbol | Inc   | hes        | Millim | neters | Notes |

|--------|-------|------------|--------|--------|-------|

| Symbol | Min.  | Max.       | Min.   | Max.   | Notes |

| А      | _     | .134       | _      | 3.40   |       |

| A1     | .010  | _          | .25    | —      |       |

| A2     | .100  | .120       | 2.55   | 3.05   |       |

| В      | .012  | .018       | .30    | .45    | 3, 5  |

| С      | .005  | .009       | .13    | .23    | 5     |

| D      | .904  | .923       | 22.95  | 23.45  |       |

| D1     | .783  | .791       | 19.90  | 20.10  |       |

| E      | .667  | .687       | 16.95  | 17.45  |       |

| E1     | .547  | .555       | 13.90  | 14.10  |       |

| е      | .0315 | BSC        | .80    | BSC    |       |

| L      | .025  | .041       | .65    | 1.03   | 4     |

| Ν      | 8     | 0          | 8      | 0      |       |

| ND     | 2     | 4          | 24     |        |       |

| NE     | 1     | 6          | 16     |        |       |

| α      | 0°    | <b>7</b> ° | 0°     | 7°     |       |

| CCC    | —     | .004       | —      | 0.10   |       |

#### Notes:

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Controlling dimension is millimeters.

- 3. Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be .08mm (.003in.) maximum in excess of the "B" dimension. Dambar cannot be located on the lower radius or the foot.

- 4. "L" is the length of terminal for soldering to a substrate.

- 5. "B" & "C" includes lead finish thickness.

Seating Plane

A A2

A1

See Lead Detail

-C-

Lead Detail

#### **Ordering Information**

| Product Number | Conversion<br>Rate (Msps) | Temperature Range                   | Screening  | Package      | Package Marking |

|----------------|---------------------------|-------------------------------------|------------|--------------|-----------------|

| TMC1103KLC20   | 20 Msps                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | 80-Lead MQFP | 1103KLC20       |

| TMC1103KLC40   | 40 Msps                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | 80-Lead MQFP | 1103KLC40       |

| TMC1103KLC50   | 50 Msps                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | Commercial | 80-Lead MQFP | 1103KLC50       |

For additional information regarding our products, please visit CADEKA at: cadeka.com

CADEKA Headquarters Loveland, Colorado T: 970.663.5452 T: 877.663.5452 (toll free)

CADEKA, the CADEKA logo design, COMLINEAR and the COMLINEAR logo design are trademarks or registered trademarks of CADEKA Microcircuits LLC. All other brand and product names may be trademarks of their respective companies.

CADEKA reserves the right to make changes to any products and services herein at any time without notice. CADEKA does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by CADEKA; nor does the purchase, lease, or use of a product or service from CADEKA convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of CADEKA or of third parties.

Copyright ©2007-2008 by CADEKA Microcircuits LLC. All rights reserved.

Amplify the Human Experience