### **General Description**

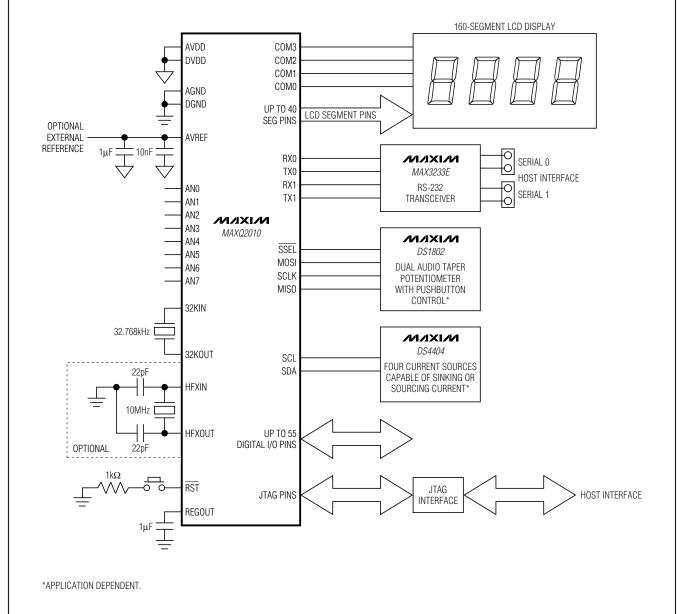

The MAXQ2010 microcontroller is a low-power, 16-bit device that incorporates a high-performance, 12-bit, multichannel ADC and a liquid-crystal display (LCD) interface. A combination of high performance, low power, and mixed-signal integration makes the MAXQ2010 ideal for a wide variety of applications.

The MAXQ2010 has 64KB of flash memory, 2KB of RAM, three 16-bit timers, and two universal synchronous/asynchronous receiver/transmitters (USARTs). Flash memory aids prototyping and is available for mass production. Mask ROM versions are available for large production volumes when cost is a critical factor. The microcontroller runs from a 2.7V to 3.6V operating supply. For the ultimate in low-power performance, the MAXQ2010 includes a low-power sleep mode, the ability to selectively disable peripherals, and multiple power-saving operating modes.

| Battery-Powered and                             | Home Appliances                               |

|-------------------------------------------------|-----------------------------------------------|

| Portable Devices                                | Consumer Electronics                          |

| Portable Medical                                | Thermostats/Humidity                          |

| Equipment                                       | Sensors                                       |

| Blood Glucose Meters                            | Security Sensors                              |

| Electrochemical and                             | Gas and Chemical                              |

| Optical Sensors                                 | Sensors                                       |

| Industrial Control                              | HVAC                                          |

| Data-Acquisition<br>Systems and Data<br>Loggers | Smart Transmitters<br>Medical Instrumentation |

### **Ordering Information**

**Applications**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAXQ2010-RFX+ | -40°C to +85°C | 100 LQFP    |

+Denotes a lead(Pb)-free/RoHS-compliant package.

# Typical Application Circuit, Pin Configuration, and Selector Guide appear at end of data sheet.

MAXQ is a registered trademark of Maxim Integrated Products, Inc. SPI is a trademark of Motorola, Inc.

### **Features**

- High-Performance, Low-Power, 16-Bit MAXQ<sup>®</sup> RISC Core

- ♦ DC to 10MHz Operation, Approaching 1MIPS per MHz

- ♦ 2.7V to 3.6V Operating Voltage

- ♦ 33 Instructions, Most Single Cycle

- Three Independent Data Pointers Accelerate Data Movement with Automatic Increment/Decrement

- 16-Level Hardware Stack

- ♦ 16-Bit Instruction Word, 16-Bit Data Bus

- ♦ 16 x 16-Bit General-Purpose Working Registers

- Optimized for C-Compiler (High-Speed/Density Code)

- On-Chip FLL Reduces External Clock Frequency

### Memory Features

### Peripheral Features

12-Bit SAR ADC with Internal Reference and Autoscan

Eight Single-Ended or Four Differential Inputs Up to 312.5ksps Sample Rate

- Supply Voltage Monitor with Adjustable Threshold One-Cycle, 16 x 16 Hardware Multiply/Accumulate with 48-Bit Accumulator

- Three 16-Bit Programmable Timers/Counters with PWM Outputs

- 32-Bit Binary Real-Time Clock with Digital Trim Capability

- Integrated LCD

160 Segments

No External Resistors Required

Two USARTs, I<sup>2</sup>C Master/Slave, and SPI™ Master/ Slave Communications Ports

On-Chip Power-On Reset/Brownout Reset Programmable Watchdog Timer

### Low Power Consumption

1mA (typ) at 1MHz Flash Operation at 2.7V 370nA (typ) in Stop Mode Low-Power Power-Management Mode (PMM)

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <u>www.maxim-ic.com/errata</u>.

###

Maxim Integrated Products 1

MHz Q2010 Data ent

# For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>64</sup>KB Flash Memory (In-Application and In-System Programmable)2KB Internal Data RAMJTAG Bootloader for Programming and Debug

| Absolute Maximum Ratings                                                   | 4  |

|----------------------------------------------------------------------------|----|

| Recommended DC Operating Conditions                                        | 4  |

| I <sup>2</sup> C Electrical Characteristics                                | 10 |

| I <sup>2</sup> C Bus Controller Timing                                     | 11 |

| I <sup>2</sup> C Bus Controller Timing (Acting As I <sup>2</sup> C Master) | 12 |

| I <sup>2</sup> C Bus Controller Timing (Acting As I <sup>2</sup> C Slave)  | 13 |

| Typical Operating Characteristics                                          | 14 |

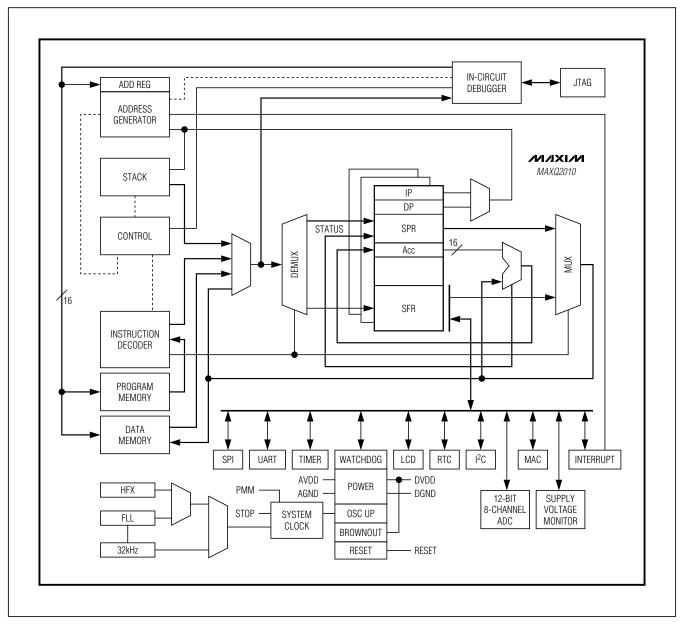

| Block Diagram                                                              | 15 |

| Pin Description                                                            | 16 |

| Detailed Description                                                       | 21 |

| MAXQ Core Architecture                                                     | 21 |

| Instruction Set                                                            | 21 |

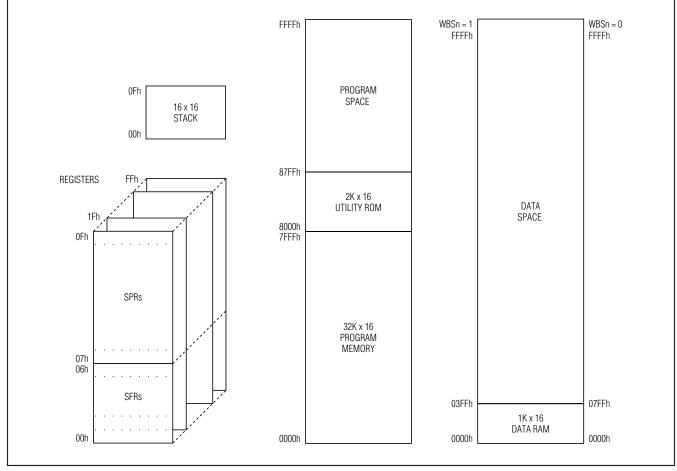

| Memory Organization                                                        | 21 |

| Stack Memory                                                               | 21 |

| Utility ROM                                                                |    |

| Programming                                                                |    |

| (Bootloader) In-System Programming                                         |    |

| In-Application Programming                                                 |    |

| Register Set                                                               |    |

| System Timing                                                              |    |

| Interrupts                                                                 | 24 |

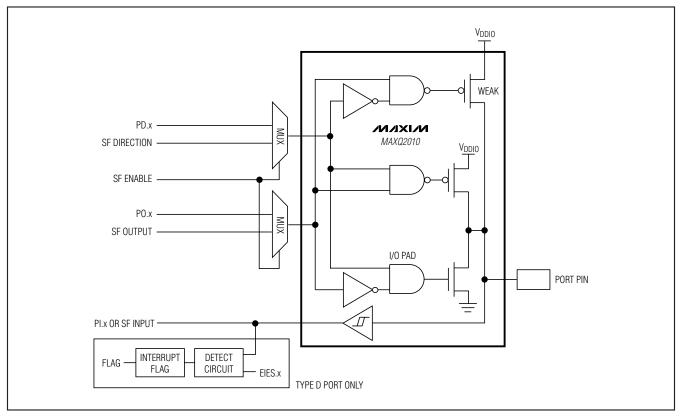

| I/O Ports                                                                  | 24 |

| Supply Voltage Monitor                                                     |    |

| Serial Peripherals                                                         |    |

| USART Serial Ports                                                         |    |

| I <sup>2</sup> C Bus                                                       | 26 |

| Serial Peripheral Interface (SPI)                                          | 26 |

| Real-Time Clock                                                            | 26 |

| Programmable Timers                                                        | 26 |

| Watchdog Timer                                                             | 27 |

| Hardware Multiplier                                                        | 27 |

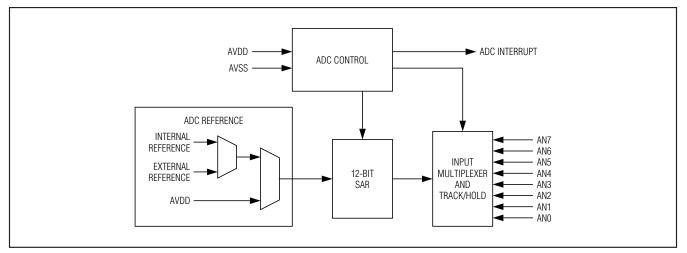

| Analog-to-Digital Converter                                                | 27 |

| LCD Controller                                                             | 28 |

| In-Circuit Debug                                                           |    |

| Applications Information                                                   | 30 |

| Grounds and Bypassing                                                      | 30 |

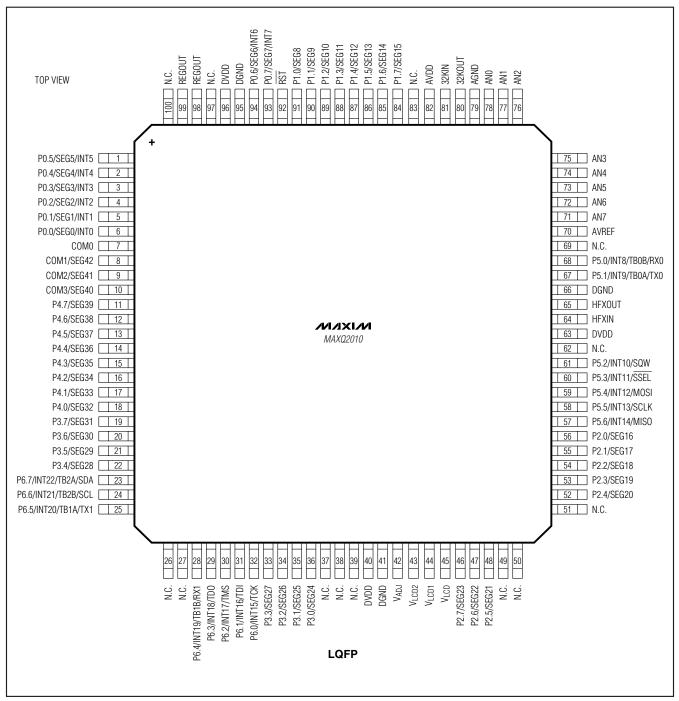

| Pin Configuration                                                          | 31 |

|                                                                            |    |

TABLE OF CONTENTS

###

| TABLE OF CONTENTS (continued)     |  |  |  |

|-----------------------------------|--|--|--|

| Typical Application Circuit       |  |  |  |

| Additional Documentation          |  |  |  |

| Development and Technical Support |  |  |  |

| Selector Guide                    |  |  |  |

| Package Information               |  |  |  |

| Revision History                  |  |  |  |

### **LIST OF FIGURES**

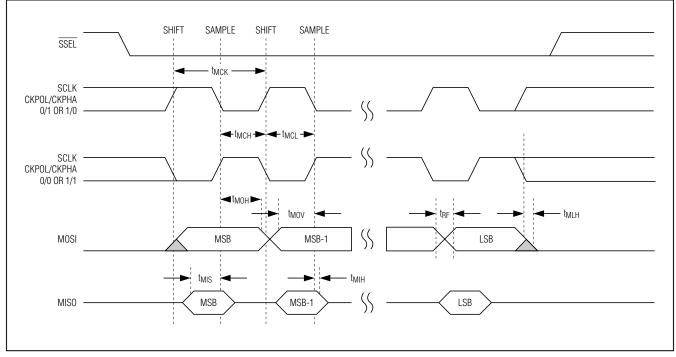

| Figure 1. SPI Master Timing                                                | 9  |

|----------------------------------------------------------------------------|----|

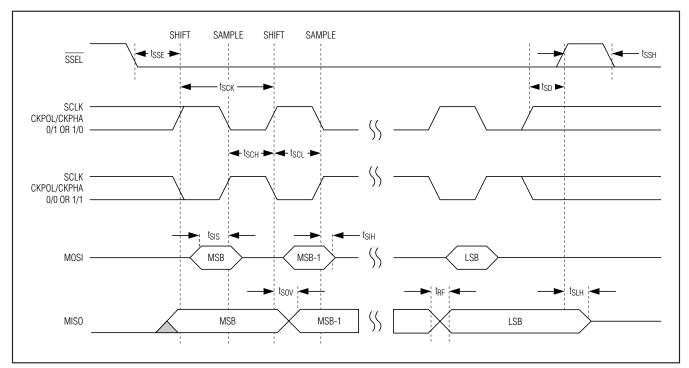

| Figure 2. SPI Slave Timing                                                 | 9  |

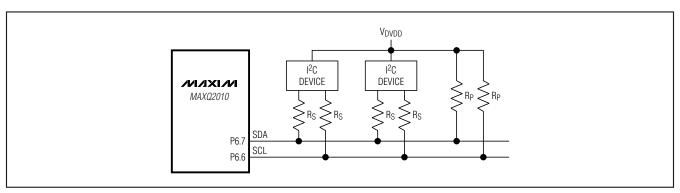

| Figure 3. Series Resistors (Rs) for Protecting Against High-Voltage Spikes | 10 |

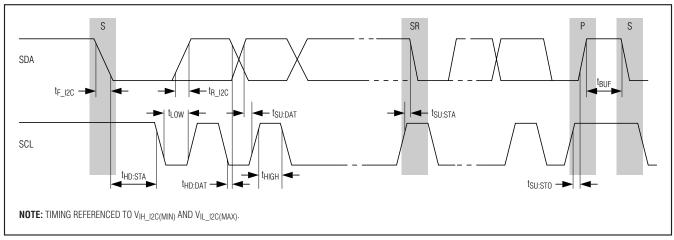

| Figure 4. I <sup>2</sup> C Bus Controller Timing Diagram                   | 13 |

| Figure 5. MAXQ2010 Default Memory Map                                      | 22 |

| Figure 6. Type C/D Port Pin Schematic                                      | 25 |

| Figure 7. ADC Block Diagram                                                | 28 |

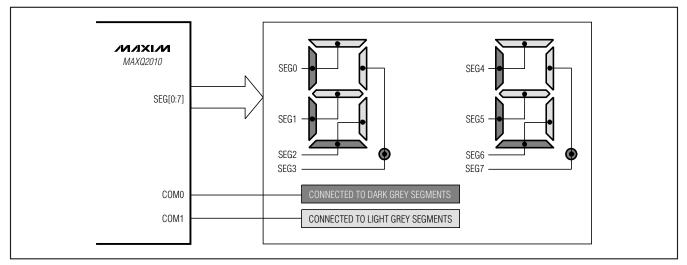

| -igure 8. Two-Character, 1/2 Duty, LCD Interface Example                   | 29 |

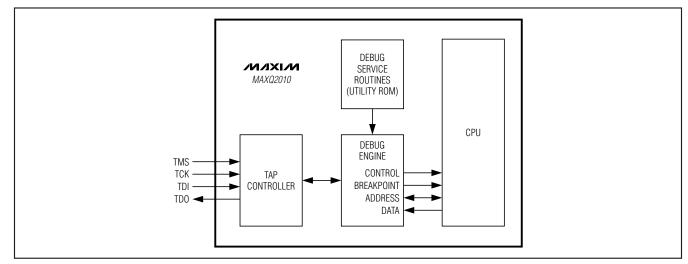

| -igure 9. In-Circuit Debugger                                              | 30 |

|                                                                            |    |

### LIST OF TABLES

| Table 1. Serial Port Operating Characteristics |  | 26 |

|------------------------------------------------|--|----|

|------------------------------------------------|--|----|

MAXQ2010

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on All Pins (including AVDD,

| DVDD) Relative to Ground             | 0.5V to +3.6V                       |

|--------------------------------------|-------------------------------------|

| Voltage Range on Any Pin Relative to |                                     |

| Ground Except AVDD, DVDD             | -0.5V to (V <sub>DVDD</sub> + 0.5V) |

| Operating Temperature Range          | 40°C to +85°C                       |

| Continuous Output Current |                          |

|---------------------------|--------------------------|

| Any Single I/O Pin        | 20mA                     |

| All I/O Pins Combined     | 100mA                    |

| Storage Temperature Range |                          |

| Soldering Temperature     |                          |

| 0                         | J-STD-020 Specification. |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED DC OPERATING CONDITIONS**

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$  (Note 1)

| PARAMETER                              | SYMBOL                          | CONDITIONS                                                               | MIN  | ТҮР    | MAX                         | UNITS |

|----------------------------------------|---------------------------------|--------------------------------------------------------------------------|------|--------|-----------------------------|-------|

| Digital Supply Voltage                 | Vdvdd                           |                                                                          | 2.7  |        | 3.6                         | V     |

| Digital Supply Voltage Output          | VREGOUT                         | (Note 2)                                                                 |      | 1.8    |                             | V     |

| Analog Supply Voltage                  | Vavdd                           | VAVDD = VDVDD                                                            | 2.7  |        | 3.6                         | V     |

| Ground                                 | GND                             | AGND = DGND                                                              | 0    |        | 0                           | V     |

| Digital Power-Fail Reset Voltage       | V <sub>RST</sub>                | Monitors V <sub>DVDD</sub>                                               | 2.55 | 2.6    | 2.65                        | V     |

| Active Current, FLL Disabled           | IDD_HFX1                        | $f_{CK} = 10MHz$ , $V_{DVDD} = V_{AVDD} = 2.7V$ ,<br>FREQMD = 0          |      | 3.1    | 3.75                        | mA    |

| (Note 3)                               | IDD_HFX2                        | $f_{CK} = 10MHz$ , $V_{DVDD} = V_{AVDD} = 3.6V$ ,<br>FREQMD = 0 (Note 4) |      | 3.2    | 4.0                         | ШA    |

|                                        | IDD1_FLL                        | Divide-by-1 mode, FREQMD = 0                                             |      | 3.15   | 4                           |       |

|                                        | IDD2_FLL                        | Divide-by-2 mode, FREQMD = 0 (Note 4)                                    |      | 2.9    | 3.6                         |       |

| Active Current, FLL Enabled (Note 5)   | IDD3_FLL                        | Divide-by-4 mode, FREQMD = 1 (Note 4)                                    |      | 2.25   | 3                           | mA    |

|                                        | IDD4_FLL                        | Divide-by-8 mode, FREQMD = 1 (Note 4)                                    |      | 1.4    | 2                           |       |

|                                        | IDD5_FLL                        | PMM mode, FREQMD = 1 (Note 4)                                            |      | 0.5    | 0.7                         |       |

|                                        | ISTOP_1                         | $T_{A} = +25^{\circ}C$                                                   |      | 0.37   | 4                           |       |

|                                        | (Note 7)                        | $T_{A} = +85^{\circ}C$                                                   |      | 0.68   | 6.5                         |       |

| Stop-Mode Current                      | I <sub>STOP_2</sub><br>(Note 8) | $T_A = +25^{\circ}C$                                                     |      | 0.94   | 5                           | μA    |

| (Note 6)                               |                                 | $T_{A} = +85^{\circ}C$                                                   |      | 1.3    | 6.5                         |       |

|                                        | ISTOP_3                         | $T_A = +25^{\circ}C$                                                     |      | 195    | 295                         |       |

|                                        | (Note 9)                        | $T_{A} = +85^{\circ}C$                                                   |      | 225    | 335                         |       |

|                                        | tSTOP_1                         | Internal regulator on                                                    |      | 4tcLCL |                             |       |

| Stop-Mode Resume Time<br>(Note 4)      | tSTOP_2                         | Internal regulator off, brownout or SVM on,<br>SVMSTOP = 1               |      | 30     | 160                         | μs    |

|                                        | tSTOP_3                         | Internal regulator, brownout, and SVM off                                |      | 30     | 320                         |       |

| Input Low Voltage on HFXIN and 32KIN   | VIL1                            |                                                                          | DGND |        | 0.20 x<br>V <sub>DVDD</sub> | V     |

| Input Low Voltage on All Other<br>Pins | V <sub>IL2</sub>                |                                                                          | DGND |        | 0.30 x<br>V <sub>DVDD</sub> | V     |

**MAXQ2010**

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$  (Note 1)

| PARAMETER                                          | SYMBOL           | CONDITIONS                      | MIN                         | ТҮР  | MAX   | UNITS |

|----------------------------------------------------|------------------|---------------------------------|-----------------------------|------|-------|-------|

| Input High Voltage on HFXIN<br>and 32KIN           | VIH1             |                                 | 0.75 x<br>V <sub>DVDD</sub> |      | Vdvdd | V     |

| Input High Voltage on All Other<br>Pins            | V <sub>IH2</sub> |                                 | 0.70<br>V <sub>DVDD</sub>   |      | Vdvdd | V     |

| Input Hysteresis (Schmitt)                         | VIHYS            |                                 |                             | 0.18 |       | V     |

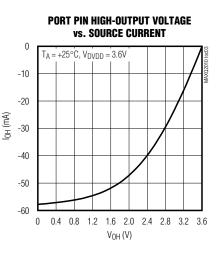

| Output Low Voltage for All Port<br>Pins (Note 10)  | V <sub>OL</sub>  | $I_{OL} = +4mA$                 | DGND                        |      | 0.4   | V     |

| Output High Voltage for All Port<br>Pins (Note 10) | V <sub>OH</sub>  | I <sub>OH</sub> = -4mA          | V <sub>DVDD</sub><br>- 0.4  |      |       | V     |

| I/O Pin Capacitance                                | CIO              | Guaranteed by design            |                             |      | 15    | pF    |

| I/O Pin Capacitance SCL, SDA<br>(Note 11)          | CIO_I2C          | Guaranteed by design            |                             |      | 10    | pF    |

| RST Pullup Resistance                              | R <sub>RST</sub> |                                 | 30                          |      | 85    | kΩ    |

| Input Low Current for $\overline{RST}$ Pin         | l <sub>IL1</sub> | $V_{IN} = 0.4V$                 | -85                         |      | -30   | μA    |

| Input Low Current for All Other<br>Pins            | I <sub>IL2</sub> | $V_{IN} = 0.4V$                 | -85                         |      | -30   | μA    |

| Input Leakage Current                              | ١L               | Internal pullup disabled        | -150                        |      | +150  | nA    |

| Input Pullup Resistor                              | R <sub>PU</sub>  |                                 | 30                          |      | 85    | kΩ    |

| CLOCK SOURCE                                       |                  |                                 |                             |      |       |       |

| External Clock Frequency                           | fHFIN            |                                 | DC                          |      | 10    | MHz   |

| External Clock Period                              | tCLCL            |                                 | 100                         |      |       | ns    |

| External Clock Duty Cycle                          | txclk_duty       |                                 | 40                          |      | 60    | %     |

| System Clock Frequency                             | fCK              |                                 | DC                          |      | 10    | MHz   |

| FREQUENCY-LOCKED LOOP (FL                          | .L)              |                                 |                             |      |       |       |

| FLL Output Frequency                               | f <sub>FLL</sub> | $f_{32KIN} = 32.768 \text{kHz}$ |                             | 8.4  |       | MHz   |

| FLL Output Frequency Delta                         | $\Delta f_{FLL}$ | f <sub>32KIN</sub> = 32.768kHz  |                             | 1.5  | ±5    | %     |

**Note 1:** Specifications to -40°C are guaranteed by design and are not production tested.

**Note 2:** Typical value presented for reference only. Do not draw current from this pin.

**Note 3:** FLL disabled. Crystal connected across HFXIN and HFXOUT. Operating in divide-by-1 mode. Measured on the DVDD pin and part executing program code from flash. All inputs are connected to GND or DVDD. Outputs do not source/sink any current. Timer B enabled.

**Note 4:** This parameter is guaranteed by design and is not production tested.

**Note 5:** FLL enabled. f<sub>32KIN</sub> = 32.768kHz, HFXIN = disconnected, FLL = 8.39MHz, measured on the DVDD pin, part executing program code from flash. All inputs are connected to GND or DVDD. Outputs do not source/sink any current. Timer B enabled.

**Note 6:** I<sub>STOP</sub> is the total current into the device when the device is in stop mode. This includes both the digital and analog current (current into DVDD and AVDD).

**Note 7:** Regulator, brownout monitor, LCD, and RTC disabled.

Note 8: Regulator, brownout monitor, and LCD disabled; RTC enabled.

**Note 9:** Regulator enabled, brownout monitor enabled, and LCD and RTC disabled.

Note 10: IOH(MAX) + IOL(MAX) for all outputs combined should not exceed 35mA to meet the specification.

**Note 11:** When DVDD is switched off, SDA and SCL may obstruct the line.

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                      | SYMBOL                  | CONDITIONS                                                                 | MIN                                | ТҮР      | MAX                  | UNITS               |

|------------------------------------------------|-------------------------|----------------------------------------------------------------------------|------------------------------------|----------|----------------------|---------------------|

| FLASH PROGRAMMING                              | •                       |                                                                            |                                    |          |                      |                     |

| System Clock During Flash<br>Programming/Erase |                         |                                                                            | 2                                  |          |                      | MHz                 |

| Flash Erase Time                               |                         | Mass erase<br>Page erase                                                   |                                    | 24<br>24 |                      | ms                  |

| Flash Programming Time per<br>Word (Note 12)   |                         |                                                                            |                                    | 66       |                      | μs                  |

| Write/Erase Cycles                             |                         |                                                                            | 20,000                             |          |                      | Cycles              |

| Data Retention                                 |                         | $T_A = +25^{\circ}C$                                                       | 100                                |          |                      | Years               |

| ANALOG-TO-DIGITAL CONVERT                      | ER (Note 13)            |                                                                            |                                    |          |                      | I                   |

| Serial Clock Frequency                         | fsclk                   |                                                                            | 0.1                                |          | 5                    | MHz                 |

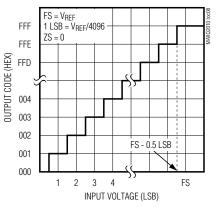

| Innut Valtaga Danga                            | Mana                    | Unipolar (single-ended)                                                    | 0                                  |          | VREF                 |                     |

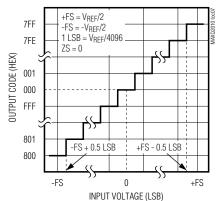

| Input Voltage Range                            | Vain                    | Bipolar (differential) (Note 14)                                           | -V <sub>REF</sub> /2               |          | +V <sub>REF</sub> /2 | V                   |

| Analog Input Capacitance                       | CAIN                    |                                                                            |                                    | 16       |                      | рF                  |

|                                                | IAVDD1                  | f <sub>SCLK</sub> = 5MHz, internal reference                               |                                    | 1.9      | 2.5                  |                     |

| Current Consumption (Note 4)                   | IAVDD2                  | f <sub>SCLK</sub> = 5MHz, external reference (internal reference disabled) |                                    | 1.1      | 1.3                  | mA                  |

| ANALOG-TO-DIGITAL CONVERT                      | ER PERFORM              | MANCE (V <sub>REF</sub> = V <sub>AVDD</sub> , 0.1µF capacitor on           | V <sub>REF</sub> , f <sub>SC</sub> | LK = 5M  | Hz)                  | 1                   |

| Resolution                                     |                         |                                                                            | 12                                 |          |                      | Bits                |

| Integral Nonlinearity                          | INL                     |                                                                            |                                    | ±1       | ±2                   | LSB                 |

| Differential Nonlinearity                      | DNL                     | No missing codes over temperature                                          |                                    |          | ±1                   | LSB                 |

| Offset Error                                   | VOS                     |                                                                            |                                    |          | ±2                   | LSB                 |

| Offset Temperature Coefficient                 |                         |                                                                            |                                    | ±0.5     |                      | ppm/°C              |

| Gain Error                                     |                         |                                                                            |                                    |          | ±1                   | %                   |

| Gain Temperature Coefficient                   |                         |                                                                            |                                    | ±0.5     |                      | ppm/°C              |

| Signal-to-Noise Plus Distortion                | SINAD                   | f <sub>IN</sub> = 1kHz                                                     | 65                                 |          |                      | dB                  |

| Spurious-Free Dynamic Range                    | SFDR                    | f <sub>IN</sub> = 1kHz                                                     | 68                                 |          |                      | dB                  |

| Throughput                                     |                         | 16 SCLK samples                                                            |                                    |          | 312.5                | ksps                |

| Conversion Time                                | tCONV                   | Not including t <sub>ACQ</sub>                                             | 2.6                                |          |                      | μs                  |

| ADC Setup Time                                 | tADC_SETUP<br>(Note 15) |                                                                            |                                    |          | 4                    | μs                  |

| Input Leakage Current                          | I <sub>ILA</sub>        | Shutdown or conversion stopped,<br>ANx and VAEREF                          |                                    |          | ±1                   | μA                  |

| Autoscan Throughput                            |                         | All channels active                                                        |                                    |          | 39                   | ksps per<br>channel |

| ANALOG-TO-DIGITAL CONVERT                      | ER REFEREN              | NCE                                                                        |                                    |          |                      |                     |

| Internal Reference Voltage                     | VAIREF                  |                                                                            | 1.47                               | 1.5      | 1.53                 | V                   |

| Internal Reference Voltage<br>Startup Time     | tAIREF                  |                                                                            |                                    |          | 50                   | μs                  |

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DVDD}=V_{AVDD}=2.7V$  to 3.6V,  $T_A=-40^{\circ}C$  to +85^{\circ}C.) (Note 1)

| PARAMETER                                                                                                             | SYMBOL                        | CONDITIONS                                                                    | MIN                         | ТҮР                                         | MAX                         | UNITS   |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------|-----------------------------|---------------------------------------------|-----------------------------|---------|

| External Reference Voltage<br>Input                                                                                   | VAEREF                        |                                                                               | 0.9                         |                                             | V <sub>AVDD</sub><br>+ 0.05 | V       |

| Internal Reference Voltage Drift                                                                                      | VADRIFT                       | Guaranteed by design                                                          |                             |                                             | ±50                         | ppm/°C  |

| Reference Settle Time<br>(Switching ADC Reference from<br>Either Internal or External<br>Reference to AVDD) (Note 16) | taavdd_<br>SETUP<br>(Note 17) |                                                                               |                             |                                             | 4                           | Samples |

| SUPPLY VOLTAGE MONITOR                                                                                                |                               |                                                                               |                             |                                             |                             |         |

| Supply Voltage Set Point                                                                                              | Vsvm                          |                                                                               | 2.7                         |                                             | 3.5                         | V       |

| Supply Voltage Increment<br>Resolution (Note 18)                                                                      | SVINC                         |                                                                               | 0.08                        | 0.1                                         | 0.12                        | V       |

| Supply Voltage Default Set Point                                                                                      |                               |                                                                               |                             | 2.7                                         |                             | μA      |

| Supply Voltage Monitor Current<br>Consumption                                                                         | ISVM                          |                                                                               |                             | 20                                          |                             | μs      |

| Supply Voltage Monitor Setup<br>Time (Time from Supply Voltage<br>Monitor Enabled to SVMRDY Is<br>Set to 1) (Note 18) | tsvm_su                       |                                                                               |                             | 15                                          | 25                          | μs      |

| REAL-TIME CLOCK                                                                                                       | •                             |                                                                               | •                           |                                             |                             | •       |

| RTC Input Frequency                                                                                                   | f32KIN                        | 32kHz watch crystal                                                           |                             | 32,768                                      |                             | Hz      |

| RTC Operating Current                                                                                                 | IRTC                          | $V_{\text{DVDD}} = 2.7V$ , guaranteed by design                               |                             | 0.45                                        | 0.7                         | μA      |

| The operating current                                                                                                 | IRIC                          | $V_{\text{DVDD}} = 3.6V$                                                      |                             | 0.5                                         | 0.8                         | μΑ      |

| LCD                                                                                                                   |                               |                                                                               |                             |                                             |                             |         |

| LCD Reference Voltage                                                                                                 | VLCD                          |                                                                               | Vdvdd                       |                                             | 3.6                         | V       |

| LCD Bias Voltage 1                                                                                                    | V <sub>LCD1</sub>             | 1/3 bias                                                                      | 2/3                         | V <sub>ADJ</sub> +<br>(V <sub>LCD</sub> - V | (ADJ)                       | V       |

| LCD Bias Voltage 2                                                                                                    | V <sub>LCD2</sub>             | 1/3 bias                                                                      | 2/3                         | V <sub>ADJ</sub> +<br>(V <sub>LCD</sub> - V | ADJ)                        | V       |

| LCD Adjustment Voltage                                                                                                | V <sub>ADJ</sub>              | Guaranteed by design                                                          | 0                           |                                             | 0.4 x<br>V <sub>LCD</sub>   | V       |

| LCD Bias Resistor                                                                                                     | R <sub>LCD</sub>              |                                                                               |                             | 40                                          |                             | kΩ      |

| LCD Adjustment Resistor                                                                                               | R <sub>LADJ</sub>             | LRA[3:0] = 15                                                                 |                             | 80                                          |                             | kΩ      |

|                                                                                                                       |                               | Pin is driven at $V_{LCD} = 3V$ , $I_{SEGxx} = -3\mu A$                       | V <sub>LCD</sub> -<br>0.02  |                                             | V <sub>LCD</sub>            |         |

| LCD Segment and COM Voltage (Note 18)                                                                                 | V <sub>SEGxx</sub>            | Pin is driven at $V_{LCD1} = 2V$ , $I_{SEGxx} = -3\mu A$                      | V <sub>LCD1</sub> -<br>0.02 |                                             | V <sub>LCD1</sub> +<br>0.02 | V       |

|                                                                                                                       |                               | Pin is driven at $V_{LCD2} = 1V$ , $I_{SEGxx} = -3\mu A$                      | V <sub>LCD2</sub> -<br>0.02 |                                             | V <sub>LCD2</sub> +<br>0.02 |         |

|                                                                                                                       |                               | Pin is driven at V <sub>ADJ</sub> = 0V, I <sub>SEGxx</sub> = -3µA             | -0.1                        |                                             | +0.1                        |         |

| LCD Output Rise Time                                                                                                  | tLCD_RISE                     | COM output load = 5000pF, SEG output<br>load = 200pF, V <sub>LCD</sub> = 3.3V |                             |                                             | 200                         | μs      |

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                               | SYMBOL             | CONDITIONS    | MIN                           | ТҮР                 | MAX                      | UNITS |

|---------------------------------------------------------|--------------------|---------------|-------------------------------|---------------------|--------------------------|-------|

| SPI (See Figures 1 and 2)                               |                    |               | L                             |                     |                          |       |

| SPI Master Operating Frequency                          | 1/t <sub>MCK</sub> |               |                               |                     | f <sub>CK</sub> /2       | MHz   |

| SPI Slave Operating Frequency                           | 1/tsck             |               |                               |                     | fCK/8                    | MHz   |

| SCLK Output Pulse-Width<br>High/Low                     | tMCH, tMCL         |               | (t <sub>MCK</sub> /2)<br>- 25 |                     |                          | ns    |

| SCLK Input Pulse-Width<br>High/Low                      | tSCH, tSCL         |               |                               | t <sub>SCK</sub> /2 |                          | ns    |

| MOSI Output Hold Time After<br>SCLK Sample Edge         | tмон               | $C_L = 50 pF$ | (t <sub>MCK</sub> /2)<br>- 25 |                     |                          | ns    |

| MOSI Output Valid to Sample<br>Edge                     | tmov               |               | (t <sub>MCK</sub> /2)<br>- 25 |                     |                          | ns    |

| MISO Input Valid to SCLK<br>Sample Edge Rise/Fall Setup | tMIS               |               | 25                            |                     |                          | ns    |

| MISO Input to SCLK Sample<br>Edge Rise/Fall Hold        | tMIH               |               | 0                             |                     |                          | ns    |

| SCLK Inactive to MOSI Inactive                          | tMLH               |               | (t <sub>MCK</sub> /2)<br>- 25 |                     |                          | ns    |

| SSEL Active to First Shift Edge                         | tsse               |               | 4t <sub>CK</sub>              |                     |                          | ns    |

| MOSI Input to SCLK Sample<br>Edge Rise/Fall Setup       | tsis               |               | 20                            |                     |                          | ns    |

| MOSI Input from SCLK Sample<br>Edge Transition Hold     | tsih               |               | t <sub>СК</sub> +<br>25       |                     |                          | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition   | tsov               |               |                               |                     | 3t <sub>CK</sub> +<br>25 | ns    |

| SSEL Inactive                                           | tssh               |               | t <sub>СК</sub> +<br>25       |                     |                          | ns    |

| SCLK Inactive to SSEL Rising                            | t <sub>SD</sub>    |               | t <sub>CK</sub> +<br>25       |                     |                          | ns    |

| MISO Output Disabled After<br>SSEL Edge Rise            | tslh               |               |                               |                     | 2t <sub>CK</sub> +<br>50 | ns    |

Note 12: Programming time does not include overhead associated with the utility ROM interface.

Note 13:  $V_{REF} = AV_{DD}$ .

**Note 14:** The operational input voltage range for each individual input of a differentially configured pair is from GND to AVDD. The operational input voltage difference is from  $-V_{REF}/2$  to  $+V_{REF}/2$ .

**Note 15:** The typical value is applied when a conversion is requested with ADPMO = 0. Under these conditions, the minimum delay is met. If ADPMO = 1, the user is responsible for ensuring the  $4\mu$ s delay time is met.

Note 16: Switching ADC reference from either internal or external reference to AVDD. Sample accuracy is not guaranteed prior to ADC reference settlement.

Note 17: Total on-board decoupling capacitance on the AVDD pin < 100nF. The output impedance of the regulator driving the AVDD pin <  $10\Omega$ .

Note 18: This parameter is guaranteed by design and is not production tested.

Figure 1. SPI Master Timing

Figure 2. SPI Slave Timing

9

**MAXQ2010**

### I<sup>2</sup>C ELECTRICAL CHARACTERISTICS

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                                                                                | SYMBOL              | TEST CONDITIONS                                                          | STANDA                  | RD MODE                 | FAST                     | MODE                    | UNITS |

|----------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------|-------------------------|-------------------------|--------------------------|-------------------------|-------|

| PARAMETER                                                                                                | STMBUL              | TEST CONDITIONS                                                          | MIN                     | MAX                     | MIN                      | MAX                     | UNITS |

| Input Low Voltage (Note 19)                                                                              | VIL_I2C             |                                                                          | -0.5                    | 0.3 x V <sub>DVDD</sub> | -0.5                     | 0.3 x V <sub>DVDD</sub> | V     |

| Input High Voltage (Note 19)                                                                             | VIH_I2C             |                                                                          | 0.7 x V <sub>DVDD</sub> |                         | 0.7 x V <sub>DVDD</sub>  | $V_{DVDD} + 0.5V$       | V     |

| Input Hysteresis (Schmitt)                                                                               | VIHYS_I2C           | $V_{DVDD} > 2V$                                                          |                         |                         | 0.05 x V <sub>DVDD</sub> |                         | V     |

| Output Logic-Low (Open<br>Drain or Open Collector)                                                       | V <sub>OL_I2C</sub> | V <sub>DVDD</sub> > 2V, 3mA sink<br>current                              | 0                       | 0.4                     | 0                        | 0.4                     | V     |

| Output Fall Time from<br>VIH_MIN to VIL_MAX with Bus<br>Capacitance from 10pF to<br>400pF (Notes 20, 21) | tof_12C             |                                                                          |                         | 250                     | 20 + 0.1C <sub>B</sub>   | 250                     | ns    |

| Pulse Width of Spike<br>Filtering That Must Be<br>Suppressed by Input Filter                             | tsp_12C             |                                                                          |                         |                         | 0                        | 50                      | ns    |

| Input Current on I/O                                                                                     | I <sub>IN_I2C</sub> | Input voltage from 0.1 x<br>V <sub>DVDD</sub> to 0.9 x V <sub>DVDD</sub> | -10                     | +10                     | -10                      | +10                     | μA    |

| I/O Capacitance                                                                                          | C10_12C             |                                                                          |                         | 10                      |                          | 10                      | рF    |

**Note 19:** Devices that use nonstandard supply voltages that do not conform to the intended I<sup>2</sup>C bus system levels must relate their input levels to the voltage to which the pullup resistors R<sub>P</sub> are connected. See Figure 3.

Note 20: CB-Capacitance of one bus line in pF.

**Note 21:** The maximum fall time of 300ns for the SDA and SCL bus lines shown in the *I*<sup>2</sup>*C Bus Controller Timing* table is longer than the specified maximum t<sub>OF\_I2C</sub> of 250ns for the output stages. This allows series protection resistors (R<sub>S</sub>) to be connected between the SDA/SCL pins and the SDA/SCL bus lines as shown in the *I*<sup>2</sup>*C Bus Controller Timing* (*Acting as I*<sup>2</sup>*C Slave*) table without exceeding the maximum specified fall time. See Figure 3.

Figure 3. Series Resistors (R<sub>S</sub>) for Protecting Against High-Voltage Spikes

### I<sup>2</sup>C BUS CONTROLLER TIMING

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$  (Note 22) (Figure 4)

| DADAMETED                                                                             | 0////00             | STANDAF                 |                   | FAST                                | NODE             |     |

|---------------------------------------------------------------------------------------|---------------------|-------------------------|-------------------|-------------------------------------|------------------|-----|

| PARAMETER                                                                             | SYMBOL              | MIN                     | MAX               | MIN                                 | МАХ              |     |

| Operating Frequency                                                                   | fi2C                | 0                       | 100               | 0                                   | 400              | kHz |

| Hold Time After (Repeated)<br>START                                                   | thd:sta             | 4.0                     |                   | 0.6                                 |                  | μs  |

| Clock Low Period                                                                      | tLOW_12C            | 4.7                     |                   | 1.3                                 |                  | μs  |

| Clock High Period                                                                     | thigh_i2C           | 4.0                     |                   | 0.6                                 |                  | μs  |

| Setup Time for Repeated START                                                         | tsu:sta             | 4.7                     |                   | 0.6                                 |                  | μs  |

| Hold Time for Data                                                                    | thd:dat             | 0<br>(Note 23)          | 3.45<br>(Note 24) | 0<br>(Note 23)                      | 0.9<br>(Note 24) | μs  |

| Setup Time for Data                                                                   | t <sub>SU:DAT</sub> | 250                     |                   | 100<br>(Note 25)                    |                  | ns  |

| SDA/SCL Fall Time                                                                     | tF_I2C              |                         | 300               | 20 + 0.1C <sub>B</sub><br>(Note 26) | 300              | ns  |

| SDA/SCL Rise Time                                                                     | tR_I2C              |                         | 1000              | 20 + 0.1C <sub>B</sub><br>(Note 26) | 300              | ns  |

| Setup Time for STOP                                                                   | tsu:sto             | 4.0                     |                   | 0.6                                 |                  | μs  |

| Bus-Free Time Between STOP and START                                                  | tBUF                | 4.7                     |                   | 1.3                                 |                  | μs  |

| Capacitive Load for Each Bus<br>Line                                                  | Св                  |                         | 400               |                                     | 400              | pF  |

| Noise Margin at the Low Level<br>for Each Connected Device<br>(Including Hysteresis)  | V <sub>NL_I2C</sub> | 0.1 x V <sub>DVDD</sub> |                   | 0.1 x V <sub>DVDD</sub>             |                  | V   |

| Noise Margin at the High Level<br>for Each Connected Device<br>(Including Hysteresis) | VNH_I2C             | 0.2 x V <sub>DVDD</sub> |                   | 0.2 x V <sub>DVDD</sub>             |                  | V   |

Note 22: All values referenced to VIH\_I2C(MIN) and VIL\_I2C(MAX).

Note 23: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to as the V<sub>IH\_I2C(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

Note 24: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW\_I2C</sub>) of the SCL signal.

**Note 25:** A fast-mode I<sup>2</sup>C bus device can be used in a standard-mode I<sup>2</sup>C bus system, but the requirement  $t_{SU:DAT} \ge 250$ ns must be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line  $t_{R_{-1}2C(MAX)} + t_{SU:DAT} = 1000 + 250$ = 1250ns (according to the standard-mode I<sup>2</sup>C specification) before the SCL line is released.

Note 26: CB-Total capacitance of one bus line in pF.

### I<sup>2</sup>C BUS CONTROLLER TIMING (ACTING AS I<sup>2</sup>C MASTER)

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$  (Figure 4)

|                                                                                       | 0,4450              | STANDARD MODE           |                     | FAST N                  | IODE                |     |

|---------------------------------------------------------------------------------------|---------------------|-------------------------|---------------------|-------------------------|---------------------|-----|

| PARAMETER                                                                             | SYMBOL              | MIN                     | MAX                 | MIN                     | МАХ                 |     |

| System Frequency                                                                      | fsys                | 0.90                    |                     | 3.60                    |                     | MHz |

| Operating Frequency                                                                   | f <sub>I2C</sub>    |                         | f <sub>SYS</sub> /8 |                         | f <sub>SYS</sub> /8 | Hz  |

| Hold Time After (Repeated)<br>START                                                   | <sup>t</sup> HD:STA | <sup>t</sup> HIGH_I2C   |                     | thigh_i2C               |                     | μs  |

| Clock Low Period                                                                      | tLOW_12C            | 5tsys                   |                     | 5tsys                   |                     | μs  |

| Clock High Period                                                                     | thigh_i2C           | 3tsys                   |                     | 3tsys                   |                     | μs  |

| Setup Time for Repeated START                                                         | tsu:sta             | tLOW_12C                |                     | tLOW_I2C                |                     | μs  |

| Hold Time for Data                                                                    | thd:dat             | 0                       | 3.45                | 0                       | 0.9                 | μs  |

| Setup Time for Data                                                                   | tsu:dat             | 250                     |                     | 100                     |                     | ns  |

| SDA/SCL Fall Time                                                                     | tF_I2C              |                         | 300                 | 20+ 0.1C <sub>B</sub>   | 300                 | ns  |

| SDA/SCL Rise Time                                                                     | tR_I2C              |                         | 1000                | 20+ 0.1C <sub>B</sub>   | 300                 | ns  |

| Setup Time for STOP                                                                   | tsu:sto             | thigh_i2C               |                     | thigh_i2C               |                     | μs  |

| Bus-Free Time Between STOP<br>and START                                               | tBUF                | tLOW_I2C                |                     | tLOW_I2C                |                     | μs  |

| Capacitive Load for Each Bus<br>Line                                                  | Св                  |                         | 400                 |                         | 400                 | pF  |

| Noise Margin at the Low Level<br>for Each Connected Device<br>(Including Hysteresis)  | V <sub>NL_12C</sub> | 0.1 x V <sub>DVDD</sub> |                     | 0.1 x V <sub>DVDD</sub> |                     | V   |

| Noise Margin at the High Level<br>for Each Connected Device<br>(Including Hysteresis) | V <sub>NH_12C</sub> | 0.2 x V <sub>DVDD</sub> |                     | 0.2 x V <sub>DVDD</sub> |                     | V   |

### I<sup>2</sup>C BUS CONTROLLER TIMING (ACTING AS I<sup>2</sup>C SLAVE)

(V\_DVDD = V\_AVDD = 2.7V to 3.6V,  $T_A$  = -40°C to +85°C.) (Figure 4)

| DADAMETED                                                                             | 0////201            | STANDAR                 | D MODE              | FAST M                  | IODE                |     |

|---------------------------------------------------------------------------------------|---------------------|-------------------------|---------------------|-------------------------|---------------------|-----|

| PARAMETER                                                                             | SYMBOL              | MIN                     | MAX                 | MIN                     | MAX                 |     |

| System Frequency                                                                      | fsys                | 0.9                     |                     | 3.60                    |                     | MHz |

| Operating Frequency                                                                   | fi2C                |                         | f <sub>SYS</sub> /8 |                         | f <sub>SYS</sub> /8 | Hz  |

| System Clock Period                                                                   | tsys                | 1/f <sub>I2C</sub>      |                     |                         | 1/f <sub>I2C</sub>  | μs  |

| Hold Time After (Repeated)<br>START                                                   | <sup>t</sup> HD:STA | 3tsys                   |                     | 3tsys                   |                     | μs  |

| Clock Low Period                                                                      | tLOW_I2C            | 5tsys                   |                     | 5tsys                   |                     | μs  |

| Clock High Period                                                                     | thigh_i2C           | 3t <sub>SYS</sub>       |                     | 3t <sub>SYS</sub>       |                     | μs  |

| Setup Time for Repeated START                                                         | tsu:sta             | 5tsys                   |                     | 5tsys                   |                     | μs  |

| Hold Time for Data                                                                    | thd:dat             | 0                       | 3.45                | 0                       | 0.9                 | μs  |

| Setup Time for Data                                                                   | tsu:dat             | 250                     |                     | 100                     |                     | ns  |

| SDA/SCL Fall Time                                                                     | tF_I2C              |                         | 300                 | 20 + 0.1C <sub>B</sub>  | 300                 | ns  |

| SDA/SCL Rise Time                                                                     | tR_I2C              |                         | 1000                | 20 + 0.1C <sub>B</sub>  | 300                 | ns  |

| Setup Time for STOP                                                                   | tsu:sto             | 3t <sub>SYS</sub>       |                     | 3tsys                   |                     | μs  |

| Bus-Free Time Between STOP<br>and START                                               | tBUF                | 5tsys                   |                     | 5tsys                   |                     | μs  |

| Capacitive Load for Each Bus<br>Line                                                  | CB                  |                         | 400                 |                         | 400                 | pF  |

| Noise Margin at the Low Level<br>for Each Connected Device<br>(Including Hysteresis)  | V <sub>NL_12C</sub> | 0.1 x V <sub>DVDD</sub> |                     | 0.1 x VDVDD             |                     | V   |

| Noise Margin at the High Level<br>for Each Connected Device<br>(Including Hysteresis) | V <sub>NH_I2C</sub> | 0.2 x V <sub>DVDD</sub> |                     | 0.2 x V <sub>DVDD</sub> |                     | v   |

Figure 4. I<sup>2</sup>C Bus Controller Timing Diagram

$(T_A = +25^{\circ}C, unless otherwise noted.)$

**VDD SUPPLY CURRENT** PORT PIN LOW-OUTPUT VOLTAGE vs. CLOCK FREQUENCY vs. SINK CURRENT 3.5 40 CLOCK SOURCE DRIVEN ON HFXIN, T<sub>A</sub> = +25°C, FLL DISABLED  $T_A = +25^{\circ}C$ ,  $V_{DVDD} = 3.6V$ 35 3.0 30 25 loo1 (mA) 2.5 I<sub>0L</sub> (mA) 20 FREQMD = 02.0 15 FREQMD = 1 10 1.5 5 1.0 0 0.4 0.8 1.2 1.6 2.0 0 2 6 8 10 0 4 f<sub>HFXIN</sub> (MHz) Vol (V) **INTEGRAL NONLINEARITY (INL) DIFFERENTIAL NONLINEARITY (DNL)** vs. CODE vs. CODE 2.0 1.0  $T_A = +25^{\circ}C, V_{AVDD} = 3.3V, V_{REF} = 3.0V$  $T_A = +25^{\circ}C$ ,  $V_{AVDD} = 3.3V$ ,  $V_{REF} = 3.0V$ 0.8 1.5 0.6 1.0 0.4 0.5 0.2 INL (LSB) DNL (LSB) 0 0 -0.2 -0.5 -0.4 -1.0 -0.6 -1.5 -0.8

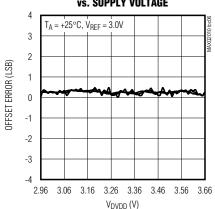

### **Typical Operating Characteristics**

**OFFSET ERROR** vs. SUPPLY VOLTAGE

### **DIFFERENTIAL BIPOLAR TRANSFER**

4000

3000

-1.0

0

1000

2000

CODE

### SINGLE-ENDED UNIPOLAR TRANSFER

2.4 2.8 3.2 3.6

<u>, n. t. t. t. t.</u>

4000

3000

-2.0

0

1000

2000

CODE

### Block Diagram

**MAXQ2010**

**Pin Description**

| PIN        | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                   | POWER PINS                                                                                                                                                                                                                                                                                                                                                              |

| 40, 63, 96 | DVDD              | Digital Supply Voltage                                                                                                                                                                                                                                                                                                                                                  |

| 41, 66, 95 | DGND              | Digital Ground                                                                                                                                                                                                                                                                                                                                                          |

| 98, 99     | REGOUT            | <b>Regulator Capacitor.</b> These pins must be shorted together at the pins and then connected to ground through a $1.0\mu$ F ceramic capacitor.                                                                                                                                                                                                                        |

| 82         | AVDD              | Analog Supply Voltage                                                                                                                                                                                                                                                                                                                                                   |

| 79         | AGND              | Analog Ground                                                                                                                                                                                                                                                                                                                                                           |

|            |                   | ANALOG MEASUREMENT PINS                                                                                                                                                                                                                                                                                                                                                 |

| 70         | AVREF             | <b>Analog Voltage Reference.</b> When using an external reference source, this pin must be connected to $1\mu$ F and $0.01\mu$ F filter capacitors in parallel. When using an internal reference source, this pin must be connected to a $0.01\mu$ F capacitor.                                                                                                         |

| 78, 77     | AN0, AN1          | <b>Analog Input 0:1.</b> This pair of analog inputs can function as two single-ended inputs or one differential pair. When functioning in differential mode, AN0 is the positive input and AN1 is the negative input.                                                                                                                                                   |

| 76, 75     | AN2, AN3          | <b>Analog Input 2:3.</b> This pair of analog inputs can function as two single-ended inputs or one differential pair. When functioning in differential mode, AN2 is the positive input and AN3 is the negative input.                                                                                                                                                   |

| 74, 73     | AN4, AN5          | <b>Analog Input 4:5.</b> This pair of analog inputs can function as two single-ended inputs or one differential pair. When functioning in differential mode, AN4 is the positive input and AN5 is the negative input.                                                                                                                                                   |

| 72, 71     | AN6, AN7          | <b>Analog Input 6:7.</b> This pair of analog inputs can function as two single-ended inputs or one differential pair. When functioning in differential mode, AN6 is the positive input and AN7 is the negative input.                                                                                                                                                   |

|            |                   | RESET PIN                                                                                                                                                                                                                                                                                                                                                               |

| 92         | RST               | <b>Digital, Active-Low, Reset Input/Output.</b> The CPU is held in reset when this pin is low and begins executing from the reset vector when released. The pin includes pullup current source and should be driven by an open-drain, external source capable of sinking in excess of 4mA. This pin is driven low as an output when an internal reset condition occurs. |

|            |                   | CLOCK PINS                                                                                                                                                                                                                                                                                                                                                              |

| 81         | 32KIN             | 32kHz Crystal Input/Output. Connect an external 6pF, 32kHz watch crystal between 32KIN                                                                                                                                                                                                                                                                                  |

| 80         | 32KOUT            | - and 32KOUT to generate the system clock. Alternatively, 32KIN is the input for an external clock source when 32KOUT is disconnected.                                                                                                                                                                                                                                  |

| 64         | HEXIN             | High-Frequency Crystal Input. Connect an external crystal or resonator between HFXIN and                                                                                                                                                                                                                                                                                |

| 65         | HFXOUT            | HFXOUT as the high-frequency system clock. Alternatively, HFXIN is the input for an external,                                                                                                                                                                                                                                                                           |

| 00         |                   | high-frequency clock source when HFXOUT is disconnected.                                                                                                                                                                                                                                                                                                                |

|            |                   | LCD PINS                                                                                                                                                                                                                                                                                                                                                                |

| 45         | VLCD              | external source.                                                                                                                                                                                                                                                                                                                                                        |

| 44         | V <sub>LCD1</sub> | <b>LCD Bias, Voltage 1.</b> LCD drive voltage used with 1/2 and 1/3 LCD bias. An internal resistor-<br>divider sets the voltage. External resistors and capacitors can be used to change the LCD voltage or drive capability at this pin.                                                                                                                               |

MAXQ2010

# Pin Description (continued)

| PIN          | NAME                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FUNC                                                                                                                                                                                                                   | TION                                                                                |                                                   |  |  |  |

|--------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| 43           | VLCD2                    | sets the voltage. Externa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>CD Bias, Voltage 2.</b> LCD drive voltage used with 1/3 LCD bias. An internal resistor-divider ets the voltage. External resistors and capacitors can be used to change LCD voltage or rive capability at this pin. |                                                                                     |                                                   |  |  |  |

| 42           | VADJ                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>.CD Adjustment Voltage.</b> Connect to an external resistor to provide external control of the LCD contrast. Leave disconnected for internal contrast adjustment.                                                   |                                                                                     |                                                   |  |  |  |

|              | GENE                     | RAL-PURPOSE I/O, SPEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CIAL FUNCTION, AND LO                                                                                                                                                                                                  | CD INTERFACE PINS                                                                   |                                                   |  |  |  |