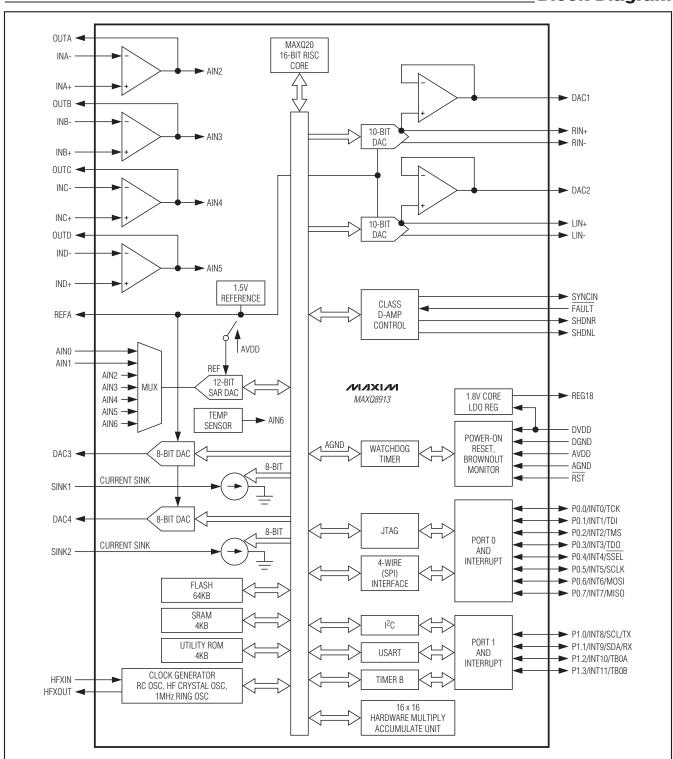

### **General Description**

The MAXQ8913 is a single-chip servo controller designed as a complete solution for dual axis optical image stabilization (OIS) applications. The device incorporates all the necessary elements for conditioning of sensor signals, analog-to-digital conversion, digital servo algorithm implementation using a 16-bit RISC microcontroller, and digital-to-analog conversion, as well as including dual servo amplifiers.

Even though the device is targeted for OIS applications, it can be effectively used in many other types of servo control. The MAXQ8913 supports both voice coil and stepper motor applications.

The MAXQ8913 includes four op amps; a 7-channel, 12-bit ADC; dual 10-bit differential DACs; and dual 8-bit single-ended DACs. It also contains 64KB of flash memory, 4KB of RAM, 4KB of ROM, a 16-bit timer/counter, a universal asynchronous/synchronous receiver-transmitter (USART), an I2C port, and an SPI™ master/slave

For the ultimate in low-power performance, the OIS device includes a low-power sleep mode, the ability to selectively disable peripherals, and multiple power-saving operating modes.

### **Applications**

Digital Camera and Cell Phone Optical Image Stabilization

Servo Loop Control

Tone Generation with Speaker Drive

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAXQ8913EWG+T | -40°C to +85°C | 58 WLP      |

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

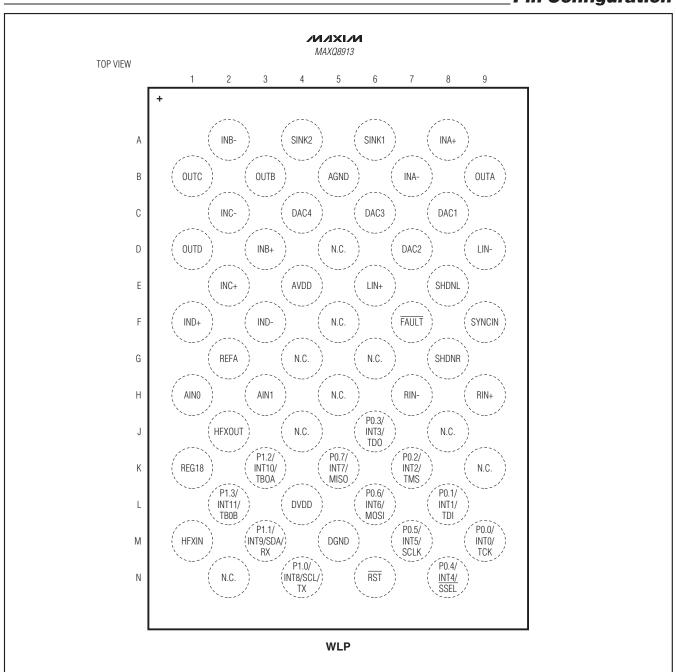

Pin Configuration appears at end of data sheet.

#### **Features**

- ♦ High-Performance, Low-Power, 16-Bit MAXQ® **RISC Core**

- ♦ One-Cycle, 16 x 16 Hardware Multiply/Accumulate with 48-Bit Accumulator

- **♦ Two Current Sinks for Driving Hall-Effect Elements**

- **♦ Four DACs**

- ♦ DC to 10MHz Operation; Approaching 1MIPS per MHz

- ♦ 2.7V to 3.6V Logic/Analog Operating Voltage

- ♦ 33 Instructions, Most Single Cycle

- ♦ Three Independent Data Pointers Accelerate Data **Movement with Automatic Increment/Decrement**

- ♦ 16-Level Hardware Stack

- ♦ 16-Bit Instruction Word, 16-Bit Data Bus

- ♦ 16 x 16-Bit General-Purpose Working Registers

- **♦ Optimized for C Compilers**

- **♦ Memory Features**

64KB Flash Memory 4KB of Internal Data RAM 4KB of Utility ROM

JTAG Bootloader for Programming and Debug

#### **♦** Peripherals

Four Operational Amplifiers 12-Bit SAR ADC with Internal Reference and Autoscan Up to 312ksps Sample Rate Seven-Input Mux (Four Internally Connected to Op-Amp Outputs, One Internally Connected to Temp Sensor, and Two Connected to

Brownout Reset Generation 16-Bit Programmable Timer/Counter USART, I<sup>2</sup>C, and SPI Master/Slave On-Chip Power-On Reset/Brownout Reset Programmable Watchdog

Uncommitted External Pins)

#### **♦ Low-Power Consumption**

3mA (max) at 10MHz Flash Operation at 3.3V 4.5µA (max) in Stop Mode Low-Power Power-Management Mode (PMM)

SPI is a trademark of Motorola. Inc.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on All Pins (including AVDD,          | Operating Temperature Range |                          |

|-----------------------------------------------------|-----------------------------|--------------------------|

| DVDD) Relative to Ground0.5V to +3.6V               | Storage Temperature Range   | 65°C to +150°C           |

| Voltage Range on Any Pin Relative to Ground         | Soldering Temperature       | Refer to the IPC/JEDEC   |

| except AVDD, DVDD0.5V to (V <sub>DVDD</sub> + 0.5V) |                             | J-STD-020 Specification. |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                   | SYMBOL               | CONDITIONS                                                      | MIN                         | TYP  | MAX                         | UNITS |

|-------------------------------------------------------------|----------------------|-----------------------------------------------------------------|-----------------------------|------|-----------------------------|-------|

| Digital Supply Voltage                                      | V <sub>D</sub> VDD   | V <sub>A</sub> V <sub>DD</sub> = V <sub>D</sub> V <sub>DD</sub> | VRST                        | 3.3  | 3.6                         | V     |

| Digital Operating Voltage                                   |                      |                                                                 | VRST                        |      | 3.6                         | V     |

| Regulator Voltage Output                                    | V <sub>REG18</sub>   | (Note 2)                                                        | 1.71                        | 1.8  | 1.89                        | V     |

| Analog Supply Voltage                                       | V <sub>AVDD</sub>    | V <sub>A</sub> V <sub>DD</sub> = V <sub>D</sub> V <sub>DD</sub> | 2.7                         |      | 3.6                         | V     |

| Ground                                                      | GND                  | AGND = DGND                                                     | 0                           | 0    | 0                           | V     |

| Digital Power-Fail Reset Voltage                            | V <sub>RST</sub>     | Monitors V <sub>DVDD</sub>                                      | 2.58                        |      | 2.68                        | V     |

| Active Current (Note 3)                                     | I <sub>DD_HFX3</sub> | $f_{CK} = 10MHz$ , $V_{DVDD} = 2.7V$                            |                             |      | 2.2                         | mA    |

| Active Current (Note 3)                                     | IDD_HFX4             | $f_{CK} = 10MHz, V_{DVDD} = 3.3V$                               |                             |      | 3.0                         | IIIA  |

|                                                             | ISTOP_1              | (Notes 4, 5)                                                    |                             | 0.2  | 4.5                         |       |

| Stop-Mode Current                                           | ISTOP_2              | (Notes 4, 6)                                                    |                             |      | 40                          | μΑ    |

|                                                             | ISTOP_3              | (Notes 4, 7)                                                    |                             |      | 500                         |       |

| Stop-Mode Resume Time                                       | tSTOP_1              | Internal regulator on                                           |                             | 15   |                             |       |

| Stop-Mode Nesume Time                                       | tSTOP_2              | Internal regulator off, brownout or SVM on                      |                             | 375  |                             | μs    |

| Input Low Voltage on HFXIN                                  | V <sub>IL1</sub>     |                                                                 | V <sub>DGND</sub>           |      | 0.20 x<br>V <sub>DVDD</sub> | V     |

| Input Low Voltage on All Other Port Pins                    | VIL2                 |                                                                 | VDGND                       |      | 0.30 x<br>V <sub>DVDD</sub> | V     |

| Input High Voltage on HFXIN                                 | V <sub>IH1</sub>     |                                                                 | 0.75 x<br>V <sub>DVDD</sub> |      | V <sub>DVDD</sub>           | V     |

| Input High Voltage on All Other Port Pins                   | V <sub>IH2</sub>     |                                                                 | 0.70 x<br>V <sub>DVDD</sub> |      | V <sub>DVDD</sub>           | V     |

| Input Hysteresis (Schmitt)                                  | VIHYS                |                                                                 |                             | 0.18 |                             | V     |

| Output Low Voltage for All Port<br>Pins Except SHDNL, SHDNR | VoL                  | I <sub>OL</sub> = 4mA (Note 8)                                  | VDGND                       |      | 0.4                         | V     |

| Output Low Voltage for SHDNL, SHDNR                         | VoL                  | I <sub>OL</sub> = 1.5mA                                         | V <sub>DGND</sub>           |      | 0.4                         | V     |

| Output High Voltage for All Port<br>Pins                    | Voн                  | I <sub>OH</sub> = -4mA (Note 8)                                 | V <sub>D</sub> VDD<br>- 0.4 |      |                             | V     |

| I/O Pin Capacitance                                         | CIO                  | Guaranteed by design                                            |                             |      | 15                          | рF    |

### RECOMMENDED DC OPERATING CONDITIONS (continued)

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                      | SYMBOL             | CONDITIONS                                                                 | MIN                  | TYP   | MAX                  | UNITS  |

|------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------------|-------|----------------------|--------|

| Input Low Current for Port Pins                | I <sub>I</sub> L   | $V_{IN} = 0.4V$                                                            |                      |       | 100                  | μΑ     |

| Input-Leakage Current                          | IL                 | Internal pullup disabled                                                   | -300                 |       | +300                 | nA     |

| Input Pullup Resistor                          | R <sub>PU</sub>    |                                                                            | 30                   | 70    | 110                  | kΩ     |

| CLOCK SOURCE                                   | •                  |                                                                            | •                    |       |                      |        |

| External Clock Frequency                       | fHFIN              |                                                                            | DC                   |       | 10                   | MHz    |

| External Clock Duty Cycle                      | txclk_duty         |                                                                            | 40                   |       | 60                   | %      |

| Internal Ring Oscillator                       |                    |                                                                            |                      | 1     |                      | MHz    |

| System Clock Frequency                         | fck                |                                                                            | DC                   |       | 10                   | MHz    |

| FLASH AC CHARACTERISTICS                       | •                  |                                                                            | •                    |       |                      |        |

| System Clock During Flash<br>Programming/Erase |                    |                                                                            | 2                    |       |                      | MHz    |

| Program Time                                   | tprog              |                                                                            | 20                   |       | 40                   | μs     |

| Page Erase Time                                | terasetme          |                                                                            | 20                   |       | 40                   | ms     |

| Mass Erase Time                                |                    |                                                                            | 20                   |       | 40                   | ms     |

| Write/Erase Cycles                             |                    |                                                                            | 1000                 |       |                      | Cycles |

| Data Retention                                 |                    | T <sub>A</sub> = +25°C                                                     | 100                  |       |                      | Years  |

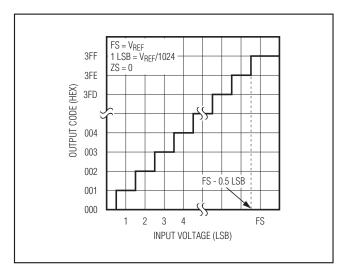

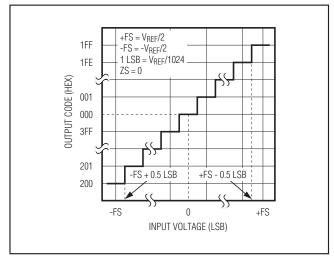

| ANALOG-TO-DIGITAL CONVERT                      | ER (Note 9)        |                                                                            |                      |       |                      |        |

| ADC Clock Frequency                            | fsclk              |                                                                            | 0.1                  |       | 5                    | MHz    |

| Input Voltage Dange                            | Mana               | Unipolar (single-ended)                                                    | 0                    |       | V <sub>REF</sub>     | V      |

| Input Voltage Range                            | VAIN               | Bipolar (differential) (Note 10)                                           | -V <sub>REF</sub> /2 |       | +V <sub>REF</sub> /2 | V      |

| Analog Input Capacitance                       | CAIN               |                                                                            |                      | 16    |                      | рF     |

|                                                | lavdd1             | f <sub>SCLK</sub> = 5MHz, internal reference                               |                      |       | 3.0                  | mΑ     |

| Current Consumption                            | l <sub>AVDD2</sub> | f <sub>SCLK</sub> = 5MHz, external reference (internal reference disabled) |                      |       | 800                  | μΑ     |

|                                                | IASTOP             | Power-down mode                                                            |                      |       | 2.5                  |        |

| ANALOG-TO-DIGITAL CONVERT                      | ER PERFORM         | MANCE (V <sub>REF</sub> = 3V, 0.1µF capacitor on REF.                      | A, fsclk =           | 5MHz) |                      |        |

| Resolution                                     |                    |                                                                            |                      | 12    |                      | Bits   |

| Integral Nonlinearity                          | INL                |                                                                            |                      | ±1    | ±2                   | LSB    |

| Differential Nonlinearity                      | DNL                | No missing codes from +25°C to +85°C                                       |                      |       | ±1                   | LSB    |

| Offset Error                                   |                    |                                                                            |                      |       | ±10                  | LSB    |

| Gain Error                                     |                    |                                                                            |                      |       | ±1                   | %      |

| Gain Temperature Coefficient                   |                    |                                                                            |                      | ±0.5  |                      | ppm/°C |

| Signal-to-Noise Plus Distortion                | SINAD              | $f_{IN} = 1kHz$                                                            | 69                   |       |                      | dB     |

| Spurious-Free Dynamic Range                    | SFDR               | f <sub>IN</sub> = 1kHz                                                     | 76                   |       |                      | dB     |

| Throughput                                     |                    | 16f <sub>SCLK</sub> samples                                                |                      |       | 312                  | ksps   |

| ADC Setup Time                                 | tADC_SETUP         | (Note 11)                                                                  |                      |       | 4                    | μs     |

| Input-Leakage Current                          | lila               | Shutdown or conversion stopped;<br>AINO/AIN1 and VAEREF                    |                      |       | ±1                   | μΑ     |

### RECOMMENDED DC OPERATING CONDITIONS (continued)

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                                                                   | SYMBOL            | CONDITIONS                                       | MIN  | TYP              | MAX                         | UNITS                  |

|-------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------|------|------------------|-----------------------------|------------------------|

| Autoscan Throughput                                                                                         |                   | All channels active                              |      |                  | 39                          | ksps<br>per<br>channel |

| ANALOG-TO-DIGITAL CONVERTE                                                                                  | R REFEREN         | NCE                                              |      |                  |                             |                        |

| Internal Reference Voltage                                                                                  | VAIREF            |                                                  | 1.44 | 1.5              | 1.56                        | V                      |

| Internal Reference Voltage<br>Startup Time                                                                  | tairef            |                                                  |      |                  | 50                          | μs                     |

| External Reference Voltage Input                                                                            | VAEREF            |                                                  | 0.9  |                  | V <sub>AVDD</sub><br>+ 0.05 | V                      |

| Internal Reference Voltage Drift                                                                            | Vadrift           | Guaranteed by design                             |      |                  | ±50                         | ppm/°C                 |

| Reference Settle Time<br>(Switching ADC Reference from<br>Either Internal or External<br>Reference to AVDD) | taavdd_<br>SETUP  | (Note 12)                                        |      |                  | 4                           | Samples                |

| Reference Output                                                                                            | V <sub>REFA</sub> |                                                  |      | V <sub>REF</sub> |                             | V                      |

| SUPPLY VOLTAGE MONITOR                                                                                      |                   |                                                  |      |                  |                             |                        |

| Supply Voltage Set Point                                                                                    | Svtr              |                                                  | 2.7  |                  | 3.5                         | V                      |

| Supply Voltage Increment<br>Resolution                                                                      |                   |                                                  | 80   | 100              | 120                         | mV                     |

| Supply Voltage Default Set Point                                                                            |                   |                                                  |      | 2.7              |                             | V                      |

| Supply Voltage Monitor Start<br>Time                                                                        | tsvmst            |                                                  |      |                  | 50                          | μs                     |

| Supply Voltage Monitor Setup                                                                                | tsvm_su1          | Changing from one set point to another set point |      |                  | 2                           |                        |

| Time                                                                                                        | tsvm_su2          | Exit from stop mode                              |      |                  | 8                           | - μs                   |

| CLASS D AMPLIFIER CONTROL                                                                                   | DACs, 10-BI       | T DACs                                           |      |                  |                             | •                      |

| Resolution                                                                                                  |                   |                                                  | 10   |                  |                             | Bits                   |

| Full-Scale Output Voltage                                                                                   | VFS               | Code 0 = -2.5, code 1023 = +2.5,<br>VREF = 1.5V  | ±2.3 | ±2.5             | ±2.8                        | V                      |

| Output Common-Mode Voltage                                                                                  | VCM               |                                                  | 1.15 | 1.25             | 1.4                         | V                      |

| DC Output Impedance                                                                                         | ZOUT              | At DC, per side                                  |      | 10               |                             | kΩ                     |

| Integral Nonlinearity                                                                                       | INL               |                                                  |      | ±2               |                             | LSB                    |

| Differential Nonlinearity                                                                                   | DNL               | Guaranteed monotonic by design                   | -1   | ±0.10            |                             | LSB                    |

| Settling Time                                                                                               |                   | From 1/4 FS to 3/4 FS to 1 LSB                   |      | 2                |                             | μs                     |

| Digital Feedthrough                                                                                         |                   |                                                  |      | 0.15             |                             | nV-s                   |

| Glitch Impulse                                                                                              |                   | Major carry transition                           |      | 12               |                             | nV-s                   |

| Update Rate                                                                                                 |                   | (Note 13)                                        | 100  |                  | <u> </u>                    | ksps                   |

4 \_\_\_\_\_\_*MIXIM*

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                      | SYMBOL             | CONDITIONS                                                                                                            | MIN                          | TYP             | MAX                 | UNITS |

|----------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|---------------------|-------|

| DAC3 AND DAC4 INCLUDING BU                                     | JFFER              |                                                                                                                       | •                            |                 |                     |       |

| Resolution                                                     |                    |                                                                                                                       | 8                            |                 |                     | Bits  |

| Full-Scale Output Voltage                                      | VFS                | Code 0 = 0.35, code 255 = 2.35,<br>V <sub>REF</sub> = 1.5                                                             | 0.30 to<br>2.20              | 0.35 to<br>2.35 | 0.45 to<br>2.7      | V     |

| Output Common-Mode Voltage                                     | VCM                | Code = 128, V <sub>REF</sub> = 1.5V                                                                                   | 1.25                         | 1.35            | 1.55                | V     |

| DC Drive Capability                                            | I <sub>DRIVE</sub> | (Note 14)                                                                                                             | 1                            |                 |                     | mA    |

| Integral Nonlinearity                                          | INL                |                                                                                                                       |                              | ±1              |                     | LSB   |

| Differential Nonlinearity                                      | DNL                | Guaranteed monotonic by design                                                                                        | -1                           | ±0.5            |                     | LSB   |

| Settling Time                                                  |                    | From 1/4 FS to 3/4 FS to 1 LSB                                                                                        |                              | 5               |                     | μs    |

| Update Rate                                                    |                    | (Note 14)                                                                                                             | 100                          |                 |                     | ksps  |

| OP AMP A, B, C, D                                              | •                  |                                                                                                                       | •                            |                 |                     |       |

| Offset Voltage                                                 | Vos                | V <sub>CM</sub> = 2V                                                                                                  | -8                           | ±2              | +8                  | mV    |

| Offset Drift                                                   | Vosdrift           | V <sub>CM</sub> = 2V                                                                                                  |                              | 10              |                     | μV/°C |

| Input Bias Current                                             | IBIAS              | $T_A = +25^{\circ}C \text{ (Note 13)}$                                                                                |                              |                 | 1                   | nA    |

| Common-Mode Rejection Ratio                                    | CMMR               |                                                                                                                       | 60                           | 80              |                     | dB    |

| Gain Bandwidth Product                                         | GB                 |                                                                                                                       |                              | > 200           |                     | kHz   |

| Input Common-Mode Range                                        | CMR <sub>NG</sub>  |                                                                                                                       | 1                            |                 | VAVDD               | V     |

| TEMPERATURE SENSOR                                             |                    |                                                                                                                       |                              |                 |                     |       |

| Sensitivity                                                    |                    | Code 0 = -273.15C; absolute 0; 8 LSB/°C for V <sub>REF</sub> = 1.5V, 12-bit ADC; 4 LSB/°C for V <sub>REF</sub> = 3.0V |                              | 2.9304          |                     | mV/°C |

| Raw Accuracy                                                   |                    | No correction, T = 300°K (Note 14)                                                                                    | -6                           |                 | +6                  | °C    |

| CURRENT SINK                                                   | •                  |                                                                                                                       | •                            |                 |                     | •     |

| Resolution                                                     |                    | Code 0 = 0, code 1 = 62.5µA,<br>code 255 = 15.94mA                                                                    | 8                            |                 |                     | Bits  |

| Full-Scale Sink Current                                        | I <sub>S15</sub>   | Code = 255, V <sub>DS</sub> = 2V, V <sub>REF</sub> = 1.5V                                                             | 14.9                         | 15.94           | 18.0                | mA    |

| Zero-Scale Sink Current                                        | I <sub>S0</sub>    | Code = 0, V <sub>DS</sub> = 2V                                                                                        |                              | 0               | 1                   | μΑ    |

| LSB Size                                                       | LSB                | V <sub>DS</sub> = 2V, V <sub>REF</sub> = 1.5V                                                                         |                              | 62.5            |                     | μΑ    |

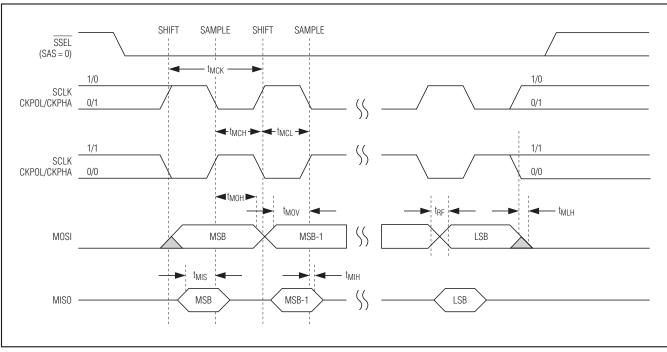

| SPI: MASTER MODE (See Figure                                   | es 1, 2)           |                                                                                                                       | •                            |                 |                     |       |

| SPI Master Operating Frequency                                 | 1/t <sub>MCK</sub> |                                                                                                                       |                              |                 | f <sub>SYS</sub> /2 | MHz   |

| SCLK Output Pulse Width-<br>High/Low                           | tMCH, tMCL         |                                                                                                                       | tMCK/<br>2 - t <sub>RF</sub> |                 |                     | ns    |

| I/O Rise/Fall Time<br>(This parameter is device<br>dependent.) | tRF                | $C_L = 15pF$ , pullup = $560\Omega$                                                                                   |                              |                 | 16                  | ns    |

| MOSI Output Valid to SCLK<br>Sample Edge (MOSI Setup)          | tmov               |                                                                                                                       | tMCK/<br>2 - t <sub>RF</sub> |                 |                     | ns    |

| MOSI Output Hold After SCLK<br>Sample Edge                     | tMOH               |                                                                                                                       | tMCK/<br>2 - t <sub>RF</sub> |                 |                     | ns    |

#### RECOMMENDED DC OPERATING CONDITIONS (continued)

$(V_{DVDD} = V_{AVDD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                       | SYMBOL             | CONDITIONS                          | MIN                                       | TYP | MAX                                     | UNITS |

|-----------------------------------------------------------------|--------------------|-------------------------------------|-------------------------------------------|-----|-----------------------------------------|-------|

| SCLK Last Sample Edge to MOSI<br>Output Change (MOSI Last Hold) | tMLH               |                                     | t <sub>MCK</sub> /<br>2 - t <sub>RF</sub> |     |                                         | ns    |

| MISO Input Valid to SCLK<br>Sample Edge (MISO Setup)            | tMIS               | (Note 13)                           | 2t <sub>RF</sub>                          |     |                                         | ns    |

| MISO Input Hold After SCLK<br>Sample Edge                       | tMIH               |                                     | 0                                         |     |                                         | ns    |

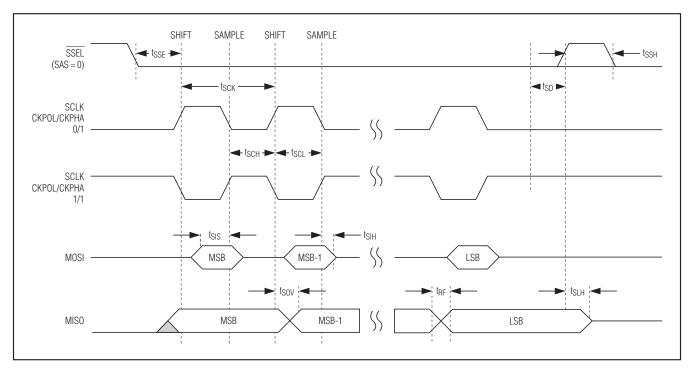

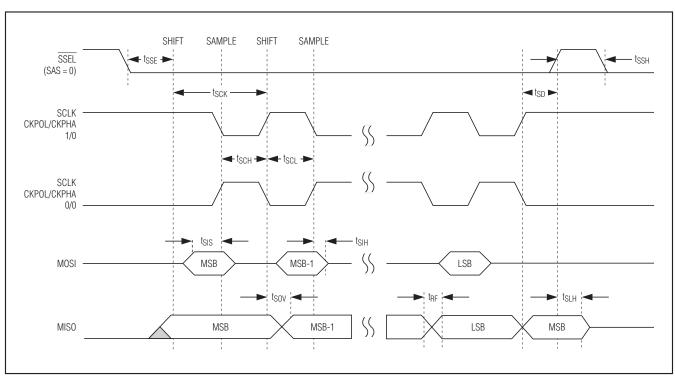

| SPI: SLAVE MODE (See Figures                                    | 1, 3)              |                                     |                                           |     |                                         |       |

| SPI Slave Operating Frequency                                   | 1/t <sub>SCK</sub> |                                     |                                           |     | f <sub>SYS</sub> /4                     | kHz   |

| SCLK Input Pulse-Width<br>High/Low                              | tsch, tscl         |                                     | tsck/<br>2 - t <sub>RF</sub>              |     |                                         | ns    |

| I/O Rise/Fall Time<br>(This parameter is device<br>dependent.)  | t <sub>RF</sub>    | $C_L$ = 15pF, pullup = 560 $\Omega$ |                                           |     | 16                                      | ns    |

| SSEL Active to First Shift Edge                                 | tsse               |                                     | t <sub>RF</sub>                           |     |                                         | ns    |

| MOSI Input to SCLK Sample<br>Edge Rise/Fall Setup               | tsis               |                                     | t <sub>RF</sub>                           |     |                                         | ns    |

| MOSI Input from SCLK Sample<br>Edge Transition Hold             | tsıн               |                                     | t <sub>RF</sub>                           |     |                                         | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition           | tsov               | (Note 13)                           |                                           |     | 2t <sub>RF</sub>                        | ns    |

| SSEL Inactive to Next SSEL<br>Asserted                          | tssh               |                                     | tsys +                                    |     |                                         | ns    |

| SCLK Inactive to SSEL Deasserted                                | t <sub>SD</sub>    |                                     | t <sub>RF</sub>                           |     |                                         | ns    |

| MISO Output Disabled After SSEL Edge Deasserted                 | tslh               |                                     |                                           |     | 2t <sub>SYS</sub><br>+ 2t <sub>RF</sub> | ns    |

- Note 1: Specifications to -20°C are guaranteed by design and are not production tested.

- **Note 2:** Connect to ground through a 1µF capacitor.

- **Note 3:** Crystal connected to HFXIN, HFXOUT. Operating in /1 mode. Measured on the DVDD pin and the device not in reset. All inputs are connected to GND or DVDD. Outputs do not source/sink any current. One timer B enabled, with the device executing code from flash.

- Note 4: ISTOP is the total current into the device when the device is in stop mode.

- Note 5: Regulator, brownout disabled. Stop mode current through AVDD and DVDD.

- Note 6: Regulator disabled, brownout enabled. Stop mode current through AVDD and DVDD.

- Note 7: Regulator enabled, brownout enabled.

- Note 8: IOH(MAX) + IOL(MAX) for all outputs combined should not exceed 35mA to meet the specification.

- Note 9:  $V_{REF} = V_{AVDD}$ .

- **Note 10:** The operational input voltage range for each individual input of a differentially configured pair is from GND to AVDD. The operational input voltage difference is from -V<sub>REF</sub>/2 to +V<sub>REF</sub>/2.

- **Note 11:** The typical value is applied when a conversion is requested with ADPMO = 0. Under these conditions, the minimum delay is met. If ADPMO = 1, the user is responsible for ensuring the 4µs delay time is met.

- **Note 12:** Total on-board decoupling capacitance on the AVDD pin < 100nF. The output impedance of the regulator driving the AVDD pin <  $10\Omega$ .

- Note 13: This value is the sum of input R/F and output R/F.

- Note 14: Guaranteed by design and characterization.

Figure 1. Enhanced SPI Master Timing

Figure 2. Enhanced SPI Slave Mode Timing (CKPHA = 1)

Figure 3. Enhanced SPI Slave Mode Timing (CKPHA = 0)

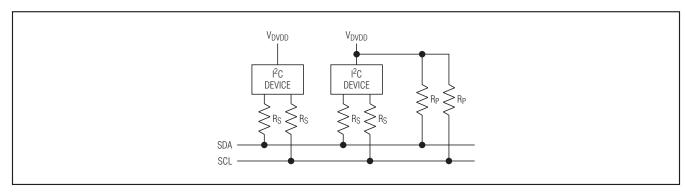

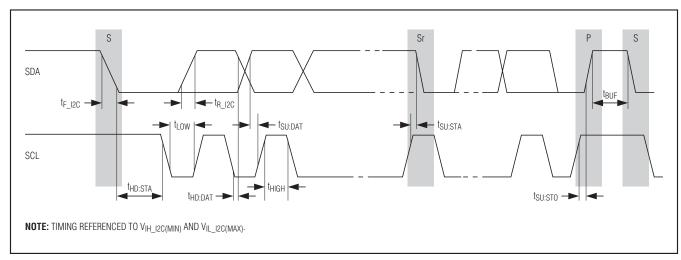

#### I<sup>2</sup>C BUS CONTROLLER AC CHARACTERISTICS

$(V_{DVDD} = 1.8V \text{ to } 3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$  (See Figure 4.)

| PARAMETER                                                                                                                            | SYMBOL                | TEST                                        | STANDA                  | RD MODE                 | FAST                        | MODE                                 | UNITS |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------|-------------------------|-------------------------|-----------------------------|--------------------------------------|-------|

| PARAMETER                                                                                                                            | SYMBOL                | CONDITIONS                                  | MIN                     | MAX                     | MIN                         | MAX                                  | UNITS |

| Input Low Voltage                                                                                                                    | V <sub>IL_I2C</sub>   |                                             | -0.5                    | 0.3 x V <sub>DVDD</sub> | -0.5                        | 0.3 x V <sub>DVDD</sub><br>(Note 15) | V     |

| Input High Voltage                                                                                                                   | VIH_I2C               |                                             | 0.7 x V <sub>DVDD</sub> |                         | 0.7 x V <sub>DVDD</sub>     | (Note 16)                            | V     |

| Input Hysteresis (Schmitt)                                                                                                           | V <sub>IHYS_I2C</sub> | V <sub>DVDD</sub> > 2V                      |                         |                         | 0.05 x<br>V <sub>DVDD</sub> |                                      | V     |

| Output Logic-Low (Open Drain or Open Collector)                                                                                      | V <sub>OL_I2C</sub>   | V <sub>DVDD</sub> > 2V, 3mA<br>sink current | 0                       | 0.4                     | 0                           | 0.4                                  | V     |

| Output Fall Time from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> with Bus Capacitance from 10pF to 400pF (Notes 17, 18)            | tOF_I2C               |                                             |                         | 250                     | 20 + 0.1C <sub>B</sub>      | 250                                  | ns    |

| Pulse Width of Spike Filtering<br>That Must Be Suppressed by<br>Input Filter                                                         | tsp_i2C               |                                             |                         |                         | 0                           | 50                                   | ns    |

| Input Current Each I/O Pin<br>with an Input Voltage<br>Between 0.1 x V <sub>DVDD</sub> and 0.9<br>x V <sub>DVDD(MAX)</sub> (Note 19) | I <sub>IN_I2C</sub>   |                                             | -10                     | +10                     | -10                         | +10                                  | μΑ    |

| I/O Capacitance                                                                                                                      | C <sub>10_12C</sub>   |                                             |                         | 10                      |                             | 10                                   | pF    |

- **Note 15:** Devices that use nonstandard supply voltages that do not conform to the intended I<sup>2</sup>C-bus system levels must relate their input levels to the V<sub>DVDD</sub> voltage to which the pullup resistors R<sub>P</sub> are connected.

- Note 16: Maximum  $V_{IH}$   $I_{2C} = V_{DVDD(MAX)} + 0.5V$ .

- Note 17: C<sub>B</sub> = capacitance of one bus line in pF.

- Note 18: The maximum fall time of 300ns for the SDA and SCL bus lines as shown in the *I*<sup>2</sup>*C* Bus Controller Timing table is longer than the specified maximum toF\_12C of 250ns for the output stages. This allows series protection resistors (R<sub>s</sub>) to be connected between the SDA/SCL pins and the SDA/SCL bus lines as shown in the *I*<sup>2</sup>*C* Bus Controller Timing (Acting as *I*<sup>2</sup>*C* Slave) table without exceeding the maximum specified fall time. See Figure 4.

- Note 19: I/O pins of fast-mode devices must not obstruct the SDA and SCL lines if V<sub>DVDD</sub> is switched off.

Figure 4. Series Resistors (Rs) for Protecting Against High-Voltage Spikes

#### I<sup>2</sup>C BUS CONTROLLER TIMING

(All values referenced to  $V_{IH\_I2C(MIN)}$  and  $V_{IL\_I2C(MAX)}$ . See Figure 5.)

| PARAMETER                                                                       | SYMBOL               | STANDA                     | RD MODE | FAST M                     | IODE | LINITE |

|---------------------------------------------------------------------------------|----------------------|----------------------------|---------|----------------------------|------|--------|

| PARAMETER                                                                       | SYMBOL               | MIN                        | MAX     | MIN                        | MAX  | UNITS  |

| Operating Frequency                                                             | f <sub>I2C</sub>     | 0                          | 100     | 0                          | 400  | kHz    |

| Hold Time After (Repeated) START                                                | tHD:STA              | 4.0                        |         | 0.6                        |      | μs     |

| Clock Low Period                                                                | tLOW_I2C             | 4.7                        |         | 1.3                        |      | μs     |

| Clock High Period                                                               | thigh_i2C            | 4.0                        |         | 0.6                        |      | μs     |

| Setup Time for Repeated START                                                   | tsu:sta              | 4.7                        |         | 0.6                        |      | μs     |

| Hold Time for Data (Notes 20, 21)                                               | tHD:DAT              | 0                          | 3.45    | 0                          | 0.9  | μs     |

| Setup Time for Data (Note 22)                                                   | tsu:dat              | 250                        |         | 100                        |      | ns     |

| SDA/SCL Fall Time (Note 23)                                                     | tF_I2C               |                            | 300     | 20 + 0.1C <sub>B</sub>     | 300  | ns     |

| SDA/SCL Rise Time (Note 23)                                                     | t <sub>R_I2C</sub>   |                            | 1000    | 20 + 0.1C <sub>B</sub>     | 300  | ns     |

| Setup Time for STOP                                                             | tsu:sto              | 4.0                        |         | 0.6                        |      | μs     |

| Bus-Free Time Between STOP and START                                            | tBUF                 | 4.7                        |         | 1.3                        |      | μs     |

| Capacitive Load for Each Bus Line                                               | CB                   |                            | 400     |                            | 400  | pF     |

| Noise Margin at the Low Level for Each Connected Device (Including Hysteresis)  | V <sub>NL_</sub> 12C | 0.1 x<br>V <sub>DVDD</sub> |         | 0.1 x<br>V <sub>DVDD</sub> |      | V      |

| Noise Margin at the High Level for Each Connected Device (Including Hysteresis) | VNH_I2C              | 0.2 x<br>V <sub>DVDD</sub> |         | 0.2 x<br>V <sub>DVDD</sub> |      | V      |

- Note 20: A device must internally provide a hold time of at least 300ns for the SDA signal (referenced to the V<sub>IH\_I2C(MIN)</sub>) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 21: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW 12C</sub>) of the SCL signal.

- Note 22: A fast-mode I<sup>2</sup>C-bus device can be used in a standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>R\_I2C(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I<sup>2</sup>C specification) before the SCL line is released.

- **Note 23:**  $C_B = Total$  capacitance of one bus line in pF.

### I<sup>2</sup>C BUS CONTROLLER TIMING (ACTING AS I<sup>2</sup>C MASTER)

| DADAMETER                                                                       | CVMDOL               | STANDAF                    | RD MODE             | FAST N                      | IODE                | LIMITO |

|---------------------------------------------------------------------------------|----------------------|----------------------------|---------------------|-----------------------------|---------------------|--------|

| PARAMETER                                                                       | SYMBOL               | MIN                        | MAX                 | MIN                         | MAX                 | UNITS  |

| System Frequency                                                                | fsys                 | 1                          |                     | 3.60                        |                     | MHz    |

| Operating Frequency                                                             | f <sub>I2C</sub>     |                            | f <sub>SYS</sub> /8 |                             | f <sub>SYS</sub> /8 | Hz     |

| Hold Time After (Repeated) START                                                | thd:sta              | tHIGH_I2C                  |                     | tHIGH_I2C                   |                     | μs     |

| Clock Low Period                                                                | tLOW_I2C             | 5                          |                     | 5                           |                     | tsys   |

| Clock High Period                                                               | thigh_i2C            | 3                          |                     | 3                           |                     | tsys   |

| Setup Time for Repeated START                                                   | tsu:sta              | tLOW_I2C                   |                     | tLOW_I2C                    |                     | μs     |

| Hold Time for Data                                                              | thd:dat              | 0                          | 3.45                | 0                           | 0.9                 | μs     |

| Setup Time for Data                                                             | t <sub>SU:DAT</sub>  | 250                        |                     | 100                         |                     | ns     |

| SDA/SCL Fall Time                                                               | tF_I2C               |                            | 300                 | 20 + 0.1C <sub>B</sub>      | 300                 | ns     |

| SDA/SCL Rise Time                                                               | t <sub>R_I2C</sub>   |                            | 1000                | 20 + 0.1C <sub>B</sub>      | 300                 | ns     |

| Setup Time for STOP                                                             | tsu:sto              | tHIGH_I2C                  |                     | thigh_i2C                   |                     | μs     |

| Bus-Free Time Between STOP and START                                            | tBUF                 | tLOW_I2C                   |                     | tLOW_I2C                    |                     | μs     |

| Capacitive Load for Each Bus Line                                               | CB                   |                            | 400                 |                             | 400                 | pF     |

| Noise Margin at the Low Level for Each Connected Device (Including Hysteresis)  | V <sub>NL_I2C</sub>  | 0.1 x<br>V <sub>DVDD</sub> |                     | 0.1 x<br>V <sub>D</sub> VDD |                     | V      |

| Noise Margin at the High Level for Each Connected Device (Including Hysteresis) | V <sub>NH</sub> _I2C | 0.2 x<br>V <sub>DVDD</sub> |                     | 0.2 x<br>V <sub>DVDD</sub>  |                     | V      |

### I<sup>2</sup>C BUS CONTROLLER TIMING (ACTING AS I<sup>2</sup>C SLAVE)

| PARAMETER                                                                       | SYMBOL               | STANDA                     | RD MODE             | FAST N                     | IODE                | UNITS |

|---------------------------------------------------------------------------------|----------------------|----------------------------|---------------------|----------------------------|---------------------|-------|

| PARAMETER                                                                       | STIMBUL              | MIN                        | MAX                 | MIN                        | MAX                 | UNITS |

| System Frequency                                                                | fsys                 | 1                          |                     | 3.60                       |                     | MHz   |

| Operating Frequency                                                             | f <sub>I2C</sub>     |                            | f <sub>SYS</sub> /8 |                            | f <sub>SYS</sub> /8 | Hz    |

| System Clock Period                                                             | tsys                 | 1/f <sub>12C</sub>         |                     |                            | 1/f <sub>I2C</sub>  | μs    |

| Hold Time After (Repeated) START                                                | tHD:STA              | 3t <sub>SYS</sub>          |                     | 3t <sub>SYS</sub>          |                     | μs    |

| Clock Low Period                                                                | tLOW_I2C             | 5tsys                      |                     | 5tsys                      |                     | μs    |

| Clock High Period                                                               | tHIGH_I2C            | 3tsys                      |                     | 3tsys                      |                     | μs    |

| Setup Time for Repeated START                                                   | tsu:sta              | 5tsys                      |                     | 5tsys                      |                     | μs    |

| Hold Time for Data                                                              | tHD:DAT              | 0                          | 3.45                | 0                          | 0.9                 | μs    |

| Setup Time for Data                                                             | tsu:dat              | 250                        |                     | 100                        |                     | ns    |

| SDA/SCL Fall Time                                                               | tF_I2C               |                            | 300                 | 20 + 0.1C <sub>B</sub>     | 300                 | ns    |

| SDA/SCL Rise Time                                                               | t <sub>R_I2C</sub>   |                            | 1000                | 20 + 0.1C <sub>B</sub>     | 300                 | ns    |

| Setup Time for STOP                                                             | tsu:sto              | 3tsys                      |                     | 3tsys                      |                     | μs    |

| Bus-Free Time Between STOP and START                                            | tBUF                 | 5tsys                      |                     | 5tsys                      |                     | μs    |

| Capacitive Load for Each Bus Line                                               | CB                   |                            | 400                 |                            | 400                 | pF    |

| Noise Margin at the Low Level for Each Connected Device (Including Hysteresis)  | V <sub>NL_12</sub> C | 0.1 x<br>V <sub>DVDD</sub> |                     | 0.1 x<br>V <sub>DVDD</sub> |                     | V     |

| Noise Margin at the High Level for Each Connected Device (Including Hysteresis) | VNH_I2C              | 0.2 x<br>V <sub>DVDD</sub> |                     | 0.2 x<br>V <sub>DVDD</sub> |                     | V     |

Figure 5. I<sup>2</sup>C Timing Diagram

Figure 6. Single-Ended Unipolar Transfer Function

Figure 7. Differential Bipolar Transfer Function

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                         |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |       | POWER PINS                                                                                                                                                                                                                                                                                       |

| L4  | DVDD  | Digital Supply Voltage                                                                                                                                                                                                                                                                           |

| M5  | DGND  | Digital Ground                                                                                                                                                                                                                                                                                   |

| E4  | AVDD  | Analog Supply Voltage                                                                                                                                                                                                                                                                            |

| B5  | AGND  | Analog Ground                                                                                                                                                                                                                                                                                    |

| K1  | REG18 | Regulator Output. This pin must be connected to ground through a 1.0µF capacitor. It provides the 1.8V internal regulated output. This pin is not meant to provide power externally.                                                                                                             |

|     | •     | ANALOG MEASUREMENT PINS                                                                                                                                                                                                                                                                          |

| G2  | REFA  | Analog Voltage Reference. When using an external reference source, this pin must be connected to 1µF and a 0.01µF filter capacitors in parallel. When using an internal reference source, this pin must be connected to a 0.01µF capacitor. The external reference can only be used for the ADC. |

| A8  | INA+  | Operational Amplifier A Noninverting Input. This analog input pin serves as the operational amplifier A noninverting input.                                                                                                                                                                      |

| В7  | INA-  | Operational Amplifier A Inverting Input. This analog input pin serves as the operational amplifier A inverting input.                                                                                                                                                                            |

| В9  | OUTA  | Operational Amplifier A Output. This analog input pin serves as the operational amplifier A output. This pin is also internally connected to the ADC input mux.                                                                                                                                  |

| D3  | INB+  | Operational Amplifier B Noniverting Input. This analog input pin serves as the operational amplifier B noninverting input.                                                                                                                                                                       |

| A2  | INB-  | Operational Amplifier B Inverting Input. This analog input pin serves as the operational amplifier B inverting input.                                                                                                                                                                            |

| В3  | OUTB  | Operational Amplifier B Output. This analog input pin serves as the operational amplifier B output. This pin is also internally connected to the ADC input mux.                                                                                                                                  |

| E2  | INC+  | Operational Amplifier C Noninverting Input. This analog input pin serves as the operational amplifier C noninverting input.                                                                                                                                                                      |

| C2  | INC-  | Operational Amplifier C Inverting Input. This analog input pin serves as the operational amplifier C inverting input.                                                                                                                                                                            |

| B1  | OUTC  | Operational Amplifier C Output. This analog input pin serves as the operational amplifier C output. This pin is also internally connected to the ADC input mux.                                                                                                                                  |

| F1  | IND+  | Operational Amplifier D Noninverting Input. This analog input pin serves as the operational amplifier A noninverting input.                                                                                                                                                                      |

| F3  | IND-  | Operational Amplifier D Inverting Input. This analog input pin serves as the operational amplifier D inverting input.                                                                                                                                                                            |

| D1  | OUTD  | Operational Amplifier D Output. This analog input pin serves as the operational amplifier D output. This pin is also internally connected to the ADC input mux.                                                                                                                                  |

| H1  | AIN0  | ADC Input 0, 1. These two analog pins function as single-ended ADC inputs or a differential pair.                                                                                                                                                                                                |

| НЗ  | AIN1  | ADO INPULO, 1. Triese two analog pins function as single-ended ADO inputs of a differential pair.                                                                                                                                                                                                |

| C6  | DAC3  | DAC3 Single-Ended Output                                                                                                                                                                                                                                                                         |

| C4  | DAC4  | DAC4 Single-Ended Output                                                                                                                                                                                                                                                                         |

| A6  | SINK1 | Programmable Current Sink 1                                                                                                                                                                                                                                                                      |

| A4  | SINK2 | Programmable Current Sink 2                                                                                                                                                                                                                                                                      |

### Pin Description (continued)

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| C8  | DAC1               | DAC1 Buffer Output. Positive terminal of the differential DAC1's output buffered signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| D7  | DAC2               | DAC2 Buffer Output. Positive terminal of the differential DAC2's output buffered signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| E6  | LIN+               | DAC2 Output. Positive DAC output voltage to drive the left Class D amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| D9  | LIN-               | DAC2 Output. Negative DAC output voltage to drive the left Class D amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| H9  | RIN+               | DAC1 Output. Positive DAC output voltage to drive the right Class D amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| H7  | RIN-               | DAC1 Output. Negative DAC output voltage to drive the right Class D amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|     | RESET PIN          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| N6  | RST                | Digital, Active-Low, Reset Input/Output. The CPU is held in reset when this pin is low and begins executing from the reset vector when released. The pin includes a pullup current source and show be driven by an open-drain external source capable of sinking in excess of 4mA. This pin is driven low as an output when an internal reset condition occurs.                                                                                                                                          |  |  |  |  |  |

|     | 1                  | CLOCK PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| M1  | HFXIN              | High-Frequency Crystal Input. Connect an external crystal or resonator between HFXIN and HFXOUT as the high-frequency system clock. Alternatively, HFXIN is the input for an external high-frequency CMOS clock source when HFXOUT is floating.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| J2  | HFXOUT             | High-Frequency Crystal Output. Connect an external crystal or resonator between HFXIN and HFXOUT as the high-frequency system clock. Alternatively, float HFXOUT when an external high-frequency CMOS clock source is connected to the HFXIN pin.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| F9  | SYNCIN             | SYNCIN Clock. This pin acts as the input clock to the Class D amplifier's sawtooth generator. SYNCIN is a divided system clock with the divide ratio set by programmable bits.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|     |                    | GENERAL-PURPOSE I/O, SPECIAL FUNCTION PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| M9  | P.0.0/INT0/<br>TCK | P0.0 I/O with Interrupt or JTAG Test Clock. This pin defaults as an input with weak pullup after a reset and functions as a general-purpose I/O with interrupt capability. Enabling the pin's special function disables the general-purpose I/O on the pin and makes the pin function as the test clock input. Note that the JTAG function can be disabled using the TAP bit in the SC register.                                                                                                         |  |  |  |  |  |

| L8  | P0.1/INT1/<br>TDI  | P0.1 I/O with Interrupt or JTAG Test Data In. This pin defaults as an input with a weak pullup after a reset and functions as a general-purpose I/O with interrupt capability. Enabling the pin's special function disables the general-purpose I/O on the pin and makes the pin function as the test data input. Note that the JTAG function can be disabled using the TAP bit in the SC register.                                                                                                      |  |  |  |  |  |

| K7  | P0.2/INT2/<br>TMS  | P0.2 I/O with Interrupt or JTAG Test Mode Select. This pin defaults as an input with a weak pullup after a reset and functions as a general-purpose I/O with interrupt capability. Enabling the pin's special function disables the general-purpose I/O on the pin and makes the pin function as the test mode select. Note that the JTAG function can be disabled using the TAP bit in the SC register. The TMS should be gated high when JTAG is disabled.                                             |  |  |  |  |  |

| J6  | P0.3/INT3/<br>TDO  | P0.3 I/O with Interrupt or JTAG Test Data Out. This pin defaults as an input with a weak pullup after a reset and functions as a general-purpose I/O with interrupt capability. The output function of the test data is only enabled during the TAP's Shift_IR or Shift_DR states. Enabling the pin's special function disables the general-purpose I/O on the pin and makes the pin function as the test data output. Note that the JTAG function can be disabled using the TAP bit in the SC register. |  |  |  |  |  |

| N8  | P0.4/INT4/<br>SSEL | P0.4 I/O with Interrupt or SPI Chip Select. This port pin functions as a bidirectional I/O pin with interrupt capability or as the SPI chip select. This port pin defaults to an input with a weak pullup after a reset and functions as a general-purpose I/O. The port pad also contains a Schmitt input circuit.                                                                                                                                                                                      |  |  |  |  |  |

| M7  | P0.5/INT5/<br>SCLK | P0.5 I/O with Interrupt or SPI Clock. This port pin functions as a bidirectional I/O pin with interrupt capability or as the SPI clock. This port pin defaults to an input with a weak pullup after a reset and functions as a general-purpose I/O. The port pad also contains a Schmitt input circuit.                                                                                                                                                                                                  |  |  |  |  |  |

### **Pin Description (continued)**