# COMLINEAR® CLC1606

# 1.3GHz Current Feedback Amplifier

#### **FEATURES**

- 1.2GHz -3dB bandwidth at G=2

- 3,300V/µs slew rate

- 0.01%/0.01° differential gain/ phase error

- 7.5mA supply current

- 875MHz large signal bandwidth

- 120mA output current (easily drives three video loads)

- Fully specified at 5V and ±5V supplies

- CLC1606: Pb-free SOT23-5

- CLC1606: Pb-free SOIC-8

### APPLICATIONS

- RGB video line drivers

- High definition video driver

- Video switchers and routers

- ADC buffer

- Active filters

- High-speed instrumentation

- Wide dynamic range IF amp

## **General Description**

The COMLINEAR CLC1606 is a high-performance, current feedback amplifier with superior bandwith and video specifications. The CLC1606 provides 1.3GHz unity gain bandwidth,  $\pm 0.1 dB$  gain flatness to 150MHz, and provides 3,300V/ $\mu$ s slew rate exceeding the requirements of high-definition television (HDTV) and other multimedia applications. The COMLINEAR CLC1606 high-performance amplifier also provide ample output current to drive multiple video loads.

The COMLINEAR CLC1606 is designed to operate from ±5V or +5V supplies. It consumes only 7.5mA of supply current. The combination of high-speed and excellent video performance make the CLC1606 well suited for use in many general purpose, high-speed applications including standard definition and high definition video. Data communications applications benefit from the CLC1606's total harmonic distortion of -68dBc at 10MHz and fast settling time to 0.1%.

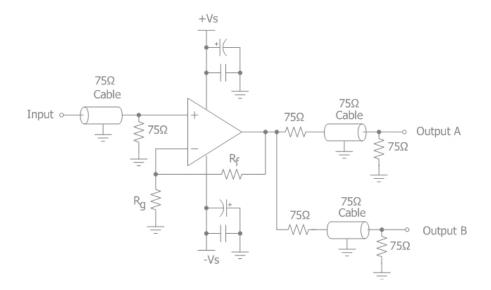

### Typical Application - Driving Dual Video Loads

### Ordering Information

| Part Number  | Package | Pb-Free | RoHS Compliant | Operating Temperature Range | Packaging Method |

|--------------|---------|---------|----------------|-----------------------------|------------------|

| CLC1606IST5X | SOT23-5 | Yes     | Yes            | -40°C to +85°C              | Reel             |

| CLC1606ISO8  | SOIC-8  | Yes     | Yes            | -40°C to +85°C              | Rail             |

| CLC1606ISO8X | SOIC-8  | Yes     | Yes            | -40°C to +85°C              | Reel             |

Moisture sensitivity level for all parts is MSL-1.

©2007-2008 CADEKA Microcircuits LLC www.cadeka.com

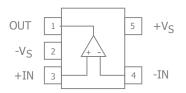

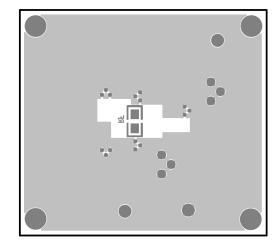

# SOT23-5 Pin Configuration

# SOT23-5 Pin Assignments

| Pin No. | Pin Name        | Description     |

|---------|-----------------|-----------------|

| 1       | OUT             | Output          |

| 2       | -V <sub>S</sub> | Negative supply |

| 3       | +IN             | Positive input  |

| 4       | -IN             | Negative input  |

| 5       | +V <sub>S</sub> | Positive supply |

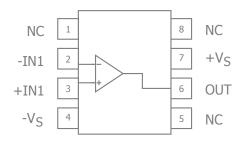

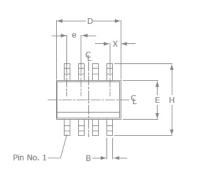

# **SOIC Pin Configuration**

# **SOIC Pin Assignments**

| Pin No. | Pin Name        | Description               |

|---------|-----------------|---------------------------|

| 1       | NC              | No connect                |

| 2       | -IN1            | Negative input, channel 1 |

| 3       | +IN1            | Positive input, channel 1 |

| 4       | -V <sub>S</sub> | Negative supply           |

| 5       | NC              | No connect                |

| 6       | OUT             | Output                    |

| 7       | +V <sub>S</sub> | Positive supply           |

| 8       | NC              | No connect                |

# **Absolute Maximum Ratings**

The safety of the device is not guaranteed when it is operated above the "Absolute Maximum Ratings". The device should not be operated at these "absolute" limits. Adhere to the "Recommended Operating Conditions" for proper device function. The information contained in the Electrical Characteristics tables and Typical Performance plots reflect the operating conditions noted on the tables and plots.

| Parameter                 | Min                   | Max                   | Unit |

|---------------------------|-----------------------|-----------------------|------|

| Supply Voltage            | 0                     | 14                    | V    |

| Input Voltage Range       | -V <sub>S</sub> -0.5V | +V <sub>S</sub> +0.5V | V    |

| Continuous Output Current |                       | 120                   | mA   |

# **Reliability Information**

| Parameter                         | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| Junction Temperature              |     |     | 150 | °C   |

| Storage Temperature Range         | -65 |     | 150 | °C   |

| Lead Temperature (Soldering, 10s) |     |     | 260 | °C   |

| Package Thermal Resistance        |     |     |     |      |

| 5-Lead SOT23                      |     | 221 |     | °C/W |

| 8-Lead SOIC                       |     | 100 |     | °C/W |

Notes:

Package thermal resistance  $(\theta_{JA})$ , JDEC standard, multi-layer test boards, still air.

### **ESD Protection**

| Product                    | SOT23-5 |

|----------------------------|---------|

| Human Body Model (HBM)     | 2kV     |

| Charged Device Model (CDM) | 1kV     |

# **Recommended Operating Conditions**

| Parameter                   | Min | Тур | Max | Unit |

|-----------------------------|-----|-----|-----|------|

| Operating Temperature Range | -40 |     | +85 | °C   |

| Supply Voltage Range        | 4.5 |     | 12  | V    |

©2007-2008 CADEKA Microcircuits LLC

# Electrical Characteristics at +5V

$T_A=25^{\circ}\text{C},\,V_S=+5\text{V},\,R_f=270\Omega,\,R_L=150\Omega$  to  $V_S/2,\,G=2;$  unless otherwise noted.

| Symbol                          | Parameter                          | Conditions                                     | Min | Тур  | Max | Units  |

|---------------------------------|------------------------------------|------------------------------------------------|-----|------|-----|--------|

| Frequency Do                    | omain Response                     |                                                |     |      |     |        |

| UGBW                            | -3dB Bandwidth                     | $G = +1, R_f = 390\Omega, V_{OUT} = 0.5V_{pp}$ |     | 1000 |     | MHz    |

| BW <sub>SS</sub>                | -3dB Bandwidth                     | $G = +2$ , $V_{OUT} = 0.5V_{DD}$               |     | 900  |     | MHz    |

| BW <sub>LS</sub>                | Large Signal Bandwidth             | $G = +2$ , $V_{OUT} = 1V_{pp}$                 |     | 800  |     | MHz    |

| BW <sub>0.1dBSS</sub>           | 0.1dB Gain Flatness                | $G = +2$ , $V_{OUT} = 0.5V_{pp}$               |     | 132  |     | MHz    |

| BW <sub>0.1dBLS</sub>           | 0.1dB Gain Flatness                | $G = +2$ , $V_{OUT} = 1V_{pp}$                 |     | 140  |     | MHz    |

| Time Domain                     | Response                           |                                                |     |      |     |        |

| t <sub>R</sub> , t <sub>F</sub> | Rise and Fall Time                 | V <sub>OUT</sub> = 1V step; (10% to 90%)       |     | 0.6  |     | ns     |

| t <sub>S</sub>                  | Settling Time to 0.1%              | V <sub>OUT</sub> = 1V step                     |     | 10   |     | ns     |

| OS                              | Overshoot                          | V <sub>OUT</sub> = 0.2V step                   |     | 1    |     | %      |

| SR                              | Slew Rate                          | 1V step                                        |     | 1500 |     | V/µs   |

| Distortion/No                   | ise Response                       | ,                                              |     | '    |     |        |

| HD2                             | 2nd Harmonic Distortion            | 1V <sub>pp</sub> , 5MHz                        |     | -74  |     | dBc    |

| HD3                             | 3rd Harmonic Distortion            | 1V <sub>pp</sub> , 5MHz                        |     | -70  |     | dBc    |

| THD                             | Total Harmonic Distortion          | 1V <sub>pp</sub> , 5MHz                        |     | 68   |     | dB     |

| IP3                             | Third-Order Intercept              | 1V <sub>pp</sub> , 10MHz                       |     | 36   |     | dBm    |

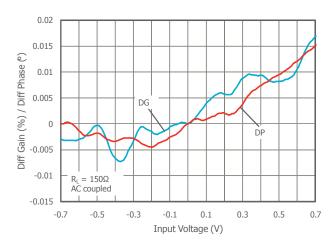

| $D_G$                           | Differential Gain                  | NTSC (3.58MHz), AC-coupled, $R_1 = 150\Omega$  |     | 0.01 |     | %      |

| D <sub>P</sub>                  | Differential Phase                 | NTSC (3.58MHz), AC-coupled, $R_L = 150\Omega$  |     | 0.01 |     | 0      |

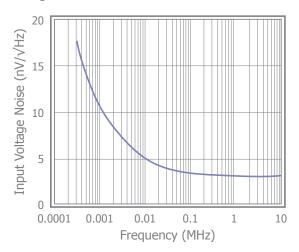

| e <sub>n</sub>                  | Input Voltage Noise                | > 1MHz                                         |     | 3    |     | nV/√Hz |

|                                 | _                                  | > 1MHz, Inverting                              |     | 20   |     | pA/√Hz |

| i <sub>ni</sub>                 | Input Current Noise                | > 1MHz, Non-inverting                          |     | 30   |     | pA/√Hz |

| DC Performa                     | nce                                |                                                |     | -    |     |        |

| V <sub>IO</sub>                 | Input Offset Voltage               |                                                |     | 0    |     | mV     |

| dV <sub>IO</sub>                | Average Drift                      |                                                |     | 3.7  |     | μV/°C  |

| I <sub>bn</sub>                 | Input Bias Current - Non-Inverting |                                                |     | ±3.0 |     | μA     |

| dI <sub>bn</sub>                | Average Drift                      |                                                |     | 100  |     | nA/°C  |

| I <sub>bi</sub>                 | Input Bias Current - Inverting     |                                                |     | ±6.0 |     | μΑ     |

| dI <sub>bi</sub>                | Average Drift                      |                                                |     | 56   |     | nA/°C  |

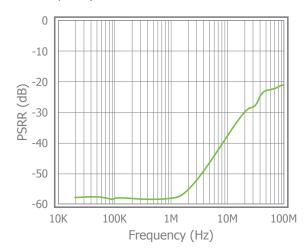

| PSRR                            | Power Supply Rejection Ratio       | DC                                             |     | 55   |     | dB     |

| I <sub>S</sub>                  | Supply Current                     |                                                |     | 6.5  |     | mA     |

| Input Charac                    | teristics                          |                                                |     |      |     |        |

| _                               |                                    | Non-inverting                                  |     | 150  |     | kΩ     |

| $R_{IN}$                        | Input Resistance                   | Inverting                                      |     | 70   |     | Ω      |

| C <sub>IN</sub>                 | Input Capacitance                  |                                                |     | 1.0  |     | pF     |

| CMIR                            | Common Mode Input Range            |                                                |     | ±1.5 |     | V      |

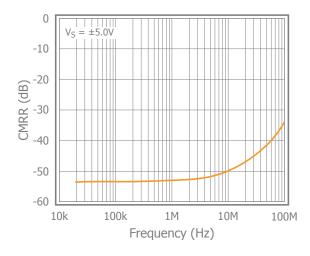

| CMRR                            | Common Mode Rejection Ratio        | DC                                             |     | 50   |     | dB     |

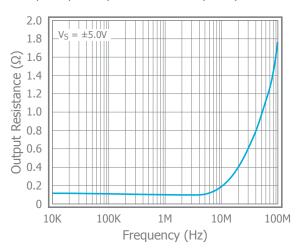

| Output Chara                    | -                                  |                                                |     |      |     |        |

| R <sub>O</sub>                  | Output Resistance                  | Closed Loop, DC                                |     | 0.1  |     | Ω      |

| V <sub>OUT</sub>                | Output Voltage Swing               | $R_{I} = 150\Omega$                            |     | ±1.5 |     | V      |

| I <sub>OUT</sub>                | Output Current                     | 14 - 12035                                     |     | ±120 |     | mA     |

©2007-2008 CADEKA Microcircuits LLC

# Electrical Characteristics at ±5V

$T_A=25^{\circ}\text{C},\,V_S=\pm5\text{V},\,R_f=270\Omega,\,R_L=150\Omega,\,G=2;$  unless otherwise noted.

| Symbol                          | Parameter                              | Conditions                                           | Min  | Тур  | Max | Units  |

|---------------------------------|----------------------------------------|------------------------------------------------------|------|------|-----|--------|

| Frequency D                     | omain Response                         |                                                      |      |      |     |        |

| UGBW                            | -3dB Bandwidth                         | $G = +1$ , $R_f = 390\Omega$ , $V_{OUT} = 0.5V_{pp}$ |      | 1300 |     | MHz    |

| BW <sub>SS</sub>                | -3dB Bandwidth                         | $G = +2$ , $V_{OUT} = 0.5V_{pp}$                     |      | 1200 |     | MHz    |

| BW <sub>LS</sub>                | Large Signal Bandwidth                 | $G = +2$ , $V_{OUT} = 2V_{pp}$                       |      | 875  |     | MHz    |

| BW <sub>0.1dBSS</sub>           | 0.1dB Gain Flatness                    | $G = +2$ , $V_{OUT} = 0.5V_{pp}$                     |      | 150  |     | MHz    |

| BW <sub>0.1dBLS</sub>           | 0.1dB Gain Flatness                    | $G = +2$ , $V_{OUT} = 2V_{pp}$                       |      | 150  |     | MHz    |

| Time Domai                      | n Response                             |                                                      | ·    |      |     |        |

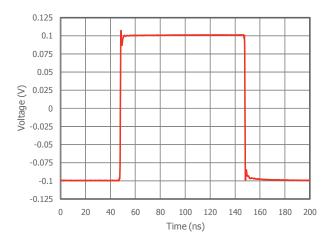

| t <sub>R</sub> , t <sub>F</sub> | Rise and Fall Time                     | V <sub>OUT</sub> = 2V step; (10% to 90%)             |      | 0.5  |     | ns     |

| t <sub>S</sub>                  | Settling Time to 0.1%                  | V <sub>OUT</sub> = 2V step                           |      | 13   |     | ns     |

| OS                              | Overshoot                              | V <sub>OUT</sub> = 0.2V step                         |      | 1    |     | %      |

| SR                              | Slew Rate                              | 2V step                                              |      | 3300 |     | V/µs   |

| Distortion/N                    | oise Response                          |                                                      |      |      | ,   |        |

| HD2                             | 2nd Harmonic Distortion                | 2V <sub>pp</sub> , 5MHz                              |      | -71  |     | dBc    |

| HD3                             | 3rd Harmonic Distortion                | 2V <sub>pp</sub> , 5MHz                              |      | -71  |     | dBc    |

| THD                             | Total Harmonic Distortion              | 2V <sub>pp</sub> , 5MHz                              |      | -68  |     | dB     |

| IP3                             | Third-Order Intercept                  | 2V <sub>pp</sub> , 10MHz                             |      | 39   |     | dBm    |

| $D_G$                           | Differential Gain                      | NTSC (3.58MHz), AC-coupled, $R_L = 150\Omega$        |      | 0.01 |     | %      |

| D <sub>P</sub>                  | Differential Phase                     | NTSC (3.58MHz), AC-coupled, $R_L = 150\Omega$        |      | 0.01 |     | 0      |

| e <sub>n</sub>                  | Input Voltage Noise                    | > 1MHz                                               |      | 3    |     | nV/√Hz |

|                                 |                                        | > 1MHz, Inverting                                    |      | 20   |     | pA/√Hz |

| i <sub>ni</sub>                 | Input Current Noise - Inverting        | > 1MHz, Non-inverting                                |      | 30   |     | pA/√Hz |

| DC Performa                     | ance                                   |                                                      |      |      | ,   |        |

| V <sub>IO</sub>                 | Input Offset Voltage(1)                |                                                      | -10  | 0.5  | 10  | mV     |

| dV <sub>IO</sub>                | Average Drift                          |                                                      |      | 3.7  |     | μV/°C  |

| I <sub>bn</sub>                 | Input Bias Current - Non-Inverting (1) |                                                      | -45  | ±3.0 | 45  | μA     |

| dI <sub>bn</sub>                | Average Drift                          |                                                      |      | 100  |     | nA/°C  |

| I <sub>bi</sub>                 | Input Bias Current - Inverting (1)     |                                                      | -50  | ±7.0 | 50  | μΑ     |

| dI <sub>bi</sub>                | Average Drift                          |                                                      |      | 56   |     | nA/°C  |

| PSRR                            | Power Supply Rejection Ratio (1)       | DC                                                   | 40   | 50   |     | dB     |

| I <sub>S</sub>                  | Supply Current (1)                     |                                                      |      | 7.5  | 9.5 | mA     |

| Input Charac                    | cteristics                             |                                                      |      |      |     |        |

| Б                               | Total Budden                           | Non-inverting                                        |      | 150  |     | kΩ     |

| R <sub>IN</sub>                 | Input Resistance                       | Inverting                                            |      | 170  |     | k      |

| C <sub>IN</sub>                 | Input Capacitance                      |                                                      |      | 1.0  |     | pF     |

| CMIR                            | Common Mode Input Range                |                                                      |      | ±4.0 |     | V      |

| CMRR                            | Common Mode Rejection Ratio (1)        | DC                                                   | 40   | 50   |     | dB     |

| Output Char                     | -                                      |                                                      |      |      |     |        |

| R <sub>O</sub>                  | Output Resistance                      | Closed Loop, DC                                      |      | 0.1  |     | Ω      |

| V <sub>OUT</sub>                | Output Voltage Swing                   | $R_{L} = 150\Omega^{(1)}$                            | ±3.0 | ±3.7 |     | V      |

| I <sub>OUT</sub>                | Output Current                         |                                                      | 1    | ±280 |     | mA     |

| -001                            |                                        |                                                      |      |      | l   |        |

#### Notes:

1. 100% tested at 25°C

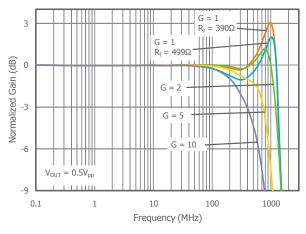

## **Typical Performance Characteristics**

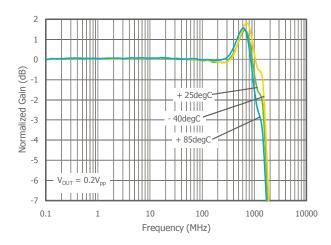

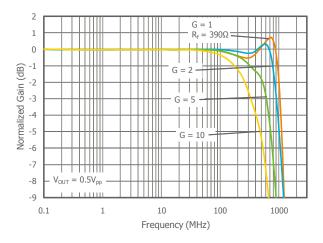

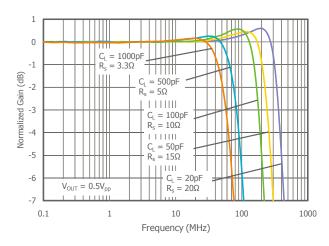

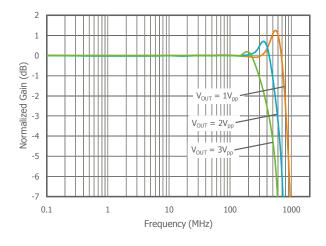

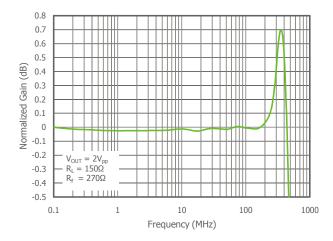

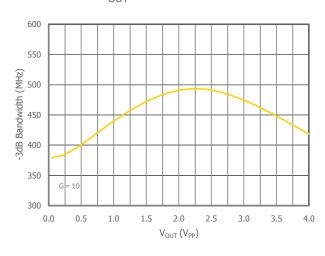

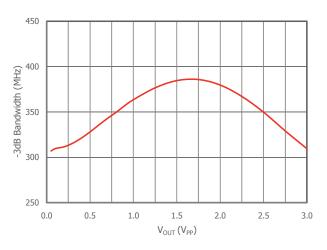

$T_A = 25$ °C,  $V_S = \pm 5V$ ,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

### Non-Inverting Frequency Response

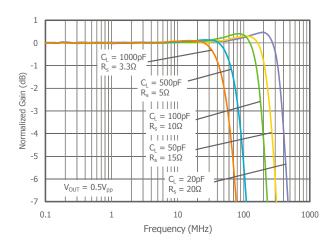

# Frequency Response vs. C<sub>I</sub>

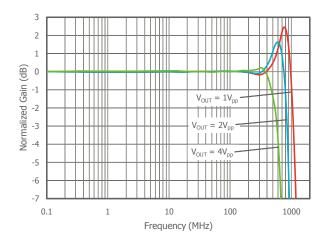

### Frequency Response vs. V<sub>OUT</sub>

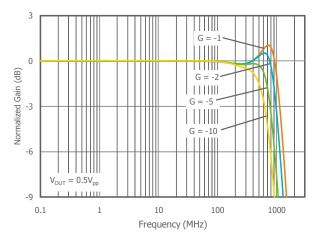

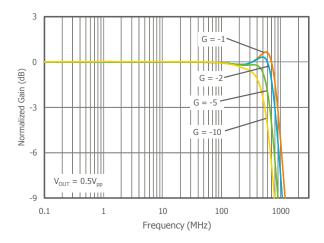

### **Inverting Frequency Response**

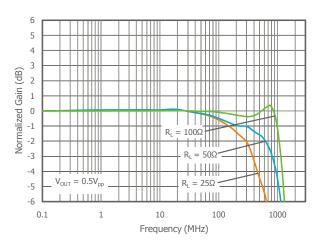

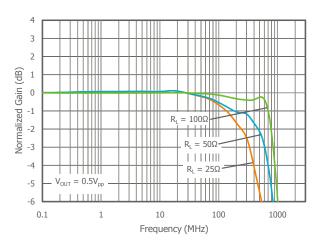

### Frequency Response vs. R<sub>L</sub>

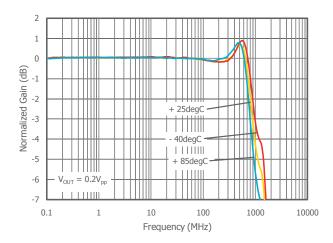

### Frequency Response vs. Temperature

# **Typical Performance Characteristics**

$T_A = 25$ °C,  $V_S = \pm 5V$ ,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

Non-Inverting Frequency Response at  $V_S = 5V$

Frequency Response vs.  $C_L$  at  $V_S = 5V$

Frequency Response vs.  $V_{OUT}$  at  $V_S = 5V$

Inverting Frequency Response at  $V_S = 5V$

Frequency Response vs.  $R_L$  at  $V_S = 5V$

Frequency Response vs. Temperature at  $V_S = 5V$

$T_A = 25$ °C,  $V_S = \pm 5V$ ,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

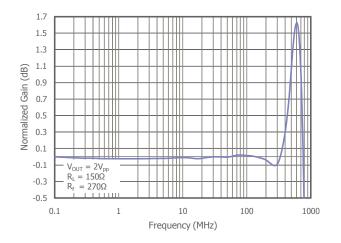

### **Gain Flatness**

Gain Flatness at  $V_S = 5V$

-3dB Bandwidth vs.  $V_{OUT}$  at G=10

-3dB Bandwidth vs.  $V_{OUT}$  at G=10,  $V_S=5V$

Closed Loop Output Impedance vs. Frequency

Input Voltage Noise

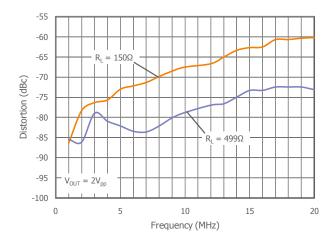

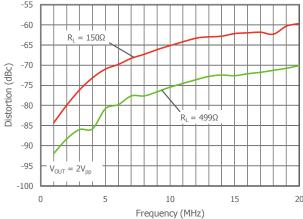

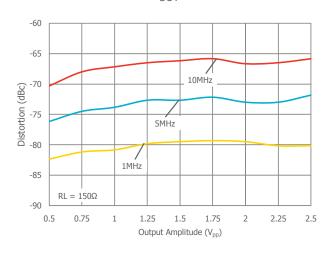

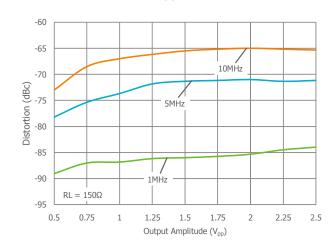

$T_A = 25$ °C,  $V_S = \pm 5V$ ,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

### 2nd Harmonic Distortion vs. $R_L$

# 3rd Harmonic Distortion vs. R<sub>L</sub>

# 2nd Harmonic Distortion vs. $V_{OUT}$

3rd Harmonic Distortion vs. V<sub>OUT</sub>

### CMRR vs. Frequency

PSRR vs. Frequency

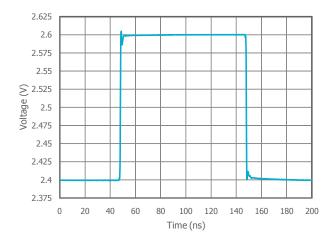

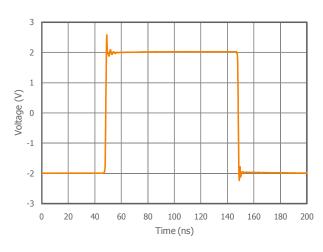

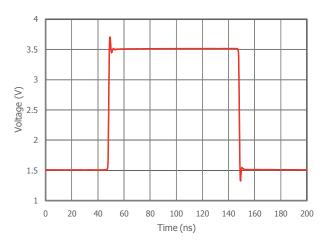

$T_A = 25$ °C,  $V_S = \pm 5V$ ,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

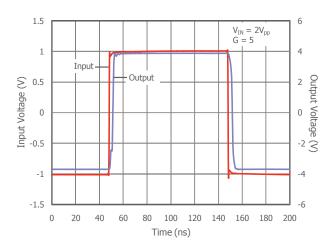

### Small Signal Pulse Response

### Small Signal Pulse Response at $V_S = 5V$

### Large Signal Pulse Response

Large Signal Pulse Response at  $V_S = 5V$

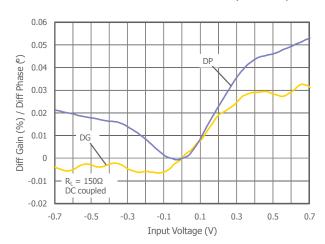

### Differential Gain & Phase AC Coupled Output

Differential Gain & Phase DC Coupled Output

$T_A = 25$ °C,  $V_S = \pm 5$ V,  $R_f = 270\Omega$ ,  $R_L = 150\Omega$ , G = 2; unless otherwise noted.

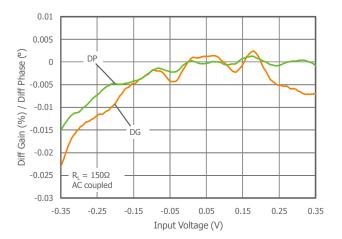

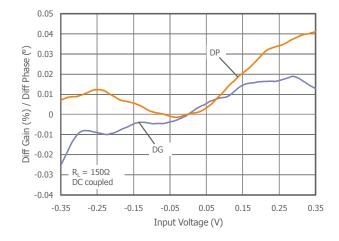

Differential Gain & Phase AC Coupled Output at  $V_S = \pm 2.5V$

Differential Gain & Phase DC Coupled at  $V_S = \pm 2.5V$

# General Information - Current Feedback Technology

### Advantages of CFB Technology

The CLC1606 Family of amplifiers utilize current feedback (CFB) technology to achieve superior performance. The primary advantage of CFB technology is higher slew rate performance when compared to voltage feedback (VFB) architecture. High slew rate contributes directly to better large signal pulse response, full power bandwidth, and distortion.

CFB also alleviates the traditional trade-off between closed loop gain and usable bandwidth that is seen with a VFB amplifier. With CFB, the bandwidth is primarily determined by the value of the feedback resistor,  $R_{\rm f}$ . By using optimum feedback resistor values, the bandwidth of a CFB amplifier remains nearly constant with different gain configurations.

When designing with CFB amplifiers always abide by these basic rules:

- Use the recommended feedback resistor value

- Do not use reactive (capacitors, diodes, inductors, etc.) elements in the direct feedback path

- Avoid stray or parasitic capacitance across feedback resistors

- Follow general high-speed amplifier layout guidelines

- Ensure proper precautions have been made for driving capacitive loads

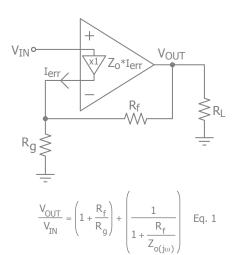

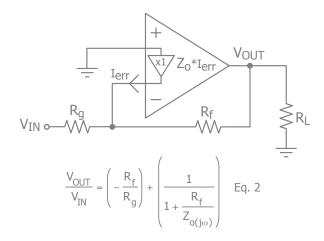

Figure 1. Non-Inverting Gain Configuration with First Order Transfer Function

Figure 2. Inverting Gain Configuration with First Order

Transfer Function

### CFB Technology - Theory of Operation

Figure 1 shows a simple representation of a current feedback amplifier that is configured in the traditional noninverting gain configuration.

Instead of having two high-impedance inputs similar to a VFB amplifier, the inputs of a CFB amplifier are connected across a unity gain buffer. This buffer has a high impedance input and a low impedance output. It can source or sink current ( $I_{err}$ ) as needed to force the non-inverting input to track the value of Vin. The CFB architecture employs a high gain trans-impedance stage that senses Ierr and drives the output to a value of ( $Z_{o}(j\omega) * I_{err}$ ) volts. With the application of negative feedback, the amplifier will drive the output to a voltage in a manner which tries to drive Ierr to zero. In practice, primarily due to limitations on the value of  $Z_{o}(j\omega)$ , Ierr remains a small but finite value.

A closer look at the closed loop transfer function (Eq.1) shows the effect of the trans-impedance,  $Z_0(j\omega)$  on the gain of the circuit. At low frequencies where  $Z_0(j\omega)$  is very large with respect to  $R_f$ , the second term of the equation approaches unity, allowing  $R_f$  and  $R_g$  to set the gain. At higher frequencies, the value of  $Z_0(j\omega)$  will roll off, and the effect of the secondary term will begin to dominate. The -3dB small signal parameter specifies the frequency where the value  $Z_0(j\omega)$  equals the value of  $R_f$  causing the gain to drop by 0.707 of the value at DC.

For more information regarding current feedback amplifiers, visit <a href="www.cadeka.com">www.cadeka.com</a> for detailed application notes, such as AN-3: The Ins and Outs of Current Feedback Amplifiers.

### **Application Information**

#### **Basic Operation**

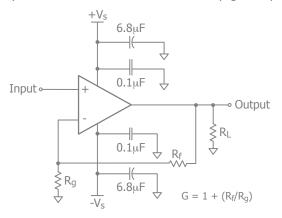

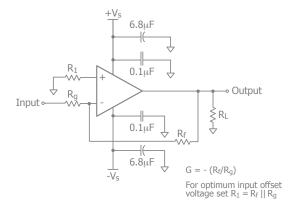

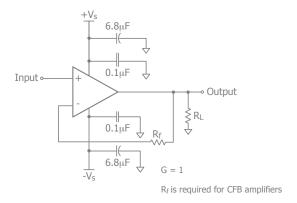

Figures 3, 4, and 5 illustrate typical circuit configurations for non-inverting, inverting, and unity gain topologies for dual supply applications. They show the recommended bypass capacitor values and overall closed loop gain equations.

Figure 3. Typical Non-Inverting Gain Circuit

Figure 4. Typical Inverting Gain Circuit

Figure 5. Typical Unity Gain (G=1) Circuit

CFB amplifiers can be used in unity gain configurations. Do not use the traditional voltage follower circuit, where the output is tied directly to the inverting input. With a CFB amplifier, a feedback resistor of appropriate value must be used to prevent unstable behavior. Refer to figure 5 and Table 1. Although this seems cumbersome, it does allow a degree of freedom to adjust the passband characteristics.

#### **Feedback Resistor Selection**

One of the key design considerations when using a CFB amplifier is the selection of the feedback resistor,  $R_f$ .  $R_f$  is used in conjunction with  $R_g$  to set the gain in the traditional non-inverting and inverting circuit configurations. Refer to figures 3 and 4. As discussed in the Current Feedback Technology section, the value of the feedback resistor has a pronounced effect on the frequency response of the circuit.

Table 1, provides recommended  $R_f$  and associated  $R_g$  values for various gain settings. These values produce the optimum frequency response, maximum bandwidth with minimum peaking. Adjust these values to optimize performance for a specific application. The typical performance characteristics section includes plots that illustrate how the bandwidth is directly affected by the value of  $R_f$  at various gain settings.

| Gain<br>(V/V | R <sub>f</sub> (Ω) | R <sub>g</sub> (Ω) | ±0.1dB BW<br>(MHz) | -3dB BW<br>(MHz) |

|--------------|--------------------|--------------------|--------------------|------------------|

| 1            | 390                | -                  | 136                | 1300             |

| 2            | 270                | 270                | 150                | 1200             |

| 5            | 270                | 67.5               | 115                | 750              |

Table 1: Recommended R<sub>f</sub> vs. Gain

In general, lowering the value of  $R_f$  from the recommended value will extend the bandwidth at the expense of additional high frequency gain peaking. This will cause increased overshoot and ringing in the pulse response characteristics. Reducing  $R_f$  too much will eventually cause oscillatory behavior.

Increasing the value of  $R_f$  will lower the bandwidth. Lowering the bandwidth creates a flatter frequency response and improves 0.1dB bandwidth performance. This is important in applications such as video. Further increase in  $R_f$  will cause premature gain rolloff and adversely affect gain flatness.

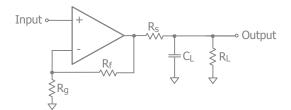

#### **Driving Capacitive Loads**

Increased phase delay at the output due to capacitive loading can cause ringing, peaking in the frequency response, and possible unstable behavior. Use a series resistance, R<sub>S</sub>, between the amplifier and the load to help improve stability and settling performance. Refer to Figure 6.

Figure 6. Addition of R<sub>S</sub> for Driving Capacitive Loads

Table 2 provides the recommended  $R_{\rm S}$  for various capacitive loads. The recommended  $R_{\rm S}$  values result in <=0.5dB peaking in the frequency response. The Frequency Response vs.  $C_{\rm L}$  plot, on page 5, illustrates the response of the CLC1606 Family.

| C <sub>L</sub> (pF) | R <sub>S</sub> (Ω) | -3dB BW (MHz) |

|---------------------|--------------------|---------------|

| 20                  | 20                 | 375           |

| 100                 | 10                 | 180           |

| 1000                | 3.3                | 58            |

Table 1: Recommended R<sub>S</sub> vs. C<sub>I</sub>

For a given load capacitance, adjust  $R_S$  to optimize the tradeoff between settling time and bandwidth. In general, reducing  $R_S$  will increase bandwidth at the expense of additional overshoot and ringing.

#### Parasitic Capacitance on the Inverting Input

Physical connections between components create unintentional or parasitic resistive, capacitive, and inductive elements.

Parasitic capacitance at the inverting input can be especially troublesome with high frequency amplifiers. A parasitic capacitance on this node will be in parallel with the gain setting resistor  $R_g.$  At high frequencies, its impedance can begin to raise the system gain by making  $R_g$  appear smaller.

In general, avoid adding any additional parasitic capacitance at this node. In addition, stray capacitance across the  $R_f$  resistor can induce peaking and high frequency

ringing. Refer to the **Layout Considerations** section for additional information regarding high speed layout techniques.

### Overdrive Recovery

An overdrive condition is defined as the point when either one of the inputs or the output exceed their specified voltage range. Overdrive recovery is the time needed for the amplifier to return to its normal or linear operating point. The recovery time varies, based on whether the input or output is overdriven and by how much the range is exceeded. The CLC1606 Family will typically recover in less than 10ns from an overdrive condition. Figure 7 shows the CLC1606 in an overdriven condition.

Figure 7. Overdrive Recovery

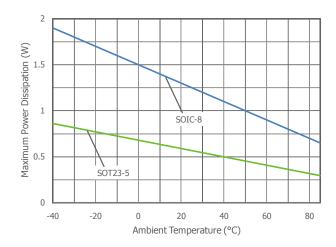

### **Power Dissipation**

Power dissipation should not be a factor when operating under the stated 1000 ohm load condition. However, applications with low impedance, DC coupled loads should be analyzed to ensure that maximum allowed junction temperature is not exceeded. Guidelines listed below can be used to verify that the particular application will not cause the device to operate beyond it's intended operating range.

Maximum power levels are set by the absolute maximum junction rating of 150°C. To calculate the junction temperature, the package thermal resistance value Theta $_{JA}$  ( $\Theta_{JA}$ ) is used along with the total die power dissipation.

$$T_{Junction} = T_{Ambient} + (\Theta_{JA} \times P_D)$$

Where T<sub>Ambient</sub> is the temperature of the working environment.

Where I Ambient is the temperature of the working environment.

In order to determine  $P_D$ , the power dissipated in the load needs to be subtracted from the total power delivered by the supplies.

$$P_D = P_{supply} - P_{load}$$

Supply power is calculated by the standard power equation.

$$P_{\text{supply}} = V_{\text{supply}} \times I_{\text{RMS supply}}$$

$$V_{\text{supply}} = V_{S+} - V_{S-}$$

Power delivered to a purely resistive load is:

$$P_{load} = ((V_{LOAD})_{RMS^2})/Rload_{eff}$$

The effective load resistor (Rload<sub>eff</sub>) will need to include the effect of the feedback network. For instance,

Rload<sub>eff</sub> in figure 3 would be calculated as:

$$R_L \mid\mid (R_f + R_q)$$

These measurements are basic and are relatively easy to perform with standard lab equipment. For design purposes however, prior knowledge of actual signal levels and load impedance is needed to determine the dissipated power. Here,  $P_D$  can be found from

$$P_D = P_{Quiescent} + P_{Dynamic} - P_{Load}$$

Quiescent power can be derived from the specified  $I_S$  values along with known supply voltage,  $V_{Supply}$ . Load power can be calculated as above with the desired signal amplitudes using:

$$(V_{IOAD})_{RMS} = V_{PFAK} / \sqrt{2}$$

$$(I_{LOAD})_{RMS} = (V_{LOAD})_{RMS} / Rload_{eff}$$

The dynamic power is focused primarily within the output stage driving the load. This value can be calculated as:

$$P_{DYNAMIC} = (V_{S+} - V_{LOAD})_{RMS} \times (I_{LOAD})_{RMS}$$

Assuming the load is referenced in the middle of the power rails or  $V_{\text{supply}}/2$ .

Figure 8 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 8 and 14 lead SOIC packages.

Figure 8. Maximum Power Derating

Better thermal ratings can be achieved by maximizing PC board metallization at the package pins. However, be careful of stray capacitance on the input pins.

In addition, increased airflow across the package can also help to reduce the effective  $\Theta_{JA}$  of the package.

In the event the outputs are momentarily shorted to a low impedance path, internal circuitry and output metallization are set to limit and handle up to 65mA of output current. However, extended duration under these conditions may not guarantee that the maximum junction temperature  $(+150^{\circ}\text{C})$  is not exceeded.

### **Layout Considerations**

General layout and supply bypassing play major roles in high frequency performance. CADEKA has evaluation boards to use as a guide for high frequency layout and as aid in device testing and characterization. Follow the steps below as a basis for high frequency layout:

- $\bullet$  Include 6.8µF and 0.1µF ceramic capacitors for power supply decoupling

- Place the 6.8µF capacitor within 0.75 inches of the power pin

- Place the 0.1µF capacitor within 0.1 inches of the power pin

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitance

- Minimize all trace lengths to reduce series inductances

Refer to the evaluation board layouts below for more information.

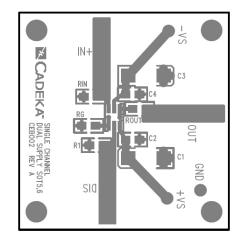

### **Evaluation Board Information**

The following evaluation boards are available to aid in the testing and layout of these devices:

| Evaluation Board | Products     |

|------------------|--------------|

| CEB002           | CLC1606IST5X |

| CEB003           | CLC1606ISO8X |

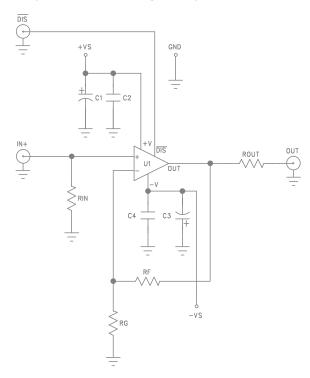

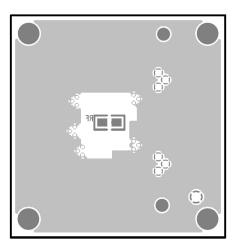

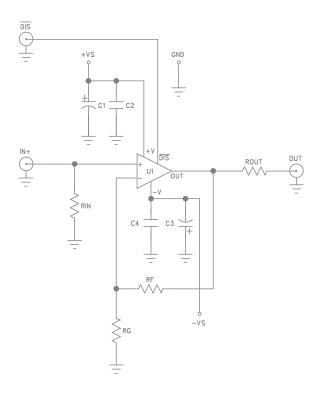

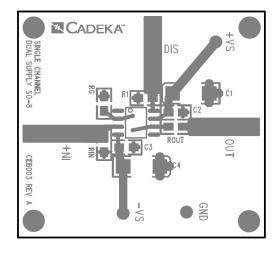

### **Evaluation Board Schematics**

Evaluation board schematics and layouts are shown in Figures 9-14. These evaluation boards are built for dual- supply operation. Follow these steps to use the board in a single-supply application:

- 1. Short -Vs to ground.

- 2. Use C3 and C4, if the  $\text{-V}_{\text{S}}$  pin of the amplifier is not directly connected to the ground plane.

Figure 9. CEB002 Schematic

Figure 10. CEB002 Top View

Figure 11. CEB002 Bottom View

Figure 12. CEB003 Schematic

Figure 13. CEB003 Top View

Figure 14. CEB003 Bottom View

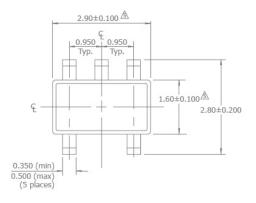

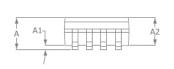

## **Mechanical Dimensions**

### SOT23-5 Package

#### NOTES:

- 1. Dimensions and tolerances are as per ANSI Y14.5M-1982.

- 2. Package surface to be matte finish VDI 11~13.

- 3. Die is facing up for mold. Die is facing down for trim/form, ie. reverse trim/form.

- 4. The footlength measuring is based on the guage plane method.

- △ Dimension are exclusive of mold flash and gate burr.

- ▲ Dimension are exclusive of solder plating.

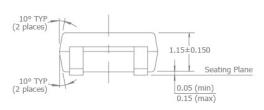

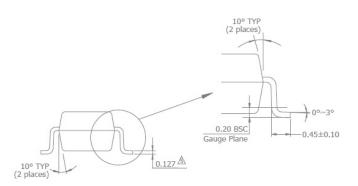

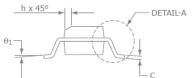

#### SOIC-8 Package

| SOIC-8 |          |      |

|--------|----------|------|

| SYMBOL | MIN      | MAX  |

| A1     | 0.10     | 0.25 |

| В      | 0.36     | 0.48 |

| С      | 0.19     | 0.25 |

| D      | 4.80     | 4.98 |

| Е      | 3.81     | 3.99 |

| е      | 1.27 BSC |      |

| Н      | 5.80     | 6.20 |

| h      | 0.25     | 0.5  |

| L      | 0.41     | 1.27 |

| Α      | 1.37     | 1.73 |

| θ1     | 00       | 80   |

| X      | 0.55 ref |      |

| θ2     | 7° BSC   |      |

#### NOTE:

- All dimensions are in millimeters.

- 2. Lead coplanarity should be 0 to 0.1mm (0.004") max.

- 3. Package surface finishing: VDI 24~27

- All dimension excluding mold flashes.

- 5. The lead width, B to be determined at 0.1905mm from the lead tip.

#### For additional information regarding our products, please visit CADEKA at: cadeka.com

CADEKA Headquarters Loveland, Colorado

T: 970.663.5452

T: 877.663.5452 (toll free)

CADEKA, the CADEKA logo design, COMLINEAR, the COMLINEAR logo design, and ARCTIC are trademarks or registered trademarks of CADEKA Microcircuits LLC. All other brand and product names may be trademarks of their respective companies.

CADEKA reserves the right to make changes to any products and services herein at any time without notice. CADEKA does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by CADEKA; nor does the purchase, lease, or use of a product or service from CADEKA convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of CADEKA or of third parties.