### 1. General description

The TDA9951 is a single-chip Consumer Electronics Control (CEC) to I<sup>2</sup>C-bus translator dedicated to the control and interfacing Consumer Electronics products. The built-in processor simplifies Consumer Electronics (CE) product CPU design by managing a range of interfacing and control functions including the CEC protocol, timings and interrupts. Designed as an I<sup>2</sup>C-bus slave device the TDA9951 enables control of these features to any I<sup>2</sup>C-bus master device such as the CE host processor.

This data sheet describes the  $I^2$ C-bus interface, together with the control and management features of the TDA9951. The TDA9951 is an enhancement of the TDA9950.

### 2. Features

- CEC support:

- Receive and transmit messages using compliant signal free time handling

- Up to 16 bytes message length

- Multiple logical addresses

- Comprehensive arbitration and collision handling

- Dedicated processor control of CEC-line and I<sup>2</sup>C-bus interface utilizing embedded software

- I<sup>2</sup>C-bus interface to host communication in Standard mode (100 kbit/s) and Fast mode (400 kbit/s)

- Automatic Idle mode reduces power consumption if no messages are on CEC-line and I<sup>2</sup>C-bus plus

- Managed Standby and Wake-up power modes

- Active LOW reset input and on-chip Power-On Reset (POR) enables operation without external reset components

- Reset counter and reset glitch circuitry prevents false and incomplete resets

- Programmable on-chip retry counter

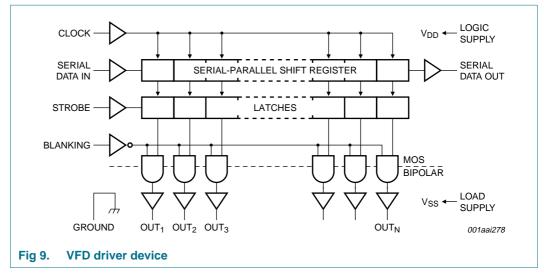

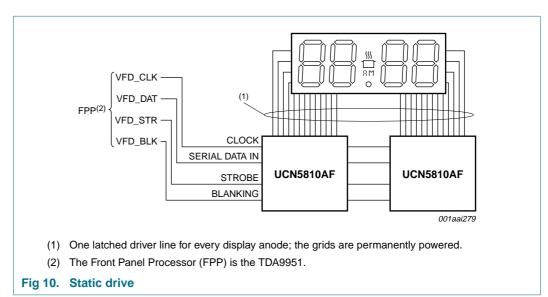

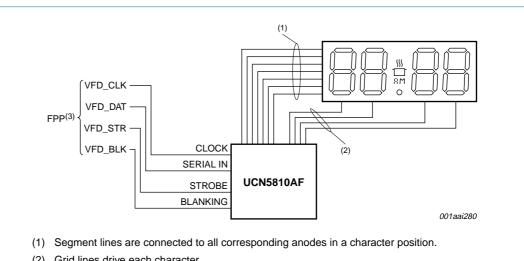

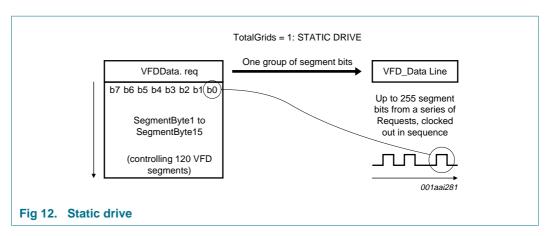

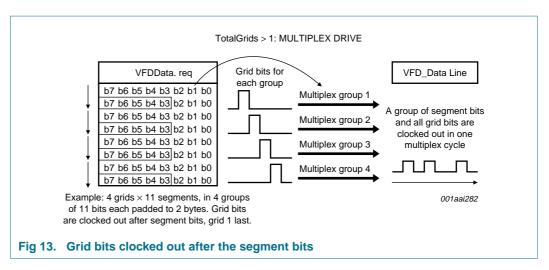

- Controls specific Vacuum Fluorescent Display (VFD) devices and/or up to four LEDs

- Decode up to 10 panel switches

- Decode infrared protocol RC5, RC5 enlarged and RC6 Mode 0

- Battery operation detection maintains clock and calendar in low power mode

- Provides real-time clock features including time-of-day alarm and periodic timer

- V<sub>DD</sub> operating range 3.0 V to 3.6 V

- 5 V tolerant input/output pins

- On-chip oscillator for a 12 MHz crystal

- Schmitt trigger port inputs

### 3. Applications

- All devices using an HDMI connector

- Sector Content of the sector o

- Projector, plasma and LCD TV

- Rear-projection TV

- High-end TV

- Home-theater amplifier

- DVD recorder

### 4. Quick reference data

| Table 1.                                             | Quick reference data    |                                                                    |     |     |     |      |  |  |

|------------------------------------------------------|-------------------------|--------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol                                               | Parameter               | Conditions                                                         | Min | Тур | Max | Unit |  |  |

| V <sub>DD</sub>                                      | supply voltage          |                                                                    | 2.4 | 3.0 | 3.6 | V    |  |  |

| T <sub>amb</sub>                                     | ambient temperature     |                                                                    | -40 | -   | +85 | °C   |  |  |

| P <sub>tot</sub>                                     | total power dissipation | based on package heat<br>transfer, not device power<br>consumption | -   | -   | 1.5 | W    |  |  |

| I <sup>2</sup> C-bus: pins SDA and SCL; 5 V tolerant |                         |                                                                    |     |     |     |      |  |  |

| f <sub>clk</sub>                                     | clock frequency         | Standard mode                                                      | -   | -   | 100 | kHz  |  |  |

|                                                      |                         | Fast mode                                                          | -   | -   | 400 | kHz  |  |  |

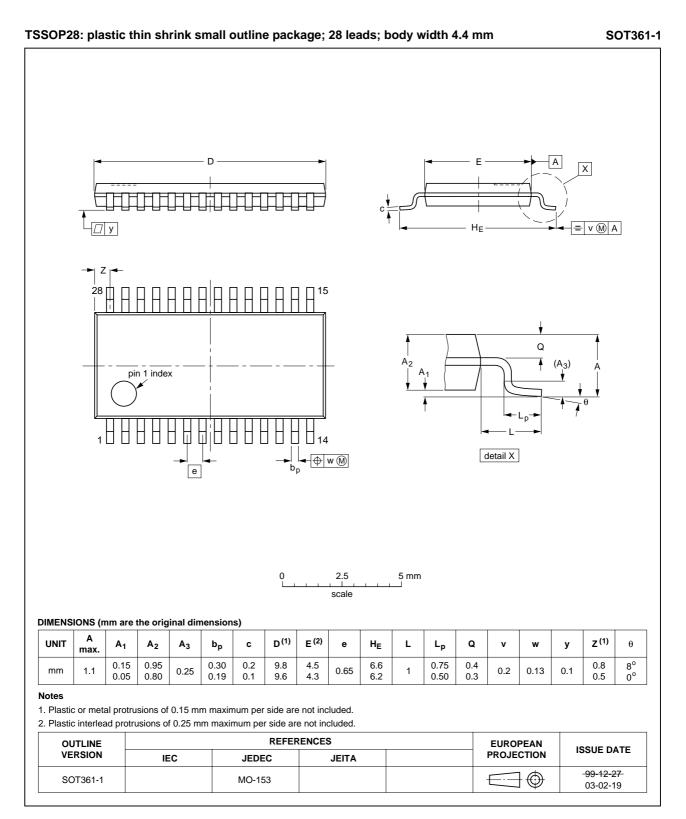

### 5. Ordering information

| Table 2.         Ordering information |         |                                                                        |          |  |  |  |  |

|---------------------------------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|

| Type number                           | Package |                                                                        |          |  |  |  |  |

|                                       | Name    | Description                                                            | Version  |  |  |  |  |

| TDA9951TT                             | TSSOP28 | plastic thin shrink small outline package; 28 leads; body width 4.4 mm | SOT361-1 |  |  |  |  |

**TDA9951**

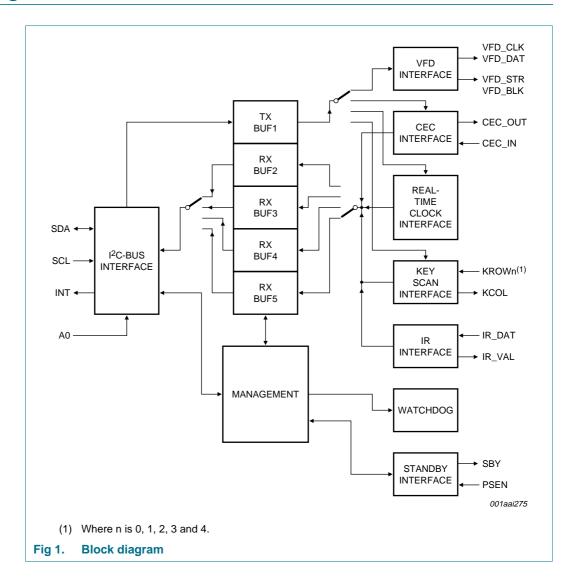

### 6. Block diagram

**TDA9951**

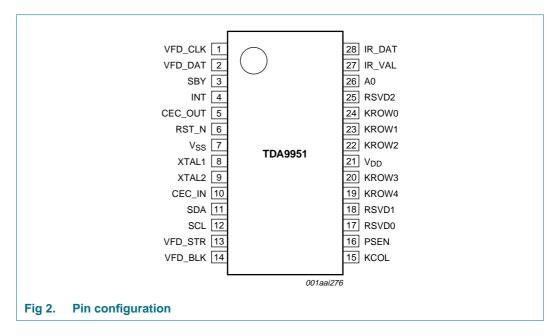

### 7. Pinning information

### 7.1 Pinning

#### 7.2 Pin description

| Table 3.        | Pin desc | ription               |                                                                                                                                                                                                         |

|-----------------|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Pin      | Type <mark>[1]</mark> | Description                                                                                                                                                                                             |

| VFD_CLK         | 1        | 0                     | pulsed HIGH to clock output of the VFD display driver                                                                                                                                                   |

| VFD_DAT         | 2        | 0                     | data output to the VFD display driver                                                                                                                                                                   |

| SBY             | 3        | 0                     | power control output to the host processor.                                                                                                                                                             |

|                 |          |                       | Operating mode = LOW-level                                                                                                                                                                              |

|                 |          |                       | Standby mode = HIGH-level                                                                                                                                                                               |

| INT             | 4        | 0                     | interrupt line to the host processor. Indicates data is available for reading. The polarity of operation is configured using the common configuration register; default is INT_POL bit = 1, active-HIGH |

| CEC_OUT         | 5        | 0                     | output to the CEC interface <sup>[2]</sup>                                                                                                                                                              |

| RST_N           | 6        | I                     | external reset input. Holding this input LOW resets the TDA9951. It must be held LOW for a time after power-up when using an 18 MHz crystal <sup>[2]</sup> .                                            |

| V <sub>SS</sub> | 7        | GND                   | ground; 0 V reference                                                                                                                                                                                   |

| XTAL1           | 8        | I                     | input to the oscillator and internal clock generator circuits (18 MHz crystal) <sup>[2]</sup>                                                                                                           |

| XTAL2           | 9        | 0                     | output from the oscillator amplifier                                                                                                                                                                    |

| CEC_IN          | 10       | I                     | input from the CEC interface <sup>[2]</sup>                                                                                                                                                             |

| SDA             | 11       | I/O                   | I <sup>2</sup> C-bus serial data input/output <sup>[2]</sup>                                                                                                                                            |

| SCL             | 12       | I                     | I <sup>2</sup> C-bus serial clock input <sup>[2]</sup>                                                                                                                                                  |

| Table 3.        | Pin desc | riptionc              | ontinued                                                                                                                                        |

|-----------------|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Pin      | Type <mark>[1]</mark> | Description                                                                                                                                     |

| VFD_STR         | 13       | 0                     | VFD strobe line. Pulsed HIGH latches clocked output at the VFD driver                                                                           |

| VFD_BLK         | 14       | 0                     | VFD blank line. Default HIGH blanks output at the VFD display driver. The polarity is configurable using the I <sup>2</sup> C-bus               |

| KCOL            | 15       | 0                     | key matrix column output <sup>[2]</sup>                                                                                                         |

| PSEN            | 16       | I                     | power sense input detects power supply type.                                                                                                    |

|                 |          |                       | LOW-level = battery                                                                                                                             |

|                 |          |                       | HIGH-level = main power                                                                                                                         |

| RSVD0           | 17       | I                     | reserved pin; connect to ground                                                                                                                 |

| RSVD1           | 18       | 0                     | reserved pin                                                                                                                                    |

| KROW4           | 19       | I                     | key matrix row input <sup>[2]</sup>                                                                                                             |

| KROW3           | 20       | I                     | key matrix row input <sup>[2]</sup>                                                                                                             |

| V <sub>DD</sub> | 21       | Р                     | power supply voltage                                                                                                                            |

| KROW2           | 22       | I                     | key matrix row input <sup>[2]</sup>                                                                                                             |

| KROW1           | 23       | I                     | key matrix row input <sup>[2]</sup>                                                                                                             |

| KROW0           | 24       | I                     | key matrix row input <sup>[2]</sup>                                                                                                             |

| RSVD2           | 25       | 0                     | reserved pin                                                                                                                                    |

| A0              | 26       | I                     | I <sup>2</sup> C-bus slave address bit. This pin configures the least significant bit A0 of the I <sup>2</sup> C-bus slave address; connect to: |

|                 |          |                       | V <sub>DD</sub> (HIGH) sets A0 to logic 1 (address 35h)                                                                                         |

|                 |          |                       | V <sub>SS</sub> (LOW) sets A0 to logic 0 (address 34h)                                                                                          |

| IR_VAL          | 27       | 0                     | pulse LOW for 65 ms after every valid IR frame is received, to indicate activity using an LED                                                   |

| IR_DAT          | 28       | I                     | input from external infrared demodulator.                                                                                                       |

|                 |          |                       | LOW-level = active IR pulse,                                                                                                                    |

|                 |          |                       | HIGH-level = no IR pulse (a space)                                                                                                              |

[1] P = power supply, I = input, O = output and I/O = Input and Output.

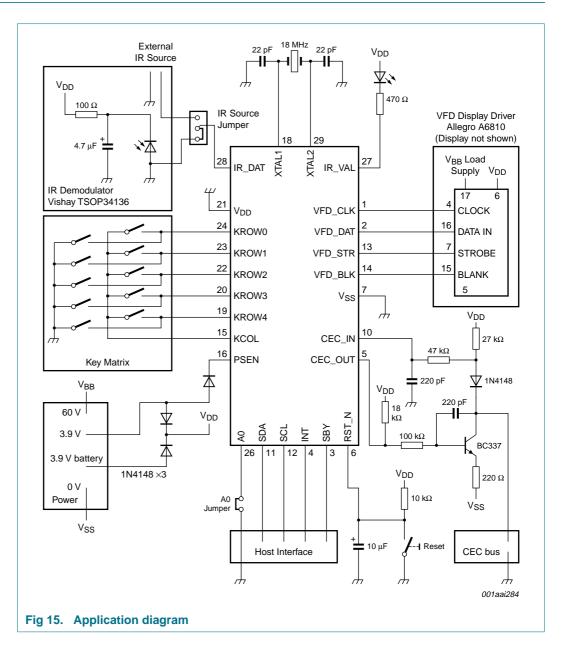

[2] See Figure 15 "Application diagram" on page 35.

### 8. Functional description

The TDA9951 controls the interface between the CEC-line and the I<sup>2</sup>C-bus using its internal processor and embedded software.

#### 8.1 Device addressing

The SDA and SCL pins are managed by the I<sup>2</sup>C-bus peripheral which automatically communicates in Standard mode (100 kbit/s) or Fast mode (400 kbit/s) as an I<sup>2</sup>C-bus slave.

The TDA9951 signals the host processor that data is ready by asserting the INT output. The polarity is configurable using the INT\_POL bit in the CCONR register (see Table 14).

The seven-bit I<sup>2</sup>C-bus slave address is hard-coded as 34h and can be changed to 35h by setting the pin A0, as shown in <u>Table 3</u> and <u>Table 4</u>. This enables two TDA9951 to be connected to the same host using the addresses 34h and 35h. Alternatively, changing the address enables one TDA9951 to avoid address clashes with other I<sup>2</sup>C-bus slaves.

| Table 4. | I <sup>2</sup> C-bus sla | ave address |   |   |   |   |    |     |  |

|----------|--------------------------|-------------|---|---|---|---|----|-----|--|

| Bit      | 7                        | 6           | 5 | 4 | 3 | 2 | 1  | 0   |  |

| Value    | 0                        | 1           | 1 | 0 | 1 | 0 | A0 | R/W |  |

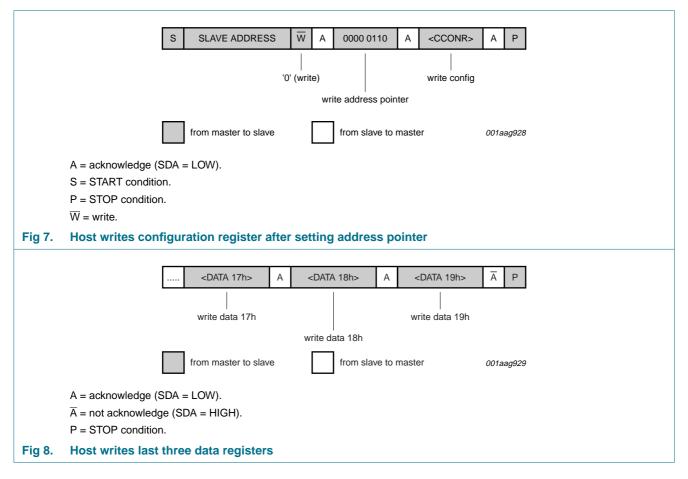

### 8.2 Configuring the TDA9951

The TDA9951 is controlled using a series of registers.

|          | r o negloter ooningaration    |            |            |           |

|----------|-------------------------------|------------|------------|-----------|

| Register | Description                   | Address    | Read/Write | Reference |

| APR      | Address Pointer Register      | 00h        | W          | Table 6   |

| CSR      | Common Status Register        | 00h        | R          | Table 7   |

| CER      | Common Error Register         | 01h        | R          | Table 8   |

| CVR      | Common Version Register       | 02h        | R          | Table 9   |

| CCR      | Common Control Register       | 03h        | R/W        | Table 10  |

| ACKH     | CEC Address ACK High register | 04h        | R/W        | Table 11  |

| ACKL     | CEC Address ACK Low register  | 05h        | R/W        | Table 12  |

| CCONR    | Common Configuration Register | 06h        | R/W        | Table 14  |

| CDR      | Common Data Registers         | 07h to 19h | R/W        | Table 15  |

|          |                               |            |            |           |

#### Table 5. I<sup>2</sup>C Register configuration

The first byte of any I<sup>2</sup>C-bus write frame configures the address pointer register APR. This determines the TDA9951 register accessed by the next I<sup>2</sup>C-bus read or write.

If for example, a read is carried out without first writing to the address pointer register, the register returned is the register that address pointer register was last set to. The address pointer auto-increments after each successful read or write for all address pointer values other than 00h. When the address pointer register is set 00h, the common status register is polled using successive reads without needing to reset the address pointer register each time.

When the address pointer register is set higher than 07h, this is treated as setting it to 07h. This is because all message data transfers must start from register 07h and continue by auto-incrementing in one contiguous transfer.

When the host writes to two or more non-contiguous registers, two separate write sequences are used with either a STOP/START sequence or repeated START between them.

Before a read takes place, the host must first write to the address pointer register (if required) and then, repeat the START condition or STOP/START sequence. Finally, it starts reading data bytes until the read sequence is complete.

#### 8.3 Using the INT line

The TDA9951 is an I<sup>2</sup>C-bus slave device and when data is ready to be read, it uses the INT output line to signal the host processor. The common configuration register INT\_POL bit sets the operating polarity of the INT line. When the INT line is active, it matches the state of the INT\_POL bit. The INT line state is updated in the common status register making it possible to poll the register instead of monitoring the INT line. This method is less efficient consequently, it is not recommended. The common status register INT indication is not affected by the common configuration register INT\_POL bit.

### 8.4 Register descriptions

| Table 6 | Table 6.         APR - Address pointer register (address 00h) bit description |        |       |                                                                                                             |  |  |

|---------|-------------------------------------------------------------------------------|--------|-------|-------------------------------------------------------------------------------------------------------------|--|--|

| Bit     | Symbol                                                                        | Access | Value | Description                                                                                                 |  |  |

| 7 to 5  | reserved                                                                      | W      | 000   | reserved                                                                                                    |  |  |

| 4 to 0  | REG_PTR[4:0]                                                                  | W      | -     | address pointer: Address of the register to be read/written in the next I <sup>2</sup> C-bus communication. |  |  |

#### Table 7. CSR - Common status register (address 00h) bit description

|        |        |        | •     |                                                                 |

|--------|--------|--------|-------|-----------------------------------------------------------------|

| Bit    | Symbol | Access | Value | Description                                                     |

| 7      | BUSY   | R      | 0     | default; requests accepted                                      |

|        |        |        | 1     | busy; cannot accept further requests                            |

| 6      | INT    | R      | 0     | default; INT interrupt output is inactive                       |

|        |        |        | 1     | the INT interrupt output is active                              |

| 5      | 5 ERR  | R      | 0     | default; no error                                               |

|        |        |        | 1     | an error occurred; cleared on reading the common error register |

| 4      | SBY    | R      | 0     | default; the SBY (standby) output pin is<br>inactive LOW        |

|        |        |        | 1     | the SBY output pin is HIGH                                      |

| 3      | PSEN   |        | 0     | the PSEN input pin is LOW                                       |

|        |        |        | 1     | the PSEN input pin is HIGH                                      |

| 2 to 0 |        |        | 000   | not used (must be set to 000)                                   |

Table 8. CER - Common error register (address 01h) bit description

| Bit               | Symbol   | Access | Value                             | Description                                                                                                                    |

|-------------------|----------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 CER[7:0] R | CER[7:0] | R      |                                   | This register contains details of the last error.<br>Reading this register resets the ERR bit in the<br>common status register |

|                   |          | 00h    | no error has occurred since reset |                                                                                                                                |

|                   |          | 01h    | a watchdog reset has occurred     |                                                                                                                                |

|                   |          |        | 02h                               | a long CEC message with no End Of Message (EOM) was detected                                                                   |

|                   |          |        | 03h                               | CEC input has overrun. No buffer was available to hold new data                                                                |

This register enables the host processor to read the TDA9951 software version.

| Table 0  |                | and the second states of the |              | A left of a solution the second |

|----------|----------------|------------------------------|--------------|---------------------------------|

| Table 9. | CVR - Common v | version register (           | (address uzn | ) bit description               |

| Bit    | Symbol       | Access | Value | Description   |

|--------|--------------|--------|-------|---------------|

| 7 to 4 | CVR_MAJ[3:0] | R      | -     | major version |

| 3 to 0 | CVR_MIN[3:0] | R      | -     | minor version |

| D''   |          | • · · · · |                                                                                                                                                                                                                        |                                                                                                                                                                                                   |

|-------|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Symbol   | Access    | Value                                                                                                                                                                                                                  | Description                                                                                                                                                                                       |

| 7     | RESET    | R/W       | 0                                                                                                                                                                                                                      | no action                                                                                                                                                                                         |

|       |          | W         | 1                                                                                                                                                                                                                      | resets the TDA9951 and returns it to its power-up<br>state. CEC transmissions are completed before the<br>reset. Only performed when the TDA9951 is in Idle<br>mode, restores all default values. |

| 6 CEC | R/W      | 0         | default; the CEC interface is disabled after<br>completion or reception of a pending CEC<br>transmission. Further messages on the CEC line<br>and messages for transmission are no longer<br>acknowledged or accepted. |                                                                                                                                                                                                   |

|       |          | 1         | The CEC interface is enabled and acknowledges messages based on the contents of the CEC address ACK high and address ACK low registers.                                                                                |                                                                                                                                                                                                   |

| 5     | 5 RC5    | R/W       | 0                                                                                                                                                                                                                      | default; ignores RC5 commands from the IRX interface                                                                                                                                              |

|       |          |           | 1                                                                                                                                                                                                                      | accepts RC5 commands                                                                                                                                                                              |

| 4     | RC6      | R/W       | 0                                                                                                                                                                                                                      | default; ignores RC6 commands from the IRX interface                                                                                                                                              |

|       |          |           | 1                                                                                                                                                                                                                      | accepts RC6 commands                                                                                                                                                                              |

| 3     | KEY      | R/W       | 0                                                                                                                                                                                                                      | default; key matrix is disabled                                                                                                                                                                   |

|       |          |           | 1                                                                                                                                                                                                                      | key matrix is enabled                                                                                                                                                                             |

| 2     | VFD      | R/W       | 0                                                                                                                                                                                                                      | default; VFD display output is disabled                                                                                                                                                           |

|       |          |           | 1                                                                                                                                                                                                                      | VFD display output is enabled                                                                                                                                                                     |

| 1     | not used | -         | 0                                                                                                                                                                                                                      | not used                                                                                                                                                                                          |

| 0     | SBY      | R/W       | 1                                                                                                                                                                                                                      | enters Standby mode and sets the SBY output. This<br>bit is then cleared automatically. The common status<br>register SBY bit indicates the SBY output state                                      |

|       |          |           |                                                                                                                                                                                                                        |                                                                                                                                                                                                   |

| Table 10. | CCR - Common control register (address 03h) bit description |

|-----------|-------------------------------------------------------------|

|           |                                                             |

| Table 11. | ACKH - CEC address ACK high register (address 04h) bit description | on |

|-----------|--------------------------------------------------------------------|----|

|           |                                                                    |    |

| Bit    | Symbol    | Access | Value | Description                                         |

|--------|-----------|--------|-------|-----------------------------------------------------|

| 7      | reserved  | R      | 0     | reserved; must be set to 0                          |

| 6 to 0 | ACKH[6:0] | R/W    |       | for each bit:                                       |

|        |           |        | 0     | messages are not acknowledged                       |

|        |           |        | 1     | messages are acknowledged and forwarded to the host |

| Bit    | Symbol   | Access | Value | Description                                         |  |

|--------|----------|--------|-------|-----------------------------------------------------|--|

| 7 to 0 | reserved | R/W    |       | for each bit:                                       |  |

|        |          |        | 0     | messages are not acknowledged                       |  |

|        |          |        | 1     | messages are acknowledged and forwarded to the host |  |

#### Table 12. ACKL - CEC address ACK low register (address 05h) bit description

Using ACKH and ACKL, each bit of ADDR[14:0] corresponds to a CEC logical address. CEC reserves ADDR[15] as a broadcast address. ADDR[14:0] is built-up from ACKH[6:0] and ACKL[7:0].

#### Table 13. ADDR[14:0] definition

| Bit  | 7       | 6        | 5        | 4        | 3        | 2        | 1       | 0       |

|------|---------|----------|----------|----------|----------|----------|---------|---------|

| ACKH | -       | ADDR[14] | ADDR[13] | ADDR[12] | ADDR[11] | ADDR[10] | ADDR[9] | ADDR[8] |

| ACKL | ADDR[7] | ADDR[6]  | ADDR[5]  | ADDR[4]  | ADDR[3]  | ADDR[2]  | ADDR[1] | ADDR[0] |

#### Table 14. CCONR - Common configuration register (address 06h) bit description

| Bit    | Symbol           | Access | Value                    | Description                                                                                                           |  |

|--------|------------------|--------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 7 to 5 | not used         | R      | 000 not used; set to 000 |                                                                                                                       |  |

| 4      | ENABLE_<br>ERROR | R/W    |                          | controls how the TDA9951 notifies the host processor of errors:                                                       |  |

|        |                  |        | 0                        | default; errors are not reported using the TDA9951 Data.err service or common error register                          |  |

|        |                  |        | 1                        | errors reported using the TDA9951 Data.err service or common error register                                           |  |

| 3      | INT_POL          |        |                          | sets the polarity of the INT output when it is active:                                                                |  |

|        |                  |        | 0                        | default; the I2C_INT output is active-LOW                                                                             |  |

|        |                  |        | 1                        | the I2C_INT output is active-HIGH                                                                                     |  |

| 2 to 0 | RETRY[2:0]       | R/W    |                          | these bits set the CEC retry count used by the TDA9951. The maximum value is 5; values greater than 5 give 5 retries: |  |

|        |                  |        | 0 to 4                   | valid retry count                                                                                                     |  |

|        |                  |        | 5                        | default; maximum valid retry count                                                                                    |  |

|        |                  |        | 6 to 7                   | accepted as 5 retries                                                                                                 |  |

Communication between the TDA9951 and the host processor for the data registers is carried out using information frames transferred using the common data register subaddress range 07h to 19h. The common data registers CDR0 to CDR18 are described in detail in Section 8.5.

#### 8.5 Data register protocol

Before a frame is read or written, the host processor must set the REG\_PTR field in the address pointer register to the base data register address. Message transfers can only start from the first data register at address 07h. They must not start from higher addresses because message transfer must be in complete sequences and not in fragments.

Each frame consists of a byte count, service selector, followed by zero or more parameters as shown in Figure 3.

TDA9951

| Register 07h   | Register 08h    | Register 09h | [] | [] |

|----------------|-----------------|--------------|----|----|

| FrameByteCount | ServiceSelector | [Parameter]  | [] | [] |

#### Fig 3. Frame format for the data register protocol

The FrameByteCount is the number of bytes in the frame (including the FrameByteCount itself).

The service is specified by the ServiceSelector (see <u>Table 15</u>). If an unused ServiceSelector is sent to the TDA9951, it responds with the confirm Bad.req service (see <u>Table 17</u>, <u>Table 28</u>, <u>Table 32</u> and <u>Table 36</u>).

The remaining bytes of the frame can contain up to 17 parameters associated with the service. Services do not have optional parameters. The TDA9951 only accepts one outstanding request.

The data service provided using the common data registers comprises:

- Host to the TDA9951: requests.

- A request is sent from the host to the TDA9951 or to a device on one of its interfaces.

- TDA9951 to the host: confirmations, indications and errors.

- Confirmations are used to answer requests for status and flow control, to show if the request has been passed on to the intended recipient or if it has been accepted/rejected.

- Indications are messages from the TDA9951 interface to the host. Generally relating to normal operation.

- Errors are messages from a TDA9951 to the host. Generally relating to an error state.

<u>Table 15</u> lists the data services and their ServiceSelector values. The contents of each service is described in detail in the following Protocol Layer sections.

| ServiceSelector | Host to TDA9951 | TDA9951 to host | Message type             |

|-----------------|-----------------|-----------------|--------------------------|

| 00h             | CECData.req     |                 | request                  |

| 01h             |                 | CECData.cnf     | confirmation             |

| 02h             | VFDData.req     |                 | request                  |

| 03h             |                 | VFDData.cnf     | confirmation             |

| 04h             | RTCData.req     |                 | request                  |

| 05h             |                 | RTCData.cnf     | confirmation             |

| 06h             | SBYData.req     |                 | request                  |

| 07h             |                 | SBYData.cnf     | confirmation             |

| 08h             | KEYData.req     |                 | request                  |

| 09h             |                 | KEYData.cnf     | confirmation             |

| 81h             |                 | CECData.ind     | CEC indication, no error |

#### Table 15. Data services

Table 15.

Data services ...continued

| ServiceSelector | Host to TDA9951 | TDA9951 to host | Message type                    |

|-----------------|-----------------|-----------------|---------------------------------|

| 82h             |                 | CECData.err     | no indication, error            |

| 83h             |                 | CECData.ier     | indication and error            |

| 84h             |                 | RTCData.ind     | RTC alarm indication, no error  |

| 85h             |                 | IRData.ind      | IR command indication, no error |

| 86h             |                 | KEYData.ind     | KEY indication, no error        |

#### 8.5.1 CECData.req service

This CECData.req request service is sent from the host to the TDA9951 instructing it to transmit an addressed or broadcast message. If the correct signal free time rules are met, transmission of the CEC message starts as soon as the complete message is received by the TDA9951. Table 16 shows the frame byte for the service.

#### Table 16. Frame Bytes for CECData.req service

| Register   | Frame Byte      | Value      | Comments                                                          |

|------------|-----------------|------------|-------------------------------------------------------------------|

| 07h        | FrameByteCount  | 03h to 18h |                                                                   |

| 08h        | ServiceSelector | 00h        | CECData.req                                                       |

| 09h        | AddressByte     | -          | source and destination logical addresses in the format: SSSS DDDD |

| 0Ah to 18h | DataBytes       | -          | zero to fifteen bytes up to the FrameByteCount – 3 data length    |

#### 8.5.2 CECData.cnf service

Using this service the TDA9951 informs the host of the success or failure of a CECData.req service. The frame bytes are shown in Table 17.

#### Table 17. Frame Bytes for CECData.cnf service

| Register | Frame Byte      | Value | Comments                                          |

|----------|-----------------|-------|---------------------------------------------------|

| 07h      | FrameByteCount  | 03h   |                                                   |

| 08h      | ServiceSelector | 01h   | CECData.cnf                                       |

| 09h      | ResultCode      |       | a value indicating the result of the transmission |

|          |                 | 00h   | success                                           |

|          |                 | 80h   | CEC in off-state                                  |

|          |                 | 81h   | Bad.req service                                   |

|          |                 | 82h   | failed; unable to access CEC line                 |

|          |                 | 83h   | failed; arbitration error                         |

|          |                 | 84h   | failed; bit timing error                          |

|          |                 | 85h   | failed; destination address not acknowledged      |

|          |                 | 86h   | failed; data byte not acknowledged                |

TDA9951 1

#### 8.5.3 CECData.ind service

Using this service the TDA9951 transfers a CEC indication message to the host which was received from another remote device. The frame bytes are shown in Table 18.

| Table 18. | Frame B | tes for | <b>CECData.ind</b> | service |

|-----------|---------|---------|--------------------|---------|

|-----------|---------|---------|--------------------|---------|

| Register   | Frame Byte      | Value      | Comments                                                          |  |  |  |  |  |

|------------|-----------------|------------|-------------------------------------------------------------------|--|--|--|--|--|

| 07h        | FrameByteCount  | 03h to 12h |                                                                   |  |  |  |  |  |

| 08h        | ServiceSelector | 81h        | CECData.ind                                                       |  |  |  |  |  |

| 09h        | AddressByte     | -          | source and destination logical addresses in the format: SSSS DDDD |  |  |  |  |  |

| 0Ah to 18h | DataBytes       | -          | zero to fifteen bytes up to the FrameByteCount – 3 data length    |  |  |  |  |  |

#### 8.5.4 CECData.err service

Using this service, the TDA9951 alerts the host to a CEC error condition. There are no parameters. The host should read the Common Error Register (CER) for details of the error. Only active when bit 4 of the Common Configuration Register (CCONR) is set to enable error indications. The frame bytes for the service are shown in Table 19.

#### Table 19. Frame Bytes for CECData.err service

| Register | Frame Byte      | Value | Comments    |

|----------|-----------------|-------|-------------|

| 07h      | FrameByteCount  | 02h   |             |

| 08h      | ServiceSelector | 82h   | CECData.err |

#### 8.5.5 CECData.ier service

Using this service, the TDA9951 transfers a CEC message to the host which was received from another remote device. In addition, it alerts the host to a CEC error condition. The host should read the TDA9951 Common Error Register (CER) for details of the error. Only active when bit 4 of the CEC Common Configuration Register (CCONR) is set to enable error indications. The frame bytes are listed in Table 20.

| Register   | Frame Byte      | Value      | Comments                                                          |  |  |  |  |

|------------|-----------------|------------|-------------------------------------------------------------------|--|--|--|--|

| 07h        | FrameByteCount  | 03h to 13h |                                                                   |  |  |  |  |

| 08h        | ServiceSelector | 83h        | CECData.ier                                                       |  |  |  |  |

| 09h        | AddressByte     | -          | source and destination logical addresses in the format: SSSS DDDD |  |  |  |  |

| 0Ah to 19h | DataBytes       | -          | zero to sixteen bytes up to the<br>FrameByteCount – 3 data length |  |  |  |  |

#### Table 20. Frame Bytes for CECData.ier service

TDA9951 1

#### 8.6 Example communication sequences

#### 8.6.1 Notes on writing the CEC common data registers

Common data registers should be written in one contiguous operation between a START and STOP condition. The write action starts from the first data register and includes all registers indicated by the contents of that data register. The length of the message is given by the byte in the first data register. This is at least three for the shortest message. Lower values than three indicate an invalid message.

Data registers ignore data in the following cases:

- When fewer data registers are written than the number indicated by the first data register. The partial message is ignored and a confirmation is not returned.

- When more data registers are written than the number indicated by the first data register. The message is processed once the message's last data register is written but the extra bytes written are ignored.

- When the highest data register is written and more message bytes are indicated by the first data register. The message is processed once the highest data register is written but the extra bytes written are ignored.

#### 8.6.2 Notes on reading the CEC common data registers

Data registers should be read in one contiguous operation, starting from the first data register up to the last register indicated by the Data register.

The data registers can only contain valid messages when the INT line and the INT bit in the TDA9951 status register are set.

Typical read situations:

- When data registers are read and the INT line is not set, the first data register contains 0 (no bytes to read). Any additional read sequences before a STOP condition return the value FFh.

- When the host writes to data registers and starts reading without first resetting the address pointer register, the read sequence commences from the first data register.

- When reading stops before all indicated data registers are read, the TDA9951 resets the INT line, ignores the message and the message is lost.

- When reading continues for more data registers than indicated by the first data register, the value FFh is read. The INT line is reset when the last valid data register for the message is read.

TDA9951

CEC/I<sup>2</sup>C-bus translator

### 8.6.3 Communication use cases

|        | S SLAVE AD                                                                                                                      | DRES                                 | s w                            | A 00                                 | 00 0000     | A       | Sr SLAVE AD   | DRESS       |                          | R                                                                             | А     | <csr></csr> | A P           |     |

|--------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|--------------------------------------|-------------|---------|---------------|-------------|--------------------------|-------------------------------------------------------------------------------|-------|-------------|---------------|-----|

|        |                                                                                                                                 |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

|        |                                                                                                                                 |                                      |                                | write ad                             | dress po    | inter   |               |             | '1'                      | (read)                                                                        | ) 1   | ead statu   | S             |     |

|        | '0' (write) Sr = repeated START condition                                                                                       |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

|        | from master to slave from slave to master 001aag925                                                                             |                                      |                                |                                      |             |         |               |             |                          | ī                                                                             |       |             |               |     |

|        | A = acknowledge (SDA = LOW).<br>S = START condition.                                                                            |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

|        | P = STOP conditio                                                                                                               |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

| Fig 4. | Host reads TDA                                                                                                                  | 9951                                 | status                         | s registe                            | r after     | settin  | g address poi | nter        |                          |                                                                               |       |             |               |     |

|        | S     SLAVE ADDRESS     R     A <csr>     A     P       '1' (read)     '1' (read)     read status</csr>                         |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

|        |                                                                                                                                 |                                      |                                | from mas                             | ster to sla | ave     | from sla      | ave to m    | aster<br>201 <i>aa</i> g |                                                                               |       |             |               |     |

|        | A = acknowledge (SDA = LOW).<br>S = START condition.<br>P = STOP condition.                                                     |                                      |                                |                                      |             |         |               |             |                          |                                                                               |       |             |               |     |

| Fig. 5 |                                                                                                                                 |                                      | -1-1                           |                                      |             |         | ting address  |             |                          | - 1                                                                           |       | o ot 0 o    | luce du ()    |     |

| Fig 5. | P = STOP conditio<br>Host reads TDA                                                                                             |                                      | status                         | s registe                            | r witho     | out set | ting address  | pointe      | er (p                    | ointe                                                                         | er wa | s at 0 a    | Iready)       |     |

| Fig 5. |                                                                                                                                 | .9951                                | _                              | <b>registe</b>                       | r witho     |         | ting address  | pointe<br>R | er (p                    | ointe                                                                         | _     | _           | ACKL>         | A P |

|        | Host reads TDA                                                                                                                  | 9951                                 | A 000                          | 00 0100                              | A Sr        |         | VE ADDRESS    | R           | A                        |                                                                               | _     |             | <ackl></ackl> |     |

|        | Host reads TDA                                                                                                                  | 9951<br>w                            | A 000                          | 00 0100                              | A Sr<br>er  | SLA     | VE ADDRESS    |             | A<br>)                   |                                                                               | H> A  |             |               |     |

|        | Host reads TDA                                                                                                                  | 9951                                 | A 000                          | 00 0100                              | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th></th></ack<>   | H> A  |             | <ackl></ackl> |     |

| S      | Host reads TDA                                                                                                                  | 9951<br>w                            | A 000<br>write ad              | 00 0100                              | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th></th></ack<>   | H> A  |             | <ackl></ackl> |     |

| S      | Host reads TDA<br>SLAVE ADDRESS<br>'0'<br>rom master to slave<br>A = acknowledge (                                              | .9951<br>                            | A 000<br>write ad<br>)<br>fron | 00 0100<br>dress pointe<br>Sr = repe | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th>sL</th></ack<> | H> A  |             | <ackl></ackl> | sL  |

| S      | Host reads TDA<br>SLAVE ADDRESS<br>'0'<br>rom master to slave<br>A = acknowledge (<br>S = START condition                       | .9951<br>w (write) (write) SDA = on. | A 000<br>write ad<br>)<br>fron | 00 0100<br>dress pointe<br>Sr = repe | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th>sL</th></ack<> | H> A  |             | <ackl></ackl> | sL  |

| S      | Host reads TDA<br>SLAVE ADDRESS<br>'0'<br>rom master to slave<br>A = acknowledge (                                              | .9951<br>w (write) (write) SDA = on. | A 000<br>write ad<br>)<br>fron | 00 0100<br>dress pointe<br>Sr = repe | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th>sL</th></ack<> | H> A  |             | <ackl></ackl> | sL  |

| S      | Host reads TDA<br>SLAVE ADDRESS<br>'0'<br>rom master to slave<br>A = acknowledge (<br>S = START condition<br>P = STOP condition | .9951<br>w (write) (write) SDA = on. | A 000<br>write ad<br>)<br>fron | 00 0100<br>dress pointe<br>Sr = repe | A Sr<br>er  | SLA     | VE ADDRESS    | R           | A<br>)                   | <ack< th=""><th>H&gt; A</th><th></th><th><ackl></ackl></th><th>sL</th></ack<> | H> A  |             | <ackl></ackl> | sL  |

**TDA9951**

#### CEC/I<sup>2</sup>C-bus translator

### 8.7 I<sup>2</sup>C command examples

#### 8.7.1 Initialization

After a reset, configure the TDA9951 with its logical address or addresses (as required):

#### • I2C\_WRITE: 04h, 00h, 08h

Set address pointer to 04h (ACKH), set ACKH to 00h and set ACKL to 08h (example). The TDA9951 is now configured to acknowledge messages to logical address 3 (Tuner 1).

Remark: It is then mandatory to set the TDA9951 to the ON state as follows:

#### • I2C\_WRITE: 03h, 40h

Set address pointer to 03h (CCR) and set CCR to 40h.

The TDA9951 is now enabled. Messages addressed to logical address Tuner 1 is acknowledged and forwarded to the host processor.

#### 8.7.2 Sending CEC messages

Example: the host processor of playback device 1 wishes to send the message <TextView On> to TV:

• I2C\_WRITE: 00h; I2C\_READ, I2C\_READ, ...

Set address pointer to 00h (CSR) and read common status register. Repeat the read sequence until TDA9951 is no longer busy (bit 7 = 0).

• I2C\_WRITE: 07h, 04h, 00h, 40h, 0Dh

Set address pointer to 07h (Data Register 1) and write data registers. FrameByteCount = 4, ServiceSelector = CECData.req, AddressByte = DVD/TV and DataByte = <TextView On>.

#### • Wait for INT line to be asserted

When TDA9951 has a response, it asserts the I2C\_INT line (could also poll bit 6 of CSR).

#### • I2C\_WRITE: 07h; I2C\_READ: 03h, 01h, 00h

Set address pointer to 07h (Data Register 1) and read data registers. FrameByteCount = 3, ServiceSelector = CECData.cnf and ResultCode = Success.

#### 8.7.3 Receiving CEC messages

Example: TV sends the message <Give Physical Address> to Playback Device 1:

#### • INT line is asserted

The TDA9951 at playback device 1 has acknowledged the message from TV and it is now available for reading by the playback device 1 host processor.

#### • I2C\_WRITE: 07h; I2C\_READ: 04h, 81h, 04h, 83h

Set address pointer to 07h (Data Register 1) and read data registers. FrameByteCount = 4, ServiceSelector = CECData.ind, AddressByte = TV/DVD and DataByte = <Give Physical Address>.

#### 8.8 Infrared receiver interface

#### 8.8.1 Infrared hardware

The input port pin IR\_DAT is active LOW and receives demodulated infrared data from an external demodulator device that strips the 36 kHz infrared carrier. The output port pin IR\_VAL is driven LOW for 65 ms after a valid frame is received enabling it to drive an external LED activity indicator.

Wave form timing is achieved using the chip's capture and compare unit based on the defined timing limits.

- In RC5 mode, timing tolerances are checked and frames containing any bits outside the limits are rejected.

- Start bits have wider timing tolerances than other bits to avoid false frame rejection.

- In RC6 Mode 0, timing tolerances are checked and frames containing any bits outside the limits are rejected.

- Dropout spikes of 60 μs or less are ignored during start bit or leader pulse detection.

#### 8.8.2 Protocol discrimination

The three protocol variants are automatically selected by measuring the length of the first active pulse, as follows:

| Table 21. Protocol discrimination | 21. Protocol discriminati | on |

|-----------------------------------|---------------------------|----|

|-----------------------------------|---------------------------|----|

| Protocol     | Active pulse                                                  |      | Time range<br>(μs) |

|--------------|---------------------------------------------------------------|------|--------------------|

| RC5          | second half of start bit S1                                   | 889  | 676 to 1306        |

| RC5 Enlarged | second half of start bit S1 and first half of command bit /C6 | 1778 | 1352 to 2178       |

| RC6 Mode 0   | first part of leader pulse                                    | 2667 | 2179 to 3360       |

#### 8.8.3 IRData.ind service

This service is used to transfer an infrared remote control commands to the host. The frame bytes for the service are shown in Table 22.

**Remark:** The SBYData.req request service configures some IRX commands to enter or leave Standby mode.

|          | Table 22. Traine Bytes for indutating service |        |        |                                        |  |  |  |  |

|----------|-----------------------------------------------|--------|--------|----------------------------------------|--|--|--|--|

| Register | Frame Byte                                    | Bit    | Value  | Comments                               |  |  |  |  |

| 07h      | FrameByteCount                                |        | 05h    |                                        |  |  |  |  |

| 08h      | ServiceSelector                               |        | 85h    | IRData.ind                             |  |  |  |  |

| 09h      | CmdFlags                                      |        |        | bit flags associated with the command: |  |  |  |  |

|          |                                               | 7 to 2 | 00h    | unused; set to 0                       |  |  |  |  |

|          |                                               | 1      |        | protocol type                          |  |  |  |  |

|          |                                               |        | 0      | RC5                                    |  |  |  |  |

|          |                                               |        | 1      | RC6                                    |  |  |  |  |

|          |                                               | 0      | 0 or 1 | a copy of the received Toggle bit      |  |  |  |  |

| 0Ah      | CmdAddress                                    |        | -      | command address byte                   |  |  |  |  |

| 0Bh      | CmdData                                       |        | -      | command data or command byte           |  |  |  |  |

|          |                                               |        |        |                                        |  |  |  |  |

Table 22. Frame Bytes for IRData.ind service

#### 8.9 Key matrix interface

#### 8.9.1 Key matrix hardware

The Key Matrix Interface (KEY) is designed to manage up to 10 buttons. The key matrix interface uses five input lines (KROW0 to KROW4) and one output line (KCOL) to decode a matrix of up to ten normally open switch contacts. Contact de-bouncing is achieved by reading the input again after a nominal 20 ms period and discarding the event if the state changes in that time.

#### 8.9.2 Key matrix decoding

The decoding algorithm is described in Application Note AN10184 (Connecting a keyboard to the LPC9xx microcontroller, 14/09/2002).

Multiple simultaneous contact closure events are discarded.

#### 8.9.3 Key matrix encoding

The KROW0 to KROW4 input lines (matrix rows) are connected to the chip port 0. The port produces an interrupt when certain port inputs match or deviate from a set pattern. This allows the unused pins of port 0 to be masked out of this process and used for other purposes.

The KCOL output line (matrix column) is used to identify which set of five switches the input contact closure belongs to.

Key events are encoded as follows. The matrix rows are numbered 0 to 4 and the matrix columns 0 to 1. A contact closure is defined as the intersection of a row and column in the matrix:

| Column | Row | Key ID | Column | Row | Key ID |

|--------|-----|--------|--------|-----|--------|

| 0      | 0   | 1      | 1      | 0   | 6      |

| 0      | 1   | 2      | 1      | 1   | 7      |

| 0      | 2   | 3      | 1      | 2   | 8      |

| 0      | 3   | 4      | 1      | 3   | 9      |

| 0      | 4   | 5      | 1      | 4   | 10     |

#### Table 23. Key matrix

#### 8.9.4 KEYData.req service

Using this service the host requests the current matrix key switch states. The frame bytes for the service are shown in Table 24.

#### Table 24. Frame Bytes for KEYData.req service

| Register | Frame Byte      | Value | Comments    |  |

|----------|-----------------|-------|-------------|--|

| 07h      | FrameByteCount  | 02h   |             |  |

| 08h      | ServiceSelector | 08h   | KEYData.req |  |

#### 8.9.5 KEYData.cnf service

Using this service, the TDA9951 informs the host of the matrix key switch states after a KEYData.req service request. The frame bytes are shown in Table 25.

| Table 25. | . Frame Bytes for KEYData.cnf service |        |       |                                                      |  |

|-----------|---------------------------------------|--------|-------|------------------------------------------------------|--|

| Register  | Frame Byte                            | Bit    | Value | Comments                                             |  |

| 07h       | FrameByteCount                        |        | 04h   |                                                      |  |

| 08h       | ServiceSelector                       |        | 09h   | KeyData.cnf                                          |  |

| 09h       | KeyStates1                            |        |       | bit flags showing the states of key switches 1 to 8  |  |

|           |                                       | 7      |       | key 8                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 6      |       | key 7                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 5      |       | key 6                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 4      |       | key 5                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 3      |       | key 4                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 2      |       | key 3                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 1      |       | key 2                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 0      |       | key 1                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

| 0Ah       | KeyStates2                            |        |       | bit flags showing the states of key switches 9 to 10 |  |

|           |                                       | 7 to 2 |       | not used                                             |  |

|           |                                       | 1      |       | key 10                                               |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

|           |                                       | 0      |       | key 9                                                |  |

|           |                                       |        | 0     | open                                                 |  |

|           |                                       |        | 1     | closed                                               |  |

#### Table 25. Frame Bytes for KEYData.cnf service

#### 8.9.6 KEYData.ind service

Using this service, the TDA9951 transfers a key press or release command to the host. The frame bytes are listed in Table 26.

| Table 26. | Frame Bytes for KEYData.ind service |        |       |                                                 |  |  |  |

|-----------|-------------------------------------|--------|-------|-------------------------------------------------|--|--|--|

| Register  | Frame Byte                          | Bit    | Value | Comments                                        |  |  |  |

| 07h       | FrameByteCount                      |        | 03h   |                                                 |  |  |  |

| 08h       | ServiceSelector                     |        | 86h   | KEYData.ind                                     |  |  |  |

| 09h       | KeyData                             |        |       | bit field associated with the key switch event: |  |  |  |

|           |                                     | 0 to 3 | -     | key code 1 to 10                                |  |  |  |

|           |                                     | 4 to 6 | -     | not used                                        |  |  |  |

|           |                                     | 7      | 1     | key open                                        |  |  |  |

|           |                                     |        | 0     | closed                                          |  |  |  |

|           |                                     |        |       |                                                 |  |  |  |

#### Table 26 Eromo Butoo for KEVData ind convice

#### 8.10 Real time clock interface

#### 8.10.1 Real time clock hardware

The Real Time Clock (RTC) interface communicates with a software clock-calendar running in the TDA9951 which uses the dedicated 23-bit RTC. The RTC timer is set to generate a 1 s interrupt.

When the power source changes from power supply to battery, the PSEN input goes LOW. All interface and alarm/timer activity is stopped. The chip switches to low-power mode but continues to count RTC timer ticks.

The host can read the clock-calendar on demand by using the RTCData.req request service. The current date and time is returned using the RTCData.cnf confirm service. The data registers are fixed during a read action ensuring a consistent time value is returned.

#### 8.10.2 Clock-calendar

The 1 s event handler increments a long integer representing the number of seconds since the start of a time epoch. It also manages any active alarm and timers.

The date and time fields in the request and confirmation services are converted to and from the long integer using code adapted from the "Maxim/Dallas Semiconductor application note 3721 Interfacing the DS1318 with an 8051 type Microcontroller, 9/12/2005".

#### 8.10.3 Alarm

Only one alarm is active at a time with the clock-calendar and timers. The alarm is triggered when the real-time clock matches all date and time bytes set in an active alarm request. Setting an alarm replaces a previously set alarm.

Alarms are cancelled by clearing the alarm active bit in the RTCData.req ServiceFlags byte. The Date and time bytes in RTCData.reg are ignored if the active bit is cleared. Alarms are not active after a power-up or reset.

An alarm sets Standby mode when its standby bit in the RTCData.req ServiceFlags byte is set. An alarm triggered in Standby mode exits and its standby bit is not set.

#### 8.10.4 Timers

A maximum of two timers may be simultaneously active with the clock-calendar and alarm. Each timer may be either one-shot or periodic.

- One-shot timers are triggered when the real-time clock matches the current time plus the time and day bytes set by an active timer request.

- Periodic timers work in the same way but are triggered repeatedly at the specified interval.

The timer resolution is 1 s and allowed timer interval range is from 1 s up to 31 days, 23 hours, 59 minutes and 59 s. Setting timer 1 replaces the previous timer 1 setting but does not change timer 2 or a pending alarm. Timer 2 functions in the same way.

Timers are stopped by clearing its respective timer active bit in the RTCData.req ServiceFlags byte. Date and time bytes in RTCData.req are ignored when the active bit is clear. After power-up and reset, the timers are not active.

A timer sets Standby mode if its standby bit is set in the RTCData.req ServiceFlag byte. Timers triggered in Standby mode exits Standby mode when the respective standby bit is not set.

#### 8.10.5 RTCData.req service

This service is used to read or set the clock date and time, to set an alarm or to set the timers. The frame bytes are listed in Table 27.

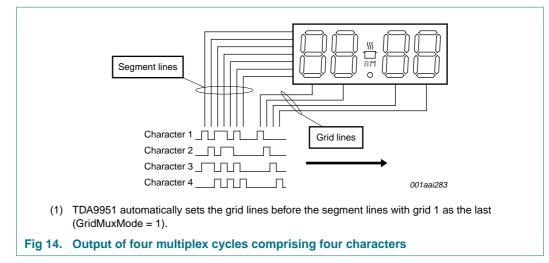

The ServiceType byte determines the action to be performed. When the clock is read, all other bytes are ignored and can be set to 00h. When a timer is set, the Month and Year bytes are ignored and can be set to 00h.