### LTC4006

### 4A, High Efficiency, Standalone Li-Ion Battery Charger

### FEATURES

- Complete Charger Controller for 2-, 3- or 4-Cell Lithium-Ion Batteries

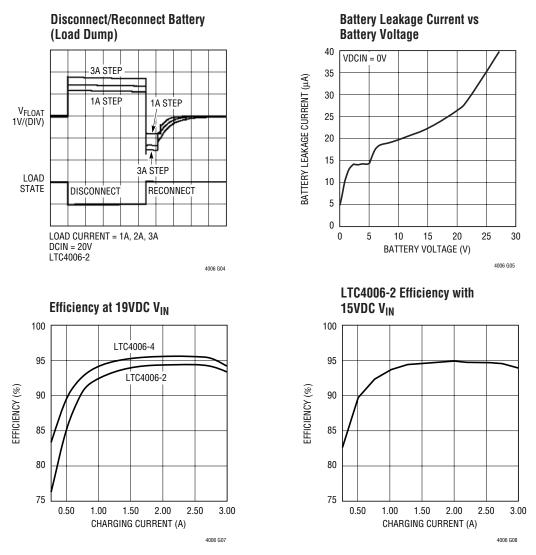

- High Conversion Efficiency: Up to 96%

- Output Currents Exceeding 4A

- ±0.8% Accurate Preset Voltages: 8.4V, 12.6V, 16.8V

- Built-In Charge Termination with Automatic Restart

- AC Adapter Current Limiting Maximizes Charge Rate\*

- Automatic Conditioning of Deeply Discharged Batteries

- Thermistor Input for Temperature Qualified Charging

- Wide Input Voltage Range: 6V to 28V

- 0.5V Dropout Voltage; Maximum Duty Cycle: 98%

- Programmable Charge Current: ±4% Accuracy

- Indicator Outputs for Charging, C/10 Current Detection and AC Adapter Present

- Charging Current Monitor Output

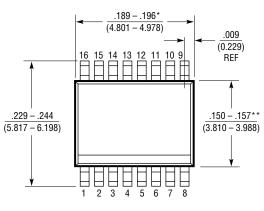

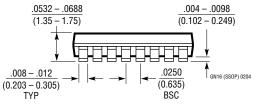

- 16-Pin Narrow SSOP Package

### **APPLICATIONS**

- Notebook Computers

- Portable Instruments

- Battery-Backup Systems

- Standalone Li-Ion Chargers

## DESCRIPTION

The LTC<sup>®</sup>4006 is a complete constant-current/constantvoltage charger controller for 2-, 3- or 4-cell lithium batteries in a small package using few external components. The PWM controller is a synchronous, quasi-constant frequency, constant off-time architecture that will not generate audible noise even when using ceramic capacitors.

The LTC4006 is available in 8.4V, 12.6V and 16.8V versions with  $\pm 0.8\%$  voltage accuracy. Charging current is programmable with a single sense resistor to  $\pm 4\%$  typical accuracy. Charging current can be monitored as a representative voltage at the I<sub>MON</sub> pin. A timer, programmed by an external resistor, sets the total charge time or is reset to 25% of total charge time after C/10 charging current is reached. Charging automatically resumes when the cell voltage falls below 3.9V/cell.

Fully discharged cells are automatically trickle charged at 10% of the programmed current until the cell voltage exceeds 2.5V/cell. Charging terminates if the low-battery condition persists for more than 25% of the total charge time.

The LTC4006 includes a thermistor sensor input that suspends charging if an unsafe temperature condition is detected and automatically resumes charging when the battery temperature returns to within safe limits.

**L7**, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5723970.

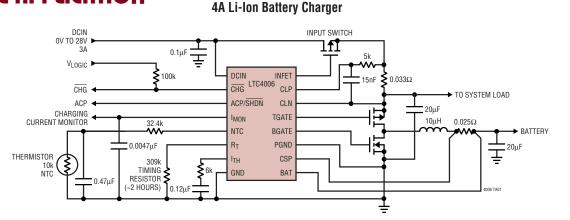

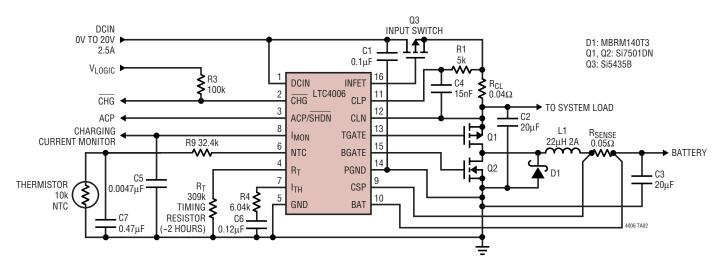

### TYPICAL APPLICATION

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Voltage from DCIN, CLP, CLN, TGATE, INFET,      |

|-------------------------------------------------|

| ACP/SHDN, $\overline{CHG}$ to GND +32V to -0.3V |

| Voltage from CLP to CLN ±0.3V                   |

| CSP, BAT to GND +28V to -0.3V                   |

| $R_T$ to GND+7V to -0.3V                        |

| NTC +10V to -0.3V                               |

| Operating Ambient Temperature Range             |

| (Note 4)40°C to 85°C                            |

| Operating Junction Temperature –40°C to 125°C   |

| Storage Temperature Range –65°C to 150°C        |

| Lead Temperature (Soldering, 10 sec)            |

|                                                 |

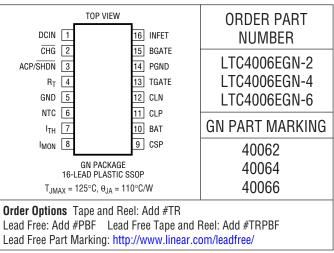

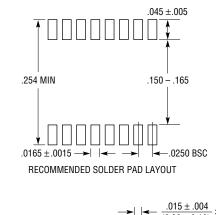

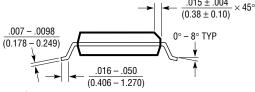

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

### **ELECTRICAL CHARACTERISTICS**

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range (Note 4), otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>BAT</sub> = 12V unless otherwise noted.

| SYMBOL           | PARAMETER                                 | CONDITIONS                                                                                                                                                                                  |   | MIN                                                    | ТҮР                                        | MAX                                                    | UNITS                      |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------|--------------------------------------------|--------------------------------------------------------|----------------------------|

|                  | DCIN Operating Range                      |                                                                                                                                                                                             |   | 6                                                      |                                            | 28                                                     | V                          |

| IDCIN            | DCIN Operating Current                    | Sum of Current from CLP, CLN, DCIN                                                                                                                                                          |   |                                                        | 3                                          | 5                                                      | mA                         |

| V <sub>TOL</sub> | Voltage Accuracy                          | (Note 2)<br>LTC4006-6<br>LTC4006-2<br>LTC4006-2<br>LTC4006-2<br>LTC4006-4<br>LTC4006-4                                                                                                      | • | 8.333<br>8.316<br>12.499<br>12.474<br>16.665<br>16.632 | 8.4<br>8.4<br>12.6<br>12.6<br>16.8<br>16.8 | 8.467<br>8.484<br>12.700<br>12.726<br>16.935<br>16.968 | V<br>V<br>V<br>V<br>V<br>V |

| I <sub>TOL</sub> | Current Accuracy (Note 3)                 | $ \begin{array}{l} V_{CSP} - V_{BAT} \mbox{ Target} = 100mV \\ V_{BAT} = 11.5V \mbox{ (LTC4006-2)} \\ V_{BAT} = 7.6V \mbox{ (LTC4006-6)} \\ V_{BAT} = 12V \mbox{ (LTC4006-4)} \end{array} $ | • | -4<br>-5                                               |                                            | 4<br>5                                                 | %                          |

|                  |                                           | V <sub>BAT</sub> < 6V, V <sub>CSP</sub> – V <sub>BAT</sub> Target = 10mV                                                                                                                    |   | -60                                                    |                                            | 60                                                     | %                          |

|                  |                                           | $6V \le V_{BAT} \le V_{LOBAT},$<br>$V_{CSP} - V_{BAT}$ Target = 10mV                                                                                                                        |   | -40                                                    |                                            | 40                                                     | %                          |

| T <sub>TOL</sub> | Termination Timer Accuracy                | R <sub>RT</sub> = 270k                                                                                                                                                                      | • | -15                                                    |                                            | 15                                                     | %                          |

| Shutdown         |                                           |                                                                                                                                                                                             |   |                                                        |                                            |                                                        | ,                          |

|                  | Battery Leakage Current                   | DCIN = 0V<br>DCIN = 0V<br>DCIN = 20V, V <sub>SHDN</sub> = 0V, V <sub>BAT</sub> = 12V                                                                                                        | • | -10                                                    | 20<br>25<br>0                              | 35<br>45<br>10                                         | μΑ<br>μΑ<br>μΑ             |

| UVLO             | Undervoltage Lockout Threshold            | DCIN Rising, V <sub>BAT</sub> = 0V                                                                                                                                                          | • | 4.2                                                    | 4.7                                        | 5.5                                                    | V                          |

|                  | Shutdown Threshold at ACP/SHDN            |                                                                                                                                                                                             | • | 1                                                      |                                            | 2.5                                                    | V                          |

|                  | DCIN Current in Shutdown                  | V <sub>SHDN</sub> = 0V, Sum of Current from CLP,<br>CLN, DCIN                                                                                                                               |   |                                                        | 2                                          | 3                                                      | mA                         |

| Current S        | ense Amplifier, CA1                       | · · ·                                                                                                                                                                                       |   |                                                        |                                            |                                                        |                            |

|                  | Input Bias Current Into BAT Pin           |                                                                                                                                                                                             |   |                                                        | 11.67                                      |                                                        | μA                         |

| CMSL             | CA1/I <sub>1</sub> Input Common Mode Low  |                                                                                                                                                                                             | • | 0                                                      |                                            |                                                        | V                          |

| CMSH             | CA1/I <sub>1</sub> Input Common Mode High |                                                                                                                                                                                             | • |                                                        |                                            | V <sub>CLN</sub> - 0.2                                 | V                          |

|                  |                                           | I                                                                                                                                                                                           |   | 1                                                      |                                            | -                                                      | 4006fa                     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range (Note 4), otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>BAT</sub> = 12V unless otherwise noted.

| SYMBOL            | PARAMETER                                                                    | CONDITIONS                                              |   | MIN              | ТҮР              | MAX              | UNITS    |

|-------------------|------------------------------------------------------------------------------|---------------------------------------------------------|---|------------------|------------------|------------------|----------|

| Current Co        | omparators I <sub>CMP</sub> and I <sub>REV</sub>                             |                                                         |   |                  |                  |                  |          |

| I <sub>TMAX</sub> | Maximum Current Sense Threshold ( $V_{CSP} - V_{BAT}$ )                      | V <sub>ITH</sub> = 2.5V                                 |   | 140              | 165              | 200              | m۷       |

| I <sub>TREV</sub> | Reverse Current Threshold (V <sub>CSP</sub> – V <sub>BAT</sub> )             |                                                         |   |                  | -30              |                  | mV       |

| Current Se        | ense Amplifier, CA2                                                          |                                                         |   |                  |                  |                  |          |

|                   | Transconductance                                                             |                                                         |   |                  | 1                |                  | mmho     |

|                   | Source Current                                                               | Measured at $I_{TH}$ , $V_{ITH} = 1.4V$                 |   |                  | -40              |                  | μA       |

|                   | Sink Current                                                                 | Measured at $I_{TH}$ , $V_{ITH} = 1.4V$                 |   |                  | 40               |                  | μA       |

| Current Li        | mit Amplifier                                                                |                                                         |   |                  |                  |                  |          |

|                   | Transconductance                                                             |                                                         |   |                  | 1.5              |                  | mmho     |

| V <sub>CLP</sub>  | Current Limit Threshold                                                      |                                                         | • | 93               | 100              | 107              | mV       |

| I <sub>CLP</sub>  | CLP Input Bias Current                                                       |                                                         |   |                  | 100              |                  | nA       |

| Voltage Er        | rror Amplifier, EA                                                           |                                                         |   |                  |                  |                  |          |

|                   | Transconductance                                                             |                                                         |   |                  | 1                |                  | mmho     |

|                   | Sink Current                                                                 | Measured at $I_{TH}$ , $V_{ITH} = 1.4V$                 |   |                  | 36               |                  | μA       |

| OVSD              | Overvoltage Shutdown Threshold as a Percent<br>of Programmed Charger Voltage |                                                         | • | 102              | 107              | 110              | %        |

| Input P-Ch        | annel FET Driver (INFET)                                                     |                                                         |   |                  |                  |                  |          |

|                   | DCIN Detection Threshold ( $V_{DCIN} - V_{CLN}$ )                            | DCIN Voltage Ramping Up<br>from V <sub>CLN</sub> – 0.1V | • | 0                | 0.17             | 0.25             | V        |

|                   | Forward Regulation Voltage (V <sub>DCIN</sub> – V <sub>CLN</sub> )           |                                                         | • |                  | 25               | 50               | mV       |

|                   | Reverse Voltage Turn-Off Voltage (V <sub>DCIN</sub> – V <sub>CLN</sub> )     | DCIN Voltage Ramping Down                               | • | -60              | -25              |                  | mV       |

|                   | INFET "On" Clamping Voltage (V <sub>DCIN</sub> – V <sub>INFET</sub> )        | I <sub>INFET</sub> = 1µA                                | • | 5                | 5.8              | 6.5              | V        |

|                   | INFET "Off" Clamping Voltage (V <sub>DCIN</sub> – V <sub>INFET</sub> )       | $I_{INFET} = -25\mu A$                                  |   |                  |                  | 0.25             | V        |

| Thermisto         | r                                                                            |                                                         |   |                  |                  |                  |          |

| NTCVR             | Reference Voltage During Sample Time                                         |                                                         |   |                  | 4.5              |                  | V        |

|                   | High Threshold                                                               | V <sub>NTC</sub> Rising                                 | • | NTCVR<br>• 0.48  | NTCVR<br>• 0.5   | NTCVR<br>• 0.52  | V        |

|                   | Low Threshold                                                                | V <sub>NTC</sub> Falling                                | • | NTCVR<br>• 0.115 | NTCVR<br>• 0.125 | NTCVR<br>• 0.135 | V        |

|                   | Thermistor Disable Current                                                   | $V_{NTC} \le 10V$                                       |   |                  |                  | 10               | μA       |

| Indicator (       | Dutputs (ACP/SHDN, CHG)                                                      |                                                         |   |                  |                  |                  |          |

| C10TOL            | C/10 Indicator Accuracy                                                      | Voltage Falling at PROG                                 |   | 0.375            | 0.400            | 0.425            | V        |

| LBTOL             | LOBAT Threshold Accuracy                                                     | LTC4006-6                                               | • | 4.70             | 4.93             | 5.14             | V        |

|                   |                                                                              | LTC4006-2<br>LTC4006-4                                  | • | 7.27<br>9.70     | 7.5<br>10        | 7.71<br>10.28    | V<br>  V |

|                   | RESTART Threshold Accuracy                                                   | LTC4006-6                                               | • | 7.5              | 7.8              | 7.96             | V        |

|                   |                                                                              | LTC4006-2<br>LTC4006-4                                  | • | 11.35<br>15.15   | 11.7<br>15.6     | 11.94<br>15.92   |          |

| V <sub>OL</sub>   | Low Logic Level of ACP/SHDN, CHG                                             | I <sub>OL</sub> = 100μA                                 | • |                  |                  | 0.5              | V        |

| V <sub>OH</sub>   | High Logic Level of ACP/SHDN                                                 | $I_{OH} = -1\mu A$                                      | • | 2.7              |                  |                  | V        |

| I <sub>PO</sub>   | Pull-Up Current on ACP/SHDN                                                  | V = 0V                                                  |   |                  | -10              |                  | μA       |

| IC10              | C/10 Indicator Sink Current from CHG                                         | V <sub>0H</sub> = 3V                                    | • | 15               | 25               | 38               | μA       |

| I <sub>OFF</sub>  | Off State Leakage Current of CHG                                             | V <sub>OH</sub> = 3V                                    |   | -1               |                  | 1                | μΑ       |

|                   | Timer Defeat Threshold at CHG                                                |                                                         |   | 1                |                  |                  | V        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range (Note 4), otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>BAT</sub> = 12V unless otherwise noted.

| SYMBOL            | PARAMETER                                                               | CONDITIONS                                                                       | MIN | ТҮР      | MAX        | UNITS    |

|-------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|----------|------------|----------|

| Oscillator        |                                                                         |                                                                                  |     |          |            |          |

| f <sub>OSC</sub>  | Regulator Switching Frequency                                           |                                                                                  | 255 | 300      | 345        | kHz      |

| f <sub>MIN</sub>  | Regulator Switching Frequency in Drop Out                               | Duty Cycle ≥ 98%                                                                 | 20  | 25       |            | kHz      |

| DC <sub>MAX</sub> | Regulator Maximum Duty Cycle                                            | $V_{CSP} = V_{BAT}$                                                              | 98  | 99       |            | %        |

| Gate Drive        | ers (TGATE, BGATE)                                                      |                                                                                  |     |          |            |          |

|                   | V <sub>TGATE</sub> High (V <sub>CLN</sub> – V <sub>TGATE</sub> )        | I <sub>TGATE</sub> = -1mA                                                        |     |          | 50         | mV       |

|                   | V <sub>BGATE</sub> High                                                 | C <sub>LOAD</sub> = 3000pF                                                       | 4.5 | 5.6      | 10         | V        |

|                   | V <sub>TGATE</sub> Low (V <sub>CLN</sub> – V <sub>TGATE</sub> )         | C <sub>LOAD</sub> = 3000pF                                                       | 4.5 | 5.6      | 10         | V        |

|                   | V <sub>BGATE</sub> Low                                                  | I <sub>BGATE</sub> = 1mA                                                         |     |          | 50         | mV       |

| TGTR<br>TGTF      | TGATE Transition Time<br>TGATE Rise Time<br>TGATE Fall Time             | C <sub>LOAD</sub> = 3000pF, 10% to 90%<br>C <sub>LOAD</sub> = 3000pF, 10% to 90% |     | 50<br>50 | 110<br>100 | ns<br>ns |

| BGTR<br>BGTF      | BGATE Transition Time<br>BGATE Rise Time<br>BGATE Fall Time             | C <sub>LOAD</sub> = 3000pF, 10% to 90%<br>C <sub>LOAD</sub> = 3000pF, 10% to 90% |     | 40<br>40 | 90<br>80   | ns<br>ns |

|                   | V <sub>TGATE</sub> at Shutdown (V <sub>CLN</sub> – V <sub>TGATE</sub> ) | $I_{TGATE} = -1\mu A$ , DCIN = 0V, CLN = 12V                                     |     |          | 100        | mV       |

|                   | V <sub>BGATE</sub> at Shutdown                                          | I <sub>BGATE</sub> = 1µA, DCIN = 0V, CLN = 12V                                   |     |          | 100        | mV       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 3: Does not include tolerance of current sense resistor.

**Note 4:** The LTC4006E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

Note 2: See Test Circuit

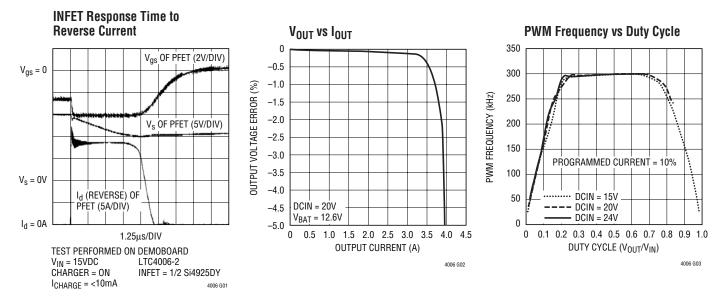

## **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### PIN FUNCTIONS

DCIN (Pin 1): External DC Power Source Input. Bypass this pin with at least  $0.01 \mu F.$  See Applications Information section.

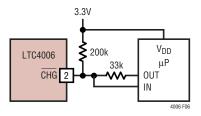

**CHG** (Pin 2): Open-Drain Charge Status Output. When the battery is being charged, the CHG pin is pulled low by an internal N-channel MOSFET. When the charge current drops below 10% of programmed current, the N-channel MOSFET turns off and a 25µA current source is connected from the CHG pin to GND. When the timer runs out or the input supply is removed, the current source will be discon-

nected and the  $\overline{CHG}$  pin is forced into a high impedance state. A pull-up resistor is required. The timer function is defeated by forcing this pin below 1V (or connecting it to GND).

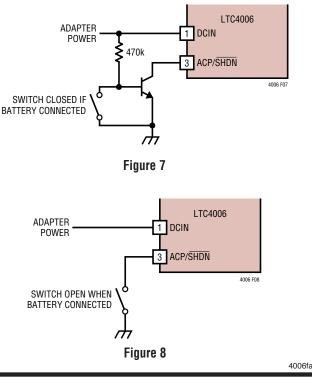

**ACP/SHDN (Pin 3):** Open-Drain Output used to indicate if the AC adapter voltage is adequate for charging. Active high digital output. Internal  $10\mu$ A pull-up to 3.5V. The charger can also be inhibited by pulling this pin below 1V. Reset the charger by pulsing the pin low for a minimum of 0.1 $\mu$ s.

### **PIN FUNCTIONS**

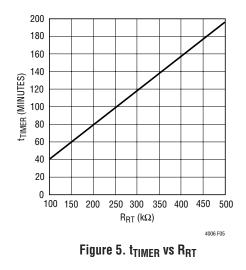

$\textbf{R}_{T}$  (Pin 4): Timer Resistor. The timer period is set by placing a resistor,  $\textbf{R}_{RT}$ , to GND.

The timer period is  $t_{TIMER} = (1hour \cdot R_{RT}/154k)$

If this resistor is not present, the charger will not start.

GND (Pin 5): Ground for low power circuitry.

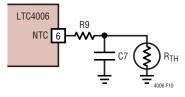

**NTC (Pin 6):** A thermistor network is connected from NTC to GND. This pin determines if the battery temperature is safe for charging. The charger and timer are suspended if the thermistor indicates a temperature that is unsafe for charging. The thermistor function may be disabled with a 300k to 500k resistor from DCIN to NTC.

$I_{TH}$  (Pin 7): Control Signal of the Inner Loop of the Current Mode PWM. Higher  $I_{TH}$  voltage corresponds to higher charging currrent in normal operation. A 6.04k resistor, in series with a capacitor of at least 0.1µF to GND, provides loop compensation. Typical full-scale output current is 40µA. Nominal voltage range for this pin is 0V to 3V.

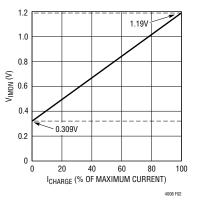

**I**<sub>MON</sub> (Pin 8): Current Monitoring Output. The voltage at this pin provides a linear indication of charging current. Peak current is equivalent to 1.19V. Zero current is approximately 0.309V. A capacitor from I<sub>MON</sub> to ground is required to filter higher frequency components. If V<sub>BAT</sub> < 2.5V/cell, then V(I<sub>MON</sub>) = 1.19V when conditioning a depleted battery. Any current sourced or sinked from this pin directly affects the charging current accuracy. If this pin is to be monitored, a high impedance input buffer should be used.

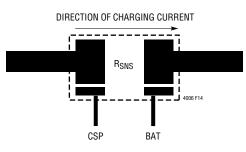

**CSP (Pin 9):** Current Amplifier CA1 Input. This pin and the BAT pin measure the voltage across the sense resistor,  $R_{SENSE}$ , to provide the instantaneous current signals required for both peak and average current mode operation.

**BAT (Pin 10):** Battery Sense Input and the Negative Reference for the Current Sense Resistor. A precision internal resistor divider sets the final float potential on this pin. The resistor divider is disconnected during shutdown.

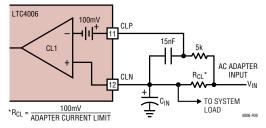

**CLP (Pin 11):** Positive Input to the Supply Current Limiting Amplifier, CL1. The threshold is set at 100mV above the voltage at the CLN pin. When used to limit supply current, a filter is needed to filter out the switching noise. If no current limit function is desired, connect this pin to CLN.

**CLN (Pin 12):** Negative Reference for the Input Current Limit Amplifier, CL1. This pin also serves as the power supply for the IC. A  $10\mu$ F to  $22\mu$ F bypass capacitor should be connected as close as possible to this pin.

**TGATE (Pin 13):** Drives the top external P-channel MOSFET of the battery charger buck converter.

**PGND (Pin 14):** High Current Ground Return for the BGATE Driver.

**BGATE (Pin 15):** Drives the bottom external N-channel MOSFET of the battery charger buck converter.

INFET (Pin 16): Drives the Gate of the External Input PFET.

### TEST CIRCUIT

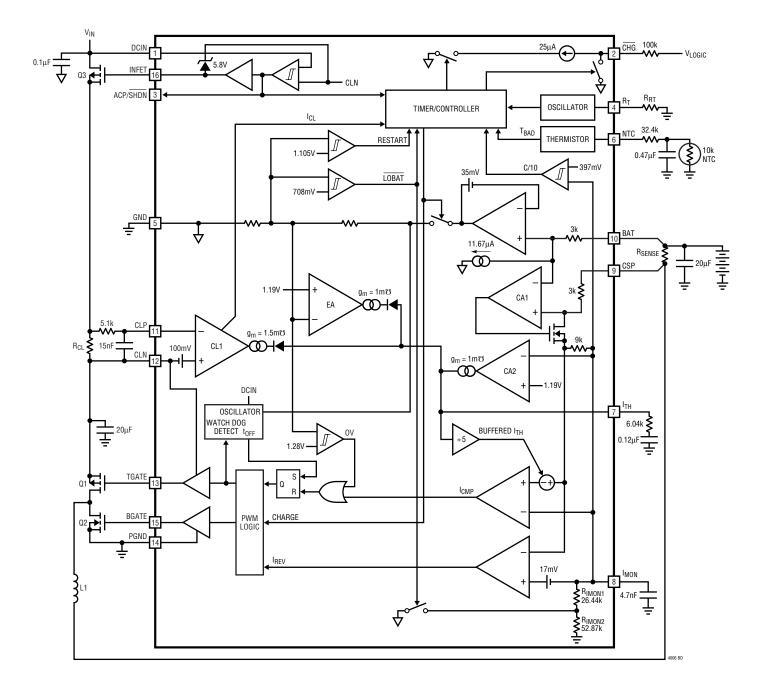

### **BLOCK DIAGRAM**

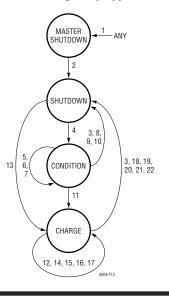

#### Overview

The LTC4006 is a synchronous current mode PWM stepdown (buck) switcher battery charger controller. The charge current is programmed by the sense resistor ( $R_{SENSE}$ ) between the CSP and BAT pins. The final float voltage is internally programmed to 8.4V (LTC4006-6), 12.6V (LTC4006-2) or 16.8V (LTC4006-4) with better than ±0.8% accuracy. Charging begins when the potential at the DCIN pin rises above the voltage at CLN (and the UVLO voltage) and the ACP/SHDN pin is allowed to go high; the CHG pin is set low. At the beginning of the charge cycle, if the cell voltage is below 2.5V, the charger will trickle charge the battery with 10% of the maximum programmed current. If the cell voltage stays below 2.5V for 25% of the total charge time, the charge sequence will be terminated immediately and the CHG pin will be set to a high impedance.

An external thermistor network is sampled at regular intervals. If the thermistor value exceeds design limits, charging is suspended. If the thermistor value returns to an acceptable value, charging resumes. An external resistor on the  $R_T$  pin sets the total charge time. The timer can be defeated by forcing the CHG pin to a low voltage.

As the battery approaches the final float voltage, the charge current will begin to decrease. When the current drops to 10% of the programmed charge current, an internal C/10 comparator will indicate this condition by sinking 25µA at the CHG pin. The charge timer is also reset to 25% of the total charge time. If this condition is caused by an input current limit condition, described below, then the C/10 comparator will be inhibited. When a time-out occurs, charging is terminated immediately and the CHG pin changes to a high impedance. The charger will automatically restart if the cell voltage is less than 3.9V. To restart the charge cycle manually, simply remove the input voltage and reapply it, or force the ACP/SHDN pin low momentarily. When the input voltage is not present, the charger goes into a sleep mode, dropping battery current drain to 15µA. This greatly reduces the current drain on the battery and increases the standby time. The charger can be inhibited at any time by forcing the ACP/SHDN pin to a low voltage.

#### Input FET

The input FET circuit performs two functions. It enables the charger if the input voltage is higher than the CLN pin and provides the logic indicator of AC present on the ACP/SHDN pin. It controls the gate of the input FET to keep a low forward voltage drop when charging and also prevents reverse current flow through the input FET.

If the input voltage is less than  $V_{CLN}$ , it must go at least 170mV higher than  $V_{CLN}$  to activate the charger. When this occurs the ACP/SHDN pin is released and pulled up with an internal load to indicate that the adapter is present. The gate of the input FET is driven to a voltage sufficient to keep a low forward voltage drop from drain to source. If the voltage between DCIN and CLN drops to less than 25mV, the input FET is turned off slowly. If the voltage between DCIN and CLN is ever less than -25mV, then the input FET is turned off in less than 10µs to prevent significant reverse current from flowing in the input FET. In this condition, the ACP/SHDN pin is driven low and the charger is disabled.

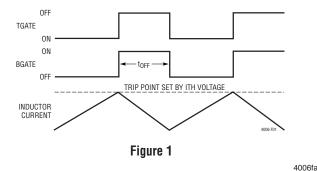

#### **Battery Charger Controller**

The LTC4006 charger controller uses a constant off-time, current mode step-down architecture. During normal operation, the top MOSFET is turned on each cycle when the oscillator sets the SR latch and turned off when the main current comparator  $I_{CMP}$  resets the SR latch. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current trips the current comparator  $I_{REV}$  or the beginning of the next cycle. The oscillator uses the equation:

$$t_{OFF} = \frac{V_{DCIN} - V_{BAT}}{V_{DCIN} \bullet f_{OSC}}$$

to set the bottom MOSFET on time. This activity is diagrammed in Figure 1.

The peak inductor current, at which  $I_{CMP}$  resets the SR latch, is controlled by the voltage on  $I_{TH}$ .  $I_{TH}$  is in turn controlled by several loops, depending upon the situation at hand. The average current control loop converts the voltage between CSP and BAT to a representative current. Error amp CA2

#### Table 1. Truth Table for LTC4006 Operation

| MODE                                                                     | DCIN                                                                                                              | BAT VOLTAGE                                                               | BAT CURRENT               | ACP/SHDN   | TIMER STATE                                                     | CHG*                             |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------|------------|-----------------------------------------------------------------|----------------------------------|

| Shut Down by Low Adapter Voltage                                         | <bat< td=""><td>&gt;UVL0</td><td>Leakage</td><td>LOW</td><td>Reset</td><td>HIGH</td></bat<>                       | >UVL0                                                                     | Leakage                   | LOW        | Reset                                                           | HIGH                             |

| Conditioning a Depleted Battery                                          | >BAT                                                                                                              | <2.5V/Cell                                                                | 10% Programmed<br>Current | HIGH       | Running                                                         | LOW                              |

| Normal Charging                                                          | >BAT                                                                                                              | >2.5V/Cell                                                                | Programmed<br>Current     | HIGH       | Running                                                         | LOW                              |

| Input Current Limited Charging                                           | >BAT                                                                                                              | >2.5V/Cell                                                                | Programmed<br>Current     | HIGH       | Running                                                         | LOW                              |

| Charger Paused Due to Thermistor Out of Range                            | >BAT                                                                                                              | Х                                                                         | OFF                       | HIGH       | Paused                                                          | LOW or 25µA<br>(Faulted)         |

| Shut Down by ACP/SHDN Pin                                                | >BAT                                                                                                              | Х                                                                         | OFF                       | Forced LOW | Reset                                                           | HIGH                             |

| Terminated by Low-Battery Fault (Note 1)                                 | >BAT                                                                                                              | <2.5V/Cell                                                                | OFF                       | HIGH       | >T/4 Stopped                                                    | HIGH<br>(Faulted)                |

| Top-Off Charging. C/10 is Latched                                        | >BAT                                                                                                              | V <sub>FLOAT</sub>                                                        | OFF                       | HIGH       | <t 10<br="" 4="" after="" c="">Comparator Trip.<br/>Running</t> | 25μΑ                             |

| Timer is Reset by C/10 Comparator (Latched), then Terminates After 1/4 T | >BAT                                                                                                              | V <sub>FLOAT</sub>                                                        | OFF                       | HIGH       | >T/4 After C/10<br>Comparator Trip.<br>Stopped                  | HIGH<br>(Waiting<br>for Restart) |

| Terminated by Expired Timer                                              | >BAT                                                                                                              | V <sub>FLOAT</sub> **                                                     | OFF                       | HIGH       | >T Stopped                                                      | HIGH<br>(Waiting<br>for Restart) |

| Timer Defeated. (Low-Battery Conditioning Still Functional)              | Х                                                                                                                 | Х                                                                         | Х                         | Х          | Х                                                               | Forced LOW                       |

| Shut Down by Undervoltage Lockout                                        | >BAT<br>and <uvl< td=""><td><uvl< td=""><td>OFF</td><td>HIGH</td><td>Reset</td><td>HIGH**</td></uvl<></td></uvl<> | <uvl< td=""><td>OFF</td><td>HIGH</td><td>Reset</td><td>HIGH**</td></uvl<> | OFF                       | HIGH       | Reset                                                           | HIGH**                           |

| Timer Defeated Until V <sub>BAT</sub> > 3.9V/Cell                        | >BAT                                                                                                              | $\begin{array}{c} 2.5V \leq V_{BAT} \leq 3.9V \\ (V/CeII) \end{array}$    | Programmed<br>Current     | HIGH       | Running                                                         | LOW                              |

\*Open Drain. High when used with pull-up resistor.

\*\*Most probable condition, X = Don't care

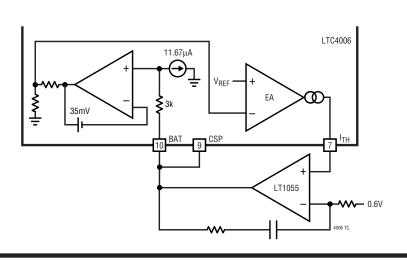

compares this current against the desired current programmed by  $R_{IMON}$  at the  $I_{MON}$  pin and adjusts  $I_{TH}$  until:

$$\frac{V_{\text{REF}}}{R_{\text{IMON}}} = \frac{V_{\text{CSP}} - V_{\text{BAT}} + 11.67 \mu \text{A} \cdot 3 k\Omega}{3 k\Omega}$$

therefore,

$$I_{CHARGE} = \left(\frac{V_{REF}}{R_{IMON}} - 11.67\mu A\right) \bullet \frac{3k\Omega}{R_{SENSE}}$$

The voltage at BAT is divided down by an internal resistor divider and is used by error amp EA to decrease  $I_{TH}$  if the divider voltage is above the 1.19V reference. When the charging current begins to decrease, the voltage at  $I_{MON}$  will decrease in direct proportion. The voltage at  $I_{MON}$  is then given by:

$$V_{IMON} = (I_{CHARGE} \bullet R_{SENSE} + 11.67 \mu A \bullet 3 k\Omega) \bullet \frac{R_{IMON}}{3 k\Omega}$$

**Note 1:** If a depleted battery is inserted while the charger is in this state, the charger must be reset to initiate charging.

The accuracy of  $V_{IMON}$  will range from 0% to  $I_{TOL}$ .

$V_{IMON}$  is plotted in Figure 2.

The amplifier CL1 monitors and limits the input current to a preset level (100mV/R<sub>CL</sub>). At input current limit, CL1 will decrease the  $I_{TH}$  voltage, thereby reducing charging current. When this condition is detected, the C/10 indicator will

Figure 2. VIMON vs I<sub>CHARGE</sub>

4006f

#### Table 2. Truth Table for LTC4006 Operation (Supplemental)

| NUMBER | FROM<br>State               | TO<br>State | MODE                                                                             | DCIN                                                                                                                | BAT<br>VOLTAGE                                                                                              | PRESENT C/10<br>Latch | NEXT C/10<br>Latch | MAX BAT<br>CURRENT                              | ACP/SHDN   | TIMER<br>STATE  | CHG*                     |

|--------|-----------------------------|-------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|-------------------------------------------------|------------|-----------------|--------------------------|

| 1      | Any                         | MSD         | Shut Down by Low Adapter Voltage                                                 | <bat< td=""><td></td><td></td><td>0</td><td>OFF</td><td>LOW</td><td>Reset</td><td>HIGH</td></bat<>                  |                                                                                                             |                       | 0                  | OFF                                             | LOW        | Reset           | HIGH                     |

| 2      | MSD                         | SD          | Charge Shutdown                                                                  | >BAT                                                                                                                |                                                                                                             |                       | 0                  | OFF                                             | HIGH       | Reset           | HIGH                     |

| 3      | SD,<br>CONDITION,<br>CHARGE | SD          | Shut Down by Undervoltage Lockout                                                | >BAT<br>and<br><uvl< td=""><td></td><td></td><td></td><td>OFF</td><td>HIGH</td><td>Reset</td><td>HIGH**</td></uvl<> |                                                                                                             |                       |                    | OFF                                             | HIGH       | Reset           | HIGH**                   |

| 4      | SD                          | CONDITION   | Start Conditioning a Depleted Battery                                            | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | 10% Programmed<br>Current                       | HIGH       |                 | LOW                      |

| 5      | CONDITION                   | CONDITION   | Input Current Limited Condition Charging                                         | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | <10% Programmed<br>Current (Note 2)             | HIGH       | Running         | LOW                      |

| 6      | CONDITION                   | CONDITION   | Conditioning a Depleted Battery                                                  | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | 10% Programmed<br>Current                       | HIGH       | Running         | LOW                      |

| 7      | CONDITION                   | CONDITION   | Timer Defeated. (Low-Battery Conditioning Still Functional)                      | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | 10% Programmed<br>Current                       | HIGH       | lgnored         | Forced LOW               |

| 8      | CONDITION                   | SD          | Charger Paused Due to Thermistor Out of Range                                    | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | OFF                                             | HIGH       | Paused          | LOW<br>(Faulted)         |

| 9      | CONDITION                   | SD          | Timeout in CONDITION Mode                                                        | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       |                    | OFF                                             | HIGH       | >T/4            | HIGH<br>(Faulted)        |

| 10     | CONDITION                   | SD          | Shut Down by ACP/SHDN Pin                                                        | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       | 0                  | OFF                                             | Forced LOW | Reset           | HIGH                     |

| 11     | CONDITION                   | CHARGE      | Start Normal Charging                                                            | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       |                    | Programmed<br>Current                           | HIGH       | Running         |                          |

| 12     | CHARGE                      | CHARGE      | Timer Defeated. (Low-Battery Conditioning Still Functional)                      | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       |                    | Programmed<br>Current                           | HIGH       | Ignored         | Forced LOW               |

| 13     | SD                          | CHARGE      | Restart                                                                          | >BAT                                                                                                                | $\begin{array}{c} 2.5 \text{V} \leq \text{V}_{\text{BAT}} \leq 3.9 \text{V} \\ (\text{V/Cell}) \end{array}$ |                       | 0                  | Programmed<br>Current                           | HIGH       | Reset           |                          |

| 14     | CHARGE                      | CHARGE      | Top-Off Charging                                                                 | >BAT                                                                                                                | >3.9V/Cell                                                                                                  | 0                     |                    | Programmed<br>Current                           | HIGH       | Running         | LOW                      |

| 15     | CHARGE                      | CHARGE      | C/10 Latch is SET when Battery Current is Less<br>Than 10% of Programmed Current | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       | 1                  | Programmed<br>Current                           | HIGH       | Reset           | 25µА                     |

| 16     | CHARGE                      | CHARGE      | Top-Off Charging                                                                 | >BAT                                                                                                                | >3.9V/Cell                                                                                                  | 1                     |                    | Programmed<br>Current                           | HIGH       | Running         | 25µА                     |

| 17     | CHARGE                      | CHARGE      | Input Current Limited Charging                                                   | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       |                    | <programmed<br>Current (Note 2)</programmed<br> | HIGH       |                 |                          |

| 18     | CHARGE                      | SD          | Charger Paused Due to Thermistor Out of Range                                    | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       |                    | OFF                                             | HIGH       | Paused          | LOW or 25µA<br>(Faulted) |

| 19     | CHARGE                      | SD          | Shut Down by ACP/SHDN Pin                                                        | >BAT                                                                                                                | >2.5V/Cell                                                                                                  |                       | 0                  | OFF                                             | Forced LOW | Reset           | HIGH                     |

| 20     | CHARGE                      | SD          | Terminated by Low-Battery Fault (Note 1)                                         | >BAT                                                                                                                | <2.5V/Cell                                                                                                  |                       | 0                  | OFF                                             | HIGH       | >T/4 then Reset | HIGH<br>(Faulted)        |

| 21     | CHARGE                      | SD          | Terminates After 1/4 T                                                           | >BAT                                                                                                                | V <sub>FLOAT</sub>                                                                                          | 1                     |                    | OFF                                             | HIGH       | >T/4 then Reset | HIGH                     |

| 22     | CHARGE                      | SD          | Terminates After T                                                               | >BAT                                                                                                                | V <sub>FLOAT</sub> **                                                                                       | 0                     |                    | OFF                                             | HIGH       | >T/4 then Reset | HIGH                     |

**Note 1:** If a depleted battery is inserted while the charger is in this state, the charger must be reset to initiate charging.

Note 2: See section on "Adapter Limiting".

**Note 3:** The information contained in this table is supplemental to the LTC4006 data sheet and has not been production qualified.

**Note 4:** Blank fields indicate no change, not considered, or other states impact value.

\*Open Drain. High when used with pull-up resistor.

\*\* Most probable condition.

#### LTC4006: State Diagram (Supplemental)

4006fa

10

be inhibited if it is not already active. If the charging current decreases below 10% to 15% of programmed current, while engaged in input current limiting, BGATE will be forced low to prevent the charger from discharging the battery. Audible noise can occur in this mode of operation.

An overvoltage comparator guards against voltage transient overshoots (>7% of programmed value). In this case, both MOSFETs are turned off until the overvoltage condition is cleared. This feature is useful for batteries which "load dump" themselves by opening their protection switch to perform functions such as calibration or pulse mode charging.

As the voltage at BAT increases to near the input voltage at DCIN, the converter will attempt to turn on the top MOSFET continuously ("dropout"). A watchdog timer detects this condition and forces the top MOSFET to turn off for about 300ns at  $40\mu$ s intervals. This is done to prevent audible noise when using ceramic capacitors at the input and output.

#### Charger Startup

When the charger is enabled, it will not begin switching until the  $I_{TH}$  voltage exceeds a threshold that assures initial current will be positive. This threshold is 5% to 15% of the maximum programmed current. After the charger begins switching, the various loops will control the current at a level that is higher or lower than the initial current. The duration of this transient condition depends upon the loop compensation but is typically less than 100µs.

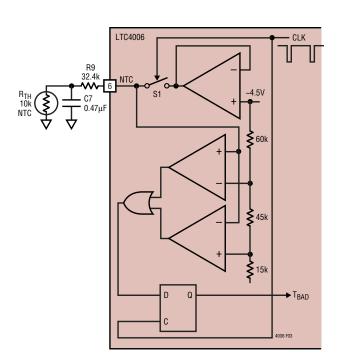

#### **Thermistor Detection**

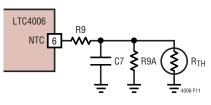

The thermistor detection circuit is shown in Figure 3. It requires an external resistor and capacitor in order to function properly.

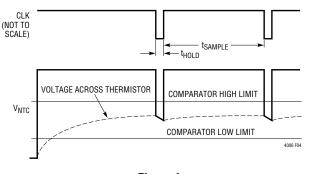

The thermistor detector performs a sample-and-hold function. An internal clock, whose frequency is determined by the timing resistor connected to  $R_T$ , keeps switch S1 closed to sample the thermistor:

$t_{SAMPLE} = 127.5 \bullet 20 \bullet R_{RT} \bullet 17.5 pF = 13.8 ms,$

for  $R_{RT} = 309k$

The external RC network is driven to approximately 4.5V and settles to a final value across the thermistor of:

$V_{RTH(FINAL)} = \frac{4.5V \bullet R_{TH}}{R_{TH} + R9}$

Figure 3

This voltage is stored by C7. Then the switch is opened for a short period of time to read the voltage across the thermistor.

$t_{HOLD} = 10 \bullet R_{RT} \bullet 17.5 pF = 54 \mu s$ , for  $R_{RT} = 309 k$

When the  $t_{HOLD}$  interval ends the result of the thermistor testing is stored in the D flip-flop (DFF). If the voltage at NTC is within the limits provided by the resistor divider feeding the comparators, then the NOR gate output will be low and the DFF will set  $T_{BAD}$  to zero and charging will continue. If the voltage at NTC is outside of the resistor divider limits, then the DFF will set  $T_{BAD}$  to one, the charger will be shut down, and the timer will be suspended until  $T_{BAD}$  returns to zero (see Figure 4).

#### Charger Current Programming

The basic formula for charging current is:

|              | _ | 100mV              |

|--------------|---|--------------------|

| ICHARGE(MAX) | _ | R <sub>SENSE</sub> |

#### Table 3. Recommended R<sub>SENSE</sub> Resistor Values

| OENOE                |                           |                        |  |  |  |  |  |

|----------------------|---------------------------|------------------------|--|--|--|--|--|

| I <sub>MAX</sub> (A) | R <sub>SENSE</sub> (Ω) 1% | R <sub>SENSE</sub> (W) |  |  |  |  |  |

| 1.0                  | 0.100                     | 0.25                   |  |  |  |  |  |

| 2.0                  | 0.050                     | 0.25                   |  |  |  |  |  |

| 3.0                  | 0.033                     | 0.5                    |  |  |  |  |  |

| 4.0                  | 0.025                     | 0.5                    |  |  |  |  |  |

#### Setting the Timer Resistor

The charger termination timer is designed for a range of 1 hour to 3 hours with a  $\pm 15\%$  uncertainty. The timer is programmed by the resistor R<sub>RT</sub> using the following equation:

$t_{TIMER}$  = 10 • 2<sup>27</sup> • R<sub>RT</sub> • 17.5pF (Refer to Figure 5) (seconds)

It is important to keep the parasitic capacitance on the  $R_T$  pin to a minimum. The trace connecting  $R_T$  to  $R_{RT}$  should be as short as possible.

#### CHG Status Output Pin

When the charge cycle starts, the  $\overline{CHG}$  pin is pulled down to ground by an internal N-channel MOSFET that can drive more than 100µA. When the charge current drops to 10% of the full-scale current (C/10), the N-channel MOSFET is turned off and a weak 25µA current source to ground is connected to the  $\overline{CHG}$  pin. After a time out occurs, the pin will go into a high impedance state. By using two different value pull-up resistors, a microprocessor can detect three states from this pin (charging, C/10 and stop charging). See Figure 6.

#### **Battery Detection**

It is generally not good practice to connect a battery while the charger is running. The timer is in an unknown state and the charger could provide a large surge current into the battery for a brief time. The circuit shown in Figure 7 keeps the charger shut down and the timer reset while a battery is not connected.

Figure 6. Microprocessor Interface

#### Soft-Start

The LTC4006 is soft started by the 0.12 $\mu$ F capacitor on the I<sub>TH</sub> pin. On start-up, I<sub>TH</sub> pin voltage will rise quickly to 0.5V, then ramp up at a rate set by the internal 40 $\mu$ A pull-up current and the external capacitor. Battery charging current starts ramping up when I<sub>TH</sub> voltage reaches 0.8V and full current is achieved with I<sub>TH</sub> at 2V. With a 0.12 $\mu$ F capacitor, time to reach full charge current is about 2ms and it is assumed that input voltage to the charger will reach full value in less than 2ms. The capacitor can be increased up to 1 $\mu$ F if longer input start-up times are needed.

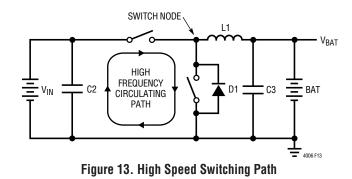

#### **Input and Output Capacitors**

The input capacitor (C2) is assumed to absorb all input switching ripple current in the converter, so it must have adequate ripple current rating. Worst-case RMS ripple current will be equal to one half of output charging current. Actual capacitance value is not critical. Solid tantalum low ESR capacitors have high ripple current rating in a relatively small surface mount package, *but caution must be used when tantalum capacitors are used for input or output bypass*. High input surge currents can be created when the adapter is hot-plugged to the charger or when a battery is connected to the charger. Solid tantalum capacitors have a known failure mechanism when subjected to very high turn-on surge currents. Only Kemet T495 series of "Surge Robust" low ESR tantalums are rated for high surge conditions such as battery to ground.

The relatively high ESR of an aluminum electrolytic for C1, located at the AC adapter input terminal, is helpful in reducing ringing during the hot-plug event. Refer to Application Note 88 for more information.

Highest possible voltage rating on the capacitor will minimize problems. Consult with the manufacturer before use. Alternatives include new high capacity ceramic (at least  $20\mu$ F) from Tokin, United Chemi-Con/Marcon, et al. Other alternative capacitors include OS-CON capacitors from Sanyo.

The output capacitor (C3) is also assumed to absorb output switching current ripple. The general formula for capacitor current is:

$$I_{\text{RMS}} = \frac{0.29(V_{\text{BAT}}) \left(1 - \frac{V_{\text{BAT}}}{V_{\text{DCIN}}}\right)}{(\text{L1})(f)}$$

For example:

$V_{DCIN}$  = 19V,  $V_{BAT}$  = 12.6V, L1 = 10 $\mu H,$  and f = 300kHz,  $I_{RMS}$  = 0.41A.

EMI considerations usually make it desirable to minimize ripple current in the battery leads, and beads or inductors may be added to increase battery impedance at the 300kHz switching frequency. Switching ripple current splits between the battery and the output capacitor depending on the ESR of the output capacitor and the battery impedance. If the ESR of C3 is  $0.2\Omega$  and the battery impedance is raised to  $4\Omega$  with a bead or inductor, only 5% of the current ripple will flow in the battery.

#### **Inductor Selection**

Higher operating frequencies allow the use of smaller inductor and capacitor values. A higher frequency generally results in lower efficiency because of MOSFET gate charge losses. In addition, the effect of inductor value on ripple current and low current operation must also be considered. The inductor ripple current  $\Delta I_L$  decreases with higher frequency and increases with higher V<sub>IN</sub>.

$$\Delta I_{L} = \frac{1}{(f)(L)} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Accepting larger values of  $\Delta I_L$  allows the use of low inductances, but results in higher output voltage ripple and greater core losses. A reasonable starting point for setting ripple current is  $\Delta I_L = 0.4(I_{MAX})$ . In no case should  $\Delta I_L$  exceed 0.6( $I_{MAX}$ ) due to limits imposed by  $I_{REV}$  and CA1. Remember the maximum  $\Delta I_L$  occurs at the maximum input voltage. In practice 10µH is the lowest value recommended for use.

Lower charger currents generally call for larger inductor values. Use Table 4 as a guide for selecting the correct inductor value for your application.

4006f

Table 4

| MAXIMUM<br>Average current (A) | INPUT<br>VOLTAGE (V) | MINIMUM INDUCTOR<br>Value (μH) |

|--------------------------------|----------------------|--------------------------------|

| 1                              | ≤20                  | 40 ±20%                        |

| 1                              | >20                  | 56 ±20%                        |

| 2                              | ≤20                  | 20 ±20%                        |

| 2                              | >20                  | 30 ±20%                        |

| 3                              | ≤20                  | 15 ±20%                        |

| 3                              | >20                  | 20 ±20%                        |

| 4                              | ≤20                  | 10 ±20%                        |

| 4                              | >20                  | 15 ±20%                        |

# Charger Switching Power MOSFET and Diode Selection

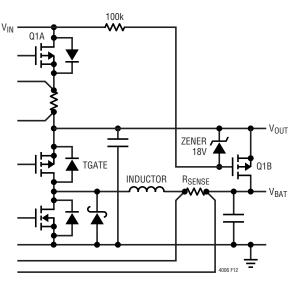

Two external power MOSFETs must be selected for use with the charger: a P-channel MOSFET for the top (main) switch and an N-channel MOSFET for the bottom (synchronous) switch.

The peak-to-peak gate drive levels are set internally. This voltage is typically 6V. Consequently, logic-level threshold MOSFETs must be used. Pay close attention to the  $BV_{DSS}$  specification for the MOSFETs as well; many of the logic level MOSFETs are limited to 30V or less.

Selection criteria for the power MOSFETs include the "ON" resistance  $R_{DS(ON)}$ , total gate capacitance  $Q_G$ , reverse transfer capacitance  $C_{RSS}$ , input voltage and maximum output current. The charger is operating in continuous mode at moderate to high currents so the duty cycles for the top and bottom MOSFETs are given by:

Main Switch Duty Cycle = V<sub>OUT</sub>/V<sub>IN</sub>

Synchronous Switch Duty Cycle =  $(V_{IN} - V_{OUT})/V_{IN}$ .

The MOSFET power dissipations at maximum output current are given by:

$PMAIN = V_{OUT}/V_{IN}(I^{2}_{MAX})(1 + \delta\Delta T)R_{DS(ON)} + k(V^{2}_{IN})(I_{MAX})(C_{RSS})(f_{OSC})$

$\mathsf{PSYNC} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}})/\mathsf{V}_{\mathsf{IN}}(\mathsf{I}^2_{\mathsf{MAX}})(1 + \delta\Delta\mathsf{T})\mathsf{R}_{\mathsf{DS}(\mathsf{ON})}$

Where  $\delta$  is the temperature dependency of  $R_{DS(ON)}$  and k is a constant inversely related to the gate drive current. Both MOSFETs have I^2R losses while the PMAIN equation includes an additional term for transition losses, which are

highest at high input voltages. For V<sub>IN</sub> < 20V the high current efficiency generally improves with larger MOSFETs, while for V<sub>IN</sub> > 20V the transition losses rapidly increase to the point that the use of a higher R<sub>DS(ON)</sub> device with lower C<sub>RSS</sub> actually provides higher efficiency. The synchronous MOSFET losses are greatest at high input voltage or during a short circuit when the duty cycle in this switch is nearly 100%. The term (1 +  $\delta\Delta$ T) is generally given for a MOSFET in the form of a normalized R<sub>DS(ON)</sub> vs temperature curve, but  $\delta = 0.005/^{\circ}$ C can be used as an approximation for low voltage MOSFETs. C<sub>RSS</sub> is usually specified in the MOSFET characteristics; if not, then C<sub>RSS</sub> can be calculated using C<sub>RSS</sub> = Q<sub>GD</sub>/ $\Delta$ V<sub>DS</sub>. The constant k = 2 can be used to estimate the contributions of the two terms in the main switch dissipation equation.

If the charger is to operate in low dropout mode or with a high duty cycle greater than 85%, then the topside P-channel efficiency generally improves with a larger MOSFET. Using asymmetrical MOSFETs may achieve cost savings or efficiency gains.

The Schottky diode D1, shown in the Typical Application on the back page, conducts during the dead-time between the conduction of the two power MOSFETs. This prevents the body diode of the bottom MOSFET from turning on and storing charge during the dead-time, which could cost as much as 1% in efficiency. A 1A Schottky is generally a good size for 4A regulators due to the relatively small average current. Larger diodes can result in additional transition losses due to their larger junction capacitance.

The diode may be omitted if the efficiency loss can be tolerated.

#### **Calculating IC Power Dissipation**

The power dissipation of the LTC4006 is dependent upon the gate charge of the top and bottom MOSFETs ( $Q_{G1}$  and  $Q_{G2}$  respectively). The gate charge is determined from the manufacturer's data sheet and is dependent upon both the gate voltage swing and the drain voltage swing of the MOSFET. Use 6V for the gate voltage swing and V<sub>DCIN</sub> for the drain voltage swing.

$$\mathsf{P}_{\mathsf{D}} = \mathsf{V}_{\mathsf{DCIN}} \bullet (\mathsf{f}_{\mathsf{OSC}} (\mathsf{Q}_{\mathsf{G1}} + \mathsf{Q}_{\mathsf{G2}}) + \mathsf{I}_{\mathsf{DCIN}})$$

Example:

$V_{DCIN}$  = 19V,  $f_{OSC}$  = 345kHz,  $Q_{G1}$  =  $Q_{G2}$  = 15nC. PD = 292mW  $I_{DCIN}$  = 5mA

#### Adapter Limiting

An important feature of the LTC4006 is the ability to automatically adjust charging current to a level which avoids overloading the wall adapter. This allows the product to operate at the same time that batteries are being charged without complex load management algorithms. Additionally, batteries will automatically be charged at the maximum possible rate of which the adapter is capable.

This feature is created by sensing total adapter output current and adjusting charging current downward if a preset adapter current limit is exceeded. True analog control is used, with closed-loop feedback ensuring that adapter load current remains within limits. Amplifier CL1 in Figure 9 senses the voltage across  $R_{CL}$ , connected

Figure 9. Adapter Current Limiting

| Table 5. | Common     | Bei | <b>Resistor Values</b> |

|----------|------------|-----|------------------------|

|          | 0011111011 |     |                        |

between the CLP and DCIN pins. When this voltage exceeds 100mV, the amplifier will override programmed charging current to limit adapter current to 100mV/R<sub>CL</sub>. A lowpass filter formed by  $5k\Omega$  and 15nF is required to eliminate switching noise. If the current limit is not used, CLP should be connected to CLN.

#### **Setting Input Current Limit**

To set the input current limit, you need to know the minimum wall adapter current rating. Subtract 7% for the input current limit tolerance and use that current to determine the resistor value.

R<sub>CL</sub> = 100mV/I<sub>LIM</sub> I<sub>LIM</sub> = Adapter Min Current – (Adapter Min Current • 7%)

As is often the case, the wall adapter will usually have at least a +10% current limit margin and many times one can simply set the adapter current limit value to the actual adapter rating (see Figure 9).

#### **Designing the Thermistor Network**

There are several networks that will yield the desired function of voltage vs temperature needed for proper operation of the thermistor. The simplest of these is the voltage divider shown in Figure 10. Unfortunately, since the HIGH/LOW comparator thresholds are fixed internally, there is only one thermistor type that can be used in this network; the thermistor must have a HIGH/LOW resistance ratio of 1:7. If this happy circumstance is true for

| Table 5. Common R <sub>CL</sub> Resistor values |                           |                                  |                              |                                          |                                     |  |  |  |

|-------------------------------------------------|---------------------------|----------------------------------|------------------------------|------------------------------------------|-------------------------------------|--|--|--|

| ADAPTER<br>RATING (A)                           | -7% ADAPTER<br>Rating (A) | R <sub>CL</sub> VALUE*<br>(Ω) 1% | R <sub>CL</sub><br>Limit (A) | R <sub>CL</sub> POWER<br>DISSIPATION (W) | R <sub>CL</sub> POWER<br>Rating (W) |  |  |  |

| 1.5                                             | 1.40                      | 0.068                            | 1.47                         | 0.15                                     | 0.25                                |  |  |  |

| 1.8                                             | 1.67                      | 0.062                            | 1.61                         | 0.16                                     | 0.25                                |  |  |  |

| 2.0                                             | 1.86                      | 0.051                            | 1.96                         | 0.20                                     | 0.25                                |  |  |  |

| 2.3                                             | 2.14                      | 0.047                            | 2.13                         | 0.21                                     | 0.25                                |  |  |  |

| 2.5                                             | 2.33                      | 0.043                            | 2.33                         | 0.23                                     | 0.50                                |  |  |  |

| 2.7                                             | 2.51                      | 0.039                            | 2.56                         | 0.26                                     | 0.50                                |  |  |  |

| 3.0                                             | 2.79                      | 0.036                            | 2.79                         | 0.28                                     | 0.50                                |  |  |  |

| 3.3                                             | 3.07                      | 0.033                            | 3.07                         | 0.31                                     | 0.50                                |  |  |  |

| 3.6                                             | 3.35                      | 0.030                            | 3.35                         | 0.33                                     | 0.50                                |  |  |  |

| 4.0                                             | 3.72                      | 0.027                            | 3.72                         | 0.37                                     | 0.50                                |  |  |  |

\* Rounded to nearest 5% standard step value. Many non-standard values are popular.

Figure 10. Voltage Divider Thermistor Network

you, then simply set  $R9 = R_{TH(LOW)}$

If you are using a thermistor that doesn't have a 1:7 HIGH/ LOW ratio, or you wish to set the HIGH/LOW limits to different temperatures, then the more generic network in Figure 11 should work.

Once the thermistor,  $R_{TH}$ , has been selected and the thermistor value is known at the temperature limits, then resistors R9 and R9A are given by:

For NTC thermistors:

$$R9 = 6 R_{TH(LOW)} \bullet R_{TH(HIGH)} / (R_{TH(LOW)} - R_{TH(HIGH)})$$

$$\label{eq:R9A} \begin{split} &R9A = 6 \, R_{TH(LOW)} \bullet R_{TH(HIGH)} / (R_{TH(LOW)} - 7 \bullet R_{TH(HIGH)}) \\ & \text{where } R_{TH(LOW)} > 7 \bullet R_{TH(HIGH)} \end{split}$$

For PTC thermistors:

$R9 = 6 R_{TH(LOW)} \bullet R_{TH(HIGH)} / (R_{TH(HIGH)} - R_{TH(LOW)})$

$\begin{array}{l} R9A = 6\,R_{TH(LOW)} \bullet R_{TH(HIGH)} / (R_{TH(HIGH)} - 7 \bullet R_{TH(LOW)}) \\ where \,\,R_{TH(HIGH)} > 7R_{TH(LOW)} \end{array}$

Example #1:  $10k\Omega$  NTC with custom limits

```

TLOW = 0°C, THIGH = 50°C

R_{TH} = 10k \text{ at } 25°C,

R_{TH(LOW)} = 32.582k \text{ at } 0°C

R_{TH(HIGH)} = 3.635k \text{ at } 50°C

R9 = 24.55k \rightarrow 24.3k \text{ (nearest } 1\% \text{ value)}

R9A = 99.6k \rightarrow 100k \text{ (nearest } 1\% \text{ value)}

```

### Example #2: $100k\Omega$ NTC

TLOW = 5°C, THIGH = 50°C  $R_{TH} = 100k \text{ at } 25°C$ ,  $R_{TH(LOW)} = 272.05k \text{ at } 5°C$   $R_{TH(HIGH)} = 33.195k \text{ at } 50°C$   $R9 = 226.9k \rightarrow 226k \text{ (nearest } 1\% \text{ value)}$  $R9A = 1.365M \rightarrow 1.37M \text{ (nearest } 1\% \text{ value)}$

Example #3:  $22k\Omega$  PTC

TLOW =  $0^{\circ}$ C, THIGH =  $50^{\circ}$ C

Figure 11. General Thermistor Network

$\begin{array}{ll} R_{TH} &= 22k \mbox{ at } 25^\circ C, \\ R_{TH(LOW)} &= 6.53k \mbox{ at } 0^\circ C \\ R_{TH(HIGH)} &= 61.4k \mbox{ at } 50^\circ C \\ R9 &= 43.9k \rightarrow 44.2k \mbox{ (nearest } 1\% \mbox{ value}) \\ R9A &= 154k \end{array}$

#### Sizing the Thermistor Hold Capacitor

During the hold interval, C7 must hold the voltage across the thermistor relatively constant to avoid false readings. A reasonable amount of ripple on NTC during the hold interval is about 10mV to 15mV. Therefore, the value of C7 is given by:

$$C7 = t_{HOLD}/(R9/7 \bullet -In(1 - 8 \bullet 15mV/4.5V))$$

= 10 • R<sub>BT</sub> • 17.5pF/(R9/7 • -In(1 - 8 • 15mV/4.5V)

Example:

R9 = 24.3k R<sub>RT</sub> = 309k (~2 hour timer) C7 =  $0.57\mu F \rightarrow 0.56\mu F$  (nearest value)

### **Disabling the Thermistor Function**

If the thermistor is not needed, connecting a resistor between DCIN and NTC will disable it. The resistor should be sized to provide at least  $10\mu$ A with the minimum voltage applied to DCIN and 10V at NTC. Do not exceed  $30\mu$ A into NTC. Generally, a 301k resistor will work for DCIN less than 15V. A 499k resistor is recommended for DCIN between 15V and 24V.

### **Optional Simple Battery Discharge Path Circuit**