Data Sheet

Fully Integrated 10Gbps Serializer/Deserializer Device

#### August 2004

Corporation

Semiconductor

### Features

- Single chip SERDES solution with integrated transmitter and receiver

- Continuous serial operation range from 9.95 Gbps to 10.31 Gbps

- Parallel LVDS data range from 622 Mbps to 644 Mbps

- Low power consumption (800 mW typical)

- Performs 16:1 serialization and 1:16 deserialization

- Embedded Limiting Amplifier enhances receiver sensitivity

- Low-jitter PLL for clock generation

- On-chip Clock Data Recovery circuit

- On-chip FIFO to decouple transmit clocks

- Bit order swap for 10GE operations

- Programmable 4-phase LVDS clock output for easy system design

- Repeating serial data output

- Line loopback, diagnostic loopback, and simultaneous loopback modes

- Frequency Lock Alarm Output

- Programmable differential output swing on both Serial driver and Parallel LVDS driver

- 1.3V core voltage and 2.5V I/O voltage

- Supports 10GE (10-Gigabit Ethernet), OC-192, XFP, XSBI and SFI-4.1 interfaces

- 269-pin flip-chip BGA (15 x 15 mm body size, 0.8 mm pitch)

- -40 to 85°C operating temperature

# **General Description**

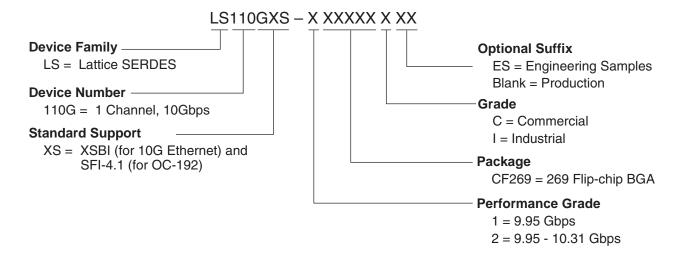

The XPIO<sup>™</sup> 110GXS is a fully integrated 10 Gbps serializer/deserializer device designed for high-speed switches and routers that require very low power budget and a small footprint as well. Centering on 10 Gbps speed, the XPIO 110GXS is a versatile chip that is capable of handling applications in various standards, such as OC-192 (9.95 Gbps) and 10GE (10.31 Gbps).

An on-chip low jitter PLL generates all required clocks based on an external reference clock at 1/16 or 1/64 frequency of the serial data rate, which is 622.08 MHz or 155.52 MHz, respectively, for OC-192 applications. An Integrated Limiting Amplifier allows flexibility in placement and reduced bit-error rates (BER).

Fabricated with state-of-the-art CMOS technology, the XPIO 110GXS performs all necessary functions for serial-to-parallel and parallel-to-serial conversions, and consumes less than one third of the power consumed by the more conventional SiGe Bi-CMOS designs.

### Overview

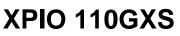

The XPIO 110GXS consists primarily of blocks of parallel-to-serial and serial-to-parallel functions plus system timing. Low Voltage Differential Signaling (LVDS) is used for parallel signal input and output while Current Mode Logic (CML) is used for serial transmission and reception. A limiting amplifier is designed into the chip to improve serial receiver sensitivity. The system timing blocks consist of the clock-multiplier-unit (CMU), LVPLL (LVDS interface timing Phase-Lock-Loop) and CDR (clock-data-recovery) units, which generate clocks for the chip. Figure 1 shows the XPIO 110GXS chip block diagram.

Table 1. XPIO 110GXS Supported Protocols

| Device      | Standards Supported | Data Rate               |

|-------------|---------------------|-------------------------|

| XPIO 110GXS | OC-192<br>10GE      | 9.95 Gbps<br>10.31 Gbps |

<sup>© 2004</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

The XPIO 110GXS is divided into a transmitter section and a receiver section. The major operations performed by the chip are:

#### Transmitter Operation

- 1. Low jitter clock generation via the Clock-Multiplier-Unit (CMU)

- 2. 16-bit LVDS parallel data input

- 3. Parallel-to-serial conversion

- 10Gbps CML serial data output

### **Receiver Operation**

- 1. CML serial input to a limiting amplifier

- 2. Clock and data recovery

- 3. Serial-to-parallel conversion

- 4. 16-bit LVDS parallel data output, with a synchronizing clock output

- 5. Built-in LVDS line loopback, and LVDS diagnostic loopback modes for testing and network diagnosis

# **Functional Description**

The XPIO 110GXS transceiver is a low power, low jitter, and fully integrated serializer/deserializer chip. It operates in the data rate range of 9.95-10.31 Gbps, performs all necessary parallel-to-serial and serial-to-parallel conversions. The chip is suitable for applications utilizing OC-192 and 10GE. The serial interface I/O uses the CML standard while the low speed parallel I/O is based on the LVDS standard. These standards are compliant to both the Optical Interface Forum's SFI-4 standard and the 10GE's XSBI standard. The LVDS parallel I/O can be directly connected to Multi-Standard-Agreement (MSA) 300 systems.

To accommodate bit order differences between OC-192 and 10GE, the XPIO 110GXS provides the capability of bit swapping. The data presented on  $TX_D_LV_P/N[15]$  or MSB is transmitted first, followed in order by  $TX_D_LV_P/N[14]$  to  $TX_D_LV_P/N[0]$  when SC\_LSB1STb is not connected or is connected to a logic high.  $TX_D_LV_P/N[0]$  or LSB is transmitted first followed in order by  $TX_D_LV_P/N[1]$  to  $TX_D_LV_P/N[15]$  when SC\_LSB1STb is connected to a logic low. The parallel receive bus mirrors this behavior. The SC\_LSB1STb unconnected, or at logic high, the first serial bit received is presented on RX\_D\_LV\_P/N[15]. Conversely the first bit received is presented on RX\_D\_LV\_P/N[15].

### Transmitter

The transmitter performs the serialization process, converting the 16-bit parallel LVDS data stream to a serial data stream at approximately a 10 Gbps data rate. The transmitter consists of a LVDS data receiver, a FIFO, a 16:1 serializer, a low jitter CMU, and a 10Gbps output data driver.

### LVDS Data Receiver

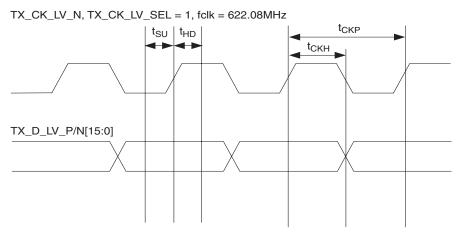

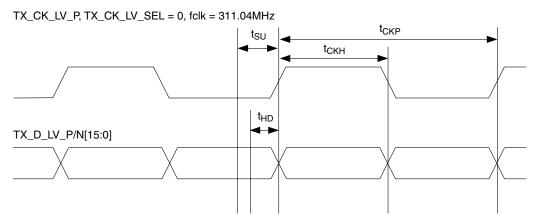

The Input and Analog Pin Assignments and Descriptions table in this document shows the 16 LVDS differential data input pairs ( $TX_D_LV_P/N$  [15:0]). Data applied at the transmit data pairs is aligned to the LVDS input clock ( $TX_CK_LV_P/N$ ), which can be either 1/16th or 1/32nd the transmit data rate (622.08 or 311.04 nominally for OC-192). The clock rate is selected through the assertion or deassertion of the  $TX_CK_LV_SEL$  pin. Figure 13 describes the LVDS data relationship to the LVDS input clock.

The LVDS input receivers convert the LVDS signals to CMOS signals. The converted signals are latched based on an internal clock that is generated from the TX\_CK\_LV\_P/N input clock through a phase-lock-loop (LVPLL). In order to achieve optimal latch timing, the phase relationship between the internal clock and the TX\_CK\_LV\_P/N clock can be adjusted by programming TX\_CK\_LV\_PA[1:0]. The LVDS PLL can also be bypassed by the assertion of the TX\_LV\_PLLBPb pin, which is a desirable feature in some applications. When the LVPLL is bypassed it is up to the system designer to manage the TX\_CK\_LV\_P/N input.

### **Transmitter FIFO**

A 16 bit wide and 8-word deep FIFO is designed into the XPIO 110GXS to decouple the LVDS clock from the serial transmission clock. In addition, the FIFO also improves the tolerance to minor phase differences between the FIFO write clock and read clock due to phase drift or phase wander.

### Lattice Semiconductor

The FIFO circuitry indicates an overflow or underflow condition by asserting TX\_FIFO\_ERR high. The TX\_FIFO\_ERR only provides status information about an overflow or underflow. It does not indicate which of the two events actually occurred. During the period of time when the TX\_FIFO\_ERR signal is asserted, the TX\_D\_P/N pins toggle at a constant rate. This prevents the AC coupling capacitors from becoming blocking capacitors.

The transmit FIFO's read and write pointers can be recentered by asserting the TX\_FIFO\_INIT pin high. Thus, one way to automatically recenter the FIFO read/write pointers after TX\_FIFO\_ERR is asserted is to connect TX\_FIFO\_INIT and TX\_FIFO\_ERR together.

The FIFO read/write pointers are re-centered after:

- Device power on reset

- Transmitter reset (asserting RESET\_TXb low)

- CMU PLL is out of lock

#### Serialization

The output data bus from the FIFO feeds a 16:1 serializer to generate a 9.953 Gbps (OC-192 rate) data stream. The high-speed clock (TX\_CLK) is a low jitter clock generated by the CMU. The serializer uses TX\_CLK to clock out high-speed data.

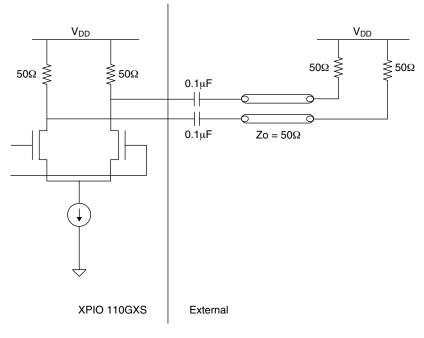

#### **TX CML Driver**

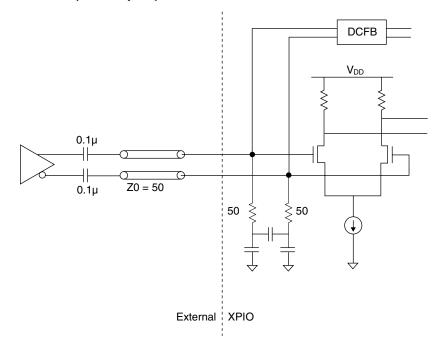

The serial data stream in turn becomes an input to a differential high-speed CML data driver. The TX\_D CML driver incorporates an internal 50-ohm termination resistor on both P and N branches for impedance matching with the PCB transmission line. The CML output may require AC coupling (as in Figure 5). The output current of the CML driver can be adjusted using two configuration pins, TX\_CML\_ISET[1:0]. These configuration pins are used to balance power consumption and performance.

In normal operation, the data presented at the LVDS TX inputs requires about nine clocks to transit the various logic blocks before being presented at the TX CML driver output.

#### Clock-Multiplier-Unit (CMU)

The CMU consists of a differential PLL that is capable of producing a very low jitter serial clock. The clock is generated through a reference clock (REF\_CLK\_P/N) at either 1/16<sup>th</sup> or 1/64<sup>th</sup> the data transmission rate (This is nominally 622.08 or 155.52 MHz for OC-192 data rates). This reference clock must be generated from a differential crystal oscillator that has a frequency accuracy of better than ±20ppm for SONET applications.

The CMU PLL can provide a phase-adjustable parallel data rate clock (CK622OUT\_P/N) that is 1/16<sup>th</sup> the transmit data rate to clock other devices or systems. The output of CK622OUT\_P/N meets the LVDS signaling specifications. Using the TX\_CK622\_PA[1:0] configuration pins, the phase can be adjusted in T/4 increments, where T is the period of the clock for the parallel interface.

#### Receiver

#### Limiting Amplifier

The XPIO 110GXS 10 Gbps CMOS receiver integrates a highly sensitive limiting amplifier. The XPIO 110GXS also implements an amplifier offset compensation technology that works in conjunction with the limiting amplifier to achieve superior amplifier input sensitivity. Sufficient gain is designed into the limiting amplifier to detect a peak-to-peak differential input as small as 50mV. This attenuated signal can be properly detected and amplified to saturation.

#### Clock and Data Recovery (CDR)

One of the most critical circuits in the receiver is the clock and data recovery (CDR) block. The CDR block extracts the clock from an incoming high-speed, non-return to zero (NRZ) data, and retimes the data based on an external reference clock. Extraction of the clock embedded in the serial data-stream is performed through comparison of the phase relationship between transitions of the data and the external reference clock.

### Lattice Semiconductor

The external reference clock is essential for the CDR block. The reference clock provides two functions: One function is training the VCO in the CDR PLL to the serial data-stream frequency. The other is to generate a stable clock when the input serial data is absent. The CDR PLL creates an internal reference frequency. The reference frequency is monitored, and a loss of lock is asserted when it goes out of specification.

### Lock Detect

The XPIO 110GXS implements a CDR lock detector circuit that monitors the frequency of the internal clock. RX\_LOCK is asserted whenever a REF\_CK or RX\_REF\_CK are operating within specification. RX\_LOCK is deas-serted under some specific circumstances:

- 1. When RX\_RESETb is asserted (i.e. '0')

- 2. When the REF\_CK (or RX\_REF\_CK) is not present.

- 3. When the clock recovered from the incoming datastream falls outside the range specified by the SC\_LOCK\_DIFF input pins. When the recovered clock is out of range, RX\_LOCK will deassert briefly and then be reasserted as it relocks to the REF\_CK (RX\_REF\_CK). This effectively leaves the RX\_LOCK signal toggling as it attempts to reacquire the clock embedded in the RX\_D\_P/N data inputs.

#### Deserialization

The XPIO 110GXS uses a 1:16 demultiplexer to deserialize the high speed data from the CDR. The demultiplexer generates the 16 bit parallel data stream. The bit order presented on the  $RX_D_LV_P/N[0..15]$  LVDS outputs mirrors the order on the  $TX_D_LV[0..15]P/N$  LVDS inputs. The first data bit received by the CDR is present on  $RX_D_LV_P/N[15]$  when SC\_LSB1STb is connected to a logic high, and it is present on  $RX_D_LV_P/N[0]$  when SC\_LSB1STb is connected to a logic high.

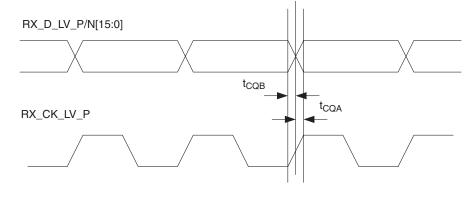

#### LVDS Data Transmitter

The 16-bit parallel data and clock are sent out via the RX\_D\_LV\_P/N[0..15] and RX\_LV\_CK\_P/N LVDS pins, respectively. Data on the RX\_D\_LV\_P/N pins is synchronous to the RX\_LV\_CK\_P/N output pins. The data coming in on the RX\_D\_P/N pins requires around five clocks to arrive at the RX\_D\_LV\_P/N outputs. The output current of the LVDS outputs is adjustable using the SC\_LV\_ISET[1:0] configuration pins. System designers can use these pins to optimize the LVDS receive data performance.

#### XFP Module Considerations

The XPIO110GXS was conceived and implemented prior to the finalization of the XFP specification. The implication of this is the CML TX voltage swing is typically higher than that specified in the XFP MSA documents.

The XFP MSA specification indicates a XFP module should accept a maximum of 800mV input swing. In practice it is the individual XFP module internal architecture that defines the maximum range. However, most XFP modules simply rate themselves to the 800mV specification regardless of the likelihood they may operate beyond the range specified in the XFP MSA.

Actual operation of the XPIO110GXS with existing XFP modules shows these still operate with the CML swing set to the default  $TX\_CML\_ISET[1:0] = "11"$ . In order to more closely match the XFP specification a  $TX\_CML\_ISET[1:0] = "01"$  configuration is recommended. This places the typical output swing from the CML TX outputs at 650mV to 1100mV.

### **Loopback Operation**

The XPIO 110GXS supports several loopback operations to provide diagnostic functions and to aid in performing SONET/SDH functional tests.

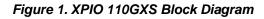

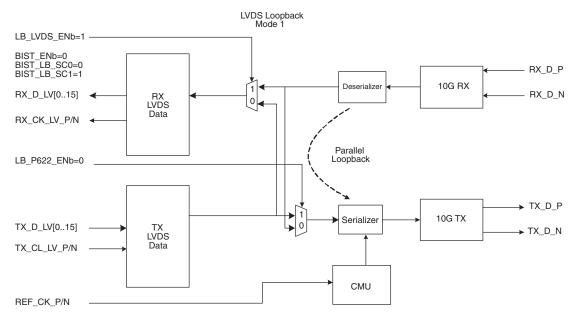

#### LVDS Diagnostic Loopback

In LVDS loopback mode, 16 bit-wide data is fed into the TX LVDS input. The XPIO 110GXS routes data from the LVDS transmit interface to the internal receiver interface, and then repeats the data at the LVDS RX output.

To enable this mode of operation set BIST\_ENb=0, LB\_LVDS\_ENb=0, and BIST\_LB\_SC[1:0]=10.

Figure 2. LVDS Loopback Mode Block Diagram

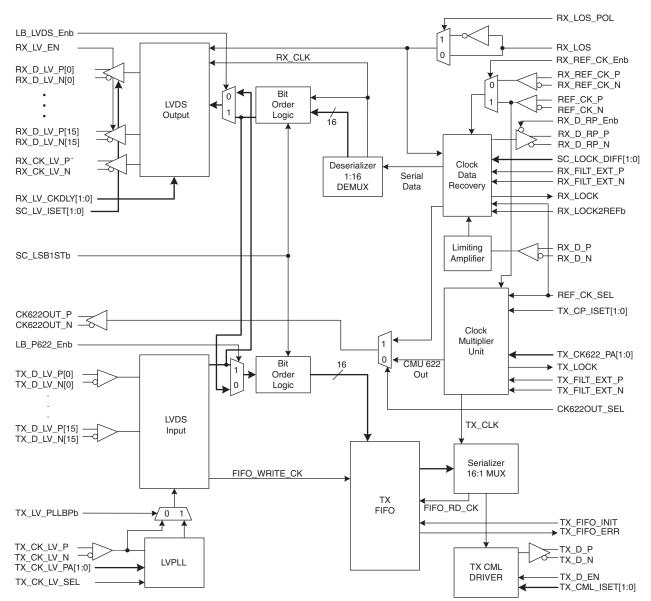

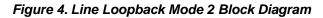

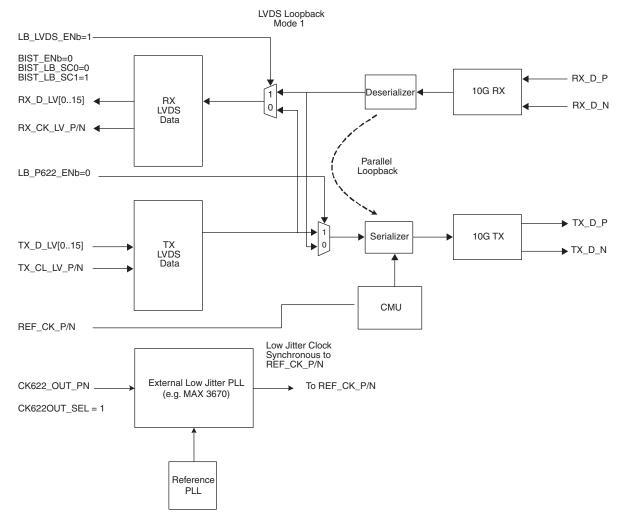

## LVDS Line Loopback

Line loopback is a diagnostic mode that establishes a parallel connection between the output of the deserializer and the input to the serializer. When this mode is active, serial receive data is deserialized, and internally looped back to the serializer. The data provided at the serializer is transmitted via the CML output. Line loopback is activated by setting the LB\_P622\_Enb pin to a logic low.

*Mode 1: Synchronous line loopback without clock clean-up.* Driving LB\_P622\_Enb low enables line loopback mode. Connecting the LVDS output clock, RX\_CK\_LV\_P/N, to REF\_CK\_P/N makes the loopback mode synchronous. In addition, a separate reference clock is input to RX\_REF\_CKP/N for use by the CDR logic. The data transmitted across the TX\_D\_P/N pins is now timed to the LVDS clock making the RX and TX data synchronous. However, the RX\_CK\_LV\_P/N does not require SONET/SDH tolerance in order to transmit the parallel LVDS data. This means the data repeated on TX\_D\_P/N will have significant jitter.

Figure 3. Line Loopback Mode 1 Block Diagram

# Lattice Semiconductor

*Mode 2: Synchronous line loopback with clock clean-up.* Driving LB\_P622\_Enb low enables line loopback mode. In order to make this loopback mode SONET/SDH compliant the CK622OUT\_P/N must be connected to a VCXO-powered PLL chip (e.g. MAX3670), and CK622OUT\_SEL pulled/driven high. The output of the PLL provides a low jitter reference clock that is in phase with the data presented at the LVDS parallel outputs. This reference clock is connected to REF\_CK\_P/N. As in Mode 1 a separate reference clock is input to RX\_REF\_CK\_P/N to drive the CDR logic. Data on the TX\_D\_P/N and RX\_D\_P/N pins are now synchronous, and the data repeated on TX\_D\_P/N meets SONET/SDH line loopback application requirements.

# **Reference Clocks**

There are two AC coupled reference clock input pairs, REF\_CK\_P/N, and RX\_REF\_CK\_P/N. The CDR block is driven by either REF\_CK\_P/N or RX\_REF\_CK\_P/N. The CMU block is only driven by REF\_CK\_P/N. The reference clock input frequency for REF\_CK\_P/N can be either 1/16<sup>th</sup> (622MHz) or 1/64<sup>th</sup> (155MHz) the transmitter/receiver data rate. Likewise, RX\_REF\_CK\_P/N can be 1/16<sup>th</sup> or 1/64<sup>th</sup> the 10Gbps receiver rate. RX\_REF\_CK\_P/N and REF\_CK\_P/N are configured in tandem to 1/16<sup>th</sup> or 1/64<sup>th</sup> by REF\_CK\_SEL. They cannot be configured independently. AC coupling for all reference clocks is recommended.

# Lattice Semiconductor

Driving RX\_REF\_CK\_P/N is only necessary when:

- The transmitter and receiver run at independent data rates

- Line Loopback Mode 1 is active

- Line Loopback Mode 2 is active

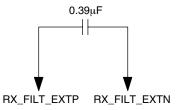

Figure 5 shows how a reference clock is input to the XPIO 110GXS using an AC coupling scheme.

### Figure 5. CML Output Driver Termination (AC Coupled)

Figure 6. CML Input Receiver (AC Coupled)

# Figure 7. Differential Oscillator Driving to XPIO 110GXS Clock Input (AC Coupled)

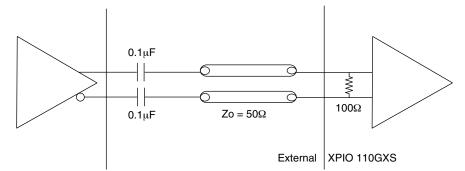

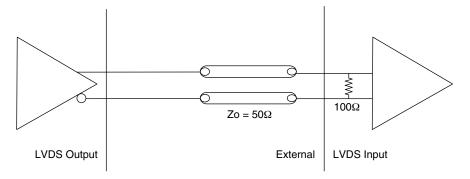

Figure 8. LVDS Output and Input Connection

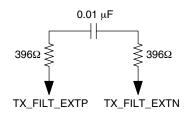

#### Figure 9. External Loop Filter Components

### **PCB Layout Recommendations**

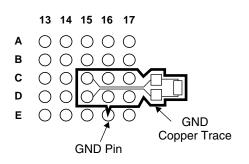

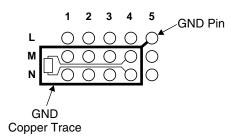

The TX/RX filter components should be small form factor capacitors and resistors. They should be placed as close as possible to the XPIO 110 device.

The TX filter components should be surrounded by a copper trace to GND. As shown below, the RX filter components should be enclosed by the GND.

### Figure 10. PCB Layout Examples

#### TX External Filter PCB Layout Example

RX External Filter PCB Layout Example

Bottom View These diagrams for example purposes only.

# **Electrical Specifications**

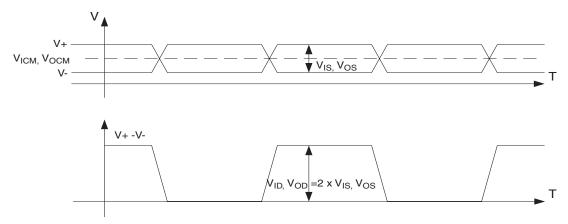

# **AC Signaling Definitions**

Figure 11. Differential Voltage Measurements

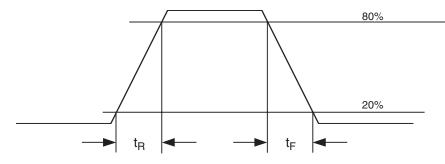

Figure 12. Rise and Fall Time Measurements

Figure 13. LVDS Data to Clock Relationship of Transmitter, 1/16<sup>th</sup> of Frequency (622.08MHz for OC-192)

Note: TX\_D\_LV\_P/N[15:0] is latched using the rising edge of TX\_CK\_LV\_N.

# Figure 14. LVDS Data to Clock Relationship of Transmitter, 1/32<sup>nd</sup> of Frequency (311.04MHz for OC-192)

#### Figure 15. LVDS Data to Clock Relationship of Receiver

# **Configuration Pin Descriptions**

| Pin Name                      | State                               | Action                                                                                                            |

|-------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| <b>Transmitter Controls</b>   | I                                   |                                                                                                                   |

|                               | 1                                   | TX_D_P/N output is active                                                                                         |

| TX_D_EN                       | 0                                   | TX_D_P/N output is inactive.                                                                                      |

|                               | 1                                   | The internal LVDS PLL is active                                                                                   |

| TX_LV_PLLBPb                  | 0                                   | The internal LVDS PLL is bypassed. External clock management and phase adjustment is required when this pin is 0. |

| TX_FIFO_INIT                  | 1                                   | Initialize the TXFIFO                                                                                             |

|                               | 0                                   | No action                                                                                                         |

|                               | 11                                  |                                                                                                                   |

| TX_CML_ISET[1:0]              | 10                                  | See V <sub>OD</sub> in the High Speed Input/Output Specifications section of this                                 |

|                               | 01                                  | data sheet.                                                                                                       |

|                               | 00                                  |                                                                                                                   |

|                               | 11                                  | 3T/4 <sup>2</sup>                                                                                                 |

| TX_CK622_PA[1:0] <sup>1</sup> | 10                                  | Adjust T/2                                                                                                        |

|                               | 01                                  | Adjust T/4                                                                                                        |

|                               | 00                                  | No Adjust                                                                                                         |

| RESET_TXb                     | 1                                   | Transmitter in normal operation                                                                                   |

|                               | 0                                   | Resets the transmitter                                                                                            |

| PWDN_TXb                      | 1                                   | Transmitter is operating                                                                                          |

|                               | 0                                   | Transmitter is powered down                                                                                       |

| TX_CK_LV_SEL                  | 1                                   | TX_CK_LV is 1/16 of frequency                                                                                     |

|                               | 0                                   | TX_CK_LV is 1/32 of frequency                                                                                     |

|                               | TX_CK_LV_SEL = 1/16 <sup>th</sup> o |                                                                                                                   |

|                               | 11                                  | Clock delay = 0                                                                                                   |

|                               | 10                                  | Clock delay = -T/16                                                                                               |

|                               | 01                                  | Clock delay = T/16                                                                                                |

| TX_CK_LV_PA[1:0]              | 00                                  | Clock delay = T/8                                                                                                 |

|                               | $TX_CK_LV_SEL = 1/32^{nd}$ of       | of Frequency                                                                                                      |

|                               | 11                                  | Clock delay = T/4                                                                                                 |

|                               | 10                                  | Clock delay = T/4-T/32                                                                                            |

|                               | 01                                  | Clock delay = T/4+T/32                                                                                            |

|                               | 00                                  | Clock delay = T/4+T/16                                                                                            |

|                               | 11                                  | 622MHz clock (default using internal pull-ups)                                                                    |

| TX_CP_ISET[1:0]               | 10                                  | Invalid                                                                                                           |

|                               | 01                                  | Invalid                                                                                                           |

|                               | 00                                  | 155MHz clock                                                                                                      |

| Receiver Controls             | •                                   |                                                                                                                   |

| RX_REF_CK_ENb                 | 1                                   | RX_REF_CK is disabled                                                                                             |

|                               | 0                                   | RX_REF_CK is enabled                                                                                              |

|                               | 11                                  | LVDS output clock is delayed: 90ps                                                                                |

|                               | 10                                  | LVDS output clock is delayed: 180ps                                                                               |

| RX_LV_CKDLY[1:0]              | 01                                  | LVDS output clock is delayed: 270ps                                                                               |

|                               | 00                                  | LVDS output clock is delayed: 360ps                                                                               |

# **Configuration Pin Descriptions (Continued)**

| Pin Name                       | State                                                 |                                                                                       | Action                                                            |  |  |  |

|--------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| L                              |                                                       | RX_LOS_POL = 0                                                                        | RX_LOS_POL = 1                                                    |  |  |  |

| DY LOS                         | 1                                                     | Asserted by the receiver to indi-<br>cate it has lost the data signal.                | Receiver OK                                                       |  |  |  |

| RX_LOS -                       | 0                                                     | Receiver OK                                                                           | Asserted by the receiver to indicate it has lost the data signal. |  |  |  |

|                                | 1                                                     | RX_LOS is an active-low input                                                         |                                                                   |  |  |  |

| RX_LOS_POL                     | 0                                                     | RX_LOS is an active-high input.                                                       |                                                                   |  |  |  |

|                                | 1                                                     | RX_D_RP_P/N signals are inacti                                                        | ve                                                                |  |  |  |

| RX_D_RP_ENb                    | 0                                                     | RX_D_RP_P/N signals are active                                                        | 2                                                                 |  |  |  |

|                                | 1                                                     | RX_PLL locks to the recovered re                                                      | eceive data clock.                                                |  |  |  |

| RX_LOCK2REFb <sup>3</sup>      | 0                                                     | RX_PLL locks to the REF_CK or                                                         | RX_REF_CK input                                                   |  |  |  |

|                                | 11                                                    |                                                                                       |                                                                   |  |  |  |

|                                | 10                                                    | See LOCK <sub>TOL</sub> in the High Speed                                             | Input/Output Specifications section of                            |  |  |  |

| SC_LOCK_DIFF[1:0] <sup>3</sup> | 01                                                    | this data sheet.                                                                      |                                                                   |  |  |  |

| -                              | 00                                                    | -                                                                                     |                                                                   |  |  |  |

|                                | 11                                                    |                                                                                       |                                                                   |  |  |  |

|                                | 10                                                    | See V <sub>OS</sub> in the Low Speed Input/Output Specifications section of this data |                                                                   |  |  |  |

| SC_LV_ISET[1:0]                | 01                                                    | sheet.                                                                                |                                                                   |  |  |  |

| -                              | 00                                                    |                                                                                       |                                                                   |  |  |  |

|                                | 1                                                     | RX_D_LV_P/N[15:0] are enabled                                                         |                                                                   |  |  |  |

| RX_LV_EN                       | 0                                                     | RX_D_LV_P/N[15:0] are disabled                                                        | 1                                                                 |  |  |  |

|                                | 1                                                     | Receiver is operating                                                                 |                                                                   |  |  |  |

| PWDN_RXb                       | 0                                                     | Receiver is powered down                                                              |                                                                   |  |  |  |

|                                | 1                                                     | Receiver normal operation                                                             |                                                                   |  |  |  |

| RESET_RXb                      | 0                                                     | Resets the receiver logic.                                                            |                                                                   |  |  |  |

| General Controls               |                                                       | 1                                                                                     |                                                                   |  |  |  |

|                                | 1                                                     | CK622 sourced by CDR                                                                  |                                                                   |  |  |  |

| CK622OUT_SEL                   | 0                                                     | CK622 sourced by CMU                                                                  |                                                                   |  |  |  |

| SC LODISTS                     | 1                                                     | TX_D_LV_P/N[15] transmitted ov<br>RX_D_LV_P/N[15] first bit receive<br>cations)       | er TX_D_P/N first<br>ed from RX_D_P/N (e.g. SONET appli-          |  |  |  |

| SC_LSB1STb -                   | 0                                                     | TX_D_LV_P/N[0] transmitted ove<br>RX_D_LV_P/N[0] first bit received<br>tions)         | r TX_D_P/N first<br>d from RX_D_P/N (e.g. 10GE applica-           |  |  |  |

|                                | 1                                                     | REF_CK is 1/16 of frequency (62                                                       | 2.08MHz for OC-192)                                               |  |  |  |

| REF_CK_SEL <sup>4</sup>        | 0                                                     | REF_CK is 1/64 of frequency (15                                                       | 5.52MHz for OC-192)                                               |  |  |  |

| DICT ENH                       | 1 Normal operation, built-in self tests are disabled. |                                                                                       |                                                                   |  |  |  |

| BIST_ENb                       | 0                                                     | Built-in self test enabled. Enable                                                    | this for LVDS loopback mode only.                                 |  |  |  |

|                                | 11                                                    | Invalid                                                                               |                                                                   |  |  |  |

|                                | 10                                                    | LVDS loopback mode enable                                                             |                                                                   |  |  |  |

| BIST_LB_SC[1:0]                | 01                                                    | Invalid                                                                               |                                                                   |  |  |  |

|                                | 00                                                    | Invalid                                                                               |                                                                   |  |  |  |

|                                |                                                       | L                                                                                     |                                                                   |  |  |  |

1. Only available when CK622OUT\_SEL = 0 (CMU CLK Mode).

2. T = period

Locks to REF\_CK when RX\_REF\_CK\_Enb = 1. Locks to RX\_REF\_CK when RX\_REF\_CK\_Enb = 0.

Applies to RX\_REF\_CK also.

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| 1.3V Supply Voltage                          |

|----------------------------------------------|

| 2.5V Supply Voltage                          |

| DC Input Voltage (Differential Inputs)       |

| DC Input Voltage (LVCMOS Inputs)             |

| Output Current (Differential Outputs) ±50 mA |

| Output Current (LVCMOS Outputs) ±15 mA       |

| Storage Temperature                          |

| Case Temperature Under Bias                  |

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied (while programming, following the programming specifications).

- 2. Thermal characteristics, maximum ratings, and thermal compliance requirements can be found in the Lattice *Thermal Management* document.

- 3. All voltages referenced to GND.

# **Recommended Operating Conditions**

| Parameter                        | Symbol                                 | Test Condition | Min. | Тур. | Max. | Units |

|----------------------------------|----------------------------------------|----------------|------|------|------|-------|

| Ambient Temperature (Commercial) | T <sub>A</sub>                         |                | 0    |      | 70   | °C    |

| Ambient Temperature (Industrial) | T <sub>A</sub>                         |                | -40  |      | 85   | °C    |

| 1.3V Supply Voltage              | VDDAR<br>VDDAT<br>VDDL<br>VDDT<br>VDDR |                | 1.23 | 1.30 | 1.37 | V     |

| 2.5V Supply Voltage              | VDDAT25<br>VDDAR25<br>VDDH             |                | 2.37 | 2.5  | 2.63 | V     |

# **Electrical Characteristics**

# **High Speed Input/Output Specifications**

### **Over Recommended Operating Conditions**

| Symbol                                                                                                | Parameter                                                                                        | Test Conditions                                                    | Min.   | Тур.  | Max.                | Units           |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|-------|---------------------|-----------------|

| AC Chara                                                                                              | cteristics                                                                                       |                                                                    |        |       |                     |                 |

| t <sub>R</sub>                                                                                        | CML output rise time                                                                             | See Figure 12.                                                     | —      | 35    | 45                  | ps              |

| t <sub>F</sub>                                                                                        | CML output fall time                                                                             | See Figure 12.                                                     | —      | 35    | 45                  | ps              |

| ſ                                                                                                     | Input reference clock frequency                                                                  | REF_CK_SEL = 1                                                     | 622.08 | —     | 644.53              | MHz             |

| f <sub>REFCLK</sub>                                                                                   | (REF_CK_P/N)                                                                                     | REF_CK_SEL = 0                                                     | 155.52 |       | 161.13              | MHz             |

|                                                                                                       | Receiver input reference clock                                                                   | REF_CK_SEL = 1                                                     | 622.08 | —     | 644.53              | MHz             |

| f <sub>REFCLK</sub>                                                                                   | frequency (RX_REF_CK_P/N, active only in applications where REF_CK_P/N is used as a transmitter) | REF_CK_SEL = 0                                                     | 155.52 | _     | 161.13              | MHz             |

| t <sub>DCREF</sub>                                                                                    | Reference clock duty cycle                                                                       |                                                                    | 40     | _     | 60                  | %               |

| $\Delta f_{REFCLK}$                                                                                   | Reference clock frequency tolerance                                                              |                                                                    | -100   | _     | 100                 | ppm             |

| DC Chara                                                                                              | cteristics                                                                                       |                                                                    |        |       |                     |                 |

| V <sub>COM</sub>                                                                                      | Serial output common mode voltage<br>(TX_D_P/N)                                                  | V <sub>DDT</sub> = 1.3V, See Figure 11.                            | 0.65   | _     | 1.0                 | V               |

|                                                                                                       | Serial output differential voltage swing<br>(TX_D_P/N)                                           | V <sub>DDT</sub> = 1.3V,<br>TX_CML_ISET[1:0]=11,<br>See Figure 11. | 1100   |       | 1750                | mV<br>- (pk-pk) |

| V <sub>OD</sub>                                                                                       |                                                                                                  | V <sub>DDT</sub> = 1.3V,<br>TX_CML_ISET[1:0]=10                    | 1000   |       | 1500                |                 |

|                                                                                                       |                                                                                                  | V <sub>DDT</sub> = 1.3V,<br>TX_CML_ISET[1:0]=01                    | 650    |       | 1100                |                 |

|                                                                                                       |                                                                                                  | V <sub>DDT</sub> = 1.3V,<br>TX_CML_ISET[1:0]=00                    | 1250   |       | 1800                |                 |

| V <sub>ID</sub>                                                                                       | Serial input differential voltage swing (RX_D_P/N)                                               | See Figure 11.                                                     | 50     | _     | 2000                | mV<br>(pk-pk)   |

| V <sub>ICM</sub>                                                                                      | Serial input common mode voltage (RX_D_P/N)                                                      | See Figure 11.                                                     | 0.75   | _     | 1.15                | V               |

| V <sub>ID</sub>                                                                                       | Input voltage differential swing for<br>(REF_CK_P/N, RX_REF_CK_P/N)                              | See Figure 11.                                                     | 250    | _     | 2400                | mV<br>(pk-pk)   |

| Performa                                                                                              | nce Characteristics                                                                              | •                                                                  |        |       |                     | •               |

| J <sub>GEN</sub>                                                                                      | Transmitter jitter generation (peak to peak)                                                     |                                                                    | —      | 0.085 | —                   | UI              |

| t <sub>ACQ</sub>                                                                                      | Transmitter CMU PLL acquisition time                                                             |                                                                    | —      | 10    | _                   | μS              |

|                                                                                                       |                                                                                                  | SC_LOCK_DIFF[1:0] = 11                                             | —      | 1200  |                     | ppm             |

|                                                                                                       | Frequency difference at which receiver PLL                                                       | SC_LOCK_DIFF[1:0] = 10                                             | —      | 600   | _                   | ppm             |

| VICM     S<br>(f       VID     Ir<br>(F       Performance       JGEN     TI       t <sub>ACQ</sub> TI | goes out of lock                                                                                 | SC_LOCK_DIFF[1:0] = 01                                             | —      | 1200  |                     | ppm             |

|                                                                                                       |                                                                                                  | SC_LOCK_DIFF[1:0] = 00                                             | —      | 600   |                     | ppm             |

| J <sub>TOL</sub>                                                                                      | Receiver jitter tolerance                                                                        |                                                                    | Ex     |       | ONET Jit<br>ce Mask | ter             |

| t <sub>ACQ</sub>                                                                                      | Receiver PLL acquisition time                                                                    |                                                                    | —      | 10    | _                   | μS              |

Note: Reference clock input characteristics should meet the following requirements for SONET/SDH applications:

-125 dBc/HZ @ 1 MHz offset

-105 dBc/HZ @ 100 KHz offset

# **Electrical Characteristics (Continued)**

# Low Speed Input/Output Specifications

#### . Over Recommended Operating Conditions

| Symbol              | Parameter                                                                               | Test Conditions                                                                 | Min. | Тур.   | Max. | Units         |

|---------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|--------|------|---------------|

| AC Chara            | acteristics                                                                             |                                                                                 |      |        |      |               |

| t <sub>R</sub>      | LVDS output rise times                                                                  | See Figure 12.                                                                  | _    | 120    | 250  | ps            |

| t <sub>F</sub>      | LVDS output fall times                                                                  | See Figure 12.                                                                  |      | 120    | 250  | ps            |

| t <sub>CQB</sub>    | LVDS output data invalid prior to LVDS out-<br>put clock                                | See Figure 15.                                                                  | _    | _      | 150  | ps            |

| t <sub>CQA</sub>    | LVDS output data invalid after LVDS output clock                                        | See Figure 15.                                                                  | _    | —      | 150  | ps            |

| f <sub>CLKOUT</sub> | LVDS output clock frequency, OC192 rate<br>(CK622OUT_P/N, RX_CK_LV_P/N)                 |                                                                                 | _    | 622.08 | _    | MHz           |

| t <sub>DCCLK</sub>  | LVDS output clock frequency duty cycle<br>(CK622OUT_P/N, RX_CK_LV_P/N)                  | t <sub>СКН</sub> /t <sub>СКР</sub><br>See Figure 13.                            | 45   | —      | 55   | %             |

| t <sub>R</sub>      | LVDS input rise times                                                                   | See Figure 12.                                                                  |      | —      | 300  | ps            |

| t <sub>F</sub>      | LVDS input fall times                                                                   | See Figure 12.                                                                  | —    | —      | 300  | ps            |

|                     | LVDS input data setup to LVDS input                                                     | See Figure 13.<br>TX_CK_LV_SEL =1,<br>TX_CK_LV_PA[1:0]=11                       | 260  | _      | _    | ps            |

| t <sub>SU</sub>     | clock                                                                                   | t <sub>SU</sub><br>See Figure 13.<br>TX_CK_LV_SEL =0 and<br>TX_CK_LV_PA[1:0]=11 | 320  | _      | _    | ps            |

| 4                   | 5 LVDS input data hold from LVDS input clock                                            | See Figure 13.<br>TX_CK_LV_SEL =1 and<br>TX_CK_LV_PA[1:0]=11                    | 260  | _      | _    | ps            |

| t <sub>HD</sub>     |                                                                                         | See Figure 13.<br>TX_CK_LV_SEL =0 and<br>TX_CK_LV_PA[1:0]=11                    | 150  | _      | _    | ps            |

| f                   | LVDS input clock frequency at OC-192 rate                                               | TX_CK_LV_SEL is no connect<br>or high                                           | _    | 622.08 | —    | MHz           |

| f <sub>CLK</sub>    | (TX_CK_LV_P/N)                                                                          | TX_CK_LV_SEL is<br>connected to low                                             | _    | 311.04 | _    | MHz           |

| t <sub>DCCLK</sub>  | LVDS input clock frequency duty cycle<br>(TX_CK_LV_P/N)                                 | t <sub>СКН</sub> /t <sub>СКР</sub><br>See Figure 13.                            | 45   | —      | 55   | %             |

| DC Chara            | acteristics                                                                             |                                                                                 |      |        |      |               |

| V <sub>OCM</sub>    | LVDS transmitter common mode range<br>RX_D_LV_P/N[15:0], RX_CK_LV_P/N,<br>TX_CK622_P/N) | 100 $\Omega$ load on line-to-line See Figure 11.                                | 0.95 | _      | 1.3  | v             |

|                     |                                                                                         | See Figure 11. 100Ω load on<br>line-to-line,<br>SC_LV_ISET[1:0]=11              | 100  | _      | 165  | mV<br>(pk-pk) |

| Maria               | LVDS single-ended output voltage swing                                                  | See Figure 11. 100Ω load on<br>line-to-line,<br>SC_LV_ISET[1:0]=10              | 50   | _      | 100  | mV<br>(pk-pk) |

| V <sub>OS</sub>     | (RX_D_LV_P/N[15:0], RX_CK_LV_P/N)                                                       | See Figure 11. 100Ω load on<br>line-to-line,<br>SC_LV_ISET[1:0]=01              | 80   | _      | 125  | mV<br>(pk-pk) |

|                     |                                                                                         | See Figure 11. 100Ω load on<br>line-to-line,<br>SC_LV_ISET[1:0]=00              | 130  | _      | 210  | mV<br>(pk-pk) |

# **Electrical Characteristics (Continued)**

# Low Speed Input/Output Specifications (Continued)

### **Over Recommended Operating Conditions**

| Symbol           | Parameter                                                                  | Test Conditions | Min. | Тур. | Max. | Units         |

|------------------|----------------------------------------------------------------------------|-----------------|------|------|------|---------------|

| V <sub>ICM</sub> | LVDS receiver common mode range<br>(TX_D_LV_P/N[15:0], TX_CK_LV_P/N)       | See Figure 11.  | 0.9  | _    | 1.6  | V             |

| V <sub>IH</sub>  | LVDS input voltage HIGH<br>(TX_D_LV_P/N[15:0], TX_CK_LV_P/N)               |                 | _    | _    | 2.4  | V             |

| V <sub>IS</sub>  | LVDS single-ended input voltage swing<br>(TX_D_LV_P/N[15:0], TX_CK_LV_P/N) | See Figure 11.  | 100  | _    | 600  | mV<br>(pk-pk) |

# LVCMOS Input/Output Specifications

### **Over Recommended Operating Conditions**

| Symbol          | Parameter                    | Test Conditions | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|-----------------|------|------|------|-------|

| V <sub>IH</sub> | LVCMOS input high voltage    |                 | 1.6  | —    | 2.6  | V     |

| V <sub>IL</sub> | LVCMOS input low voltage     |                 | 0    | —    | 0.8  | V     |

| I <sub>IH</sub> | LVCMOS input high current    |                 |      |      | 10   | μA    |

| I <sub>IL</sub> | LVCMOS input low current     |                 | _    | —    | 10   | μA    |

| V <sub>OH</sub> | LVCMOS output high voltage   | With 4mA load   | 2.0  | —    | 2.5  | V     |

| V <sub>OL</sub> | LVCMOS output low voltage    | With 4mA load   | 0    | _    | 0.4  | V     |

| I <sub>PU</sub> | LVCMOS input pull-up current |                 | 90   | _    | 170  | μA    |

# **Power Supply Specifications**

### **Over Recommended Operating Conditions**

| Symbol                         | Parameter           | Test Conditions | Min. | Тур. | Max. | Units |

|--------------------------------|---------------------|-----------------|------|------|------|-------|

| P <sub>D</sub>                 | Power dissipation   |                 | _    | 0.8  | 1.05 | W     |

| I <sub>DD13</sub> <sup>1</sup> | 1.3V supply current |                 | —    | 390  | 460  | mA    |

| I <sub>DD25</sub> <sup>2</sup> | 2.5V supply current |                 | —    | 130  | 160  | mA    |

1. 1.3V power supplies, including VDDAR, VDDAT, VDDL, VDDT, VDDR.

2. 2.5V power supplies, including VDDAR25, VDDAT25, VDDH.

# **Common Pin Assignments and Descriptions<sup>4</sup>**

| Pad Name            | Pin Description                      | Flip-chip BGA Ball Number⁴                                                                                                                                                                                                                  |

|---------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | RX analog circuit ground             | E16, K14, L14, M15                                                                                                                                                                                                                          |

| GND <sup>1, 3</sup> | TX analog circuit ground             | F3, L5                                                                                                                                                                                                                                      |

|                     | I/O ground                           | D8, D9, E8, F7, F8, G8, H7, H8, H9, H10, J8, J9, J10, K8, K9, K10, L9, L10, M10, N10, P10, R10, R11, R12                                                                                                                                    |

| GND',°              | Logic circuit ground                 | C1, D12, D13, J12, M12, M16, N7, N14, P14, P15, R1                                                                                                                                                                                          |

|                     | PLL ground                           | C12                                                                                                                                                                                                                                         |

|                     | High-speed limit amplifier ground    | F14, G13, H13, J14                                                                                                                                                                                                                          |

|                     | High-speed transmitter driver ground | F4, G5, H5, J4, K4, L4                                                                                                                                                                                                                      |

| VDDAR               | RX analog circuit power              | E11, F10, J15, J16                                                                                                                                                                                                                          |

| VDDAT               | TX analog circuit power              | M1, R8                                                                                                                                                                                                                                      |

| VDDH                | I/O power                            | C4, C5, C6, C7, C8, C9, C10, C11, D5, D10, D11, K11, L7, L8, L11, M6, M7, M8, M9, M11, N11, N12, P9, P11, P12                                                                                                                               |

| VDDL                | Logic circuit power                  | D4, E6, L12, R15, E10                                                                                                                                                                                                                       |

| VDDR                | High-speed limit amplifier power     | F15, F16                                                                                                                                                                                                                                    |

| VDDT                | High-speed transmitter driver power  | J2, J3, M3                                                                                                                                                                                                                                  |

| VDDAR25             | Reference circuit power              | J11                                                                                                                                                                                                                                         |

| VDDAT25             | Reference circuit power              | F1                                                                                                                                                                                                                                          |

| NC <sup>2</sup>     | No connect                           | C2, C14, C15, C16, C17, D1, D14, D16, E1, E2, E4, E7, E13, E14, F5,<br>F6, F12, F13, F17, G4, G6, G10, G11, H4, H6, H12, J7, J13, J17, K5,<br>K6, K7, K12, K13, L6, L13, M2, M13, N2, N3, N5, N8, N9, N17, P3, P4,<br>P7, P16, P17, R2, R14 |

1. All grounds must be electrically connected at the board level.

2. NC pins should not be connected to any active signals,  $\mathrm{V}_{\mathrm{DD}}$  or GND.

3. Balls for GND, VDDAR, VDDAT, VDDH, VDDL, VDDR, VDDT, VDDAR25 and VDDAT25 are connected within the substrate to their respective common signals.

4. Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

# **Output Pin Assignments and Descriptions**

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin Description                                                                                                                                                                                                                                                  | Function       | Flip-chip<br>BGA Ball #                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_D_N<br>TX_D_P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 Gbps CML transmit data. See Figure 5.                                                                                                                                                                                                                         | CML/<br>Out    | K3<br>L3                                                                                                                                                                      |

| TX_LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TX PLL lock indicator:<br>TX LOCK = 1, internal TX_CLK locked to REF_CLK;<br>TX LOCK = 0, PLL is unlocked.                                                                                                                                                       | LVCMOS/<br>Out | D7                                                                                                                                                                            |

| CK622OUT_N<br>CK622OUT_P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 622 MHz LVDS clock output. Phase is adjustable <sup>1</sup> and locks to CMU or CDR clock. <sup>2</sup>                                                                                                                                                          | LVDS/<br>Out   | R4<br>R5                                                                                                                                                                      |

| RX_CK_LV_P<br>RX_CK_LV_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LVDS clock output. Clock is source synchronous to the LVDS receive, runs at 622MHz and is phase adjustable.                                                                                                                                                      | LVDS/<br>Out   | U9<br>T9                                                                                                                                                                      |

| RX_D_LV_N[15], RX_D_LV_P[15],<br>RX_D_LV_N[14], RX_D_LV_P[14],<br>RX_D_LV_N[13], RX_D_LV_P[13],<br>RX_D_LV_N[12], RX_D_LV_P[12],<br>RX_D_LV_N[11], RX_D_LV_P[12],<br>RX_D_LV_N[0], RX_D_LV_P[10],<br>RX_D_LV_N[9], RX_D_LV_P[0],<br>RX_D_LV_N[9], RX_D_LV_P[9],<br>RX_D_LV_N[6], RX_D_LV_P[8],<br>RX_D_LV_N[6], RX_D_LV_P[6],<br>RX_D_LV_N[6], RX_D_LV_P[6],<br>RX_D_LV_N[5], RX_D_LV_P[6],<br>RX_D_LV_N[4], RX_D_LV_P[5],<br>RX_D_LV_N[3], RX_D_LV_P[4],<br>RX_D_LV_N[2], RX_D_LV_P[3],<br>RX_D_LV_N[2], RX_D_LV_P[2],<br>RX_D_LV_N[0], RX_D_LV_P[0] | LVDS data output. See Figure 8.                                                                                                                                                                                                                                  | LVDS/<br>Out   | T1, U1,<br>T2, U2<br>T3, U3<br>T4, U4<br>T5, U5<br>T6, U6<br>T7, U7<br>T8, U8<br>T10, U10<br>T11, U11<br>T12, U12<br>T13, U13<br>T14, U14<br>T15, U15<br>T16, U16<br>T17, U17 |

| RX_LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Receiver PLL lock indicator. The PLL locks to<br>REF_CK/RX_REF_CK.<br>RX_LOCK = 1, receiver PLL frequency is within 300 ppm;<br>RX_LOCK = 0, receiver PLL frequency is larger than 450 ppm;<br>Frequency difference range is adjustable by<br>SC_LOCK_DIFF[1:0]. | LVCMOS/<br>Out | M17                                                                                                                                                                           |

| RX_D_RP_P <sup>3</sup><br>RX_D_RP_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 Gbps CML output, repeat data. This output repeats the data at the $RX_D_P/N$ inputs when $RX_D_RP_Enb = 0$ . This output can be used for diagnostic purposes and to evaluate the receivers limiting amplifier. These pins can be left unconnected if unused.  | CML/<br>Out    | H14<br>G14                                                                                                                                                                    |

| TX_FIFO_ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FIFO error. 1 = error, 0 = normal operation.                                                                                                                                                                                                                     | LVCMOS/<br>Out | D6                                                                                                                                                                            |

1. CMU mode only.

2. Based on RX\_REF\_CK\_Enb

3. Operation above 10.3Gbps is not supported.

# Input and Analog Pin Assignments and Descriptions<sup>1</sup>

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin Description                                                                                                                                                                                          | Function               | Flip-chip<br>BGA<br>Ball #                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RX_D_P, RX_D_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 Gbps CML input.                                                                                                                                                                                       | CML/In                 | L15, K15                                                                                                                                                                     |  |