## LTC6602

INOLOGY Dual Matched, High Frequency Bandpass/Lowpass Filters

### FEATURES

- Matched Dual Filter/Driver, Ideal for RFID Readers

- Guaranteed Phase Matching to Within 2 Degrees

- Guaranteed Gain Matching to Within 0.2dB

- Configurable as Lowpass or Bandpass Programmable 5th Order Lowpass: 42kHz to 900kHz Programmable 4th Order Highpass: 4.2kHz to 90kHz

- Programmable Gain: 1×, 4×, 16×, 32×

- Simple Pin Programming or SPI Interface

- Low Noise: –145dBm/Hz (Input Referred)

- Low Distortion: –75dBc at 200kHz

- Differential, Rail-to-Rail Inputs and Outputs

- Input Range Extends from 0V to 5V

- Low Voltage Operation: 2.7V to 3.6V

- Shutdown Mode

- 4mm × 4mm QFN Package

### **APPLICATIONS**

- Multiprotocol RFID Readers: EPC-GEN2, ISD and IPX

- IDEN, PHS, GSM Basestations

- Repeaters, Radio Links, and Modems

- Wireless Telemetry

- JTRS

### DESCRIPTION

The LTC<sup>®</sup>6602 is a dual, matched, programmable bandpass or lowpass filter and differential driver. The selectivity of the LTC6602, combined with its phase matching and dynamic range, make it ideal for filtering in RFID systems. With two degree phase matching between channels, the LTC6602 can be used in applications requiring highly matched filters, such as transceiver I and Q channels. Gain programmability, and the fully differential inputs and outputs, simplify implementation in most systems.

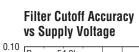

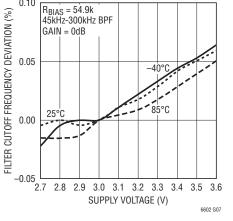

Both channels of the LTC6602 consist of a programmable lowpass and highpass filter. For bandpass functionality, the lowpass filters are programmed for the upper cutoff frequency. For lowpass functionality, the highpass filters can be bypassed. The filter cutoff frequencies can be set with a guaranteed accuracy of 3% with the use of a single resistor. Alternatively, the filter cutoff frequencies can be controlled with an external clock.

The LTC6602 operates on a single 2.7V to 3.6V supply and features a low power shutdown mode.

$\boldsymbol{\mathcal{I}}$ , LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners..

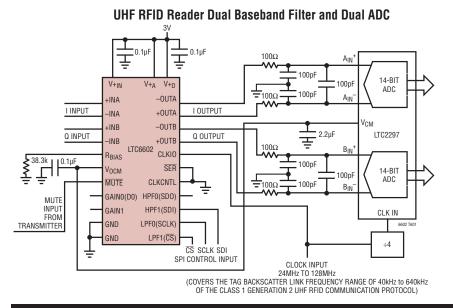

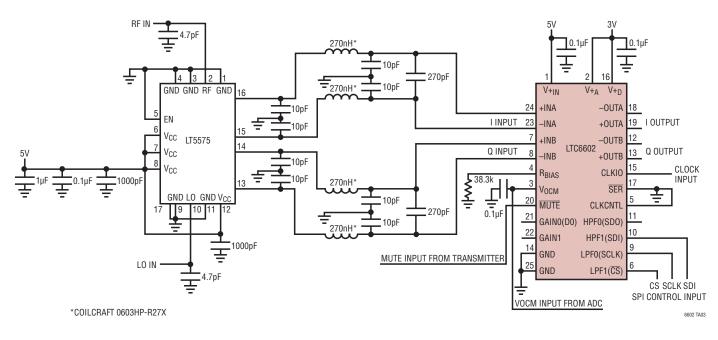

### TYPICAL APPLICATION

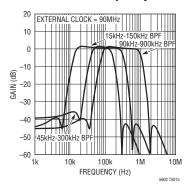

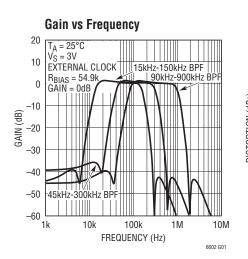

#### Gain vs Frequency

### **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                             |                                          |

|--------------------------------------|------------------------------------------|

| V+IN to GND                          | 6V                                       |

| $V_{+A}$ , $V_{+D}$ to GND           | 4V                                       |

| Filter Inputs to GND0.3              | 3V to V+ <sub>IN</sub> + 0.3V            |

| All Other Pins to GND0.3V to         | V+ <sub>A</sub> , V+ <sub>D</sub> + 0.3V |

| Maximum Input Current                | ±10mA                                    |

| Output Short Circuit Duration        | Indefinite                               |

| Operating Temperature Range (Note 2) |                                          |

| LTC6602CUF                           | –40°C to 85°C                            |

| LTC6602IUF                           | –40°C to 85°C                            |

| Specified Temperature Range (Note 3) |                                          |

| LTC6602CUF                           | 0°C to 70°C                              |

| LTC6602IUF                           | –40°C to 85°C                            |

| Storage Temperature Range            | 65°C to 150°C                            |

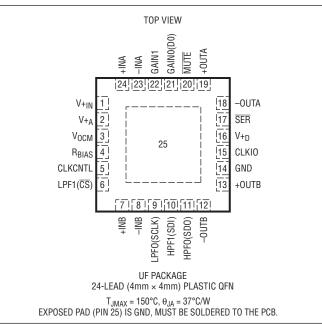

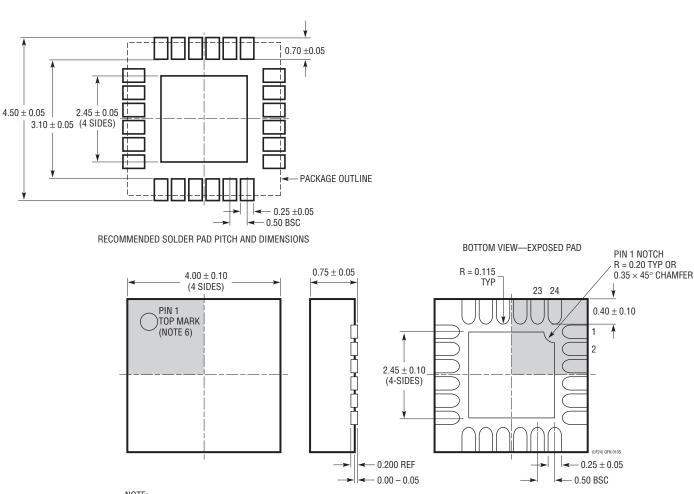

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH TAPE AND REEL |                  | PART MARKING* | PACKAGE DESCRIPTION             | SPECIFIED TEMPERATURE RANGE |

|--------------------------------|------------------|---------------|---------------------------------|-----------------------------|

| LTC6602CUF#PBF                 | LTC6602CUF#TRPBF | 6602          | 24-Lead (4mm × 4mm) Plastic QFN | 0°C to 70°C                 |

| LTC6602IUF#PBF                 | LTC6602IUF#TRPBF | 6602          | 24-Lead (4mm × 4mm) Plastic QFN | –40°C to 85°C               |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which app ly over the full operating

temperature range, otherwise specifications are at  $T_A = 25$  °C.  $V_{+A} = V_{+D} = V_{+IN} = 3V$ ,  $V_{ICM} = V_{0CM} = 1.5V$ , Gain = 0dB, lowpass cutoff = 300kHz, highpass cutoff = 45kHz, internal clocking with  $R_{BIAS} = 54.9k$  unless otherwise noted.

| PARAMETER CONDITIONS                     |                                                                                                                                                                                                                              |             |                     | ТҮР                             | MAX                               | UNITS                      |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|---------------------------------|-----------------------------------|----------------------------|

| Filter Gain Either Channel<br>Gain = 0dB | External Clock = 90MHz, Highpass Filter Cutoff = 45kHz,<br>Lowpass Filter Cutoff = 300kHz, $V_{IN}$ = 3.6 $V_{P-P}$<br>$f_{IN}$ = 22.5kHz<br>$f_{IN}$ = 45kHz<br>$f_{IN}$ = 150kHz<br>$f_{IN}$ = 300kHz<br>$f_{IN}$ = 900kHz | •<br>•<br>• | -1.8<br>0.1<br>-2.7 | -32<br>-1.2<br>0.5<br>-2<br>-44 | -30<br>-0.8<br>0.8<br>-1.2<br>-43 | dB<br>dB<br>dB<br>dB<br>dB |

| Matching of Filter Gain                  | External Clock = 90MHz, Highpass Filter Cutoff = 45kHz,<br>Lowpass Filter Cutoff = 300kHz, $V_{IN}$ = 3.6 $V_{P-P}$<br>$f_{IN}$ = 45kHz<br>$f_{IN}$ = 150kHz<br>$f_{IN}$ = 300kHz                                            | •           |                     |                                 | ±0.2<br>±0.2<br>±0.2              | dB<br>dB<br>dB             |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{+A} = V_{+D} = V_{+IN} = 3V$ ,  $V_{ICM} = V_{OCM} = 1.5V$ , Gain = OdB, lowpass cutoff = 300kHz, highpass cutoff = 45kHz, internal clocking with  $R_{BIAS} = 54.9k$  unless otherwise noted.

| PARAMETER                                | CONDITIONS                                                                                                                                                                                                                                                                                                                   |   | MIN                  | ТҮР                               | MAX                               | UNITS                      |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|-----------------------------------|-----------------------------------|----------------------------|

| Filter Phase<br>Either Channel           | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-B}$ Highpass Filter Cutoff = 45kHz,<br>Lowpass Filter Cutoff = 300kHz<br>$f_{IN}$ = 50kHz<br>$f_{IN}$ = 250kHz                                                                                                                                                                  | • | 125<br>-134          | 130<br>-130                       | 134<br>-126                       | deg<br>deg                 |

| Matching of Filter Phase                 | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 45kHz,<br>Lowpass Filter Cutoff = 300kHz<br>$f_{IN}$ = 50kHz<br>$f_{IN}$ = 250kHz                                                                                                                                                                | • |                      |                                   | ±2<br>±1.5                        | deg<br>deg                 |

| Filter Gain Either Channel<br>Gain = OdB | External Clock = 90MHz, Highpass Filter Cutoff = 15kHz,<br>Lowpass Filter Cutoff = 150kHz, $V_{IN}$ = 3.6 $V_{P-P}$<br>$f_{IN}$ = 7.5kHz<br>$f_{IN}$ = 15kHz<br>$f_{IN}$ = 50kHz<br>$f_{IN}$ = 150kHz<br>$f_{IN}$ = 450kHz                                                                                                   |   | -1.6<br>0.4<br>-2.3  | -32<br>-1.2<br>0.7<br>-1.9<br>-44 | -30<br>-0.8<br>0.9<br>-1.3<br>-43 | dB<br>dB<br>dB<br>dB<br>dB |

| Matching of Filter Gain                  | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 15kHz,<br>Lowpass Filter Cutoff = 150kHz<br>$f_{IN}$ = 15kHz<br>$f_{IN}$ = 50kHz<br>$f_{IN}$ = 150kHz                                                                                                                                            | • |                      |                                   | ±0.2<br>±0.2<br>±0.2              | dB<br>dB<br>dB             |

| Filter Phase Either<br>Channel           | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 15kHz,<br>Lowpass Filter Cutoff = 150kHz<br>$f_{IN}$ = 16.5kHz<br>$f_{IN}$ = 125kHz                                                                                                                                                              | • | 137<br>142           | 142<br>-138                       | 146<br>-134                       | deg<br>deg                 |

| Matching of Filter Phase                 | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 15kHz,<br>Lowpass Filter Cutoff = 150kHz<br>$f_{IN}$ = 16.5kHz<br>$f_{IN}$ = 125kHz                                                                                                                                                              | • |                      |                                   | ±2<br>±1                          | deg<br>deg                 |

| Filter Gain Either Channel<br>Gain = 0dB | $ \begin{array}{l} \mbox{External Clock} = 90\mbox{MHz}, \mbox{Highpass Filter Cutoff} = 90\mbox{Hz}, \mbox{Lowpass Filter Cutoff} = 90\mbox{Hz}, \mbox{V}_{IN} = 3.6\mbox{V}_{P-P} \\ f_{IN} = 45\mbox{Hz} \\ f_{IN} = 90\mbox{Hz} \\ f_{IN} = 300\mbox{Hz} \\ f_{IN} = 90\mbox{Hz} \\ f_{IN} = 2700\mbox{Hz} \end{array} $ |   | -1.8<br>-0.1<br>-2.1 | -29<br>-1.2<br>0.6<br>-1.1<br>-45 | -27<br>-0.7<br>1.2<br>-0.5<br>-44 | dB<br>dB<br>dB<br>dB<br>dB |

| Matching of Filter Gain                  | External Clock = 90MHz, Highpass Filter Cutoff = 90kHz,<br>Lowpass Filter Cutoff = 900kHz, $V_{IN} = 3.6V_{P-P}$<br>$f_{IN} = 90kHz$<br>$f_{IN} = 300kHz$<br>$f_{IN} = 900kHz$                                                                                                                                               | • |                      |                                   | ±0.3<br>±0.6<br>±0.4              | dB<br>dB<br>dB             |

| Filter Phase Either Chanel               | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 90kHz,<br>Lowpass Filter Cutoff = 900kHz<br>$f_{IN}$ = 100kHz<br>$f_{IN}$ = 750kHz                                                                                                                                                               | • | 136<br>136           | 141<br>–131                       | 145<br>-127                       | deg<br>deg                 |

| Matching of Filter Phase                 | External Clock = 90MHz, $V_{IN}$ = 3.6 $V_{P-P}$ , Highpass Filter Cutoff = 90kHz,<br>Lowpass Filter Cutoff = 900kHz<br>$f_{IN}$ = 100kHz<br>$f_{IN}$ = 750kHz                                                                                                                                                               | • |                      |                                   | ±2<br>±1.5                        | deg<br>deg                 |

| Filter Cutoff Accuracy when Self Clocked | CLKCNTL = 3V (Note 4)<br>R <sub>BIAS</sub> = 200k, Output Clock = 24.705MHz<br>R <sub>BIAS</sub> = 54.9k, Output Clock = 90MHz                                                                                                                                                                                               | • |                      |                                   | ±3<br>±3                          | %                          |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{+A} = V_{+D} = V_{+IN} = 3V$ ,  $V_{ICM} = V_{0CM} = 1.5V$ , Gain = 0dB, lowpass cutoff = 300kHz, highpass cutoff = 45kHz, internal clocking with  $R_{BIAS} = 54.9k$  unless otherwise noted.

| PARAMETER                                                                          | CONDITIONS                                                                                                                                                                                                                 |   | MIN                         | ТҮР                          | MAX                          | UNITS                                |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------|------------------------------|------------------------------|--------------------------------------|

| PGA Gain                                                                           | Lowpass Cutoff = 150kHz, Highpass Filter Bypassed,<br>Measured at DC, 0.6V to 2.4V Each Output<br>Gain Setting = 0dB<br>Gain Setting = 12dB<br>Gain Setting = 24dB<br>Gain Setting = 30dB                                  | • | 0.4<br>11.6<br>23.5<br>29.1 | 0.8<br>12<br>23.8<br>29.6    | 1.2<br>12.4<br>24.1<br>30.1  | dB<br>dB<br>dB<br>dB                 |

| PGA Gain Matching                                                                  | Lowpass Cutoff = 150kHz, Highpass Filter Bypassed,<br>Measured at DC, 0.6V to 2.4V Each Output<br>Gain Setting = 0dB<br>Gain Setting = 12dB<br>Gain Setting = 24dB<br>Gain Setting = 30dB                                  | • |                             |                              | ±0.2<br>±0.2<br>±0.3<br>±0.3 | dB<br>dB<br>dB<br>dB                 |

| Noise At 200kHz                                                                    | Voltage Noise Referred to the Input<br>Gain = 0dB<br>Gain = 12dB<br>Gain = 24dB<br>Gain = 30dB                                                                                                                             |   |                             | -119<br>-131<br>-142<br>-146 |                              | dBm/Hz<br>dBm/Hz<br>dBm/Hz<br>dBm/Hz |

| Integrated Noise                                                                   | Noise Bandwidth = 1.57MHz (Note 5), Referred to the Input<br>Gain = 0dB<br>Gain = 12dB<br>Gain = 24dB<br>Gain = 30dB                                                                                                       |   |                             | -62<br>-74<br>-85<br>-89     |                              | dBm<br>dBm<br>dBm<br>dBm             |

| THD                                                                                | V <sub>IN</sub> = 1.5V <sub>P-P</sub> , f <sub>IN</sub> = 100kHz                                                                                                                                                           |   |                             | -75                          |                              | dB                                   |

| Input Impedance                                                                    | Differential<br>Common Mode                                                                                                                                                                                                |   |                             | 16<br>20                     |                              | kΩ<br>kΩ                             |

| V <sub>OS</sub> Differential                                                       | Differential Offset Voltage at Either Output<br>Differential Offset Voltage at Either Output HPF Bypassed, Lowest LPF Cutof<br>Differential Offset Voltage at Either Output HPF Bypassed, Highest LPF Cutof                |   |                             | ±7<br>±10<br>±10             | ±15<br>±30<br>±30            | mV<br>mV<br>mV                       |

| V <sub>OSCM</sub>                                                                  | Common Mode Offset Voltage<br>V <sub>OCM</sub> = 1.5V, Supplies = 3V<br>V <sub>OSCM</sub> = V <sub>OUT-CM</sub> - V <sub>OCM</sub>                                                                                         | • | -40                         | ±20                          | 70                           | mV                                   |

| $\frac{\text{CMR Differential}}{\Delta V_{\text{INCM}}/\Delta V_{\text{OUTDIFF}}}$ | Common Mode Input from 0 to 3V<br>V+ <sub>IN</sub> = 3V<br>Common Mode Input from 0 to 5V<br>V+ <sub>IN</sub> = 5V                                                                                                         | • | 75<br>75                    | 95<br>95                     |                              | dB                                   |

| V <sub>OCM</sub> Pin Voltage                                                       | $V_{+N} = 3V$<br>V <sub>+A</sub> = V <sub>+D</sub> = 3V, Pin 3 Open                                                                                                                                                        |   | 1.2                         | 1.4                          | 1.6                          | UD<br>V                              |

| V <sub>OCM</sub> Pin Input<br>Impedance                                            | $V_{+A} = V_{+D} = 3V$ , Pin 3 Open                                                                                                                                                                                        | • | 300                         | 400                          | 700                          | Ω                                    |

| Output Swing                                                                       | Lowpass Cutoff = 150kHz, Highpass Filter Bypassed, Measured at DC<br>Source 1mA, V <sub>OUT</sub> High, Relative to V+ <sub>A</sub><br>Sink 1mA, V <sub>OUT</sub> Low, Relative to GND                                     | • |                             | 200<br>200                   | 500<br>500                   | mV<br>mV                             |

| Short-Circuit Current                                                              | Lowpass Cutoff = 150kHz, Highpass Filter Bypassed<br>Sourcing<br>Sinking                                                                                                                                                   | • | 4<br>10                     | 15<br>25                     | 25<br>50                     | mA<br>mA                             |

| Supply Current                                                                     | Internal Clock ( $R_{BIAS} = 54.9k$ ); Sum of the Currents into V+ <sub>D</sub> , V+ <sub>A</sub> , and V+ <sub>IN</sub> All Supplies Set to 3V<br>HPF = 15k, LPF = 150k<br>HPF = 45k, LPF = 300k<br>HPF = 90k, LPF = 900k | • |                             | 65<br>100<br>105             | 80<br>125<br>130             | mA<br>mA<br>mA                       |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{+A} = V_{+D} = V_{+IN} = 3V$ ,  $V_{ICM} = V_{OCM} = 1.5V$ , Gain = OdB, lowpass cutoff = 300kHz, highpass cutoff = 45kHz, internal clocking with  $R_{BIAS} = 54.9k$  unless otherwise noted.

| PARAMETER                                 | CONDITIONS                                                                                                                               |   | MIN                   | ТҮР         | MAX        | UNITS    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|-------------|------------|----------|

| Supply Current,<br>Shutdown Mode          | Sum of the Currents into $V_{+D}$ , $V_{+A}$ , and $V_{+IN}$ ; All Supplies Set to 3V Shutdown Via Serial Interface, Control Bit D1 = 1. | • |                       | 170         | 235        | μA       |

| Supply Voltage                            | V+ <sub>D</sub> , V+ <sub>A</sub> Relative to GND<br>V+ <sub>IN</sub> Relative to GND                                                    | • | 2.7<br>2.7            |             | 3.6<br>5.5 | V<br>V   |

| PSR                                       | $V_{+D} = V_{+A} = V_{+IN}$ , All from 2.7V to 3.6V<br>$V_{+D} = V_{+A} = 3.0V$ , $V_{+IN}$ from 4.5V to 5.5V                            | • | 50<br>80              | 60<br>95    |            | dB<br>dB |

| R <sub>BIAS</sub> Resistor Range          | Clock Frequency Error $\leq \pm 3\%$ , CLKCNTL = 3V                                                                                      |   | 54.9                  |             | 200        | kΩ       |

| R <sub>BIAS</sub> Pin Voltage             | 54.9k < R <sub>BIAS</sub> < 200k                                                                                                         |   |                       | 1.17        |            | V        |

| Clock Frequency Drift<br>Over Temperature | R <sub>BIAS</sub> = 54.9k, CLKCNTL Pin Open                                                                                              |   |                       | 40          |            | ppm/⁰C   |

| Clock Frequency Change<br>Over Supply     | V+ <sub>A</sub> , V+ <sub>D</sub> from 2.7V to 3.6V, R <sub>BIAS</sub> = 54.9k, CLKCNTL Pin Open                                         | • | -0.6                  | 0.1         | 0.6        | %/V      |

| Output Clock Duty Cycle                   | R <sub>BIAS</sub> = 54.9k                                                                                                                |   | 25                    | 50          | 75         | %        |

| CLKIO Pin High Level<br>Input Voltage     | CLKCNTL = 0V (Note 6)                                                                                                                    |   | V <sub>+D</sub> - 0.3 |             |            | V        |

| CLKIO Pin Low Level<br>Input Voltage      | CLKCNTL = 0V (Note 6)                                                                                                                    |   |                       |             | 0.3        | V        |

| CLKIO Pin Input Current                   | CLKCNTL = 0V<br>CLKIO = 0V (Note 7)<br>CLKIO = V+D                                                                                       | • | -1                    |             | 10         | μA<br>μA |

| CLKIO Pin High Level<br>Output Voltage    | $V_{+A} = V_{+D} = 3V$ , CLKCNTL = $3V$<br>$I_{OH} = -1mA$<br>$I_{OH} = -4mA$                                                            |   |                       | 2.95<br>2.9 |            | V<br>V   |

| CLKIO Pin Low Level<br>Output Voltage     | $V_{+A} = V_{+D} = 3V$ , CLKCNTL = $3V$<br>$I_{0L} = 1mA$<br>$I_{0L} = 4mA$                                                              |   |                       | 0.05<br>0.1 |            | V<br>V   |

| CLKIO Rise Time                           | V+ <sub>A</sub> = V+ <sub>D</sub> = CLKCNTL = 3V, 20%/80%, C <sub>LOAD</sub> = 5pF                                                       |   |                       | 0.3         |            | ns       |

| CLKIO Fall Time                           | $V_{+A} = V_{+D} = CLKCNTL = 3V$ , 20%/80%, $C_{LOAD} = 5pF$                                                                             |   |                       | 0.3         |            | ns       |

| SER, MUTE<br>High Level Input Voltage     | Pins 17, 20                                                                                                                              | • | V <sub>+D</sub> - 0.3 |             |            | V        |

| SER, MUTE<br>Low Level Input Voltage      | Pins 17, 20                                                                                                                              | • |                       |             | 0.3        | V        |

| SER, MUTE<br>Input Current                | Pin 17 or Pin 20 = 0V (Note 7)<br>Pin 17 or Pin 20 = V+ <sub>D</sub>                                                                     | • | -10                   |             | 2          | μΑ<br>μΑ |

| CLKCNTL High Level<br>Input Voltage       | Pin 5                                                                                                                                    | • | V <sub>+D</sub> - 0.5 |             |            | V        |

| CLKCNTL Low Level<br>Input Voltage        | Pin 5                                                                                                                                    |   |                       |             | 0.5        | V        |

| CLKCNTL Input Current                     | CLKCNTL = 0V (Note 7)<br>CLKCNTL = V+D                                                                                                   | • | -25                   | -15<br>15   | 25         | μA<br>μA |

### **ELECTRICAL CHARACTERISTICS**

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Specifications apply to pins 6, 9-11, 21 and 22.

#### Pin Programmable Control Mode Specifications

| SYMBOL                           | PARAMETER                  | CONDITIONS                    | MIN | ТҮР | MAX | UNITS |    |

|----------------------------------|----------------------------|-------------------------------|-----|-----|-----|-------|----|

| $V_{+D} = 2.7V \text{ to } 3.6V$ |                            |                               |     |     |     |       |    |

| V <sub>IH</sub>                  | Digital Input High Voltage | Pins 6, 9-11, 21, 22          | •   | 2   |     |       | V  |

| V <sub>IL</sub>                  | Digital Input Low Voltage  | Pins 6, 9-11, 21, 22          | •   |     |     | 0.8   | V  |

| I <sub>IN</sub>                  | Digital Input Current      | Pins 6, 9-11, 21, 22 (Note 7) | •   | -1  |     | 1     | μA |

#### Serial Port DC and Timing Specifications

| SYMBOL             | PARAMETER                   | CONDITIONS                 |   | MIN                      | ТҮР | MAX | UNITS |  |  |  |

|--------------------|-----------------------------|----------------------------|---|--------------------------|-----|-----|-------|--|--|--|

| V+p = 2.7V to 3.6V |                             |                            |   |                          |     |     |       |  |  |  |

| V <sub>IH</sub>    | Digital Input High Voltage  | Pins 6, 9, 10              | • | 2                        |     |     | V     |  |  |  |

| V <sub>IL</sub>    | Digital Input Low Voltage   | Pins 6, 9, 10              | • |                          |     | 0.8 | V     |  |  |  |

| I <sub>IN</sub>    | Digital Input Current       | Pins 6, 9, 10 (Note 7)     | • | -1                       |     | 1   | μA    |  |  |  |

| V <sub>OH</sub>    | Digital Output High Voltage | Pins 11, 21 Sourcing 500µA | • | V <sub>SUPPLY</sub> -0.3 |     |     | V     |  |  |  |

| V <sub>OL</sub>    | Digital Output Low Voltage  | Pins 11, 21 Sinking 500µA  | • |                          |     | 0.3 | V     |  |  |  |

| t <sub>1</sub>     | SDI Valid to SCLK Setup     | (Note 6)                   | • | 60                       |     |     | ns    |  |  |  |

| t <sub>2</sub>     | SDI Valid to SCLK Hold      | (Note 6)                   | • | 0                        |     |     | ns    |  |  |  |

| t <sub>3</sub>     | SCLK Low                    |                            | • | 100                      |     |     | ns    |  |  |  |

| t <sub>4</sub>     | SCLK High                   |                            | • | 100                      |     |     | ns    |  |  |  |

| t <sub>5</sub>     | CS Pulse Width              |                            | • | 60                       |     |     | ns    |  |  |  |

| t <sub>6</sub>     | LSB SCLK to CS              | (Note 6)                   | • | 60                       |     |     | ns    |  |  |  |

| t <sub>7</sub>     | CS Low to SCLK              | (Note 6)                   | • | 30                       |     |     | ns    |  |  |  |

| t <sub>8</sub>     | SDO Output Delay            | C <sub>L</sub> = 15pF      | • |                          |     | 125 | ns    |  |  |  |

| t9                 | SCLK Low to CS Low          | (Note 6)                   | • | 0                        |     |     | ns    |  |  |  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** LTC6602C and LTC6602I are guaranteed functional over the operating temperature range of -40°C to 85°C.

**Note 3:** LTC6602C is guaranteed to meet specified performance from 0°C to 70°C. The LTC6602C is designed, characterized and expected to meet specified performance from -40°C to 85°C but is not tested or QA sampled at these temperatures. The LTC6602I is guaranteed to meet the specified performance limits from -40°C to 85°C.

**Note 4:** This test measures the internal oscillator accuracy (deviation from the  $f_{CLK}$  equation). Variations in the internal oscillator frequency cause variations in the filter cutoff frequency. See the "Applications Information" section.

**Note 5:** 1.57MHz is the equivalent noise bandwidth of a 1MHz 1st order RC lowpass filter.

Note 6: Guaranteed by design, not subject to test.

The • denotes the specifications which apply over the full operating

**Note 7:** To conform to the Logic IC standard, current out of a pin is arbitrarily given a negative value.

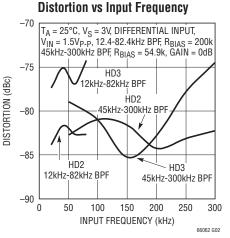

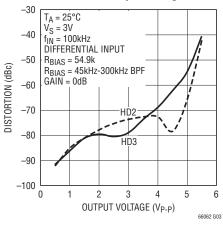

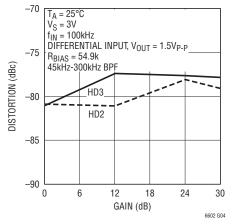

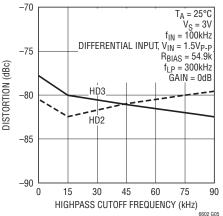

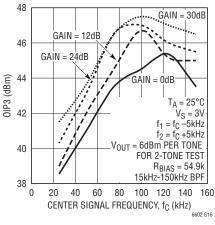

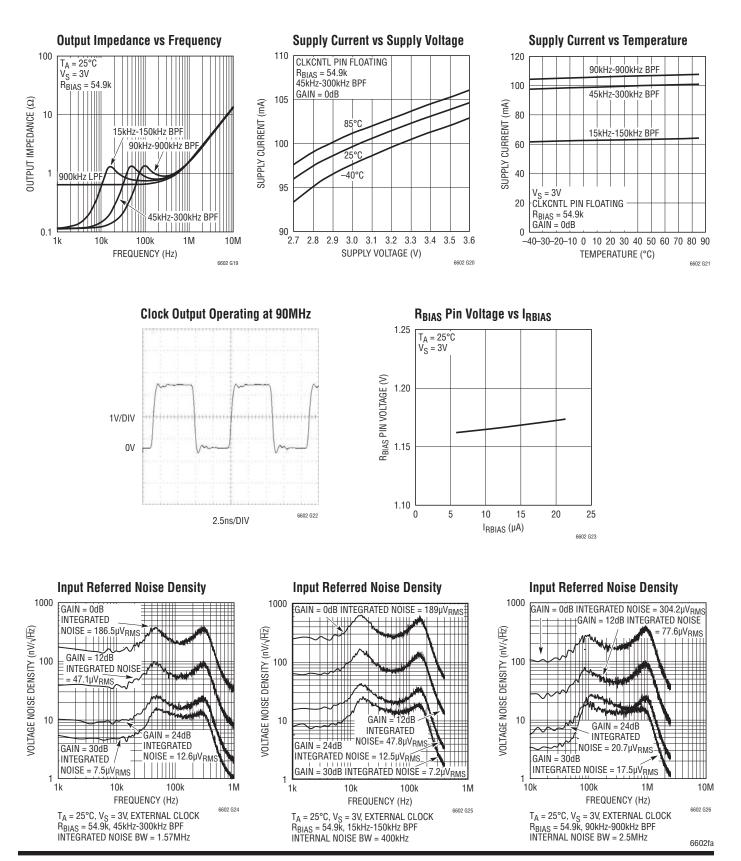

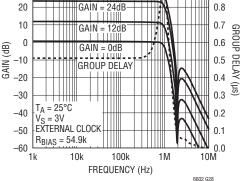

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Distortion vs Output Voltage

**Distortion vs Gain**

Distortion vs Highpass Cutoff Frequency

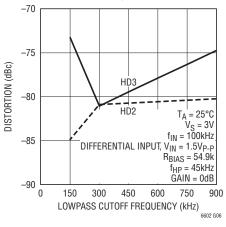

Distortion vs Lowpass Cutoff Frequency

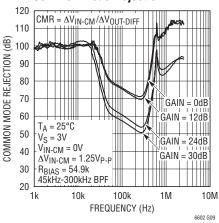

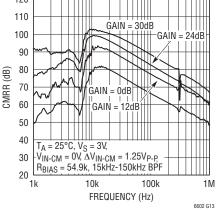

**Common Mode Rejection**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

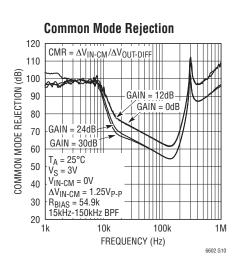

**Common Mode Rejection** 120 T<sub>A</sub> = 25°C, V<sub>S</sub> = 3V, 110  $V_{\text{IN-CM}} = 0V, \Delta V_{\text{IN-CM}} = 1.25V_{\text{P-P}}$ RBIAS = 54.9k, 90kHz-900kHz BPF (qB) 100 COMMON MODE REJECTION 90 80 70 GAIN = 0dB60 50 GAIN = 24dBGAIN = 12dB40 30  $CMR = \Delta V_{IN-CM} / \Delta V_{OUT-DIFF}$ GAIN = 30dB20 100k 1M 10k 10M FREQUENCY (Hz) 6602 G11

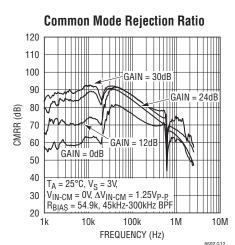

**Common Mode Rejection Ratio**

GAIN = 12dB

GAIN

1M

GAIN = 30dB

FREQUENCY (Hz)

24dB

10M

6602 G14

120

110

100

90

80

70

60

50

40

30 20 10k

CMRR (dB)

T<sub>A</sub> = 25°C

V<sub>IN-CM</sub> = 0V

$R_{BIAS} = 54.9k$

$\Delta V_{IN-CM} = 1.25 V_{P-P}$

90kHz-900kHz BPF

GAIN = 0dB

100k

$V_{\rm S} = 3V$

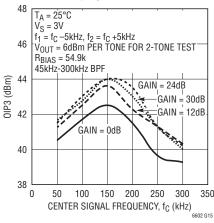

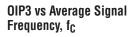

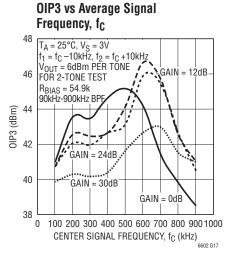

OIP3 vs Average Signal Frequency, f<sub>C</sub>

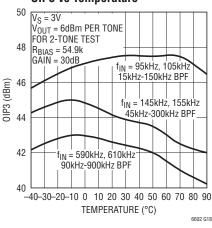

**OIP3 vs Temperature**

### Common Mode Rejection Ratio

6602fa

8

### **TYPICAL PERFORMANCE CHARACTERISTICS**

9

### PIN FUNCTIONS

**V**+<sub>IN</sub> (**Pin 1**): Input Voltage Supply  $(2.7V \le V \le 5.5V)$ . This supply must be kept free from noise and ripple. It should be bypassed directly to a ground plane with a 0.1µF capacitor unless it is tied to V+<sub>A</sub> (Pin 2). The bypass should be as close as possible to the IC, but is not as critical as the bypassing of V+<sub>A</sub> and V+<sub>D</sub> (Pin16).

**V**+A (Pin 2): Analog Voltage Supply  $(2.7V \le V \le 3.6V)$ . This supply must be kept free from noise and ripple. It should be bypassed directly to a ground plane with a  $0.1\mu$ F capacitor. The bypass should be as close as possible to the IC.

**V<sub>OCM</sub> (Pin 3):** Output common mode voltage reference. If floated, an internal resistive divider sets the voltage on this pin to half the supply voltage (typically 1.5V), maximizing the dynamic range of the filter. If this pin is floated, it must be bypassed with a quality  $0.1\mu$ F capacitor to ground. This pin has a typical input impedance of 400 $\Omega$  and may be overdriven. Driving this pin to a voltage other than the default value will reduce the signal range the filter can handle before clipping.

**R**<sub>BIAS</sub> (**Pin 4**): Oscillator Frequency-Setting Resistor Input. The value of the resistor connected between this pin and ground determines the frequency of the master oscillator, and sets the bias currents for the filter networks. The voltage on this pin is held by the LTC6602 to approximately 1.17V. For best performance, use a precision metal film resistor with a value between 54.9k and 200k and limit the capacitance on this pin to less than 10pF. This resistor is necessary even if an external clock is used.

**CLKCNTL (Pin 5):** Clock Control Input. This three-state input selects the function of CLKIO (Pin 15). Tying the CLKCNTL pin to ground allows the CLKIO pin to be driven by an external clock (CLKIO is the master clock input). If the CLKCNTL pin is floated, the internal oscillator is enabled, but the master clock is not present at the CLKIO pin (CLKIO is a no-connect). If the CLKCNTL pin is tied to V<sub>+D</sub> (Pin 16), the internal oscillator is enabled and the master clock is present at the CLKIO pin (CLKIO is the master clock output). To detect a floating CLKCNTL pin, the LTC6602 attempts to pull the pin toward mid-supply.

This is realized with two internal current sources, one tied to V<sub>+D</sub> and CLKCNTL and the other one tied to ground and CLKCNTL. Therefore, driving the CLKCNTL pin high requires sourcing approximately 15 $\mu$ A. Likewise, driving the CLKCNTL pin low requires sinking 15 $\mu$ A. When the CLKCNTL pin is floated, preferably it should be bypassed by a 1nF capacitor to ground or it should be surrounded by a ground shield to prevent excessive coupling from other PCB traces.

**LPF1(CS) (Pin 6):** Logic Input. When in pin programmable control mode, this pin is the MSB of the lowpass cutoff frequency control code; in serial control mode, this pin is the chip select input (active low).

**+INB**, **–INB** (Pins 7, 8): Channel B differential inputs. The input range and input resistance are described in the Applications Information section. Input voltages which exceed  $V_{+IN}$  (Pin 1) should be avoided.

**LPF0(SCLK) (Pin 9):** Logic Input. When in pin programmable control mode, this pin is the LSB of the lowpass cutoff frequency control code; in serial control mode, this pin is the clock of the serial interface.

**HPF1(SDI) (Pin 10):** Logic Input. When in pin programmable control mode, this pin is the MSB of the highpass cutoff frequency control code; in serial control mode, this pin is the serial data input.

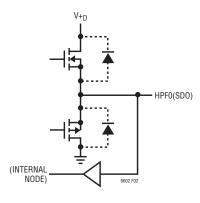

**HPF0(SD0) (Pin 11):** Logic Input. When in pin programmable control mode, this pin is the LSB of the highpass cutoff frequency control code; in serial control mode, this pin is the serial data output.

**-OUTB**, **+OUTB** (Pins 12, 13): Channel B differential filter outputs. These pins can drive 1k and/or 50pF loads. For larger capacitive loads, an external  $100\Omega$  series resistor is recommended for each output. The common mode voltage of the filter outputs is the same as the voltage at V<sub>OCM</sub> (Pin 3).

**GND (Pin 14):** Ground. Connect to a ground plane for best performance.

### PIN FUNCTIONS

**CLKIO (Pin 15):** When CLKCNTL (Pin 5) is tied to ground, CLKIO is the master clock input. When CLKCNTL is floated, CLKIO is pulled to ground by a weak,  $5\mu$ A pulldown. When CLKCNTL is tied to V+<sub>D</sub> (Pin 16), CLKIO is the master clock output. When configured as a clock output, this pin can drive 1k and/or 5pF loads. Heavier loads may cause inaccuracies due to supply bounce at high frequencies.

**V+D** (Pin 16): Digital Voltage Supply  $(2.7V \le V \le 3.6V)$ . This supply must be kept free from noise and ripple. It should be bypassed directly to a ground plane with a  $0.1\mu$ F capacitor. The bypass should be as close as possible to the IC.

**SER (Pin 17):** Interface Selection Input. When tied to  $V_{+D}$  (Pin 16), the interface is in pin programmable control mode, i.e. the filter gain and cutoff frequencies are programmed by the GAIN1, GAIN0, HPF1, HPF0, LPF1 and LPF0 pin connections. When SER is tied to ground, the filter gain, the filter cutoff frequencies and shutdown mode are programmed by the serial interface.

-OUTA, +OUTA (Pins 18, 19): Channel A differential filter outputs. These pins can drive 1k and/or 50pF loads. For

larger capacitive loads, an external 100 $\Omega$  series resistor is recommended for each output. The common mode voltage of the filter outputs is the same as the voltage at V<sub>OCM</sub> (Pin 3).

**MUTE (Pin 20):** MUTEX input. Drive to ground to disconnect and mute the inputs. Float or drive to  $V_{+D}$  (Pin 16) for normal operation.

**GAINO(D0) (Pin 21):** Logic Input. When in pin programmable control mode, this pin is the LSB of the gain control code; in serial control mode, this pin is the LSB of the serial control register, an output.

**GAIN1 (Pin 22):** Logic Input. When in pin programmable control mode, this pin is the MSB of the gain control code; in serial control mode, this pin is a no-connect.

-INA, +INA (Pins 23, 24): Channel A differential inputs. The input range and input resistance are described in the Applications Information section. Input voltage levels can range from GND to the  $V_{+IN}$  supply rail.

**Exposed Pad (Pin 25):** Ground. The Exposed Pad must be soldered to PCB.

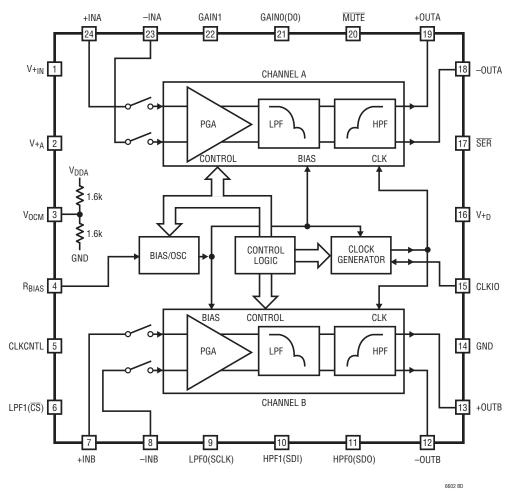

### **BLOCK DIAGRAM**

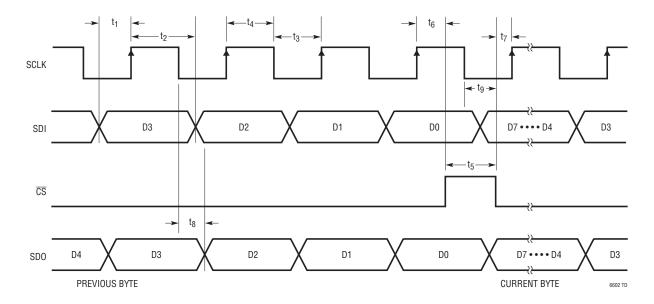

### TIMING DIAGRAM

Timing Diagram of the Serial Interface

### Theory of Operation (Refer to Block Diagram)

The LTC6602 features two matched filter channels, each containing gain control, lowpass, and highpass networks that are controlled by a single control block and clocked by a single clock generator. The gain, lowpass and highpass sections can be independently programmed. The two channels are not independent, i.e. if the gain is set to 24dB, then both channels have a gain of 24dB. The filter can also be programmed to bypass the highpass filter networks, giving a lowpass response. The filter can be clocked with an external clock source, or using the internal oscillator. A resistor connected to the R<sub>BIAS</sub> pin sets the bias currents for the filter networks and the internal oscillator frequency (unless driven by an external clock). Altering the clock frequency changes the filter bandwidths. This allows the filters to be "tuned" to many different bandwidths.

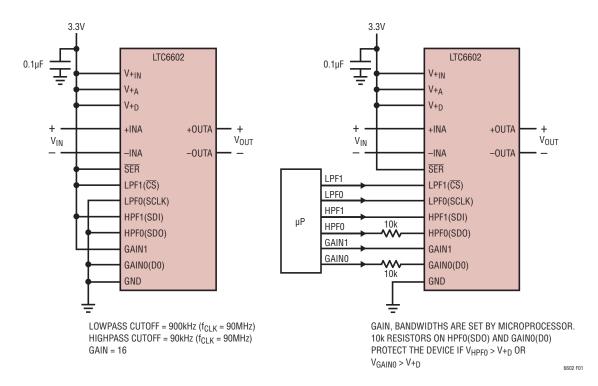

#### Pin Programmable Interface

As shown in Figure 1, connecting  $\overline{\text{SER}}$  to V<sub>+D</sub> allows the filter to be directly controlled through the pin programmable control lines GAIN1, GAIN0, HPF1, HPF0, LPF1 and LPF0. The HPF0(SD0) and GAIN0(D0) pins are bidirectional (inputs in pin programmable control mode, outputs in serial mode). In pin programmable control mode, the voltages at HPF0(SD0) and GAIN0(D0) cannot exceed V<sub>+D</sub>; otherwise, large currents can be injected to V<sub>+D</sub> through the internal diodes (see Figure 2). Connecting a 10k resistor at the HPF0(SD0) and GAIN0(D0) pins (see Figure 1) is recommended for current limiting, to less than 10mA. SER has an internal pull-up to V<sub>+D</sub>. None of the logic inputs have an internal pull-up or pull-down.

Figure 1. Filter in Pin Programmable Control Mode

Figure 3. Diagram of Serial Interface (MSB First Out)

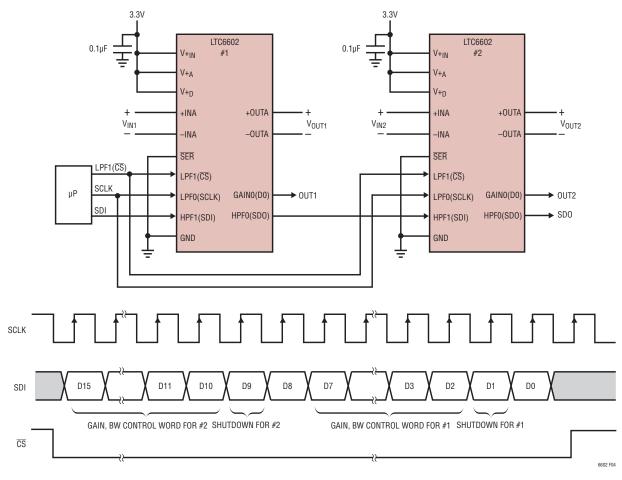

#### Figure 4. Two Filters in a Daisy Chain

#### **Serial Control Register Definition**

|       | -     |      |      |      |      |      |     |

|-------|-------|------|------|------|------|------|-----|

| D7    | D6    | D5   | D4   | D3   | D2   | D1   | D0  |

| GAINO | GAIN1 | LPF0 | LPF1 | HPF0 | HPF1 | SHDN | OUT |

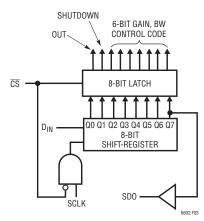

#### Serial Interface

Connecting  $\overline{SER}$  to ground allows the filter to be controlled through the SPI serial interface. When  $\overline{CS}$  is low, the serial data on SDI is shifted into an 8-bit shift-register on the rising edge of the clock (SCLK), with the MSB transferred first (see Figure 3). Serial data on SDO is shifted out on the clock's falling edge. A high  $\overline{CS}$  will load the 8 bits of the shift-register into an 8-bit D-latch, which is the serial control register. The clock is disabled internally when  $\overline{CS}$  is pulled high. Note: SCLK must be low before  $\overline{CS}$  is pulled low to avoid an extra internal clock pulse. SDO is always active in serial mode (never tri-stated) and cannot be "wire-or'ed" to other SPI outputs. In addition, SDO is not forced to zero when  $\overline{CS}$  is pulled high.

An LTC6602 may be daisy chained with other LTC6602s or other devices having serial interfaces. Daisy chaining is accomplished by connecting the SDO of the lead chip to the SDI of the next chip, while SCLK and  $\overline{CS}$  remain common to all chips in the daisy chain. The serial data is clocked to all the chips then the  $\overline{CS}$  signal is pulled high to update all of them simultaneously. Figure 4 shows an example of two LTC6602s in a daisy chained SPI configuration.

GAIN1 and GAIN0 are the gain control bits (register bits D6 and D7 when in serial mode). Their function is shown in Table 1. In serial mode, register bit D1 can be set to '1' to put the device into a low power shutdown mode. Register bit D0 is a general purpose output (Pin 21) when in serial mode.

| Table | 1. | Gain | Control  |

|-------|----|------|----------|

| IUDIO |    | aum  | 00111101 |

| GAIN 1 | GAIN O | PASSBAND GAIN<br>(dB) |

|--------|--------|-----------------------|

| 0      | 0      | 0                     |

| 0      | 1      | 12                    |

| 1      | 0      | 24                    |

| 1      | 1      | 30                    |

#### **Self-Clocking Operation**

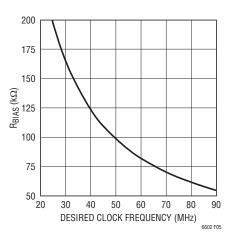

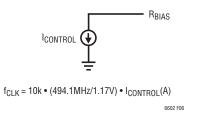

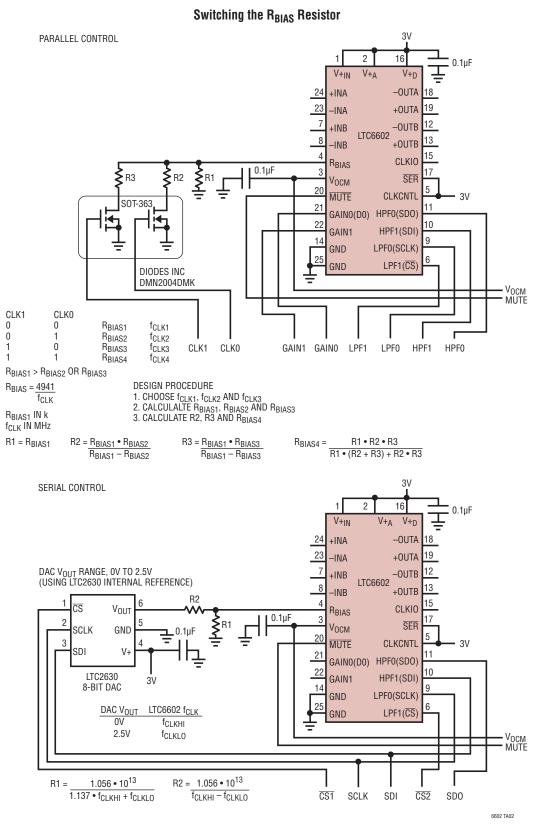

The LTC6602 features a unique internal oscillator which sets the filter cutoff frequency using a single external resistor connected to the  $R_{BIAS}$  pin. The clock frequency is determined by the following simple formula (see Figure 5):

$f_{CLK} = 494.1 MHz \bullet 10 k/R_{BIAS}$

Note:  $R_{BIAS} \le 200k$ .

Figure 5. R<sub>BIAS</sub> vs Desired Clock Frequency

The design is optimized for  $V_{+A}$ ,  $V_{+D} = 3V$ ,  $f_{CLK} = 90MHz$ , where the filter cutoff frequency error is typically <3%when a 0.1% external 54.9k resistor is used. With different resistor values and cutoff frequency control settings (HPF1, HPF0, LPF1 and LPF0), the highpass and lowpass cutoff frequencies can be accurately varied from 4.1175kHz to 90kHz and from 41.175kHz to 900kHz, respectively. Table 2 summarizes the cutoff frequencies that can be obtained with an external resistor (R<sub>BIAS</sub>) value of 54.9k. Note that the cutoff frequencies scale with the clock frequency. For example, if HPF1, HPF0, LPF1 and LPF0 are all equal to zero, and R<sub>BIAS</sub> is increased from 54.9k to 200k, f<sub>CLK</sub> will decrease from 90MHz to 24.705MHz, the lowpass cutoff frequency will be reduced from 150kHz to 41.175kHz, and the highpass cutoff frequency will be reduced from 15kHz to 4.1175Hz. The cutoff frequencies that can be obtained with an external resistor value of 200k

are shown in Table 3. When the LTC6602 is programmed for the lowest lowpass cutoff frequency (LPF1, LPF0 = '0'), the power is automatically reduced by about 35%.

Table 2. Cutoff Frequency Control, R<sub>BIAS</sub> = 54.9k, f<sub>CLK</sub> = 90MHz

| LPF1 | LPFO | Lowpass<br>BW (kHz) | HPF1 | HPFO | Highpass<br>BW (kHz) |

|------|------|---------------------|------|------|----------------------|

| 0    | 0    | 150                 | 0    | 0    | 15                   |

| 0    | 1    | 300                 | 0    | 1    | 45                   |

| 1    | 0    | 900                 | 1    | 0    | 90                   |

| 1    | 1    | 900                 | 1    | 1    | Bypass HPF           |

#### Table 3. Cutoff Frequency Control, R<sub>BIAS</sub> = 200k, f<sub>CLK</sub> = 24.705MHz

| LPF1 | LPFO | Lowpass<br>BW (kHz) | HPF1 | HPFO | Highpass<br>BW (kHz) |

|------|------|---------------------|------|------|----------------------|

| 0    | 0    | 41.175              | 0    | 0    | 4.1175               |

| 0    | 1    | 82.35               | 0    | 1    | 12.3525              |

| 1    | 0    | 247.05              | 1    | 0    | 24.705               |

| 1    | 1    | 247.05              | 1    | 1    | Bypass HPF           |

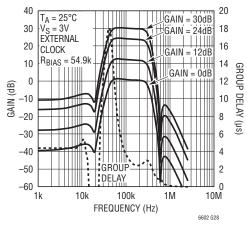

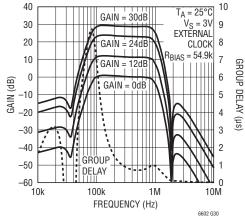

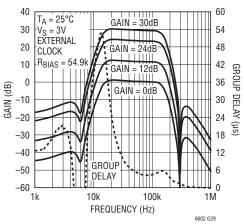

The following graphs show a few of the possible combinations of highpass and lowpass filters.

Gain and Group Delay vs Frequency (45kHz to 300kHz Bandpass Response)

#### **Preserving Oscillator Accuracy**

The oscillator is sensitive to transients on the positive supply. The IC should be soldered to the PC board and the PCB layout should include a  $0.1\mu$ F ceramic capacitor between V<sub>+A</sub> (Pin 2) and ground, as close as possible to the IC to minimize inductance. The PCB layout should also include an additional  $0.1\mu$ F ceramic capacitor between V<sub>+D</sub> (Pin 16) and ground. Avoid parasitic capacitance on R<sub>BIAS</sub> (Pin 4) and avoid routing noisy signals near R<sub>BIAS</sub>. Use a ground plane connected to Pin 14 and the Exposed Pad (Pin 25).

# Alternative Methods of Setting the Clock Frequency of the LTC6602

The oscillator may be programmed by any method that sinks a current out of the R<sub>BIAS</sub> pin. The circuit in Figure 6 sets the clock frequency by using a programmable current source and in the expression for  $f_{CLK}$ , the resistor R<sub>BIAS</sub> is replaced by the ratio of  $1.17V/I_{CONTROL}$ . Because the voltage of the R<sub>BIAS</sub> pin is approximately  $1.17V \pm 5\%$ , the Figure 6 circuit is less accurate than if a resistor controls the clock frequency.

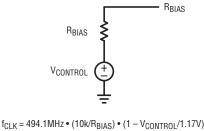

Figure 7 shows the LTC6602's oscillator configured as a VCO. A voltage source is connected in series with the R<sub>BIAS</sub> resistor. The clock frequency,  $f_{CLK}$ , will vary with V<sub>CONTROL</sub>. Again, this circuit decouples the relationship between the current out of the R<sub>BIAS</sub> pin and the voltage of the R<sub>BIAS</sub> pin; the frequency accuracy will be degraded. The clock frequency, however, will increase monotonically with decreasing V<sub>CONTROL</sub>.

#### **Operation Using an External Clock**

The LTC6602 may be clocked by an external oscillator for tighter bandwidth control by pulling CLKCNTL (Pin 5) to ground and driving a clock into CLKIO (Pin 15). If an external clock is used, the R<sub>BIAS</sub> resistor is still necessary. The value of R<sub>BIAS</sub> must be no larger than the value that would be required for using the internal oscillator. For example, a 100k resistor would program the internal oscillator for 49.41MHz, so an external oscillator frequency of 49.41MHz would require an R<sub>BIAS</sub> resistance of no more than 100k. If the value of R<sub>BIAS</sub> is too large, the filters will not receive a large enough bias current, possibly causing errors due to insufficient settling.

Figure 6. Current Controlled Clock Frequency

6602 F07

Figure 7. Voltage Controlled Clock Frequency

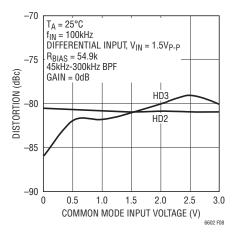

Figure 8. Distortion vs Common Mode Input Voltage (3V)

#### Input Common Mode and Differential Voltage Range

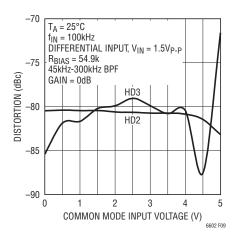

The input signal range extends from zero to the V+<sub>IN</sub> supply voltage. This input supply can be tied to V+<sub>A</sub> and V+<sub>D</sub>, or driven up to 5.5V for increased input common mode voltage range. Figures 8 and 9 show the distortion of the filter versus common mode input voltage with a  $1.5V_{P-P}$  differential input signal.

For best performance, the inputs should be driven differentially. For single ended signals, connect the unused input to  $V_{OCM}$  (Pin 3) or to a quiet DC reference voltage. To achieve the best distortion performance, the input signal should be centered around the DC voltage of the unused input.

Refer to the Typical Performance Characteristics section to estimate the distortion for a given input level.

#### **Dynamic Input Impedance**

The unique input sampling structure of the LTC6602 has a dynamic input impedance which depends on the configuration and the clock frequency. This dynamic input impedance has both a differential component and a common mode component. The common mode input impedance is a function of the clock frequency and the control bit LPF1. The differential input impedance is a function of the clock frequency is a function of the clock frequency and the control bit LPF1. The differential input impedance is a function of the clock frequency and the control bits LPF1, GAIN1 and GAIN0. Table 4 shows the typical input impedances for a clock frequency of 90MHz. These input impedances are all proportional to  $1/f_{CLK}$ , so if the clock frequency were reduced

Figure 9. Distortion vs Common Mode Input Voltage (5V)

by half to 45MHz, the impedances would be doubled. The typical part to part variation in dynamic input impedance for a given clock frequency is -20% to +35%.

Table 4. Differential, Common Mode Input Impedances,  $f_{CLK} = 90MHz$

|       |       |      | Differential Input Common Mode I |                         |

|-------|-------|------|----------------------------------|-------------------------|

| GAIN1 | GAINO | LPF1 | Impedance (k $\Omega$ )          | Impedance (k $\Omega$ ) |

| 0     | 0     | 0    | 16                               | 20                      |

| 0     | 0     | 1    | 6                                | 6.7                     |

| 0     | 1     | 0    | 8                                | 20                      |

| 0     | 1     | 1    | 2.8                              | 6.7                     |

| 1     | 0     | 0    | 2.6                              | 20                      |

| 1     | 0     | 1    | 1.8                              | 6.7                     |

| 1     | 1     | 0    | 2.4                              | 20                      |

| 1     | 1     | 1    | 1.3                              | 6.7                     |

#### **Output Common Mode and Differential Voltage Range**

The output voltage is a fully differential signal with a common mode level equal to the voltage at  $V_{OCM}$ . Any of the filter outputs may be used as single-ended outputs, although this will degrade the performance. The output voltage range is typically 0.5V to V<sub>+A</sub> – 0.5V (V<sub>+A</sub> = 2.7V to 3.6V).

The common mode output voltage can be adjusted by overdriving the voltage present on V<sub>OCM</sub>. To maximize the undistorted peak-to-peak signal swing of the filter, the V<sub>OCM</sub> voltage should be set to V<sub>+A</sub>/2. Note that the

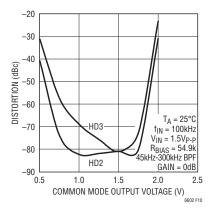

Figure 10. Distortion vs Common Mode Output Voltage

output common mode voltages of the two channels are not independent as they are both set by the  $V_{OCM}$  pin. Figure 10 illustrates the distortion versus output common mode voltage for a  $1.5V_{P-P}$  differential input voltage and a common mode input voltage that is equal to mid-supply.

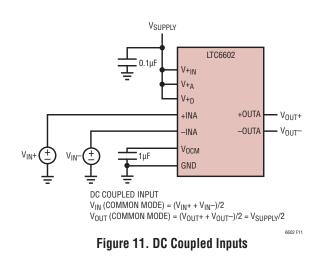

### Interfacing to the LTC6602

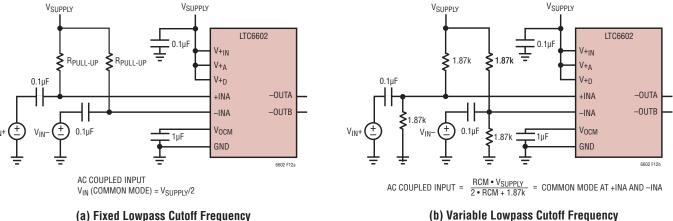

The input and output common mode voltages of the LTC6602 are independent. The input common mode voltage is set by the signal source if DC coupled, as shown in Figure 11. If the inputs are AC coupled, the input common mode voltage will pulled to ground by an equivalent resistance of  $R_{CM}$ , shown in Table 4. This does not affect the filter's performance as long as the input amplitude is less than  $0.5V_{P-P}$ . At low filter gain settings, a larger input voltage swing may be desired. Figure 12 shows two circuits with AC coupled inputs. In a fixed lowpass cutoff

frequency, connecting resistors between each input and  $V_{+IN}$  will pull the input common mode voltage up, increasing the input signal swing (Figure 12a). The resistance,  $R_{PULL-UP}$ , necessary to set the input common mode voltage,  $V_{ICM}$ , to any desired level can be calculated by

$$R_{PULL-UP} = R_{CM} \left( \frac{V_{SUPPLY}}{V_{ICM}} - 1 \right)$$

where

$R_{CM} = 20k \bullet 90MHz/f_{CLK}$  for LPFI = 0

$$R_{CM} = 6.7k \bullet 90MHz/f_{CLK}$$

for LPFI = 1

For example, if the lowpass cutoff frequency is set to 300kHz, 20k resistors connected between each input and V+ $_{\rm IN}$  will set the input common mode voltage to mid-supply.

Figure 13. Two Filters in a Master/Slave Configuration

If the lowpass cutoff frequency varies then the Figure 12b circuit must be used.

The output common mode voltage is equal to the voltage of the V<sub>OCM</sub> pin. The V<sub>OCM</sub> pin is biased to one half of the supply voltage by an internal resistive divider (see Block Diagram). To alter the common mode output voltage, V<sub>OCM</sub> can be driven with an external voltage source or resistor network. If external resistors are used, it is important to note that the internal 1.6k resistors can vary ±30% (their ratio varies only ±1%). The filter outputs can also be AC coupled.

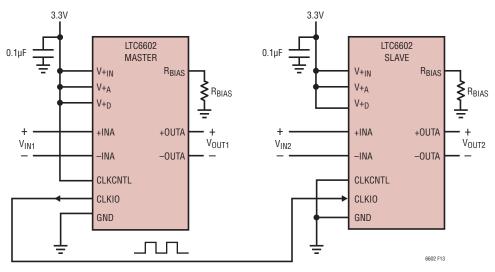

The LTC6602 can be interfaced to an A/D converter by pulling CLKCNTL (Pin 5) to V+<sub>D</sub>. This configures CLKIO (Pin 15) as a clock output, which can be used to drive the clock input of the A/D converter. This allows the A/D converter to be synchronized with the filter sampling clock, avoiding "beat frequencies" and simplifying the board layout. Any routing attached to the CLKIO pin should be as short as possible, in order to minimize ringing. Similarly, two LTC6602s can be connected in a master/ slave configuration as shown in Figure 13. This results in four matched filter channels, all synchronized to the same clock. The master has its CLKCNTL pin pulled to V+<sub>D</sub>, configuring its CLKIO pin as an output, while the slave has its CLKCNTL pin pulled to ground, configuring its CLKIO pin as an input.

#### **Output Drive**

The filter outputs can drive 1k and/or 50pF loads connected to AC ground with a 0.5V to 2.5V signal (corresponding to a  $4V_{P-P}$  differential signal). For differential loads (loads connected between +OUTA and -OUTA or +OUTB and -OUTB) the outputs can produce a  $4V_{P-P}$  signal across 2k and/or 25pF. For smaller signal amplitudes, the outputs can drive correspondingly heavier loads. For larger capacitive loads, an external 50 $\Omega$  series resistor is recommended for each output.

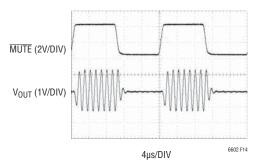

#### **Mute Function**

The LTC6602 features a mute function which is asserted by pulling MUTE (Pin 20) to ground. This breaks the signal path that leads from the input pins to the filter networks, attenuating the input signal by at least 20dB. The mute function can be used to protect the filter inputs from large transients. The filter clock continues to run when the filter is muted, allowing for a fast recovery time when MUTE is de-asserted. Typically, the recovery time is less than 5µs, as shown in Figure 14. When the mute function is asserted, the differential input impedance becomes very high, but the common mode input impedance to ground remains the same. This keeps the input common mode voltage stable when muted, even when the inputs are AC coupled. Connecting GAINO(D0) to MUTE allows for serial control of the mute function. MUTE has an internal pull-up to  $V_{+D}$ .

Figure 14. Mute Function Recovery Time

### **Clock Feedthrough**

Clock feedthrough is defined as the RMS value of the clock frequency and its harmonics that are present at the filter's output. The clock feedthrough is measured with +INA and -INA (or +INB, -INB) tied to V<sub>OCM</sub> and depends on the PC board layout and the power supply decoupling. The clock feedthrough can be reduced with a simple RC post filter.

### DC Offset

The output DC offset of the LTC6602 is less than  $\pm 15$ mV. To obtain optimum DC offset performance, appropriate PC board layout techniques should be used. The filter IC should be soldered to the PC board. The power supplies should be well decoupled including 0.1µF ceramic capacitors from V+<sub>D</sub> (Pin 16) and V+<sub>A</sub> (Pin 2) to ground.

A ground plane should be used. Noisy signals should be isolated from the filter input pins.

The output DC offset typically changes less than  $\pm 2mV$  when the clock frequency varies from 24.705MHz to 90MHz. The offset is measured by connecting the inputs to V<sub>OCM</sub> and measuring the differential voltage at the filter's output.

#### Aliasing

Aliasing is an inherent phenomenon of sampled data filters. Significant aliasing only occurs when the frequency of the input signal approaches the sampling frequency or multiples of the sampling frequency. The ratio of the LTC6602 input sampling frequency to the clock frequency,  $f_{CLK}$ , is determined by the state of control bit LPF1. If LPF1 is set to '0', the input sampling frequency is equal to  $f_{CLK}/3$ . If LPF1 is set to '1', the input sampling frequency is equal to  $f_{CLK}$ . Input signals with frequencies near the input sampling frequency will be aliased to the passband of the filter and appear at the output unattenuated.

A simple LC anti-aliasing filter is recommended at the filter inputs to attenuate frequencies near the input sampling frequency that will be aliased to the passband. For example, if the clock frequency is set to 90MHz and the lowpass cutoff frequency of the filter is set to it's maximum (LPF1 = '1'), the lowest frequency that would be aliased to the passband would be  $f_{CLK} - f_{CUTOFF}$ , i.e. 90MHz – 900kHz = 89.1MHz. In order to attenuate this frequency by 40dB, an LC filter with a cutoff frequency of 8.91MHz or lower would be required at the filter inputs. The capacitor connected between the LTC6602 filter inputs should be at least 150pF to provide sufficient charge to the input sampler. If there is no anti-aliasing filter, the LTC6602 filter inputs should be driven by a low impedance source (<100 $\Omega$ ).

### Wideband Noise

The wideband noise of the filter is the RMS value of the device's output noise spectral density. The wideband noise voltage is used to determine the operating signal-to-noise ratio at a given distortion level. The wideband noise is nearly independent of the value of the clock frequency and excludes the clock feedthrough. Most of the wideband noise is concentrated in the filter passband and cannot be removed with post filtering.

Figure 15. f<sub>CLK</sub> vs Filter Cutoff Frequencies

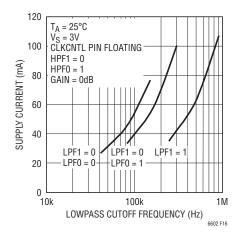

Figure 16. Supply Current vs Lowpass Cutoff Frequency

| Table 5. Total liput heleffeu litegrateu holse voltage (Fassballu dalli = 500b) |      |      |      |               |

|---------------------------------------------------------------------------------|------|------|------|---------------|

| LPF1                                                                            | LPFO | HPF1 | HPFO | Noise Voltage |

| 0                                                                               | 0    | 0    | 0    | –90dBm        |

| 0                                                                               | 1    | 0    | 1    | –89dBm        |

| 1                                                                               | Х    | 1    | 0    | -82dBm        |

#### **Power Supply Current**

The power supply current depends on the state of the lowpass cutoff frequency controls (LPF1, LPF0) and the value of  $R_{BIAS}$ . When the LTC6602 is programmed for the lowest lowpass cutoff frequency (LPF1 = LPF0 = '0'), the supply current is reduced by about 35% relative to the supply current vs. cutoff frequency for various bandwidth settings is shown in the "Typical Performance Characteristics" section. The LTC6602 can be programmed through the serial interface to enter into a low power shutdown mode as described in the Serial Interface section. The power supply current during shutdown is less than 235µA.

#### Supply Current versus Noise Tradeoff

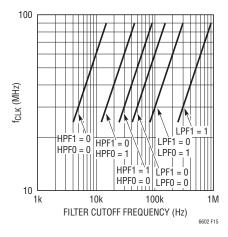

The passband of the LTC6602 is determined by the master clock frequency (which is set by  $R_{BIAS}$  when the internal oscillator is used), HPF1, HPF0, LPF1 and LPF0. The LTC6602 is optimized for use with  $R_{BIAS}$  having a value between 200k and 54.9k to set the internal oscillation

frequency from 24.705MHz to 90MHz. Both lowpass and highpass corner frequencies are proportional to the clock frequency (internal or external). To extend the filter's operational frequency range, the master clock is divided down before reaching the filter. LPF1 and LPF0 set the division ratio of the lowpass clock while HPF1 and HPF0 set the division ratio of the highpass clock. Figure 15 shows the possible cutoff frequencies versus f<sub>CLK</sub>, HPF1, HPF0, LPF1 and LPF0. Overlapping frequency ranges allow more than one possible choice of bandwidth settings for some cutoff frequencies. Figure 16 shows supply current as a function of the lowpass cutoff frequency, LPF1 and LPF0. Note that the higher bandwidth setting always gives the minimum supply current for a given cutoff frequency. The total integrated noise voltage for a passband gain of 30dB is shown in Table 5. Note that the noise is higher for the higher bandwidth settings. This creates a tradeoff between supply current and noise. For a given cutoff frequency, using the highest possible bandwidth setting gives the minimum supply current at the expense of higher noise.

# The LTC6602, an Adaptable Baseband Filter for an RFID Reader

A radio-frequency identification (RFID) system is an auto-id technology that identifies any object that contains a coded tag. An RFID system consists of a reader (or interrogator) and a tag. An RFID system capable of identifying multiple tags at a maximum operating distance operates in the UHF frequency range. A UHF reader transmits information to a tag by modulating an RF signal in the 860MHz to 960MHz frequency range. Typically a tag is passive, meaning that it receives all of its operating energy from a reader that transmits a continuous wave (CW) RF signal to power a tag. A tag responds by modulating the reflection coefficient of its antenna, thereby backscattering an information signal to the reader. Reliable detection of a tag signal requires communication protocols that define the physical and operating interaction between readers and tags. The latest UHF RFID protocol, the Electronic Product Code<sup>™</sup> (EPC) global class-1 generation 2 standard (C1G2), have been accepted worldwide and is also known as ISO 18000-6C. The C1G2 standard defines a reader to tag and a tag to reader communication using a flexible set of signal modulation, data encoding, data rates and command procedures. C1G2 specifies reader and tag data symbols using pulse-interval encoding. Tag signal detection requires measuring the time interval between signal transitions (a data "1" symbol has a longer interval than a data "0" symbol). The reader initiates a tag inventory by sending a signal that instructs a tag to set its backscatter data rate and encoding. C1G2 certified RFID readers can operate in an RF environment where many readers are in close proximity. The three operating modes of C1G2, single interrogator, multiple interrogator and dense interrogator, define the spectral limits of reader and tag signals for an optimum balance of reliable multitag detection and high data throughput (for more information on C1G2, consult the references at the end of this design note). The advantages of C1G2 complex protocols can be realized by using a reader whose receiver contains a high linearity direct conversion I and Q demodulator, a low noise amplifier, a dual baseband filter with variable gain and bandwidth and a dual analog to digital converter (ADC).

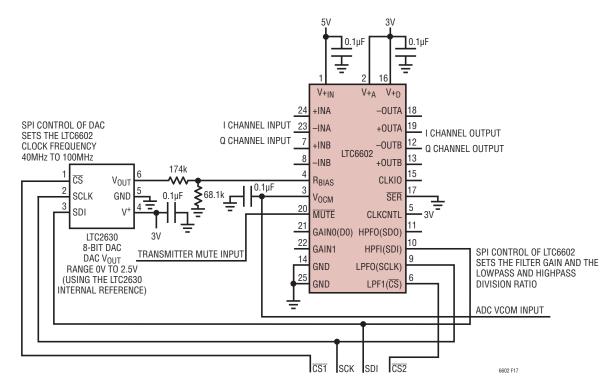

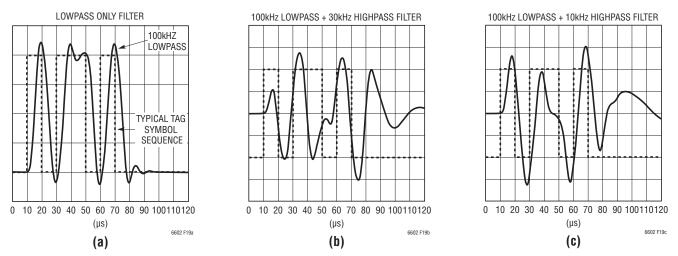

Certified C1G2 UHF RFID readers can adapt to a great variety of operating conditions. To achieve operating flexibility a reader's baseband circuits must include an adaptable bandwidth filter. Figure 17 shows an LTC6602 based filter circuit that uses SPI control to vary the filter's bandwidth to adjust for the C1G2 complex set of data rates. encoding and modulation. The filter's clock frequency is set by the SPI control of 8-bit LTC2630 DAC (digital to analog converter). The DAC voltage through a resistive divider sets the current into the LTC6602 R<sub>BIAS</sub> pin. The resistive divider sets the clock frequency range for a DAC voltage range OV to 3V. For the resistor values in Figure 17 (191k and 61.9k) the clock frequency range is 40MHz to 100MHz (234.4kHz per bit). The lowpass and highpass division ratio is set by the SPI control of the LTC6602. The cutoff range for the highpass filter is 6.7kHz to 100kHz and for the lowpass filter is 66.7kHz to 1MHz. The optimum filter bandwidth setting can be adjusted by a software algorithm and is a function of the reader's data clock, data rate, encoding and modulation. The filter bandwidth must be sufficiently narrow to maximize the dynamic range to the ADC input and wide enough to preserve signal transitions and pulse width. If the filter setting is optimum then a DSP algorithm can reliably detect tag data. Figure 18a shows the filter's time response to a typical tag symbol sequence (a "short" pulse interval followed by a "long" pulse interval). The lowpass cutoff frequency is set equal to the reciprocal of the shortest interval ( $f_{CUTOFF} = 1/10\mu s$ = 100kHz). If the lowpass cutoff frequency is lower the signal transition and time interval will be distorted beyond recognition by any tag signal detection algorithm. The setting of the highpass cutoff frequency is more qualitative than specific. The highpass cutoff frequency must be lower than the reciprocal of the longest interval (for Figure 18 example, highpass  $f_{CUTOFF} < 1/20\mu s < 50 kHz$ ) and as high as possible to decrease the receiver's low frequency noise (baseband amplifier and down-converted phase and amplitude noise). Figures 18a and 18b show the filter's total response (lowpass plus highpass filter). The filter's output is shown with 30kHz and a 10kHz highpass cutoff frequency setting. Comparing the filter outputs with a 10kHz and a 30kHz highpass setting, the signal transitions and time intervals of the 10kHz output are adequate for

detecting the symbol sequence (in an RFID environment, noise will be superimposed on the output signal). In general, increasing the lowpass  $f_{CUTOFF}$  and/or decreasing

the highpass  $f_{CUTOFF}$  "enhances" signal transitions and intervals and increases filter output noise.

Figure 17. An Adaptable RFID Baseband Filter with SPI Control

Figure 18. Filter Transient Response to a Tag Symbol Sequence

### TYPICAL APPLICATIONS

### PACKAGE DESCRIPTION

UF Package 24-Lead Plastic QFN (4mm × 4mm) (Reference LTC DWG # 05-08-1697)

NOTE:

1. DRAWING PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGD-X)-TO BE APPROVED

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE, IF PRESENT

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON THE TOP AND BOTTOM OF PACKAGE

### TYPICAL APPLICATION

**Direct Conversion Demodulator and Programmable Baseband Filter**

### **RELATED PARTS**

| PART NUMBER               | DESCRIPTION                                                                                       | COMMENTS                                                                                                  |  |

|---------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| LTC1563                   | 4th Order Filter Building Block                                                                   | Lowpass or Bandpass Filter, 256Hz to 256kHz                                                               |  |

| LTC1565-31                | 7th Order, Fully Differential 650kHz Lowpass Filter                                               | No External Components, Low Offset, SO8 Pkg                                                               |  |

| LTC1566-1                 | 7th Order, Fully Differential 2.3MHz Lowpass                                                      | No External Components, Low Noise, SO8 Pkg                                                                |  |

| LT <sup>®</sup> 1567      | Low Noise, Filter Building Block Up to 5MHz                                                       | Differential Rail-to-Rail Output, MSOP Pkg                                                                |  |

| LT1568                    | 4th Order Filter Building Block, Configurable as 2 Matched<br>Lowpass, Bandpass or 4-Pole Lowpass | 200kHz ≤ f <sub>c</sub> ≤ 5MHz, Low Noise, Rail-to-Rail<br>Input/Output, Programmable Gain, Shutdown Mode |  |

| LTC2291                   | Dual 12-Bit, 25 Msps A/D Converter                                                                | Low Power (150mW), Single 3V Supply; 71.4dB SNR, 90dB SFDR                                                |  |

| LTC2296                   | Dual 14-Bit, 25 Msps A/D Converter                                                                | Low Power (150mW), Single 3V Supply; 74.5dB SNR, 90dB SFDR                                                |  |

| LT5516                    | 800MHz to 1.5GHz Direct Conversion I/Q Demodulator                                                | 21.5dBm IIP3; 12.8dB NF                                                                                   |  |

| LT5575                    | 800MHz to 2.7GHz Direct Conversoin I/Q Demodulator                                                | 28dBm IIP3 at 900MHz; 13.2dBm P1dB; Integrated RF Input<br>Balance Transformer                            |  |

| LT6600-<br>2.5/5/10/15/20 | Fully Differential Amplifier and Lowpass Filter<br>Cutoff Frequencies: 2.5MHz/5MHz/10MHz/20MHz    | Programmable Gain, Adjustable Output CM Voltage,<br>Specified for 3V, 5V, ±5V                             |  |