# 11.4 x 9.6 x 2.5mm 6 pad SMD VCXO

- Frequency range 750kHz to 800MHz

- LVDS Output

- Supply Voltage 3.3 VDC

- Phase jitter 2.35ps typical

- Pull range from ±30ppm to ±150ppm

## **DESCRIPTION**

GDW62 VCXOs are packaged in a 6 pad 11.4 x 9.6mm SMD package. Typical phase jitter for GDW series VCXOs is 2.35ps. Output is LVDS. Applications include phase lock loop, SONET/ATM, set-top boxes, MPEG, audio/video modulation, video game consoles and HDTV.

## **SPECIFICATION**

| JI ECII ICATION              |                                                     |  |

|------------------------------|-----------------------------------------------------|--|

| Frequency Range:             | 750kHz to 800.0MHz                                  |  |

| Supply Voltage:              | 3.3 VDC ±5%                                         |  |

| Output Logic:                | LVDS                                                |  |

| RMS Period Jitter:           | 4.3ps typical                                       |  |

| Peak to Peak Jitter:         | 27.0ps typical                                      |  |

| Phase Jitter:                | 2.35ps typical                                      |  |

| Initial Frequency Accuracy:  | Tune to the nominal frequency with Vc= 1.65 ±0.2VDC |  |

| Output Voltage HIGH (1):     | 1.4 Volts typical                                   |  |

| Output Voltage LOW (0):      | 1.1 Volts typical                                   |  |

| Pulling Range:               | From ±30ppm to ±150ppm                              |  |

| Control Voltage Range:       | 1.65 ±1.35 Volts                                    |  |

| Temperature Stability:       | See table                                           |  |

| Output Load:                 | 50Ω into Vdd or Thevenin equiv.                     |  |

| Rise/Fall Times:             | 0.5ns typ., 0.7ns max.                              |  |

|                              | 20% Vdd to 80% Vdd                                  |  |

| Duty Cycle:                  | 50% ±5%                                             |  |

|                              | (Measured at Vdd-1.3V)                              |  |

| Start-up Time:               | 10ms maximum, 5ms typical                           |  |

| Current Consumption:         | 55mA typical, 60mA maximum (At 202.50MHz)           |  |

| Static Discharge Protection: | 2kV maximum                                         |  |

| Storage Temperature:         | -55° to +150°C                                      |  |

| Ageing:                      | ±2ppm per year maximum                              |  |

| Enable/Disable:              | See table                                           |  |

| RoHS Status:                 | Fully compliant or non compliant                    |  |

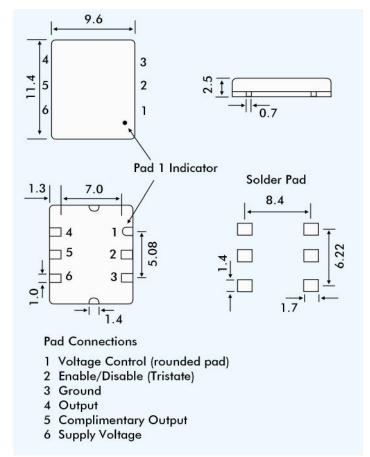

#### **OUTLINE & DIMENSIONS**

# FREQUENCY STABILITY

| Stability Code | Stability ±ppm | Temp. Range |

|----------------|----------------|-------------|

| Α              | 25             | 0°∼+70°C    |

| В              | 50             | 0°~+70°C    |

| С              | 100            | 0°∼+70°C    |

| D              | 25             | -40°~+85°C  |

| E              | 50             | -40°~+85°C  |

| F              | 100            | -40°~+85°C  |

|                |                | 111. 1      |

If non-standard frequency stability is required Use 'I' followed by stability, i.e. I20 for ±20ppm

# **ENABLE/DISABLE FUNCTION**

| Tristate Pad Status | Output Status                              |  |

|---------------------|--------------------------------------------|--|

|                     |                                            |  |

| Not connected       | LVDS and Complimentary LVDS enabled        |  |

| Below 0.3Vdd        | Both outputs are disabled (high impedance) |  |

| (Ref. to ground)    | , , , , ,                                  |  |

| Above 0.7Vdd        | Both outputs are enabled                   |  |

| (Ref. to ground)    | ·                                          |  |

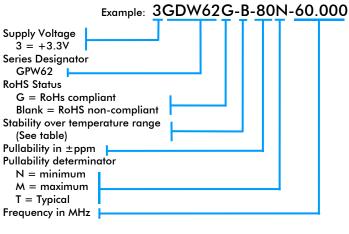

### **PART NUMBERING**