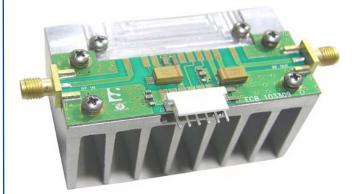

The XD010-EVAL connectorized fixture supports test and measurement of the XD series of LDMOS modules available from Sirenza. The fixture includes convenient SMA female RF connectors along with a DC header to facilitate amplifier characterization, or rapid system prototyping. The test circuit is mounted on an aluminum heatsink that requires forced air cooling to ensure proper device operating temperatures.

# XD010-EVAL

Test Fixture for Sirenza XD Module Series

#### **Product Features**

- 50 Ohm SMA (F) Interface

- Integrated Aluminum Heatsink

- Supports D2, D4, and D5 packages

### **Applications**

- Product Test and Evaluation

- Rapid System Prototyping

- Product Qualification

| Manufacturer                                            | Mfg Part #        | Item Description                                   | Qty | Ref Des |

|---------------------------------------------------------|-------------------|----------------------------------------------------|-----|---------|

| Kemet                                                   | T494D106M035AS    | CAP, 10 UF, 35V, 20%, TANT, ELECT, D               | 2   | C1,C10  |

| Johanson Technology                                     | 101R18W104KV4E    | CAP, 0.1 UF,100V,10%,1206,LEAD FREE                | 2   | C2,C20  |

| Panasonic                                               | ECJ2YB1H104K      | CAP, 0.1 UF, 50V, 10%, 0805                        | 2   | C21,C22 |

| AVX                                                     | 06031C102JAT2A    | CAP, 1000 PF, 100V, 10%, 0603                      | 2   | C23,C24 |

| ATC                                                     | 600S680JT250XT    | CAP, 68PF,250V,5%,0603,LF LEAD FREE                | 2   | C25,C26 |

| Johanson Technology                                     | 101R18W102KV4E    | CAP, 1000 PF,100V,10%,1206,LEAD FREE               | 2   | C3,C30  |

| Johnson Comp                                            | 142-0751-821      | CONNECTOR,SMA END,0.037 JOHNSON<br>COMP            | 2   | J1,J2   |

| Amp                                                     | 640455-6          | CONNECTOR, MTA,SMD,R/A,6 PIN                       | 1   | J3      |

| Various                                                 |                   | WASHER, #4 LOCK, SPLIT, S S                        | 6   |         |

| Various                                                 |                   | WASHER, #4 NARROW, .125 ID, .250 OD, .019<br>T, SS | 6   |         |

| Various                                                 |                   | SCREW, #4-40 PHILLIPS PAN HEAD, 5/16, SS           | 6   |         |

| Rogers 4350, er=3.48, 30 mils thick, 1 oz Cu both sides |                   | PCB, XD010-EVAL                                    | 1   |         |

| Wakefield                                               | 2063-HS Extrusion | Heatsink - Extruded Aluminum, machined             | 1   |         |

## **Basic Bill of Materials**

The information provided herein is believed to be reliable at press time. Sirenza Microdevices assumes no responsibility for inaccuracies or omissions. Sirenza Microdevices assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any thrid party. Sirenza Microdevices and/or systems. Copyright 2003 Sirenza Microdevices, Inc. All worldwide rights reserved.

303 S. Technology Court,

Broomfield. CO 80021

1

EDS-103395 Rev D

# J3 - Pin Description

| Pin # | Function        | Description                                                                                                                                                   |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>G1</sub> | Gate control for stage 1. Sets the quiecent bias current on Pin 3 of the XD Module. Typical values 4.0 – 4.4Vdc. This pin is not used with D2 and D4 modules. |

| 2     | Gnd             | DC ground for D package module. Also connected to RF ground.                                                                                                  |

| 3     | V <sub>D1</sub> | Drain voltage for the first stage. Nominally +28Vdc.                                                                                                          |

| 4     | V <sub>x</sub>  | Not used.                                                                                                                                                     |

| 5     | V <sub>G2</sub> | Gate control for stage 2. Sets the quiecent bias current on Pin 5. Typical values 4.0 – 4.4Vdc. This pin is not used with D2 and D4 modules.                  |

| 6     | V <sub>D2</sub> | Drain voltage for the second stage. Nominally +28Vdc                                                                                                          |

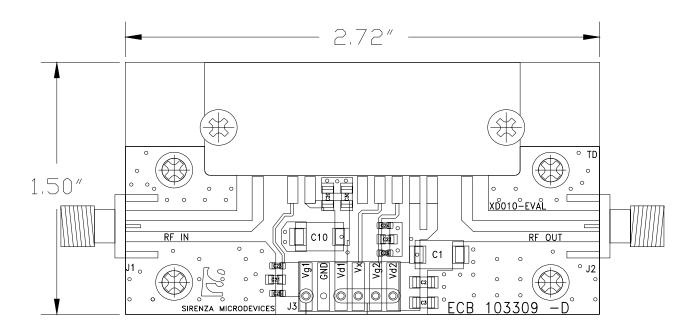

## **Test Board Layout**

#### **XD010-EVAL Test Fixture**

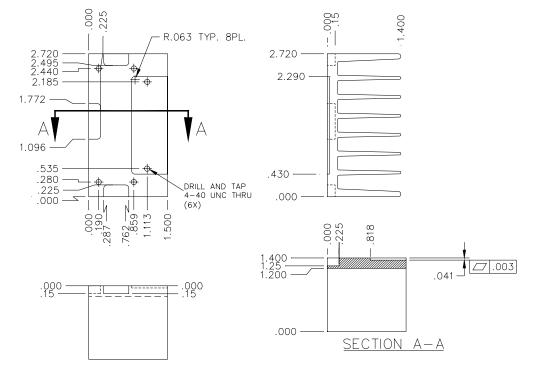

#### **Heatsink Diagram**

Material = Aluminum, Wakefield extrusion # HS-2063

To receive Gerber files, DXF drawings, a detailed BOM, and assembly recommendations for the test board with fixture, contact applications support at <a href="mailto:support@sirenza.com">support@sirenza.com</a>.