# SANYO Semiconductors DATA SHEET

# LV8761V — Forward/Reverse H-bridge Driver

#### Overview

The LV8761V is an H-bridge driver that can control four operation modes (forward, reverse, brake, and standby) of a motor. The low on-resistance, zero standby current, highly efficient IC is optimal for use in driving brushed DC motors for office equipment.

#### **Features**

- Forward/reverse H-bridge motor driver: 1 channel

- Built-in current limiter circuit

- Built-in thermal protection circuit

- Built-in short-circuit protection function

- Unusual condition warning output pin

- Short-circuit protection circuit selectable from latch-type or auto reset-type

## **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol              | Conditions                      | Ratings                      | Unit |

|-----------------------------|---------------------|---------------------------------|------------------------------|------|

| Supply voltage              | VM max              |                                 | 38                           | V    |

|                             | V <sub>CC</sub> max |                                 | 6                            | V    |

| Output peak current         | I <sub>O</sub> peak | tw ≤ 20ms, duty 5%              | 4                            | Α    |

| Output continuous current   | I <sub>O</sub> max  |                                 | 3                            | Α    |

| Logic input voltage         | V <sub>IN</sub>     |                                 | -0.3 to V <sub>CC</sub> +0.3 | V    |

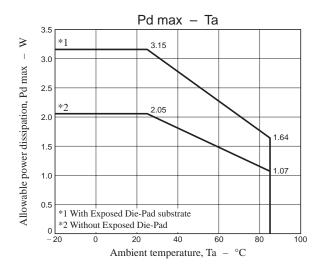

| Allowable power dissipation | Pd max              | Mounted on a specified board. * | 3.15                         | W    |

| Operating temperature       | Topr                |                                 | -20 to +85                   | °C   |

| Storage temperature         | Tstg                |                                 | -55 to +150                  | °C   |

|                             |                     |                                 |                              |      |

<sup>\*</sup> Specified circuit board: 90mm×90mm×1.6mm, glass epoxy 2-layer board (2S0P), with backside mounting.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

# LV8761V

# Allowable Operating Ratings at $Ta = 25^{\circ}C$

| Parameter            | Symbol          | Conditions | Ratings                   | Unit |

|----------------------|-----------------|------------|---------------------------|------|

| Supply voltage range | VM              |            | 9 to 35                   | V    |

|                      | Vcc             |            | 3 to 5.5                  | V    |

| VREF input voltage   | VREF            |            | 0 to V <sub>CC</sub> -1.8 | V    |

| Logic input voltage  | V <sub>IN</sub> |            | 0 to V <sub>CC</sub>      | V    |

# **Electrical Characteristics** at Ta = 25 °C, VM = 24V, $V_{CC} = 5V$ , VREF = 1.5V

| Parameter Symbol Condition                                                        | ns min                                                | Ratings<br>typ |       | Unit        |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------|----------------|-------|-------------|--|

| ,                                                                                 |                                                       | typ            |       | Unii        |  |

| Company                                                                           |                                                       | ٠,١٣           | max   | <b>5111</b> |  |

| General                                                                           |                                                       |                |       |             |  |

| Standby mode current drain 1 IMst PS = "L"                                        |                                                       |                | 1     | μΑ          |  |

| Standby mode current drain 2 I <sub>CC</sub> st PS = "L"                          |                                                       |                | 1     | μΑ          |  |

| Operating mode current drain 1 IM PS = "H", IN1 = "H", with r                     | no load                                               | 1              | 1.3   | mA          |  |

| Operating mode current drain 2 I <sub>CC</sub> PS = "H", IN1 = "H", with r        | no load                                               | 3              | 4     | mA          |  |

| VREG output voltage $VREG = -1mA$                                                 | 4.75                                                  | 5              | 5.25  | >           |  |

| V <sub>CC</sub> low-voltage cutoff voltage VthV <sub>CC</sub>                     | 2.5                                                   | 2.7            | 2.9   | >           |  |

| Low-voltage hysteresis voltage VthHIS                                             | 120                                                   | 150            | 180   | mV          |  |

| Thermal shutdown temperature TSD Design guarantee *                               | 155                                                   | 170            | 185   | °C          |  |

| Thermal hysteresis width ΔTSD Design guarantee *                                  |                                                       | 40             |       | °C          |  |

| Output block                                                                      | ·                                                     |                |       |             |  |

| Output on resistance Ron1 I <sub>O</sub> = 3A, sink side                          |                                                       | 0.2            | 0.25  | Ω           |  |

| Ron2 I <sub>O</sub> = -3A, source side                                            |                                                       | 0.32           | 0.40  | Ω           |  |

| Output leakage current I <sub>O</sub> leak V <sub>O</sub> = 35V                   |                                                       |                | 50    | μΑ          |  |

| Rising time tr 10% to 90%                                                         |                                                       | 200            | 500   | ns          |  |

| Falling time tf 90% to 10%                                                        |                                                       | 200            | 500   | ns          |  |

| Input output delay time tpLH IN1 or IN2 to OUTA or OL                             | JTB (L → H)                                           | 550            | 700   | ns          |  |

| tpHL IN1 or IN2 to OUTA or OU                                                     | JTB (H → L)                                           | 550            | 700   | ns          |  |

| Charge pump block                                                                 |                                                       |                |       |             |  |

| Step-up voltage VGH VM = 24V                                                      | 28.0                                                  | 28.7           | 29.8  | V           |  |

| Rising time $tONG 	VG = 0.1 \mu F$                                                | VG = 0.1μF 250                                        |                | 500   | μs          |  |

| Oscillation frequency Fcp                                                         | 115                                                   | 140            | 165   | kHz         |  |

| Control system input block                                                        | Control system input block                            |                |       |             |  |

| Logic pin input current 1 $I_{IN}L$ $V_{IN} = 0.8V$ adaptive pin :                | PS 5.6                                                | 8              | 10.4  | μΑ          |  |

| I <sub>IN</sub> H V <sub>IN</sub> = 5V adaptive pin : P                           | S 56                                                  | 80             | 104   | μΑ          |  |

| Logic pin input current 2 I <sub>IN</sub> L V <sub>IN</sub> = 0.8V adaptive pin : | IN1, IN2, EMM 5.6                                     | 8              | 10.4  | μΑ          |  |

| I <sub>IN</sub> H V <sub>IN</sub> = 5V adaptive pin : IN                          | N1, IN2, EMM 35                                       | 50             | 65    | μΑ          |  |

| Logic pin input H-level voltage V <sub>IN</sub> H adaptive pin : PS, IN1, IN2     | adaptive pin : PS, IN1, IN2, EMM 2.0                  |                |       | V           |  |

| Logic pin input L-level voltage V <sub>IN</sub> L adaptive pin : PS, IN1, IN2     | V <sub>IN</sub> L adaptive pin : PS, IN1, IN2, EMM 0. |                | 0.8   | V           |  |

| Current limiter block                                                             |                                                       |                |       |             |  |

| VREF input current IREF                                                           | -0.5                                                  |                |       | μΑ          |  |

| Current limit comparator Vthlim VREF = 1.5V                                       | 0.285                                                 | 0.3            | 0.315 | V           |  |

| hreshold voltage                                                                  |                                                       |                |       |             |  |

| Short-circuit protection block                                                    | 1                                                     | 1              | 1     |             |  |

|                                                                                   | SCP = 0V 3.5 5 6                                      |                | 6.5   | μA          |  |

| Comparator threshold voltage Vthscp                                               | 0.8 1                                                 |                | 1.2   | V           |  |

| EMO output saturation voltage Vemo $I_O = 500\mu A$                               |                                                       | 0.3            | 0.4   | V           |  |

<sup>\*</sup> Design guarantee value and no measurement is made.

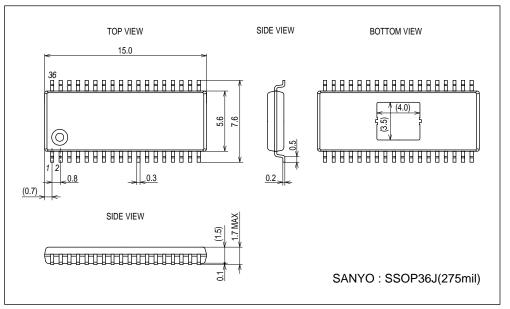

## **Package Dimensions**

unit: mm (typ)

3361

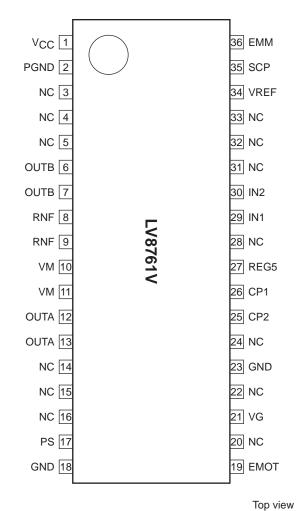

# **Pin Assignment**

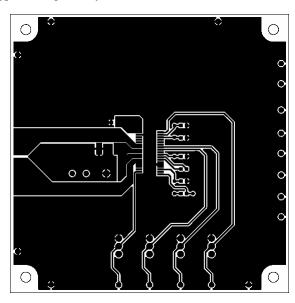

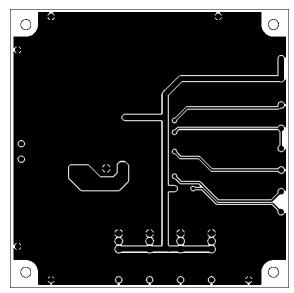

Substrate Specifications (Substrate recommended for operation of LV8761T)

Size :  $90\text{mm} \times 90\text{mm} \times 1.6\text{mm}$  (two-layer substrate [2S0P])

Material : Glass epoxy

Copper wiring density : L1 = 95% / L2 = 95%

L1: Copper wiring pattern diagram

L2: Copper wiring pattern diagram

## Cautions

- 1) The data for the case with the Exposed Die-Pad substrate mounted shows the values when 90% or more of the Exposed Die-Pad is wet.

- 2) For the set design, employ the derating design with sufficient margin.

Stresses to be derated include the voltage, current, junction temperature, power loss, and mechanical stresses such as vibration, impact, and tension.

Accordingly, the design must ensure these stresses to be as low or small as possible.

The guideline for ordinary derating is shown below:

- (1)Maximum value 80% or less for the voltage rating

- (2)Maximum value 80% or less for the current rating

- (3)Maximum value 80% or less for the temperature rating

- 3) After the set design, be sure to verify the design with the actual product.

Confirm the solder joint state and verify also the reliability of solder joint for the Exposed Die-Pad, etc. Any void or deterioration, if observed in the solder joint of these parts, causes deteriorated thermal conduction,

possibly resulting in thermal destruction of IC.

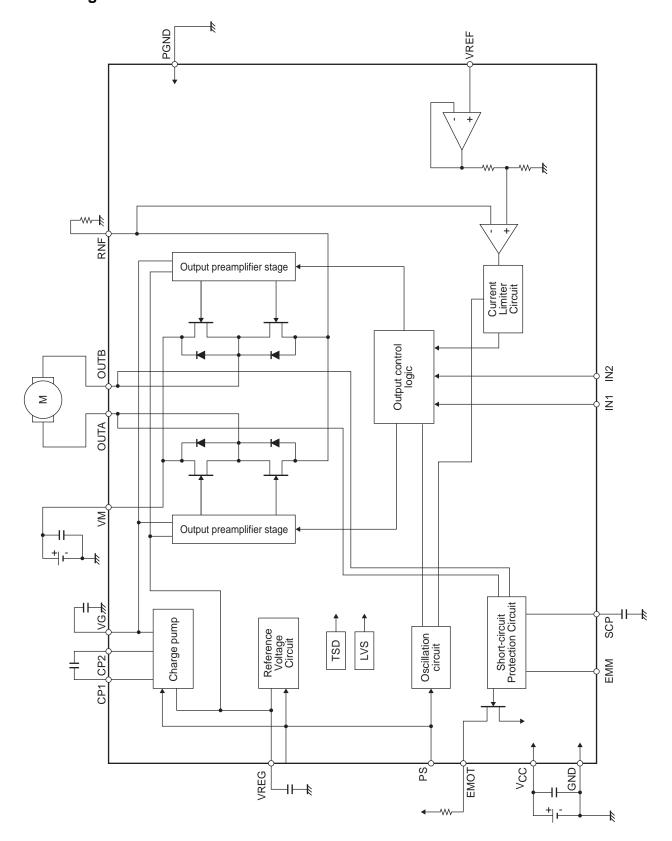

# **Block Diagram**

# LV8761V

#### **Pin Functions**

| ı ııı ı uı | ctions   |                                             |                                                                   |

|------------|----------|---------------------------------------------|-------------------------------------------------------------------|

| Pin No.    | Pin Name | Pin Functtion                               | Equivalent Circuit                                                |

| 29         | IN1      | Output control signal input pin 1.          |                                                                   |

| 30         | IN2      | Output control signal input pin 2.          | VCC O                                                             |

| 36         | EMM      | Short-circuit protection circuit mode       |                                                                   |

| 30         | LIVIIVI  | switching pin.                              |                                                                   |

|            |          | Switching pin.                              |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | 10kΩ                                                              |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | * \$100kΩ                                                         |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | GNDO                                                              |

|            |          |                                             | 5115 0                                                            |

| 17         | PS       | Power save signal input pin.                | VCC O-                                                            |

|            |          |                                             | VCC 0                                                             |

|            |          |                                             | 1                                                                 |

|            |          |                                             | <b>★</b>                                                          |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | 50kΩ \( \begin{pmatrix} 10kΩ \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|            |          |                                             | 10kΩ                                                              |

|            |          |                                             | 10kΩ 10kΩ                                                         |

|            |          |                                             |                                                                   |

|            |          |                                             | 50kΩ <del>\$</del>                                                |

|            |          |                                             | GND O                                                             |

|            |          |                                             | G.1.5 s                                                           |

| 34         | VREF     | Reference voltage input pin for output      | VCC O                                                             |

|            |          | current limit setting.                      |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | 500Ω                                                              |

|            |          |                                             |                                                                   |

|            |          |                                             | <b>*</b>                                                          |

|            |          |                                             | OND O                                                             |

|            |          |                                             | GND ○                                                             |

| 35         | SCP      | Short-circiut protection circuit, detection | Vac o                                                             |

|            |          | time setting capacitor connection pin.      | Vcc o                                                             |

|            |          |                                             |                                                                   |

|            |          |                                             | <u> </u>                                                          |

|            |          |                                             | <b> </b>                                                          |

|            |          |                                             |                                                                   |

|            |          |                                             | 500Ω                                                              |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             |                                                                   |

|            |          |                                             | T                                                                 |

|            |          |                                             |                                                                   |

|            |          |                                             | GND O                                                             |

|            |          |                                             |                                                                   |

| 1          | VCC      | Power supply connection pin for control     |                                                                   |

|            |          | block.                                      |                                                                   |

Continued on next page.

# LV8761V

|                        | Pin Name              | Pin Functtion                                                                                                             | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12, 13<br>8, 9<br>6, 7 | VM OUTA RNF OUTB PGND | Motor power-supply connection pin. OUTA output pin. Current sense resistor connection pin. OUTB output pin. Power ground. | REG5 $\bigcirc$ $1001$ $1001$ $13$ $500\Omega$ $2$ $8$ $9$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25                     | CP1<br>CP2<br>VG      | Charge pump capacitor connection pin. Charge pump capacitor connection pin. Charge pump capacitor connection pin.         | REG5 Ο 10(1) (25) (21) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (10(1) (25) (25) (25) (25) (25) (25) (25) (25 |

| 27                     | REG5                  | Internal reference voltage output pin.                                                                                    | $VM \circ$ $2k\Omega$ $25k\Omega$ $300$ $400$ $200$ $200$ $200$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19                     | EMOT                  | Unusual condition warning output pin.                                                                                     | VCC Ο 500Ω W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### **DC Motor Driver**

## 1.DCM output control logic

| Contol Input |     |     | Ou   | tput | Mode          |  |

|--------------|-----|-----|------|------|---------------|--|

| PS           | IN1 | IN2 | OUTA | OUTB | Wode          |  |

| L            | *   | *   | OFF  | OFF  | Standby       |  |

| Н            | L   | L   | OFF  | OFF  | Output OFF    |  |

| Н            | Н   | L   | Н    | L    | CW (forward)  |  |

| Н            | L   | Н   | L    | Н    | CCW (reverse) |  |

| Н            | Н   | Н   | L    | L    | Brake         |  |

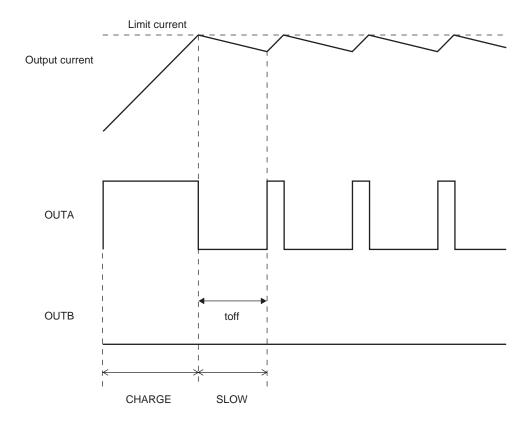

### 2. Current limit control timing chart

Braking operation time in current limit mode can be set by connecting a capacitor between SCP and GND pins. This setting is the same as the time setting required to turn off the outputs when an output short-circuit occurs as explained in the section entitled "Output Short-circuit Protection Function." See "Output Short-circuit Protection Function," for the setting procedure.

## 3. Setting the current limit value

The current limit value of the DCM driver is determined by the VREF voltage and the resistance (RNF) connected across the RNF and GND pins using the following formula:

Ilimit [A] =

$$(VREF [V] /5) /RNF [\Omega])$$

Assuming VREF = 1.5V, RNF =  $0.2\Omega$ , the current limit is :

$Ilimit = 1.5V/5/0.2\Omega = 1.5A$

#### **Output short-circuit protection function**

The LV8761V incorporates an output short-circuit protection circuit that turns off the output to prevent the IC from fatal damage when the output is short-circuited due to short-to-power or short-to-ground fault. Either the "latch-type," in which the output off state is latched when the short-circuit protection circuit is activated, or "auto reset-type," in which the output on/off states are repeated when the short-circuit protection circuit is activated, can be selected.

| EMM Pin | Short-circuit Protection Mode |  |

|---------|-------------------------------|--|

| L       | Latch type                    |  |

| Н       | Auto reset type               |  |

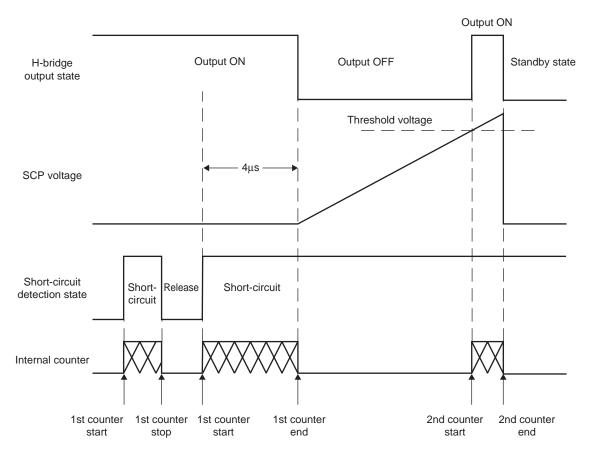

#### 1. Protection function operation (Latch method)

The short-circuit protection circuit is activated when it detects the output short-circuit state. If the short-circuit state continues for the internally preset period ( $\approx 4\mu s$ ), the protection circuit turns off the output from which the short-circuit state has been detected. Then it turns the output on again after a lapse of the timer latch time described later. If the short-circuit state is still detected, it changes all the outputs to the standby mode and retains the state. The latched state is released by setting the PS to L.

## 2. How to set the SCP pin constant (timer latch-up setting)

The user can set the time at which the outputs are turned off when a short-circuit occurs by connecting a capacitor across the SCP and GND pins. The value of the capacitor can be determined by the following formula:

Timer latch-up : Tocp Tocp  $\approx C \times V/I[s]$

V : Comparator threshold voltage (1V typical)

I : SCP charge current (5µA typical)

When a capacitor with a capacitance of 50pF is connected across the SCP and GND pins, for example, Tscp is calculated as follows:

$$Tscp = 50pF \times 1V/5\mu A = 10\mu s$$

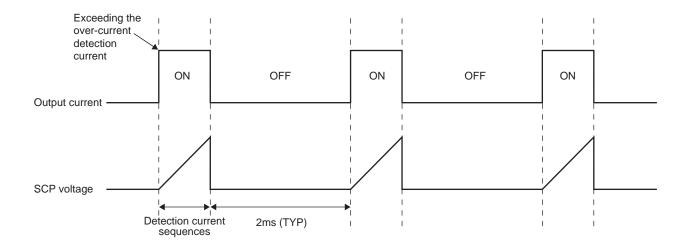

#### 3. Auto Reset Type

The sequences up to the detection of an output short-circuit state are identical to those which are explained in Section 1, "Protection Function Operation (Latch Type).

After output is turned off on detection of an output short-circuit condition, the internal counter starts counting and repeats turning on and off the output as shown in the figure below.

This state continues until the overcurrent state is eliminated.

#### 4. Unusual Condition Warning Output Pin (EMOT)

The LV8761V is provided with the EMOT pin which notifies the CPU of an unusual condition if the protection circuit operates by detecting an abnormal condition of the IC. This pin is of the open-drain output type and requires a pull-up resistor when to be used.

The EMOT pin is placed in the ON state when one of the following conditions occurs.

- 1. Shorting-to-power or shorting-to-ground occurs at the output pin and the output short-circuit protection circuit is activated.

- 2. The IC junction temperature rises and the thermal protection circuit is activated.

The EMOT pin is set to the OFF state when the relevant protection operation is eliminated.

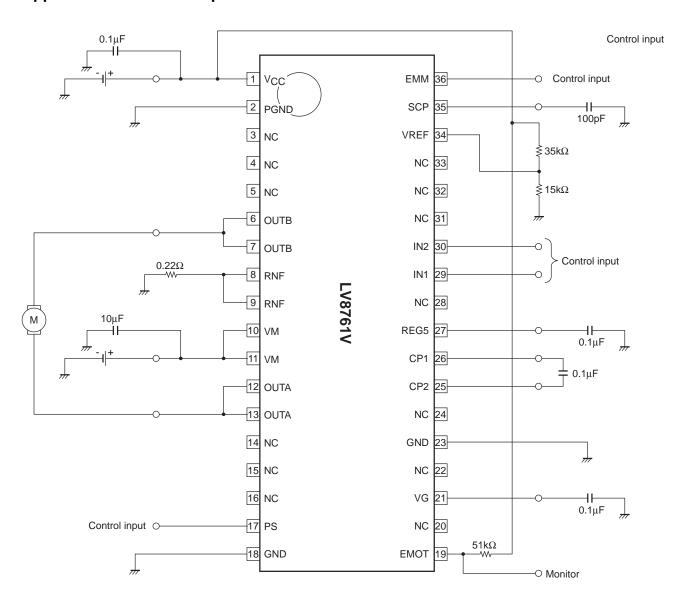

## **Application Circuit Example**

Setting the current limit value

When

$$V_{CC} = 5V$$

,

$V_{ref} = 1.5V$

$Ilimit = V_{ref}/5/RNF$

$= 1.5V/5/0.22\Omega = 1.36A$

Setting the current limit regeneration time and short-circuit detection time

$$\begin{split} Tscp &\approx C \times V/I \\ &= 100 pF \times 1V/5 \mu A \\ &= 20 \mu s \end{split}$$

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of April, 2008. Specifications and information herein are subject to change without notice.