# **DirectCore**

## **Product Summary**

#### **Intended Use**

- Analog Interface Control Using a Microprocessor/ Microcontroller and an Actel Fusion<sup>TM</sup> Device

- Voltage, Current, and Temperature Monitoring Using a Microprocessor/Microcontroller and an Actel Fusion Device

#### **Key Features**

- ADC Conversions Controlled by MCU/MPU Writes

- AMBA APB Slave Interface (8- or 16-Bit Data Widths Supported)

- 14 Maskable Interrupt Sources

- Internal Clock Divider for Generating Analog Configuration MUX Clock

- Optional Read FIFO Stores up to 256 ADC Conversion Results

- Analog Configuration MUX Can Be Configured by SmartGen

#### **Supported Families**

• Fusion (including M7 devices)

#### **Core Deliverables**

- Evaluation Version

- Compiled RTL Simulation Model Fully Supported in Actel Libero<sup>®</sup> Integrated Design Environment (IDE)

- Netlist Version

- Structural Verilog and VHDL Netlists (with and without I/O Pads) Compatible with Actel Designer Software Place-and-Route Tool

- Compiled RTL Simulation Model Fully Supported in Actel Libero IDE

- RTL Version

- Verilog and VHDL Core Source Code

- Core Synthesis Scripts

- Testbench (Verilog and VHDL)

### **Synthesis and Simulation Support**

- Directly Supported within Actel Libero IDE and CoreConsole

- Synthesis: Synplicity<sup>®</sup>, Synopsys<sup>®</sup> (Design Compiler / FPGA Compiler / FPGA Express), Exemplar

- Simulation: OVI-Compliant Verilog Simulators and Vital-Compliant VHDL Simulators

#### **Core Verification**

- Comprehensive VHDL and Verilog Testbenches

- User Can Easily Modify User Testbench Using Existing Format to Add Custom Tests

### Contents

| General Description            | 1  |

|--------------------------------|----|

| Functional Block Descriptions  | 3  |

| CoreAI Device Requirements     | 3  |

| CoreAl Verification            | 3  |

| I/O Signal Descriptions        | 4  |

| Parameter/Generic Descriptions | 6  |

| Internal CoreAI Registers 1    | 0  |

| ACM Interface 1                | 8  |

| RTC Operation 2                | 21 |

| ADC Operation 2                | 22 |

| Interrupt Logic 2              | 23 |

| Ordering Information 2         | 24 |

| Datasheet Categories 2         | 24 |

|                                |    |

### **General Description**

CoreAI (Analog Interface) allows for simple control of the analog peripherals within the Fusion family of Actel devices. Control may be implemented with an internal or external microprocessor or microcontroller (such as Core8051 or CoreMP7), or with user-created custom logic within the FPGA fabric. The industry-standard AMBA (Advanced Microcontroller Bus Architecture) APB (Advanced Peripheral Bus) slave interface is used as the primary control mechanism within CoreAI.

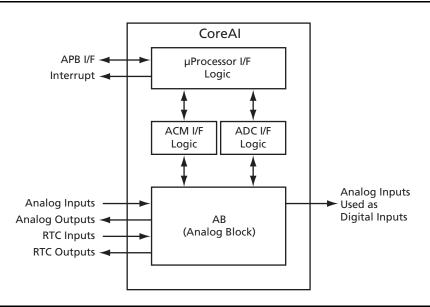

CoreAI instantiates the AB (Analog Block) macro, as shown in Figure 1 on page 2. The AB macro includes the

ACM (Analog Configuration MUX) interface, Analog Quads, and RTC (Real-Time Counter). The ACM interface, within the AB macro, is used to control configuration of the Analog Quads and RTC in the Fusion device. CoreAI generates the control signals used by the ACM, including its clock signal, which is generated by an internal clock divider. The ACM clock divider is used to ensure that the ACM interface is clocked at a frequency less than or equal to 10 MHz (refer to "ACM Interface" on page 18 for details). For more details on the silicon features of the AB macro, such as the Analog Quads, RTC, or ACM, refer to the *Fusion datasheet*.

Several aspects of CoreAI can be configured using toplevel parameters (Verilog) or generics (VHDL). For a detailed description of the parameters/generics, refer to Table 4 on page 6.

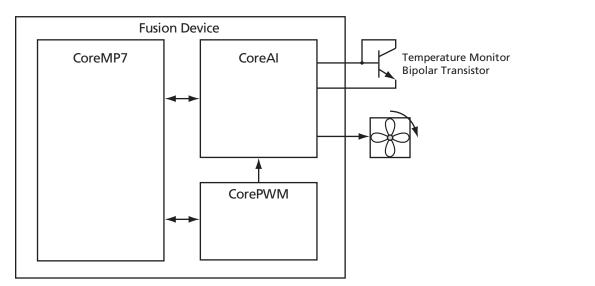

The CoreAI block diagram is shown in Figure 1. A typical application using CoreAI is shown in Figure 2.

Figure 1 • CoreAl Block Diagram

Figure 2 • CoreAl Typical Application

## **Functional Block Descriptions**

CoreAI, shown in Figure 1 on page 2, consists of the microprocessor interface logic, ACM interface logic, and ADC interface logic blocks. The microprocessor interface logic implements APB slave logic and generates a

maskable interrupt. The ACM interface block writes configuration data into the AB macro to control Analog Quad and RTC settings. The ADC interface block sends control data to and receives status information from the ADC.

## **CoreAI Device Requirements**

CoreAI has been implemented in the Actel Fusion device family. A summary of the data for CoreAI is listed in Table 1 and Table 2.

|        | Cells or Tiles |               |       | Utilization |       |             |

|--------|----------------|---------------|-------|-------------|-------|-------------|

| Family | Sequential     | Combinatorial | Total | Device      | Total | Performance |

| Fusion | 45             | 105           | 150   | AFS090      | 7%    | 150 MHz     |

**Note:** Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics that differ from the default values were set as follows: FIXED\_VAREFSEL = 1, FIXED\_VAREFSEL\_VAL = 0, FIXED\_MODE = 1, FIXED\_MODE\_VAL = 0, FIXED\_TVC = 1, FIXED\_TVC\_VAL = 0, FIXED\_STC = 1, FIXED\_STC\_VAL = 0, CFG\_ACx = 512, CFG\_ATx = 512, DISABLE\_TMSTBINT = 1, CFG\_GDx = 768, ACTLOW\_INTERRUPT = 0, DISABLE\_INTERRUPT = 1, APB\_16BIT\_DATA = 1.

Table 2 • CoreAI Device Utilization and Performance (maximum configuration)

| Family | Cells or Tiles |               |       | Utilization |        | Performance |         |

|--------|----------------|---------------|-------|-------------|--------|-------------|---------|

|        | Sequential     | Combinatorial | Total | FIFO        | Device | Total       |         |

| Fusion | 130            | 330           | 460   | 1           | AFS090 | 20%         | 133 MHz |

**Note:** Data in this table were achieved using typical synthesis and layout settings. Top-level parameters/generics that differ from the default values were set as follows: ACM\_CLK\_DIV = 4, USE\_RTC = 1, USE\_RDFIFO = 1, USE\_RDFIFO\_AEVAL = 16, USE\_RDFIFO\_AFVAL = 240.

## **CoreAl Verification**

The comprehensive simulation testbench verifies correct operation of the CoreAI macro.

The testbench applies several tests to the CoreAI macro, including the following:

- Voltage monitor, current monitor, and temperature monitor tests

- RTC tests

- Gate-driver control tests

Using the supplied testbench as a guide, the user can alter the verification of the core by adding custom tests or removing existing tests.

## **I/O Signal Descriptions**

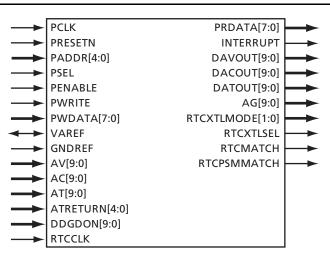

The port signals for the CoreAI macro are defined in Table 3 and illustrated in Figure 3. CoreAI has 120 I/O signals. Note that vector notation is used in Figure 3 for the AV, AC, AT, ATRETURN, DDGDON, DAVOUT, DACOUT, DATOUT, AG, and RTCXTLMODE ports; however, these ports are actually split into individual single-bit ports, as described in Table 3. For example, there are two individual output ports, RTCXTLMODE1 and RTCXTLMODE0, rather than one vectored output port RTCXTLMODE[1:0].

#### Figure 3 • CoreAl I/O Signal Diagram

#### Table 3 • CoreAl I/O Signal Descriptions

| Name          | Туре   | Description                                                                                                                                                                                                                                                             |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APB Interface |        |                                                                                                                                                                                                                                                                         |

| PCLK          | Input  | APB System Clock: reference clock for all internal logic                                                                                                                                                                                                                |

| PRESETN       | Input  | APB active-low asynchronous reset                                                                                                                                                                                                                                       |

| PADDR[4:0]    | Input  | APB address bus – This port is used to address internal CoreAI registers.                                                                                                                                                                                               |

| PSEL          | Input  | APB Slave Select – This signal selects CoreAI for reads or writes.                                                                                                                                                                                                      |

| PENABLE       | Input  | APB Strobe – This signal indicates the second cycle of an APB transfer.                                                                                                                                                                                                 |

| PWRITE        | Input  | APB Write/Read – If high, a write will occur when an APB transfer to CoreAI takes place; if low, a read from CoreAI will take place.                                                                                                                                    |

| PWDATA[15:0]  | Input  | APB write data – If the APB_16BIT_DATA parameter/generic is set to 1, all 16 bits are used; if the APB_16BIT_DATA parameter/generic is set to 0, only the lower 8 bits, PWDATA[7:0], are used (in this case, PWDATA[15:8] should be tied to static high or low values). |

| PRDATA[15:0]  | Output | APB read data – If the APB_16BIT_DATA parameter/generic is set to 1, all 16 bits are used; if the APB_16BIT_DATA parameter/generic is set to 0, only the lower 8 bits, PRDATA[7:0], are used (in this case, PRDATA[15:8] can be left unconnected).                      |

| INTERRUPT     | Output | Microprocessor interrupt output – This interrupt signal is generated from 14 possible interrupt sources, each of which can be masked or enabled via the INTENABLE register. The polarity of this output is controlled via the ACTLOW_INTERRUPT parameter/generic.       |

Note: All signals active high (logic 1) unless otherwise noted.

| Table 3 | <ul> <li>CoreAl I/O</li> </ul> | Signal | Descriptions | (Continued) |

|---------|--------------------------------|--------|--------------|-------------|

|---------|--------------------------------|--------|--------------|-------------|

| Name                                                                                                 | Туре               | Description                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Interface                                                                                     |                    |                                                                                                                                                                                                                                                                                  |

| VAREF                                                                                                | Input or<br>Output | Voltage reference – If using the internal voltage reference, this signal will be an output; if using an external voltage reference, this signal will be an input for this reference (see the FIXED_VAREFSEL and FIXED_VAREFSEL_VAL parameters/generics).                         |

| GNDREF                                                                                               | Input              | Ground reference – If external voltage reference is used, this signal must be connected to the ground for the reference; otherwise this should be connected to digital ground (logic 0).                                                                                         |

| AV9, AV8, AV7, AV6, AV5,<br>AV4, AV3, AV2, AV1, AV0                                                  | Input              | <ul> <li>Analog Voltage Monitor inputs – These signals correspond to the AVx voltage monitor inputs (AV9 through AV0) of the AB macro.</li> <li>Note: Unused AVx inputs need to be disabled with the CFG_AVx parameters/generics and connected to logic 0.</li> </ul>            |

| AC9, AC8, AC7, AC6, AC5,<br>AC4, AC3, AC2, AC1, AC0                                                  | Input              | Analog Current Monitor inputs – These signals correspond to the ACx current monitor inputs (AC9 through AC0) of the AB macro.<br>Note: Unused ACx inputs need to be disabled with the CFG_ACx parameters/generics and connected to logic 0.                                      |

| AT9, AT8, AT7, AT6, AT5,<br>AT4, AT3, AT2, AT1, AT0                                                  | Input              | <ul> <li>Analog Temperature Monitor inputs – These signals correspond to the ATx temperature monitor inputs (AT9 through AT0) of the AB macro.</li> <li>Note: Unused ATx inputs need to be disabled with the CFG_ATx parameters/generics and connected to logic 0.</li> </ul>    |

| ATRETURN4, ATRETURN3,<br>ATRETURN2, ATRETURN1,<br>ATRETURN0]                                         | Input              | Shared Analog Temperature Monitor Returns – These signals correspond to the shared returns for the temperature monitor inputs (ATRETURN89 through ATRETURN01) of the AB macro.                                                                                                   |

| DAVOUT9, DAVOUT8,<br>DAVOUT7, DAVOUT6,<br>DAVOUT5, DAVOUT4,<br>DAVOUT3, DAVOUT2,<br>DAVOUT1, DAVOUT0 | Output             | Digital AV outputs – These signals correspond to the digital AV outputs (DAVOUT9 through DAVOUT0) of the AB macro. If any of the AVx inputs are configured as digital inputs rather than analog inputs, their corresponding buffered digital signals are put out on these ports. |

| DACOUT9, DACOUT8,<br>DACOUT7, DACOUT6,<br>DACOUT5, DACOUT4,<br>DACOUT3, DACOUT2,<br>DACOUT1, DACOUT0 | Output             | Digital AC outputs – These signals correspond to the digital AC outputs (DACOUT9 through DACOUT0) of the AB macro. If any of the ACx inputs are configured as digital inputs rather than analog inputs, their corresponding buffered digital signals are put out on these ports. |

| DATOUT9, DATOUT8,<br>DATOUT7, DATOUT6,<br>DATOUT5, DATOUT4,<br>DATOUT3, DATOUT2,<br>DATOUT1, DATOUT0 | Output             | Digital AT outputs – These signals correspond to the digital AT outputs (DATOUT9 through DATOUT0) of the AB macro. If any of the ATx inputs are configured as digital inputs rather than analog inputs, their corresponding buffered digital signals are put out on these ports. |

| DDGDON9, DDGDON8,<br>DDGDON7, DDGDON6,<br>DDGDON5, DDGDON4,<br>DDGDON3, DDGDON2,<br>DDGDON1, DDGDON0 | Input              | Direct Digital Gate Driver enables – These signals can control the corresponding GDONx gate-driver enable inputs (GDON9 through GDON0) of the AB macro if the CFG_GDx parameters/generics are set appropriately (refer to "Parameter/Generic Descriptions" on page 6).           |

| AG9, AG8, AG7 AG6, AG5,<br>AG4, AG3, AG2, AG1, AG0                                                   | Output             | <ul> <li>Analog Gate Driver outputs – These signals correspond to the AGx gate driver outputs (AG9 through AG0) of the AB macro.</li> <li>Note: If unused, each of these gate driver outputs can be disabled via the CFG_GDx parameters/generics.</li> </ul>                     |

Note: All signals active high (logic 1) unless otherwise noted.

| Name                        | Туре   | Description                                                                                                                                                                                                                                                       |

|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTCCLK                      | Input  | RTC Clock input – If the RTC is used (via the USE_RTC parameter/generic), this input must come from the internal crystal oscillator (XTLOSC) CLKOUT pin; if the RTC is not used, this pin should be tied low.                                                     |

| RTCXTLMODE1,<br>RTCXTLMODE0 | Output | RTC XTLOSC Mode outputs – If the RTC is used (via the USE_RTC parameter/generic), these output ports must be connected to the internal crystal oscillator (XTLOSC) RTCMODE[1:0] pins; if the RTC is not used, these pins should be left unconnected.              |

| RTCXTLSEL                   | Output | RTC XTLOSC Mode Selection output – If the RTC is used (via the USE_RTC parameter/<br>generic), this output port must be connected to the internal crystal oscillator (XTLOSC)<br>MODESEL pin; if the RTC is not used, this pin should be left unconnected.        |

| RTCMATCH                    | Output | RTC Match output – If the RTC is used (via the USE_RTC parameter/generic), this output port indicates that a match event has occurred and can be connected to other FPGA logic; if the RTC is not used, this pin should be left unconnected.                      |

| RTCPSMMATCH                 | Output | RTC Match VRPSM output – If the RTC is used (via the USE_RTC parameter/generic), this output port can be connected to the VRPSM pin of the internal voltage regulator to control regulator power-up; if the RTC is not used, this pin should be left unconnected. |

Table 3 • CoreAl I/O Signal Descriptions (Continued)

Note: All signals active high (logic 1) unless otherwise noted.

## **Parameter/Generic Descriptions**

CoreAI has parameters (Verilog) and generics (VHDL), described in Table 4, for configuring the RTL code. All parameters and generics are integer types.

| Table 4 • CoreAl Parameters/Generics Descriptions | S |

|---------------------------------------------------|---|

|---------------------------------------------------|---|

| Name              | Valid Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APB_16BIT_DATA    | 0 or 1      | Set this to 1 if the APB reads and writes are using all 16-bits of the PRDATA[15:0] and PWDATA[15:0] ports, or to 0 if 8-bit APB reads and writes are done on the PRDATA[15:0] and PWDATA[15:0] ports. If 8-bit APB reads and writes are used, only the lower eight bits of each port are used, i.e., PRDATA[7:0] and PWDATA[7:0]; PWDATA[15:8] should be tied statically high or low and PRDATA[15:8] should be left unconnected in this case. Note that for 16-bit reads and writes, the internal address map shown in Table 9 on page 11 will concatenate adjacent bytes since PADDR[0] = 0 will correspond to the LSB and each byte that is addressed by PADDR[0] = 1 will correspond to the MSB of each 16-bit word. The default value of 0 uses 8-bit APB reads and writes. |

| ACTLOW_INTERRUPT  | 0 or 1      | Interrupt Active Low: Set this to 1 if the INTERRUPT output polarity is active low, or to 0 if the INTERRUPT output polarity is active high. The default value of 0 is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DISABLE_INTERRUPT | 0 or 1      | Disable Interrupt: Set this to 1 if the INTERRUPT output will not be used, in which case the INTERRUPT output will be fixed at the inactive polarity chosen by ACTLOW_INTERRUPT, i.e., INTERRUPT = ACTLOW_INTERRUPT; set this to 0 if the INTERRUPT output is used. The default value of 0 uses the INTERRUPT output.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**Note:** \*Invalid values are 3, 7, 11, and 15 (refer to the *Fusion datasheet*).

| Name               | Valid Range                                 | Description                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACM_CLK_DIV        | 1 to 4                                      | Set this to the division value to generate the ACM clock, which has a maximum frequency of 10 MHz. The actual value will be the frequency of PCLK divided by (2 <sup>ACM_CLK_DIV</sup> ); valid values are 1–4. The default value of 1 sets the ACM clock at half the PCLK frequency.                                                                                              |

|                    |                                             | <b>Note:</b> It is the user's responsibility to ensure that the ACM clock has a maximum operating frequency of 10 MHz.                                                                                                                                                                                                                                                             |

| USE_RTC            | 0 or 1                                      | Use RTC: Set this to 1 if the RTC is to be used, or to 0 if the RTC is not to be used. The default value of 0 does not use the RTC.                                                                                                                                                                                                                                                |

| USE_RDFIFO         | 0 or 1                                      | Use Read FIFO: Set this to 1 if using an internal data FIFO for storing up to 256 ADC conversion results for later reading by a microprocessor, or to 0 if not using the FIFO. The default value of 0 does not use a read FIFO.                                                                                                                                                    |

| USE_RDFIFO_AEVAL   | 0 to 255                                    | Read FIFO Almost Empty Value: Set this 8-bit integer to the fixed almost empty value of the read FIFO. This value determines when the almost empty flag output from the read FIFO becomes active; it represents the number of 16-bit ADC conversion result words that are left to be read before the read FIFO will be empty.<br><b>Note:</b> This is only used if USE_RDFIFO = 1. |

| USE_RDFIFO_AFVAL   | 0 to 255                                    | Read FIFO Almost Full Value: Set this 8-bit integer to the fixed almost full value<br>of the read FIFO. This value determines when the almost full flag output from<br>the read FIFO becomes active; it represents the number of 16-bit ADC<br>conversion result words that are left to be written before the read FIFO will be<br>full.                                           |

|                    |                                             | <b>Note:</b> This is only used if USE_RDFIFO = 1.                                                                                                                                                                                                                                                                                                                                  |

| FIXED_VAREFSEL     | 0 or 1                                      | Set this to 1 if the VAREFSEL input pin of the AB macro is to be fixed, or to 0 to allow register-controlled VAREFSEL setting (saves some logic tiles for a fixed system). The default value of 0 does not have a fixed VAREFSEL setting.                                                                                                                                          |

| FIXED_VAREFSEL_VAL | 0 or 1                                      | Fixed VAREFSEL Value: Set this to a 1-bit constant value (set in higher-level wrapper). Set to 1 to select external VAREF as input, 0 to select internal VAREF as output.<br><b>Note:</b> This is only used if FIXED_VAREFSEL = 1.                                                                                                                                                 |

| FIXED_MODE         | 0 or 1                                      | Set this to 1 if the MODE[3:0] pins of the AB macro are a fixed constant, or to 0 to allow register-controlled MODE[3:0] setting (saves some logic tiles for a fixed system). The default of 0 does not have a fixed MODE[3:0] setting.                                                                                                                                            |

| FIXED_MODE_VAL     | 0 to 2,<br>4 to 6,<br>8 to 10,<br>12 to 14* | Fixed MODE Value: Set this to the integer value of the 4-bit fixed constant connected to the MODE[3:0] input pins of the AB macro (controls ADC resolution, etc.).<br>Note: This is only used if FIXED_MODE = 1.                                                                                                                                                                   |

| FIXED_TVC          | 0 or 1                                      | Set this to 1 if the TVC[7:0] pins of the AB macro are a fixed constant, or to 0 to allow register-controlled TVC[7:0] setting (saves some logic tiles for a fixed system). The default value of 0 does not have a fixed TVC[7:0] setting.                                                                                                                                         |

| FIXED_TVC_VAL      | 0 to 255                                    | Fixed TVC Value: Set this to the integer value of the 8-bit fixed constant connected to the TVC[7:0] inputs of the AB macro.                                                                                                                                                                                                                                                       |

|                    |                                             | <b>Note:</b> This is only used if FIXED_TVC = 1.                                                                                                                                                                                                                                                                                                                                   |

| FIXED_STC          | 0 or 1                                      | Set this to 1 if the STC[7:0] pins of the AB macro are a fixed constant, or to 0 to allow register-controlled STC[7:0] setting (saves some logic tiles for a fixed system). The default value of 0 does not have a fixed STC[7:0] setting.                                                                                                                                         |

**Note:** \*Invalid values are 3, 7, 11, and 15 (refer to the *Fusion datasheet*).

| Table 4 | • | CoreAl | Parameters/ | <b>Generics</b> | Descriptions | (Continued) |

|---------|---|--------|-------------|-----------------|--------------|-------------|

|---------|---|--------|-------------|-----------------|--------------|-------------|

| Name                                                                                              | Valid Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|---------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FIXED_STC_VAL                                                                                     | 0 to 255    | Fixed STC Value: Set this to the integer value of the 8-bit fixed constant connected to the STC[7:0] inputs of the AB macro.<br><b>Note:</b> This is only used if FIXED_STC = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DISABLE_TMSTBINT                                                                                  | 0 or 1      | Disable Internal Temperature Monitor Strobe: Set this 1-bit integer to disable<br>the internal temperature monitor strobes. If this bit is set to 1, the TMSTBINT<br>input is disabled; if it is set to 0, the TMSTBINT input is register-controlled. The<br>default value of 0 allows the internal temperature monitor strobe to be<br>controlled via register settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CFG_AV9, CFG_AV8, CFG_AV7,<br>CFG_AV6, CFG_AV5, CFG_AV4,<br>CFG_AV3, CFG_AV2, CFG_AV1,<br>CFG_AV0 | 0 to 1,023  | Configure AVx Inputs: Set each of these 10-bit integers to configure the AV9 through AV0 inputs that are connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each AVx input, shown in Table 5 on page 9. For example, if CFG_AV5 is set to the binary value 0000000000 (decimal 0), the AV5 input will be used as an analog voltage monitor input. If CFG_AV5 is set to the binary value 0100000000 (decimal 256), the AV5 input will be used as a digital input, and the buffered DAVOUT5 output would be connected to the user's own logic. If CFG_AV5 is set to the binary value 1100000000 (decimal 768), the AV5 input will be used and the AV5 input of the AB macro will be hardwired to logic 0 within CoreAI.                                                                                                                                                                                        |  |  |  |  |

| CFG_AC9, CFG_AC8, CFG_AC7,<br>CFG_AC6, CFG_AC5, CFG_AC4,<br>CFG_AC3, CFG_AC2, CFG_AC1,<br>CFG_AC0 | 0 to 1,023  | Configure ACx Inputs: Set each of these 10-bit integers to configure the AC9 through AC0 inputs that are connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each ACx input, shown in Table 6 on page 9. For example, if CFG_AC7 is set to the binary value 0000000000 (decimal 0), the AC7 input will be used as an analog current monitor input. If CFG_AC7 is set to the binary value 0100000000 (decimal 256), the AC7 input will be used as a digital input, and the buffered DACOUT7 output would be connected to the user's own logic. If CFG_AC7 is set to the binary value 100000000 (decimal 512), the AC7 input will be used as an analog voltage monitor input. If CFG_AC7 is set to the binary value 1100000000 (decimal 768), the AC7 input will be disabled; in this case, the CoreAI AC7 input will not be used and the AC7 input of the AB macro will be hardwired to logic 0 within CoreAI. |  |  |  |  |

**Note:** \*Invalid values are 3, 7, 11, and 15 (refer to the *Fusion datasheet*).

#### Table 4 • CoreAl Parameters/Generics Descriptions (Continued)

| Name                                                                                              | Valid Range | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG_AT9, CFG_AT8, CFG_AT7,<br>CFG_AT6, CFG_AT5, CFG_AT4,<br>CFG_AT3, CFG_AT2, CFG_AT1,<br>CFG_AT0 | 0 to 1,023  | Configure ATx Inputs: Set each of these 10-bit integers to configure the AT9 through AT0 inputs that are connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings for each ATx input, shown in Table 7 on page 10. For example, if CFG_AT2 is set to the binary value 0000000000 (decimal 0), the AT2 input will be used as an analog temperature monitor input. If CFG_AT2 is set to the binary value 0100000000 (decimal 256), the AT2 input will be used as a digital input, and the buffered DATOUT2 output would be connected to the user's own logic. If CFG_AT2 is set to the binary value 100000000 (decimal 512), the AT2 input will be used as an analog value 1100000000 (decimal 512), the AT2 input will be used as an analog temperature to the binary value 100000000 (decimal 512), the AT2 input will be used as an analog value 1100000000 (decimal 512), the AT2 input will be used as an analog value 1100000000 (decimal 512), the AT2 input will be used as an analog value 1100000000 (decimal 512), the AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 100000000 (decimal 512). The AT2 input will be used as an analog value 100000000 (decimal 512). The AT2 input will be used as an analog value 1100000000 (decimal 512). The AT2 input will be used as an analog value 100000000 (decimal 512). The AT2 input will be used as an analog value 1000000000 (decimal 512). |

| CFG_GD9, CFG_GD8, CFG_GD7,<br>CFG_GD6, CFG_GD5, CFG_GD4,<br>CFG_GD3, CFG_GD2, CFG_GD1,<br>CFG_GD0 | 0 to 1,023  | Configure Gate Drivers: Set each of these 10-bit integers to configure the GDON9 through GDON0 inputs and the AG9 through AG0 outputs that are connected to the AB macro. The lower 8 bits of each of these 10-bit integers are reserved for generating firmware settings for the target processor used with CoreAI and are ignored by the CoreAI hardware. The upper 2 bits are used to create the settings shown in Table 8 on page 10. For example, if CFG_GD1 is set to the binary value 0000000000 (decimal 0), the AG1 gate-driver output will be controlled by a software-controlled register within CoreAI (ADC Control Register 5). If CFG_GD1 is set to the binary value 0100000000 (decimal 256), the DDGDON1 input (connected to the user's own logic) will be used to directly control the AG1 gate-driver output. If CFG_GD1 is set to the binary value 1100000000 (decimal 768), the AG1 output will be disabled; in this case, the CoreAI AG1 output will not be used and the GDON1 input of the AB macro will be hardwired to logic 0 within CoreAI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**Note:** \*Invalid values are 3, 7, 11, and 15 (refer to the *Fusion datasheet*).

#### Table 5• Settings for AVx Inputs

| CFG_A\ | /x Bit-Po | sition V | AVx Input Usage |   |   |   |   |   |   |                           |

|--------|-----------|----------|-----------------|---|---|---|---|---|---|---------------------------|

| 9      | 8         | 7        | 6               | 5 | 4 | 3 | 2 | 1 | 0 | Avx input usage           |

| 0      | 0         | Х        | Х               | Х | Х | Х | Х | Х | Х | Voltage Monitor (default) |

| 0      | 1         | Х        | Х               | Х | Х | Х | Х | Х | Х | Digital Input             |

| 1      | 0         | Х        | Х               | Х | Х | Х | Х | Х | Х | Reserved (unused)         |

| 1      | 1         | Х        | Х               | Х | Х | Х | Х | Х | Х | Disabled                  |

#### Table 6• Settings for ACx Inputs

| CFG_AC | Cx Bit-Po | sition V | ACx Input Usage |   |   |   |   |   |   |                           |

|--------|-----------|----------|-----------------|---|---|---|---|---|---|---------------------------|

| 9      | 8         | 7        | 6               | 5 | 4 | 3 | 2 | 1 | 0 | ACX input usage           |

| 0      | 0         | Х        | Х               | Х | Х | Х | Х | Х | Х | Current Monitor (default) |

| 0      | 1         | Х        | Х               | Х | Х | Х | Х | Х | Х | Digital Input             |

| 1      | 0         | Х        | Х               | Х | Х | Х | Х | Х | Х | Voltage Monitor           |

| 1      | 1         | Х        | Х               | Х | Х | Х | Х | Х | Х | Disabled                  |

#### Table 7• Settings for ATx Inputs

| CFG_AT | x Bit-Po | sition Va |   |   |   |   |   |   |   |                               |

|--------|----------|-----------|---|---|---|---|---|---|---|-------------------------------|

| 9      | 8        | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ATx Input Usage               |

| 0      | 0        | Х         | Х | Х | Х | Х | Х | Х | Х | Temperature Monitor (default) |

| 0      | 1        | Х         | Х | Х | Х | Х | Х | Х | Х | Digital Input                 |

| 1      | 0        | Х         | Х | Х | Х | Х | Х | Х | Х | Voltage Monitor               |

| 1      | 1        | Х         | Х | Х | Х | Х | Х | Х | Х | Disabled                      |

Table 8 • Settings for Gate Driver Usage

| CFG_GI | Ox Bit-Po | osition V | Gate Driver Usage |   |   |   |   |   |   |                                               |

|--------|-----------|-----------|-------------------|---|---|---|---|---|---|-----------------------------------------------|

| 9      | 8         | 7         | 6                 | 5 | 4 | 3 | 2 | 1 | 0 | Gate Driver Osage                             |

| 0      | 0         | Х         | Х                 | Х | Х | Х | Х | Х | Х | Register controlled (default)                 |

| 1      | 0         | Х         | Х                 | Х | Х | Х | Х | Х | Х | Gate Driver (AGx) controlled by DDGDONx input |

| 1      | 0         | Х         | Х                 | Х | Х | Х | Х | Х | Х | Reserved (unused)                             |

| 1      | 1         | Х         | Х                 | Х | Х | Х | Х | Х | Х | Disabled (GDONx and AGx)                      |

### **Internal CoreAl Registers**

The internal register address map and reset values of each APB-accessible register for CoreAI are shown in Table 9 on page 11. In the case of 8-bit APB reads and writes (APB\_16BIT\_DATA = 0), each PADDR[4:0] address is significant and contains the byte listed in the far right column; however, when 16-bit APB reads and writes are used (APB\_16BIT\_DATA = 1), PADDR[4:1] addresses contain one 16-bit word, where each two adjacent rows in Table 9 on page 11 contain the low-order and highorder bytes, consecutively (PADDR[0] is unused in this case).

Table 10 on page 12 through Table 31 on page 17 describe the various APB-accessible registers within CoreAI. Unless otherwise stated, each register can be read from or written to by an internal or external microprocessor/microcontroller. All registers are listed assuming 8-bit APB reads and writes; if 16-bit APB reads and writes are used, add 8 to each item in the "Bits" column for high-order bytes (Table 11 on page 12, Table 15 on page 13, Table 17 on page 13, Table 19 on page 14, Table 21 on page 14, Table 23 on page 14, Table 25 on page 15, Table 29 on page 16, and Table 31 on page 17).

When reading from register bits that are write-only or unused (reserved), a logic 0 will be returned. When writing to register bits that are read-only or unused (reserved), no action takes place.

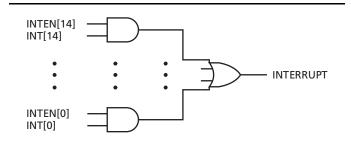

The INTERRUPT output is generated as the logical OR of the interrupt enable bits (INTEN[14:0]) ANDed with the interrupt status bits (INT[14:0]), as shown in Figure 4.

Note that after an APB read of the interrupt status registers has been performed, each INT[14:0] bit will be cleared if its condition is no longer valid. If an APB read of the interrupt status registers has just occurred coincident with a pending interrupt condition, the interrupt condition will have priority in order to prevent a missed interrupt.

| PADDR[4:0] | Туре | <b>Reset Value</b> | Brief Description                        |  |  |  |

|------------|------|--------------------|------------------------------------------|--|--|--|

| 0x00       | R/W  | 0x04               | ACM Control/Status Register (low-order)  |  |  |  |

| 0x01       | R/W  | 0x00               | ACM Control/Status Register (high-order) |  |  |  |

| 0x02       | R/W  | 0x00               | ACM Address Register                     |  |  |  |

| 0x03       | -    | 0x00               | Reserved                                 |  |  |  |

| 0x04       | R/W  | 0x00               | ACM Data Register                        |  |  |  |

| 0x05       | -    | 0x00               | Reserved                                 |  |  |  |

| 0x06       | R/W  | 0x00               | ADC Control Register 1 (low-order)       |  |  |  |

| 0x07       | R/W  | 0x00               | ADC Control Register 1 (high-order)      |  |  |  |

| 0x08       | R/W  | 0x00               | ADC Control Register 2 (low-order)       |  |  |  |

| 0x09       | R/W  | 0x00               | ADC Control Register 2 (high-order)      |  |  |  |

| 0x0a       | R/W  | 0x00               | ADC Control Register 3 (low-order)       |  |  |  |

| 0x0b       | R/W  | 0x00               | ADC Control Register 3 (high-order)      |  |  |  |

| 0x0c       | R/W  | 0x00               | ADC Control Register 4 (low-order)       |  |  |  |

| 0x0d       | R/W  | 0x00               | ADC Control Register 4 (high-order)      |  |  |  |

| 0x0e       | R/W  | 0x00               | ADC Control Register 5 (low-order)       |  |  |  |

| 0x0f       | R/W  | 0x00               | ADC Control Register 5 (high-order)      |  |  |  |

| 0x10       | R    | 0x00               | ADC Status Register (low-order)          |  |  |  |

| 0x11       | R    | 0x00               | ADC Status Register (high-order)         |  |  |  |

| 0x12       | R    | 0x00               | Read FIFO Data Output                    |  |  |  |

| 0x13       | -    | 0x00               | Reserved                                 |  |  |  |

| 0x14       | R    | 0x0c               | Read FIFO Status                         |  |  |  |

| 0x15       | -    | 0x00               | Reserved                                 |  |  |  |

| 0x16       | R/W  | 0x00               | Interrupt Enable Register (low-order)    |  |  |  |

| 0x17       | R/W  | 0x00               | Interrupt Enable Register (high-order)   |  |  |  |

| 0x18       | R    | 0x00               | Interrupt Status Register (low-order)    |  |  |  |

| 0x19       | R    | 0x00               | Interrupt Status Register (high-order)   |  |  |  |

#### Table 9 • CoreAl Internal Register Address Map\*

Note: \*Values shown in hexadecimal format. Type designations: "R" – read-only, "R/W" – read/write, "–" – Not used (to accommodate 16-bit APB access)

| Table 10 • | ACM Control/Status Register (low-order) |  |

|------------|-----------------------------------------|--|

|------------|-----------------------------------------|--|

| Bits | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | Reserved     | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4    | ACMWRBUSY    | ACM Write Cycle Busy (read-only) – If 1, the ACM is busy writing data into the AB block.                                                                                                                                                                                                                                                                                                                                                                   |

| 3    | ACMRDBUSY    | ACM Read Cycle Busy (read-only) – If 1, the ACM is busy reading data from the AB block.                                                                                                                                                                                                                                                                                                                                                                    |

| 2    | ACMRESETBUSY | ACM Reset Cycle Busy (read-only) – If 1, the ACM is busy being reset.                                                                                                                                                                                                                                                                                                                                                                                      |

| 1    | ACMRDSTART   | <ul> <li>ACM Read Start (write-only)</li> <li>1 – The ACM starts a read cycle from the ACM address in the ACMADDR[7:0] bits of the ACM Address/Data register. Note that this write-only bit is active for one ACM clock cycle (self-clearing), and that the resulting busy signal from the ACM read taking place will be reflected in the ACMRDBUSY bit of this register.</li> <li>0 – Normal (no operation or current ACM operation continues)</li> </ul> |

| 0    | ACMRESET     | ACM Reset (write-only)<br>1 – The ACM is put into a reset condition. Note that this write-only bit is active for only one ACM<br>clock cycle (self-clearing), and that the resulting busy signal from the ACM reset taking place will<br>be reflected in the ACMRESETBUSY bit of this register.<br>0 – Normal (no operation or current ACM operation continues)                                                                                            |

#### Table 11 • ACM Control/Status Register (high-order)

| Bits | Name     | Function |

|------|----------|----------|

| 7:0  | Reserved | Not used |

#### Table 12 ACM Address Register

| Bits | Name         | Function                                                           |

|------|--------------|--------------------------------------------------------------------|

| 7:0  | ACMADDR[7:0] | ACM Address                                                        |

|      |              | These bits are connected to the ACMADDR[7:0] port of the AB macro. |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)    |

#### Table 13 • ACM Data Register

| Bits | Name         | Function                                                                                    |

|------|--------------|---------------------------------------------------------------------------------------------|

| 7:0  | ACMDATA[7:0] | ACM Data                                                                                    |

|      |              | If this register is read from, the ACMRDATA[7:0] output port from the AB block is returned. |

|      |              | If this register is written to, it will drive the ACMWDATA[7:0] input port of the AB block. |

#### Table 14 • ADC Control Register 1 (low-order)

| Bits | Name      | Function                                                                                                                                                                                                                                                                                                 |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Reserved  | Not used                                                                                                                                                                                                                                                                                                 |

| 6    | ADCRESET  | <ul> <li>ADC Reset (write-only)</li> <li>1 – The ADC is given an active high pulse (connected to the ADCRESET pin of the AB macro). Note that this write-only bit is active for only one PCLK clock cycle (self-clearing).</li> <li>0 – Normal (no operation or current conversion continues)</li> </ul> |

| 5    | PWRDN     | ADC Power Down<br>1 – The ADC is powered down.<br>0 – The ADC is powered up (normal operation).                                                                                                                                                                                                          |

| 4    | VAREFSEL  | ADC Voltage Reference Select<br>1 – Select external voltage reference (3.3 V max.) to be used (input on VAREF and GNDREF ports)<br>0 – Select internal voltage reference (2.56 V) to be used (output on VAREF port)                                                                                      |

| 3:0  | MODE[3:0] | ADC Mode Selection<br>The mode selection bits are used to select between 8-, 10-, and 12-bit ADC resolution.<br>(Refer to the <i>Fusion datasheet</i> for further information.)                                                                                                                          |

#### Table 15 • ADC Control Register 1 (high-order)

| Bits | Name     | Function                                                        |

|------|----------|-----------------------------------------------------------------|

| 7:0  | TVC[7:0] | ADC Clock Divider                                               |

|      |          | (Refer to the <i>Fusion datasheet</i> for further information.) |

#### Table 16 • ADC Control Register 2 (low-order)

| Bits | Name     | Function                                                        |

|------|----------|-----------------------------------------------------------------|

| 7:0  | STC[7:0] | ADC Sample Time Control                                         |

|      |          | (Refer to the <i>Fusion datasheet</i> for further information.) |

#### Table 17 • ADC Control Register 2 (high-order)

| Bits | Name          | Function                                                                                                                                                                                                                                                               |

|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6  | Reserved      | Not used                                                                                                                                                                                                                                                               |

| 5    | ADCSTART      | ADC Start Conversion (write-only)<br>1 – The ADC starts an analog-to-digital conversion on the selected channel. Note that this write-<br>only bit is high for only one PCLK clock cycle (self-clearing).<br>0 – Normal (no operation or current conversion continues) |

| 4:0  | CHNUMBER[4:0] | ADC Channel Number<br>This 5-bit value selects one of 32 analog channels that are fed to the analog MUX within the AB<br>macro.<br>(Refer to the <i>Fusion datasheet</i> for further information.)                                                                     |

#### Table 18 • ADC Control Register 3 (low-order)

| Bits | Name       | Function                                                                                                                                                       |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | CMSTB[7:0] | Current Monitor Strobes<br>These bits are connected to the CMSTB[7:0] pins of the AB macro.<br>(Refer to the <i>Fusion datasheet</i> for further information.) |

| Table 19 • | ADC Control | <b>Register 3</b> | (high-order) |

|------------|-------------|-------------------|--------------|

|------------|-------------|-------------------|--------------|

| Bits | Name       | Function                                                                |

|------|------------|-------------------------------------------------------------------------|

| 7:2  | Reserved   | Not used                                                                |

| 1:0  | CMSTB[9:8] | Current Monitor Strobes                                                 |

|      |            | These bits are connected to the CMSTB9 and CMSTB8 pins of the AB macro. |

|      |            | (Refer to the <i>Fusion datasheet</i> for further information.)         |

#### Table 20 • ADC Control Register 4 (low-order)

| Bits | Name       | Function                                                         |

|------|------------|------------------------------------------------------------------|

| 7:0  | TMSTB[7:0] | Temperature Monitor Strobes                                      |

|      |            | These bits are connected to the TMSTB[7:0] pins of the AB macro. |

|      |            | (Refer to the <i>Fusion datasheet</i> for further information.)  |

#### Table 21 • ADC Control Register 4 (high-order)

| Bits | Name       | Function                                                                                                                                                                  |  |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:2  | Reserved   | Not used                                                                                                                                                                  |  |

| 2    | TMSTBINT   | Internal Temperature Monitor Strobe<br>This bit is connected to the TMSTBINT pin of the AB macro.<br>(Refer to the <i>Fusion datasheet</i> for further information.)      |  |

| 1:0  | TMSTB[9:8] | Temperature Monitor Strobes<br>These bits are connected to the TMSTB9 and TMSTB8 pins of the AB macro.<br>(Refer to the <i>Fusion datasheet</i> for further information.) |  |

#### Table 22 • ADC Control Register 5 (low-order)

| Bits | Name      | Function                                                                                                                                                                                                                                       |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | GDON[7:0] | Gate Driver Enables                                                                                                                                                                                                                            |

|      |           | These bits are connected to the GDON[7:0] pins of the AB macro. Note that the CFG_GDx parameters/generics settings affect whether or not the GDON[7:0] register bits are used. (Refer to the <i>Fusion datasheet</i> for further information.) |

#### Table 23 ADC Control Register 5 (high-order)

| Bits | Name      | Function                                                                                                                                                                                                                                                                          |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | Reserved  | Not used                                                                                                                                                                                                                                                                          |

| 1:0  | GDON[9:8] | Gate Driver Enables<br>These bits are connected to the GDON9 and GDON8 pins of the AB macro. Note that the CFG_GDx<br>parameters/generics settings affect whether or not the GDON[9:8] register bits are used.<br>(Refer to the <i>Fusion datasheet</i> for further information.) |

#### Table 24 • ADC Status Register (low-order)

| Bits | Name        | Function                                                        |

|------|-------------|-----------------------------------------------------------------|

| 7:0  | RESULT[7:0] | ADC Result (low-order)                                          |

|      |             | These bits come from the RESULT[7:0] bits of the AB macro.      |

|      |             | (Refer to the <i>Fusion datasheet</i> for further information.) |

#### Table 25 • ADC Status Register (high-order)

| Bits | Name         | Function                                                                                          |

|------|--------------|---------------------------------------------------------------------------------------------------|

| 7    | CALIBRATE    | ADC Calibrate                                                                                     |

|      |              | 1 – The ADC is busy performing its calibration.                                                   |

|      |              | 0 – The ADC is calibrated.                                                                        |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)                                   |

| 6    | SAMPLE       | ADC Sample                                                                                        |

|      |              | 1 – The ADC is sampling the selected analog input.                                                |

|      |              | 0 – Normal (no operation or the ADC has finished the sampling phase)                              |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)                                   |

| 5    | BUSY         | ADC Busy                                                                                          |

|      |              | 1 – The ADC is busy performing an analog-to-digital conversion.                                   |

|      |              | 0 – The ADC is not busy.                                                                          |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)                                   |

| 4    | DATAVALID    | ADC Data Valid                                                                                    |

|      |              | 1 – The ADC contains valid data from an analog-to-digital conversion on the RESULT[11:0] outputs. |

|      |              | 0 – Normal (no operation or current conversion continues)                                         |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)                                   |

| 3:0  | RESULT[11:8] | ADC Result (high-order)                                                                           |

|      |              | These bits come from the RESULT[11:8] bits of the AB macro.                                       |

|      |              | (Refer to the <i>Fusion datasheet</i> for further information.)                                   |

#### Table 26 Read FIFO Data Output Register

| Bits | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0  | DOUT[7:0] | Read FIFO Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|      |           | If CoreAl is used in 8-bit APB read/write mode, the read FIFO must be read twice to retrieve one ADC sample of result data (two bytes); in this case, the low-order byte would be read first and the high-order byte second. Note also that in 8-bit APB read/write mode, the read FIFO will not become empty until the last high-order byte has been read from the FIFO, i.e., an even number of reads must occur. If CoreAl is used in 16-bit APB read/write mode, the read FIFO will be read as one 16-bit word at once (with only the lower 12 bits being significant, since the ADC result has 12 bits of resolution); in this case, DOUT[15:0] will appear on the PRDATA[15:0] output port, rather than DOUT[7:0] appearing on PRDATA[7:0] as in 8-bit mode. |  |  |  |

#### Table 27 Read FIFO Status Register

| Bits | Name     | Function                                                                                          |

|------|----------|---------------------------------------------------------------------------------------------------|

| 7:4  | Reserved | Not used                                                                                          |

| 3    | AEMPTY   | Read FIFO Almost Empty                                                                            |

|      |          | 1 – The read FIFO is almost empty (based on the value of the USE_RDFIFO_AEVAL parameter/generic). |

|      |          | 0 – The read FIFO is not almost empty.                                                            |

| 2    | EMPTY    | Read FIFO Empty                                                                                   |

|      |          | 1 – The read FIFO is empty.                                                                       |

|      |          | 0 – The read FIFO is not empty.                                                                   |

| 1    | AFULL    | Read FIFO Almost Full                                                                             |

|      |          | 1 – The read FIFO is almost full (based on the value of the USE_RDFIFO_AFVAL parameter/generic).  |

|      |          | 0 – The read FIFO is not almost full.                                                             |

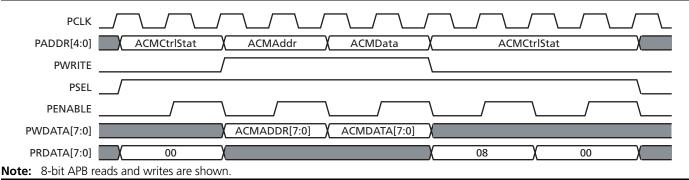

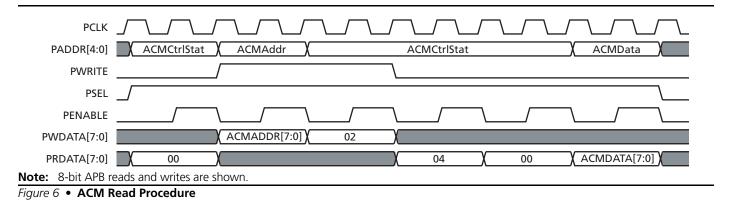

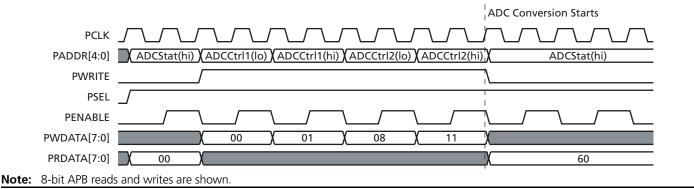

| 0    | FULL     | Read FIFO Full                                                                                    |