# I/O Structures in IGLOOe and ProASIC3E Devices

## Introduction

Low-power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO<sup>®</sup>e, ProASIC<sup>®</sup>3EL, and ProASIC3E families support Pro I/Os.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. The Actel Libero<sup>®</sup> Integrated Design Environment (IDE) provides an easy way to implement I/O that will result in robust I/O design.

This document first describes the two different I/O types in terms of the standards and features they support. It then explains the individual features and how to implement them in Actel's Libero IDE.

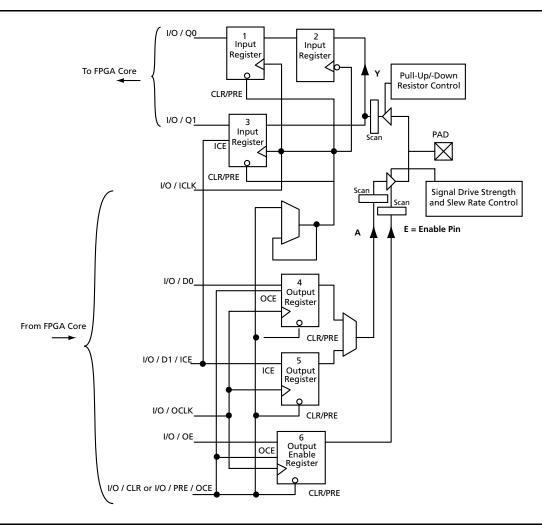

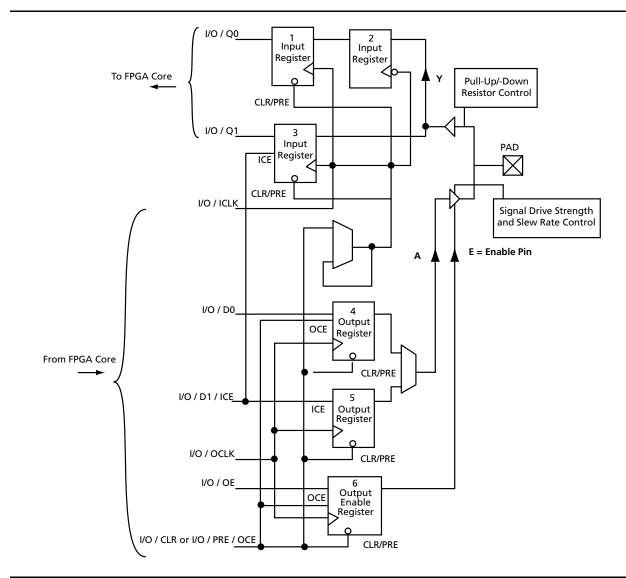

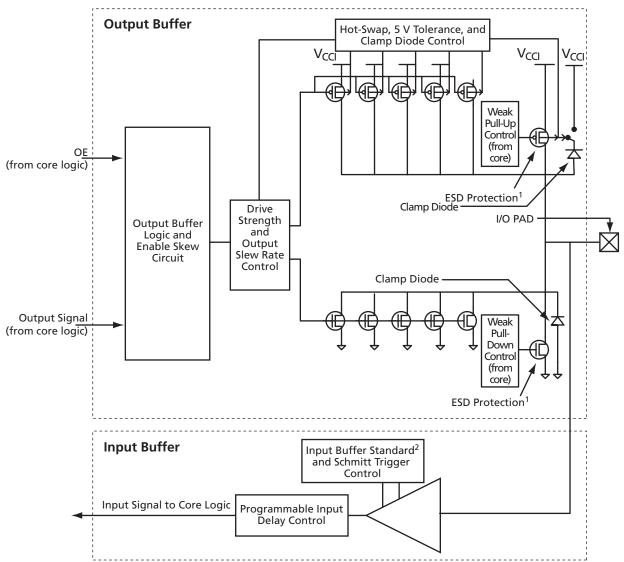

Figure 1 • I/O Block Logical Representation

## Low-Power Flash Device I/O Support

The low-power flash FPGAs listed in Table 1 support I/Os and the functions described in this document.

| Table | 1 | • | Flash-Based FPGAs |  |

|-------|---|---|-------------------|--|

|-------|---|---|-------------------|--|

| Series   | Family*              | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

| ProASIC3 | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

2

## Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E

Table 2 shows the voltages and compatible I/O standards for Pro I/Os. I/Os provide programmable slew rates, drive strengths, and weak pull-up and pull-down circuits. All I/O standards, except 3.3 V PCI and 3.3 V PCI-X, are capable of hot-insertion. 3.3 V PCI and 3.3 V PCI-X are 5 V-tolerant. See the "5 V Input Tolerance" section on page 20 for possible implementations of 5 V tolerance. Single-ended input buffers support both the Schmitt trigger and programmable delay options on a per-I/O basis.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section in the datasheet for more information. During power-up, before reaching activation levels, the I/O input and output buffers are disabled while the weak pull-up is enabled. Activation levels are described in the datasheet.

| Table 2 • | Supported I/O Standards |

|-----------|-------------------------|

|-----------|-------------------------|

|                                                                                                           | A3PE600 | A3PE1500     | A3PE3000/<br>A3PE3000L |

|-----------------------------------------------------------------------------------------------------------|---------|--------------|------------------------|

|                                                                                                           | AGLE600 | AGLE1500     | AGLE3000               |

| Single-Ended                                                                                              |         |              |                        |

| LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V / 1.8 V / 1.5 V,<br>LVCMOS 2.5/5.0 V, 3.3 V PCI/PCI-X                    | 1       | $\checkmark$ | 1                      |

| Differential                                                                                              |         |              |                        |

| LVPECL, LVDS, B-LVDS, M-LVDS                                                                              | 1       | ✓            | 1                      |

| Voltage-Referenced                                                                                        |         |              |                        |

| GTL+ 2.5 V / 3.3 V, GTL 2.5 V / 3.3 V, HSTL Class I<br>and II, SSTL2 Class I and II, SSTL3 Class I and II | 1       | ~            | ~                      |

## I/O Banks and I/O Standards Compatibility

I/Os are grouped into I/O voltage banks.

Each I/O voltage bank has dedicated I/O supply and ground voltages (VMV/GNDQ for input buffers and  $V_{CCI}$ /GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 3 on page 5 shows the required voltage compatibility values for each of these voltages.

There are eight I/O banks (two per side).

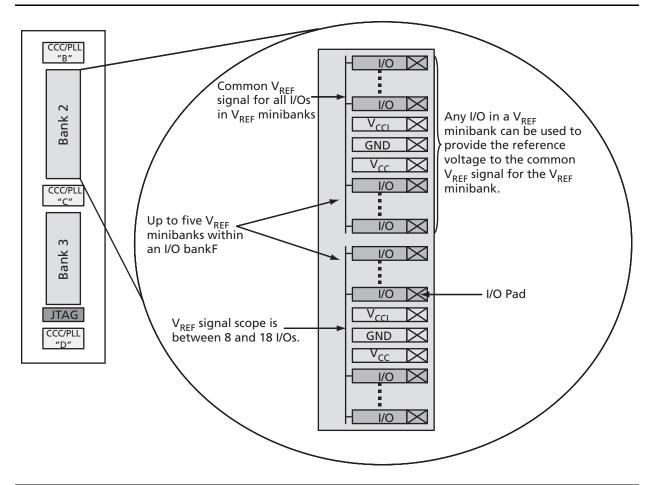

Every I/O bank is divided into minibanks. Any user I/O in a  $V_{REF}$  minibank (a minibank is the region of scope of a  $V_{REF}$  pin) can be configured as a  $V_{REF}$  pin (Figure 2). Only one  $V_{REF}$  pin is needed to control the entire  $V_{REF}$  minibank. The location and scope of the  $V_{REF}$  minibanks can be determined by the I/O name. For details, see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 33. Table 5 on page 5 shows the I/O standards supported by IGLOOe and ProASIC3E devices, and the corresponding voltage levels.

I/O standards are compatible if they comply with the following:

- Their V<sub>CCI</sub> and VMV values are identical.

- Both of the standards need a V<sub>REF</sub>, and their V<sub>REF</sub> values are identical.

- All inputs and disabled outputs are voltage tolerant up to 3.3 V.

For more information about I/O and global assignments to I/O banks in a device, refer to the specific pin table for the device in the packaging section of the datasheet, and see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 33.

Figure 2 • Typical IGLOOe and ProASIC3E I/O Bank Detail Showing V<sub>REF</sub> Minibanks

| V <sub>CCI</sub> and VMV (typical) | Compatible Standards                                                                                         |  |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3.3 V                              | LVTTL/LVCMOS 3.3, PCI 3.3, SSTL3 (Class I and II), GTL+ 3.3, GTL 3.3, LVPECL                                 |  |  |  |  |  |

| 2.5 V                              | LVCMOS 2.5, LVCMOS 2.5/5.0, SSTL2 (Class I and II), GTL+ 2.5, GTL 2.5, LVDS, DDR<br>LVDS, B-LVDS, and M-LVDS |  |  |  |  |  |

| 1.8 V                              | LVCMOS 1.8                                                                                                   |  |  |  |  |  |

| 1.5 V                              | LVCMOS 1.5, HSTL (Class I and II)                                                                            |  |  |  |  |  |

#### Table 3 • V<sub>CCI</sub> Voltages and Compatible IGLOOe and ProASIC3E Standards

#### Table 4 • V<sub>REF</sub> Voltages and Compatible IGLOOe and ProASIC3E Standards

| V <sub>REF</sub> (typical) | Compatible Standards   |  |  |  |

|----------------------------|------------------------|--|--|--|

| 1.5 V                      | SSTL3 (Class I and II) |  |  |  |

| 1.25 V                     | SSTL2 (Class I and II) |  |  |  |

| 1.0 V                      | GTL+ 2.5, GTL+ 3.3     |  |  |  |

| 0.8 V                      | GTL 2.5, GTL 3.3       |  |  |  |

| 0.75 V                     | HSTL (Class I and II)  |  |  |  |

| I/O Bank Voltage (typical) | Minibank Voltage (typical) | LVTTL/LVCMOS 3.3 V | LVCMOS 2.5 V | LVCMOS 1.8 V | LVCMOS 1.5 V | 3.3 V PCI/PCI-X | GTL+ (3.3 V) | GTL+ (2.5 V) | GTL (3.3 V) | GTL (2.5 V) | HSTL Class I and II (1.5 V) | SSTL2 Class I and II (2.5 V) | SSTL3 Class I and II (3.3 V) | LVDS, B-LVDS, and M-LVDS, DDR (2.5 V $\pm$ 5%) | LVPECL (3.3 V) |

|----------------------------|----------------------------|--------------------|--------------|--------------|--------------|-----------------|--------------|--------------|-------------|-------------|-----------------------------|------------------------------|------------------------------|------------------------------------------------|----------------|

| 3.3 V                      | Ι                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 0.80 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 1.00 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 1.50 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

| 2.5 V                      | -                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 0.80 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 1.00 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 1.25 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

| 1.8 V                      | _                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

| 1.5 V                      | _                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

|                            | 0.75 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                                |                |

*Note:* White box: Allowable I/O standard combination Gray box: Illegal I/O standard combination

## Features Supported on Every I/O

Table 6 lists all features supported by transmitter/receiver for single-ended and differential I/Os. Table 7 on page 7 lists the performance of each I/O technology.

Table 6 • IGLOOe and ProASIC3E I/O Features

| Feature                                                                        |   | Description                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All I/O                                                                        | ٠ | High performance (Table 7 on page 7)                                                                                                                                                                                    |

|                                                                                | • | Electrostatic discharge protection                                                                                                                                                                                      |

|                                                                                | • | I/O register combining option                                                                                                                                                                                           |

| Single-Ended and Voltage-Referenced<br>Transmitter Features                    | • | Hot-swap in every mode except PCI or 5 V–input–tolerant (these modes use clamp diodes and do not allow hot-swap)                                                                                                        |

|                                                                                | • | Activation of hot-insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                          |

|                                                                                | • | Output slew rate: 2 slew rates                                                                                                                                                                                          |

|                                                                                | • | Weak pull-up and pull-down resistors                                                                                                                                                                                    |

|                                                                                | • | Output drive: 5 drive strengths                                                                                                                                                                                         |

|                                                                                | • | Programmable output loading                                                                                                                                                                                             |

|                                                                                | • | Skew between output buffer enable/disable time: 2 ns delay on rising edge and 0 ns delay on falling edge (see "Selectable Skew between Output Buffer Enable and Disable Times" section on page 24 for more information) |

|                                                                                | • | LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs                                                                                                                                                               |

| Single-Ended Receiver Features                                                 | ٠ | 5 V-input-tolerant receiver (Table 13 on page 19)                                                                                                                                                                       |

|                                                                                | • | Schmitt trigger option                                                                                                                                                                                                  |

|                                                                                | • | Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at $25^{\circ}$ C, 1.5 V)                                                        |

|                                                                                | • | Separate ground plane for GNDQ pin and power plane for VMV pin are used for input buffer to reduce output-induced noise.                                                                                                |

| Voltage-Referenced Differential Receiver<br>Features                           | • | Programmable delay: 0 ns if bypassed, 0.46 ns with '000' setting, 4.66 ns with '111' setting, 0.6-ns intermediate delay increments (at 25°C, 1.5 V)                                                                     |

|                                                                                | • | Separate ground plane for GNDQ pin and power plane for VMV pin are used for input buffer to reduce output-induced noise.                                                                                                |

| CMOS-Style LVDS, B-LVDS, M-LVDS, or<br>LVPECL Transmitter                      | • | Two I/Os and external resistors are used to provide a CMOS-style LVDS, DDR LVDS, B-LVDS, and M-LVDS/LVPECL transmitter solution.                                                                                        |

|                                                                                | • | Activation of hot-insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                          |

|                                                                                | • | High slew rate                                                                                                                                                                                                          |

|                                                                                | • | Weak pull-up and pull-down resistors                                                                                                                                                                                    |

|                                                                                | • | Programmable output loading                                                                                                                                                                                             |

| LVDS, DDR LVDS, B-LVDS, and<br>M-LVDS/LVPECL Differential Receiver<br>Features | • | Programmable delay: 0 ns if bypassed, 0.46 ns with '000' setting, 4.66 ns with '111' setting, 0.6-ns intermediate delay increments (at 25°C, 1.5 V)                                                                     |

|                    |           | Maximum Performance                                         |                                            |

|--------------------|-----------|-------------------------------------------------------------|--------------------------------------------|

| Specification      | ProASIC3E | IGLOOe V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOOe V2, 1.2 V DC<br>Core Supply Voltage |

| LVTTL/LVCMOS 3.3 V | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVCMOS 2.5 V       | 250 MHz   | 230 MHz                                                     | TBD                                        |

| LVCMOS 1.8 V       | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVCMOS 1.5 V       | 130 MHz   | 120 MHz                                                     | TBD                                        |

| PCI                | 200 MHz   | 180 MHz                                                     | TBD                                        |

| PCI-X              | 200 MHz   | 180 MHz                                                     | TBD                                        |

| HSTL-I             | 300 MHz   | 275 MHz                                                     | TBD                                        |

| HSTL-II            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL2-I            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL2-II           | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL3-I            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL3-II           | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL+ 3.3 V         | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL+ 2.5 V         | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL 3.3 V          | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL 2.5 V          | 300 MHz   | 275 MHz                                                     | TBD                                        |

| LVDS               | 350 MHz   | 300 MHz                                                     | TBD                                        |

| M-LVDS             | 200 MHz   | 180 MHz                                                     | TBD                                        |

| B LVDS             | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVPECL             | 350 MHz   | 300 MHz                                                     | TBD                                        |

Table 7 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected)

## I/O Architecture

## I/O Tile

The I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 3). The registers can also be used to support the JESD-79C Double Data Rate (DDR) standard within the I/O structure (see DDR for Actel's Low-Power Flash Devices for more information).

As depicted in Figure 3, all I/O registers share one CLR port. The output register and output enable register share one CLK port.

#### Figure 3 • I/O Block Logical Representation

8

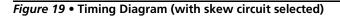

## I/O Bank Structure

Low-power flash device I/Os are divided into multiple technology banks. The number of banks is device-dependent. The IGLOOe, ProASIC3EL, and ProASIC3E devices have eight banks (two per side); and IGLOO, ProASIC3L, and ProASIC3 devices have two to four banks. Each bank has its own V<sub>CCI</sub> power supply pin. Multiple I/O standards can co-exist within a single I/O bank.

In IGLOOe, ProASIC3EL, and ProASIC3E devices, each I/O bank is subdivided into  $V_{REF}$  minibanks. These are used by voltage-referenced I/Os.  $V_{REF}$  minibanks contain 8 to 18 I/Os. All I/Os in a given minibank share a common  $V_{REF}$  line (only one  $V_{REF}$  pin is needed per  $V_{REF}$  minibank). Therefore, if an I/O in a  $V_{REF}$  minibank is configured as a  $V_{REF}$  pin, the remaining I/Os in that minibank will be able to use the voltage assigned to that pin. If the location of the  $V_{REF}$  pin is selected manually in the software, the user must satisfy  $V_{REF}$  rules (refer to I/O Software Control in Low-Power Flash Devices). If the user does not pick the  $V_{REF}$  pin manually, the software automatically assigns it.

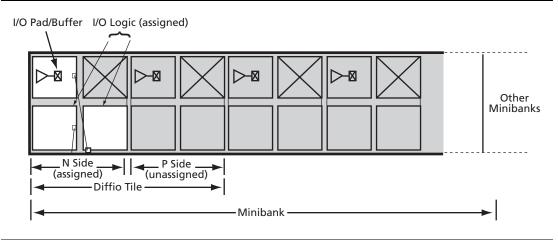

Figure 4 is a snapshot of a section of the I/O ring, showing the basic elements of an I/O tile, as viewed from the Designer place-and-route tool's MultiView Navigator (MVN).

#### Figure 4 • Snapshot of an I/O Tile

Low-power flash device I/Os are implemented using two tile types: I/O and differential I/O (diffio).

The diffio tile is built up using two I/O tiles, which form an I/O pair (P side and N side). These I/O pairs are used according to differential I/O standards. Both the P and N sides of the diffio tile include an I/O buffer and two I/O logic blocks (auxiliary and main logic).

Every minibank (E devices only) is built up from multiple diffio tiles. The number of the minibank depends on the different-size dies. Refer to the "Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E" section on page 3 for an illustration of the minibank structure.

Figure 5 on page 10 shows a simplified diagram of the I/O buffer circuitry. The Output Enable signal (OE) enables the output buffer to pass the signal from the core logic to the pin. The output buffer contains ESD protection circuitry, an n-channel transistor that shunts all ESD surges (up to the limit of the device ESD specification) to GND. This transistor also serves as an output pull-down resistor.

Each output buffer also contains programmable slew rate, drive strength, programmable power-up state (pull-up/-down resistor), hot-swap, 5 V tolerance, and clamp diode control circuitry. Multiple flash switches (not shown in Figure 5 on page 10) are programmed by user selections in the software to activate different I/O features.

#### Notes:

1. All NMOS transistors connected to the I/O pad serve as ESD protection.

2. See Table 2 on page 3 for available I/O standards.

Figure 5 • Simplified I/O Buffer Circuitry

#### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 5 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 3 on page 8) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

## I/O Standards

## Single-Ended Standards

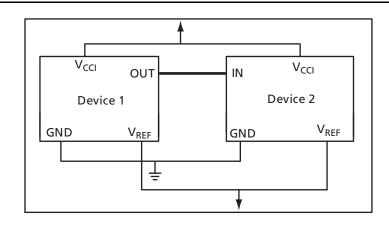

These I/O standards use a push-pull CMOS output stage with a voltage referenced to system ground to designate logical states. The input buffer configuration, output drive, and I/O supply voltage ( $V_{CCI}$ ) vary among the I/O standards (Figure 6).

#### Figure 6 • Single-Ended I/O Standard Topology

The advantage of these standards is that a common ground can be used for multiple I/Os. This simplifies board layout and reduces system cost. Their low-edge-rate (dv/dt) data transmission causes less electromagnetic interference (EMI) on the board. However, they are not suitable for high-frequency (>200 MHz) switching due to noise impact and higher power consumption.

### LVTTL (Low-Voltage TTL)

This is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. The LVTTL output buffer can have up to six different programmable drive strengths. The default drive strength is 12 mA.  $V_{CCI}$  is 3.3 V. Refer to "I/O Programmable Features" on page 15 for details.

### LVCMOS (Low-Voltage CMOS)

The low-power flash devices provide four different kinds of LVCMOS: LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 1.8 V, and LVCMOS 1.5 V. LVCMOS 3.3 V is an extension of the LVCMOS standard (JESD8-B-compliant) used for general-purpose 3.3 V applications. LVCMOS 2.5 V is an extension of the LVCMOS standard (JESD8-5-compliant) used for general-purpose 2.5 V applications. LVCMOS 2.5 V for the 30 k gate devices has a clamp diode to  $V_{CCI}$ , but for all other devices there is no clamp diode.

There is yet another standard supported by IGLOO and ProASIC3 devices (except A3P030): LVCMOS 2.5/5.0 V. This standard is similar to LVCMOS 2.5 V, with the exception that it can support up to 3.3 V on the input side (2.5 V output drive).

LVCMOS 1.8 V is an extension of the LVCMOS standard (JESD8-7-compliant) used for general-purpose 1.8 V applications. LVCMOS 1.5 V is an extension of the LVCMOS standard (JESD8-11-compliant) used for general-purpose 1.5 V applications.

The V<sub>CCI</sub> values for these standards are 3.3 V, 2.5 V, 1.8 V, and 1.5 V, respectively. All these versions use a 3.3 V–tolerant CMOS input buffer and a push-pull output buffer. Like LVTTL, the output buffer has up to seven different programmable drive strengths (2, 4, 6, 8, 12, 16, and 24 mA). Refer to "I/O Programmable Features" on page 15 for details.

### 3.3 V PCI (Peripheral Component Interface)

This standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses an LVTTL input buffer and a push-pull output buffer. With the aid of an external resistor, this I/O standard can be 5 V-compliant for low-power flash devices. It does not have programmable drive strength.

### 3.3 V PCI-X (Peripheral Component Interface Extended)

An enhanced version of the PCI specification, 3.3 V PCI-X can support higher average bandwidths; it increases the speed that data can move within a computer from 66 MHz to 133 MHz. It is backward-compatible, which means devices can operate at conventional PCI frequencies (33 MHz and 66 MHz). PCI-X is more fault-tolerant than PCI. It also does not have programmable drive strength.

## Voltage-Referenced Standards

I/Os using these standards are referenced to an external reference voltage ( $V_{REF}$ ) and are supported on E devices only.

## HSTL Class I and II (High-Speed Transceiver Logic)

These are general-purpose, high-speed 1.5 V bus standards (EIA/JESD 8-6) for signaling between integrated circuits. The signaling range is 0 V to 1.5 V, and signals can be either single-ended or differential. HSTL requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage ( $V_{REF}$ ) is 0.75 V. These standards are used in the memory bus interface with data switching capability of up to 400 MHz. The other advantages of these standards are low power and fewer EMI concerns.

HSTL has four classes, of which low-power flash devices support Class I and II. These classes are defined by standard EIA/JESD 8-6 from the Electronic Industries Alliance (EIA):

- Class I Unterminated or symmetrically parallel-terminated

- Class II Series-terminated

- Class III Asymmetrically parallel-terminated

- Class IV Asymmetrically double-parallel-terminated

#### SSTL2 Class I and II (Stub Series Terminated Logic 2.5 V)

These are general-purpose 2.5 V memory bus standards (JESD 8-9) for driving transmission lines, designed specifically for driving the DDR SDRAM modules used in computer memory. SSTL2 requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage ( $V_{REF}$ ) is 1.25 V.

#### SSTL3 Class I and II (Stub Series Terminated Logic 3.3 V)

These are general-purpose 3.3 V memory bus standards (JESD 8-8) for driving transmission lines. SSTL3 requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage ( $V_{REF}$ ) is 1.5 V.

Figure 7 • SSTL and HSTL Topology

### GTL 2.5 V (Gunning Transceiver Logic 2.5 V)

This is a low-power standard (JESD 8-3) for electrical signals used in CMOS circuits that allows for low electromagnetic interference at high transfer speeds. It has a voltage swing between 0.4 V and 1.2 V and typically operates at speeds of between 20 and 40 MHz.  $V_{CCI}$  must be connected to 2.5 V. The reference voltage ( $V_{REF}$ ) is 0.8 V.

#### GTL 3.3 V (Gunning Transceiver Logic 3.3 V)

This is the same as GTL 2.5 V above, except  $V_{CCI}$  must be connected to 3.3 V.

### GTL+ (Gunning Transceiver Logic Plus)

This is an enhanced version of GTL that has defined slew rates and higher voltage levels. It requires a differential amplifier input buffer and an open-drain output buffer. Even though the output is open-drain,  $V_{CCI}$  must be connected to either 2.5 V or 3.3 V. The reference voltage ( $V_{REF}$ ) is 1 V.

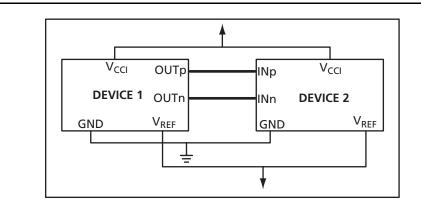

## **Differential Standards**

These standards require two I/Os per signal (called a "signal pair"). Logic values are determined by the potential difference between the lines, not with respect to ground. This is why differential drivers and receivers have much better noise immunity than single-ended standards. The differential interface standards offer higher performance and lower power consumption than their single-ended counterparts. Two I/O pins are used for each data transfer channel. Both differential standards require resistor termination.

#### *Figure 8* • Differential Topology

#### LVPECL (Low-Voltage Positive Emitter Coupled Logic)

LVPECL requires that one data bit be carried through two signal lines; therefore, two pins are needed per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 850 mV. When the power supply is +3.3 V, it is commonly referred to as Low-Voltage PECL (LVPECL). Refer to the device datasheet for the full implementation of the LVPECL transmitter and receiver.

#### LVDS (Low-Voltage Differential Signal)

LVDS is a moderate-speed differential signaling system, in which the transmitter generates two different voltages that are compared at the receiver. LVDS uses a differential driver connected to a terminated receiver through a constant-impedance transmission line. It requires that one data bit be carried through two signal lines; therefore, the user will need two pins per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 350 mV. V<sub>CCI</sub> is 2.5 V. Low-power flash devices contain dedicated circuitry supporting a high-speed LVDS standard that has its own user specification. Refer to the device datasheet for the full implementation of the LVDS transmitter and receiver.

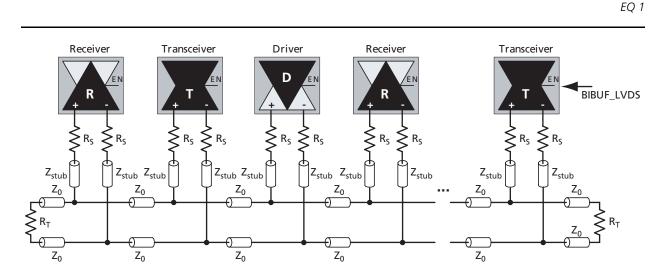

#### **B-LVDS/M-LVDS**

Bus LVDS (B-LVDS) refers to bus interface circuits based on LVDS technology. Multipoint LVDS (M-LVDS) specifications extend the LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Actel LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The driver requires series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus, since the driver can be located anywhere on the bus. These configurations can be implemented using TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Actel LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 9. The input and output buffer delays are available in the LVDS sections in the datasheet.

Example: For a bus consisting of 20 equidistant loads, the terminations given in EQ 1 provide the required differential voltage, in worst case industrial operating conditions, at the farthest receiver:

$R_S = 60 \Omega$ ,  $R_T = 70 \Omega$ , given  $Z_O = 50 \Omega(2")$  and  $Z_{stub} = 50 \Omega(\sim 1.5")$ .

Figure 9 • A B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

## **I/O Features**

Low-power flash devices support multiple I/O features that make board design easier. For example, an I/O feature like Schmitt Trigger in the ProASIC3E input buffer saves the board space that would be used by an external Schmitt trigger for a slow or noisy input signal. These features are also programmable for each I/O, which in turn gives flexibility in interfacing with other components. The following is a detailed description of all available features in low-power flash devices.

## I/O Programmable Features

Low-power flash devices offer many flexible I/O features to support a wide variety of board designs. Some of the features are programmable, with a range for selection. Table 8 lists programmable I/O features and their ranges.

| Feature           | Description                         | Range                  |

|-------------------|-------------------------------------|------------------------|

| Slew Control      | Output slew rate                    | HIGH, LOW              |

| Output Drive (mA) | Output drive strength               | 2, 4, 6, 8, 12, 16, 24 |

| Skew Control      | Output tristate enable delay option | ON, OFF                |

| Resistor Pull     | Resistor pull circuit               | Up, Down, None         |

| Input Delay       | Input delay                         | OFF, 0–7               |

| Schmitt Trigger   | Schmitt trigger for input only      | ON, OFF                |

Table 8 • Programmable I/O Features (user control via I/O Attribute Editor)

Note: Limitations of these features with respect to different devices are discussed in later sections.

## Hot-Swap Support

A pull-up clamp diode must not be present in the I/O circuitry if the hot-swap feature is used. The 3.3 V PCI standard requires a pull-up clamp diode on the I/O, so it cannot be selected if hot-swap capability is required. The A3P030 device does not support 3.3 V PCI, so it is the only device in the ProASIC3 family that supports the hot-swap feature. All devices in the ProASIC3E family are hot-swappable. All standards except LVCMOS 2.5/5.0 V and 3.3 V PCI/PCI-X support the hot-swap feature.

The hot-swap feature appears as a read-only check box in the I/O Attribute Editor that shows whether an I/O is hot-swappable or not. Refer to *Power-Upl-Down Behavior of Low-Power Flash Devices* for details on hot-swapping.

Hot-swapping (also called hot-plugging) is the operation of hot insertion or hot removal of a card in a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 9 on page 16 to Table 12 on page 17. The I/Os also need to be configured in hotinsertion mode if hot-plugging compliance is required. The AGL030 and A3P030 devices have an I/O structure that allows the support of Level 3 and Level 4 hot-swap with only two levels of staging.

#### Table 9 • Hot-Swap Level 1

| Description                              | Cold-swap                                                                                                                                                                                                                                         |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | No                                                                                                                                                                                                                                                |

| Bus State                                | -                                                                                                                                                                                                                                                 |

| Card Ground Connection                   | -                                                                                                                                                                                                                                                 |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                                                                                                 |

| Example Application                      | System and card with Actel FPGA chip are<br>powered down, and the card is plugged into<br>the system. Then the power supplies are turned<br>on for the system but not for the FPGA on the<br>card.                                                |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices: Compliant<br>Other IGLOO/ProASIC3 devices: Compliant if bus<br>switch used to isolate FPGA I/Os from rest of<br>system<br>IGLOOe/ProASIC3E devices: Compliant I/Os can,<br>but do not have to be set to hot-insertion<br>mode. |

#### Table 10 • Hot-Swap Level 2

| Description                              | Hot-swap while reset                                                                                                                                                  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                                   |

| Bus State                                | Held in reset state                                                                                                                                                   |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                        |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                     |

| Example Application                      | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable.         |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E devices:<br>Compliant I/Os can but do not have to be set to<br>hot-insertion mode.<br>Other IGLOO/ProASIC3 devices: Compliant |

#### Table 11 • Hot-Swap Level 3

| Description                              | Hot-swap while bus idle                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                                                                           |

| Bus State                                | Held idle (no ongoing I/O processes during insertion/removal)                                                                                                                                                 |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                                                                |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-down                                                                                                                                                         |

| Example Application                      | Board bus shared with card bus is "frozen," and<br>there is no toggling activity on the bus. It is<br>critical that the logic states set on the bus signal<br>not be disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E devices:<br>Compliant with two levels of staging (first:<br>GND; second: all other pins)<br>Other IGLOO/ProASIC3 devices: Compliant:                                  |

|                                          | Option A – Two levels of staging (first: GND;<br>second: all other pins) together with bus switch<br>on the I/Os                                                                                              |

|                                          | Option B – Three levels of staging (first: GND;<br>second: supplies; third: all other pins)                                                                                                                   |

#### Table 12 • Hot-Swap Level 4

| Description                              | Hot-swap on an active bus                                                                                                                                 |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                       |

| Bus State                                | Bus may have active I/O processes ongoing, but device being inserted or removed must be idle.                                                             |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                            |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-down                                                                                                     |

| Example Application                      | There is activity on the system bus, and it is<br>critical that the logic states set on the bus signal<br>not be disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E devices:<br>Compliant with two levels of staging (first:<br>GND; second: all other pins)                          |

|                                          | Other IGLOO/ProASIC3 devices: Compliant:                                                                                                                  |

|                                          | Option A – Two levels of staging (first: GND;<br>second: all other pins) together with bus switch<br>on the I/Os                                          |

|                                          | Option B – Three levels of staging (first: GND;<br>second: supplies; third: all other pins)                                                               |

#### IGLOOe and ProASIC3E

For devices requiring Level 3 and/or Level 4 compliance, the board drivers connected to the I/Os must have 10 k $\Omega$  (or lower) output drive resistance at hot insertion, and 1 k $\Omega$  (or lower) output drive resistance at hot removal. This resistance is the transmitter resistance sending a signal toward the I/O, and no additional resistance is needed on the board. If that cannot be assured, three levels of staging can be used to achieve Level 3 and/or Level 4 compliance. Cards with two levels of staging should have the following sequence:

- Grounds

- Powers, I/Os, and other pins

## **Cold-Sparing Support**

*Cold-sparing* refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

Cold-sparing is supported on ProASIC3E devices only when the user provides resistors from each power supply to ground. The resistor value is calculated based on the decoupling capacitance on a given power supply. The RC constant should be greater than 3  $\mu$ s.

To remove resistor current during operation, it is suggested that the resistor be disconnected (e.g., with an NMOS switch) from the power supply after the supply has reached its final value. Refer to the *Power-Upl-Down Behavior of Low-Power Flash Devices* chapter of the *ProASIC3* and *ProASIC3E* handbooks for details on cold-sparing.

Cold-sparing means that a subsystem with no power applied (usually a circuit board) is electrically connected to the system that is in operation. This means that all input buffers of the subsystem must present very high input impedance with no power applied so as not to disturb the operating portion of the system.

The 30 k gate devices fully support cold-sparing, since the I/O clamp diode is always off (see Table 13 on page 19). If the 30 k gate device is used in applications requiring cold-sparing, a discharge path from the power supply to ground should be provided. This can be done with a discharge resistor or a switched resistor. This is necessary because the 30 k gate devices do not have built-in I/O clamp diodes.

For other IGLOOe and ProASIC3E devices, since the I/O clamp diode is always active, cold-sparing can be accomplished either by employing a bus switch to isolate the device I/Os from the rest of the system or by driving each I/O pin to 0 V. If the resistor is chosen, the resistor value must be calculated based on decoupling capacitance on a given power supply on the board (this decoupling capacitance is in parallel with the resistor). The RC time constant should ensure full discharge of supplies before cold-sparing functionality is required. The resistor is necessary to ensure that the power pins are discharged to ground every time there is an interruption of power to the device.

IGLOOe and ProASIC3E devices support cold-sparing for all I/O configurations. Standards, such as PCI, that require I/O clamp diodes can also achieve cold-sparing compliance, since clamp diodes get disconnected internally when the supplies are at 0 V.

When targeting low-power applications, I/O cold-sparing may add additional current if a pin is configured with either a pull-up or pull-down resistor and driven in the opposite direction. A small static current is induced on each I/O pin when the pin is driven to a voltage opposite to the weak pull resistor. The current is equal to the voltage drop across the input pin divided by the pull resistor. Refer to the "Detailed I/O DC Characteristics" section of the appropriate family datasheet for the specific pull resistor value for the corresponding I/O standard.

For example, assuming an LVTTL 3.3 V input pin is configured with a weak pull-up resistor, a current will flow through the pull-up resistor if the input pin is driven LOW. For LVTTL 3.3 V, the pull-up resistor is ~45 k $\Omega$  and the resulting current is equal to 3.3 V / 45 k $\Omega$  = 73 µA for the I/O pin. This is true also when a weak pull-down is chosen and the input pin is driven HIGH. This current can be avoided by driving the input LOW when a weak pull-down resistor is used and driving it HIGH when a weak pull-up resistor is used.

I/O Structures in IGLOOe and Pro ASIC3E Devices

This current draw can occur in the following cases:

- In Active and Static modes:

- Input buffers with pull-up, driven LOW

- Input buffers with pull-down, driven HIGH

- Bidirectional buffers with pull-up, driven LOW

- Bidirectional buffers with pull-down, driven HIGH

- Output buffers with pull-up, driven LOW

- Output buffers with pull-down, driven HIGH

- Tristate buffers with pull-up, driven LOW

- Tristate buffers with pull-down, driven HIGH

- In Flash\*Freeze mode:

- Input buffers with pull-up, driven LOW

- Input buffers with pull-down, driven HIGH

- Bidirectional buffers with pull-up, driven LOW

- Bidirectional buffers with pull-down, driven HIGH

#### **Electrostatic Discharge Protection**

Low-power flash devices are tested per JEDEC Standard JESD22-A114-B.

These devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

All IGLOO and ProASIC3 devices are tested to the following models: the Human Body Model (HBM) with a tolerance of 2,000 V, the Machine Model (MM) with a tolerance of 250 V, and the Charged Device Model (CDM) with a tolerance of 200 V.

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to  $V_{CCI}$ . The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the off state, except when transient voltage is significantly above  $V_{CCI}$  or below GND levels.

In 30 k gate devices, the first diode is always off. In other devices, the clamp diode is always on and cannot be switched off.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 13 for more information about the I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

| I/O Assignment                          | Clamp Diode | Hot Insertion | 5 V Input<br>Tolerance | Input<br>Buffer  | Output<br>Buffer |

|-----------------------------------------|-------------|---------------|------------------------|------------------|------------------|

| 3.3 V LVTTL/LVCMOS                      | No          | Yes           | Yes <sup>1</sup>       | Enabled/         | Disabled         |

| 3.3 V PCI, 3.3 V PCI-X                  | Yes         | No            | Yes <sup>1</sup>       | Enabled/         | Disabled         |

| LVCMOS 2.5 V <sup>2</sup>               | No          | Yes           | No                     | Enabled/Disabled |                  |

| LVCMOS 2.5 V / 5.0 V <sup>2</sup>       | Yes         | No            | Yes <sup>3</sup>       | Enabled/Disabled |                  |

| LVCMOS 1.8 V                            | No          | Yes           | No                     | Enabled/Disabled |                  |

| LVCMOS 1.5 V                            | No          | Yes           | No                     | Enabled/         | Disabled         |

| Voltage-Referenced Input Buffer         | No          | Yes           | No                     | Enabled/Disabled |                  |

| Differential, LVDS/B-LVDS/M-LVDS/LVPECL | No          | Yes           | No                     | Enabled/         | Disabled         |

Table 13 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in IGLOOe and ProASIC3E Devices

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

2. In the SmartGen Core Reference Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard.

3. Can be implemented with an external resistor and an internal clamp diode.

## **5 V Input and Output Tolerance**

IGLOO and ProASIC3 devices are both 5 V-input– and 5 V-output–tolerant if certain I/O standards are selected. Table 6 on page 6 shows the I/O standards that support 5 V input tolerance. Only 3.3 V LVTTL/LVCMOS standards support 5 V output tolerance. Refer to the appropriate family datasheet for detailed description and configuration information.

This feature is not shown in the I/O Attribute Editor.

### 5 V Input Tolerance

I/Os can support 5 V input tolerance when LVTTL 3.3 V, LVCMOS 3.3 V, LVCMOS 2.5 V, and LVCMOS 2.5 V / 5.0 V configurations are used (see Table 13 on page 19). There are four recommended solutions for achieving 5 V receiver tolerance (see Figure 10 on page 21 to Figure 13 on page 23 for details of board and macro setups). All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

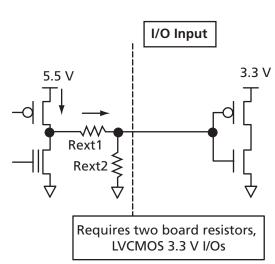

#### Solution 1

The board-level design must ensure that the reflected waveform at the pad does not exceed the limits provided in the recommended operating conditions in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the two external resistors as explained below. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

This solution requires two board resistors, as demonstrated in Figure 10 on page 21. Here are some examples of possible resistor values (based on a simplified simulation model with no line effects and 10  $\Omega$  transmitter output resistance, where Rtx\_out\_high = [V<sub>CCI</sub> - V<sub>OH</sub>] / I<sub>OH</sub> and Rtx\_out\_low = V<sub>OL</sub> / I<sub>OL</sub>).

Example 1 (high speed, high current):

$Rtx_out_high = Rtx_out_low = 10 \Omega$

R1 = 36  $\Omega(\pm 5\%)$ , P(r1)min = 0.069  $\Omega$

R2 = 82  $\Omega(\pm 5\%)$ , P(r2)min = 0.158  $\Omega$

$Imax_tx = 5.5 V / (82 \times 0.95 + 36 \times 0.95 + 10) = 45.04 mA$

$t_{RISE} = t_{FALL} = 0.85$  ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

$t_{RISE} = t_{FALL} = 4$  ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Example 2 (low-medium speed, medium current):

$Rtx_out_high = Rtx_out_low = 10 \Omega$

R1 = 220  $\Omega(\pm 5\%)$ , P(r1)min = 0.018  $\Omega$

R2 = 390  $\Omega(\pm 5\%)$ , P(r2)min = 0.032  $\Omega$

$Imax_tx = 5.5 V / (220 \times 0.95 + 390 \times 0.95 + 10) = 9.17 mA$

$t_{RISE} = t_{FALL} = 4$  ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 20 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin(rx) < 3.6 V when the transmitter sends a logic 1. This range of Vin\_dc(rx) must be assured for any combination of transmitter supply (5 V ± 0.5 V), transmitter output resistance, and board resistor tolerances.

Temporary overshoots are allowed according to the overshoot and undershoot table in the datasheet.

20

### Solution 1

#### Figure 10 • Solution 1

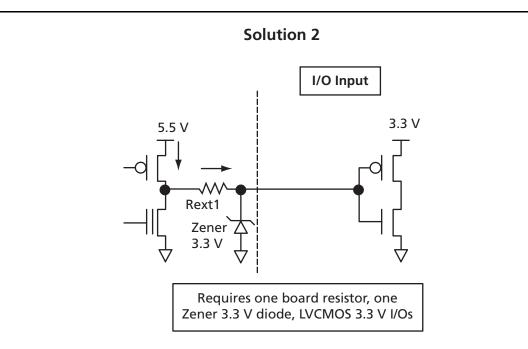

#### Solution 2

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 11. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

#### Figure 11 • Solution 2

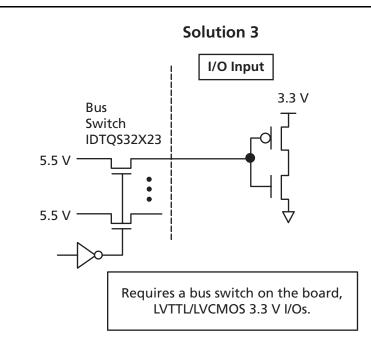

#### Solution 3

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the bus switch, as shown in Figure 12. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

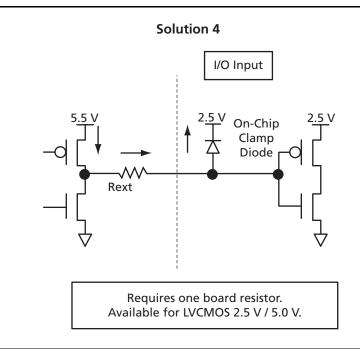

#### Solution 4

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

#### Figure 13 • Solution 4

| Solution | Board Components                                                                                               | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Two resistors                                                                                                  | Low to High <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                      |

| 2        | Resistor and Zener 3.3 V                                                                                       | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                      |

| 3        | Bus switch                                                                                                     | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                          |

| 4        | Minimum resistor value <sup>2,3,4,5</sup>                                                                      | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at 1                                                                                                                                                                                                                                                                                                             |

|          | R = 47 Ω at T <sub>J</sub> = 70°C<br>R = 150 Ω at T <sub>J</sub> = 85°C<br>R = 420 Ω at T <sub>J</sub> = 100°C |                          | 52.7 mA at $T_J = 70^{\circ}$ C / 10-year lifetime<br>16.5 mA at $T_J = 85^{\circ}$ C / 10-year lifetime<br>5.9 mA at $T_J = 100^{\circ}$ C / 10-year lifetime<br>For duty cycles other than 100%, the currents can be<br>increased by a factor of 1 / (duty cycle).<br>Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) × 52.7 mA = 5 × 52.7 mA =<br>263.5 mA |

Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

- 3. At 70°C, customers could still use 420  $\Omega$  on every I/O.

- 4. At 85°C, a 5 V solution on every other I/O is permitted, since the resistance is lower (150  $\Omega$ ) and the current is higher. Also, the designer can still use 420  $\Omega$  and use the solution on every I/O.

- 5. At 100°C, the 5 V solution on every I/O is permitted, since 420  $\Omega$  are used to limit the current to 5.9 mA.

## 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact,  $V_{OL} = 0.4$  V and  $V_{OH} = 2.4$  V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the  $V_{IL} = 0.8$  V and  $V_{IH} = 2$  V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## Schmitt Trigger

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

ProASIC3E devices have Schmitt triggers built into their I/O circuitry. The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 6 on page 6) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

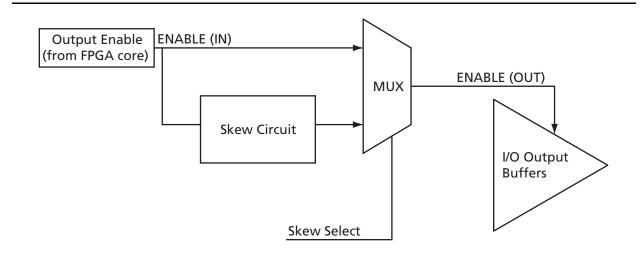

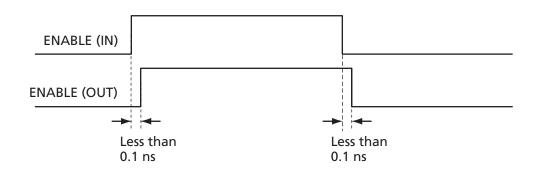

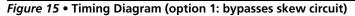

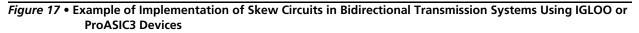

## Selectable Skew between Output Buffer Enable and Disable Times

Low-power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The Skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 6 on page 6) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.

Figure 14 • Block Diagram of Output Enable Path

24

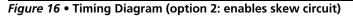

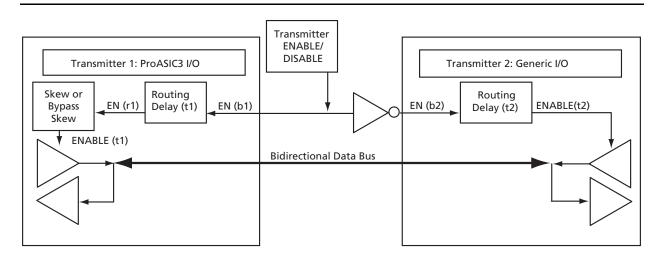

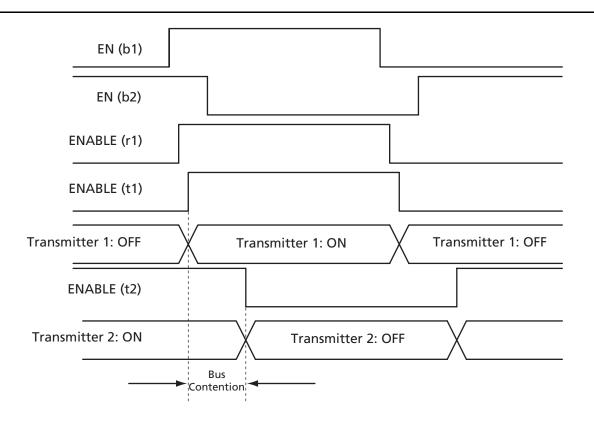

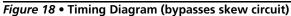

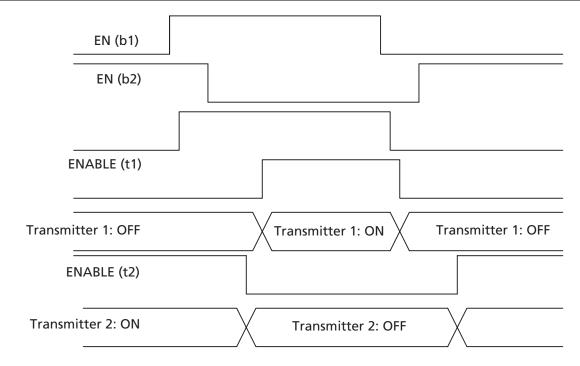

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss and/or transmitter over-stress due to transmitter-to-transmitter current shorts. Figure 17 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 18 on page 26 shows how bus contention is created, and Figure 19 on page 26 shows how it can be avoided with the skew circuit.

**Result: No Bus Contention**

## I/O Register Combining

Every I/O has several embedded registers in the I/O tile that are close to the I/O pads. Rather than using the internal register from the core, the user has the option of using these registers for faster clock-to-out timing, and external hold and setup. When combining these registers at the I/O buffer, some architectural rules must be met. Provided these rules are met, the user can enable register combining globally during Compile (as shown in the "Compiling the Design" section in the I/O Software Control in Low-Power Flash Devices section of the handbook).

This feature is supported by all I/O standards.

#### Rules for Registered I/O Function:

- 1. The fanout between an I/O pin (D, Y, or E) and a register must be equal to one for combining to be considered on that pin.

- 2. All registers (Input, Output, and Output Enable) connected to an I/O must share the same clear or preset function:

- If one of the registers has a CLR pin, all the other registers that are candidates for combining in the I/O must have a CLR pin.

- If one of the registers has a PRE pin, all the other registers that are candidates for combining in the I/O must have a PRE pin.

- If one of the registers has neither a CLR nor a PRE pin, all the other registers that are candidates for combining must have neither a CLR nor a PRE pin.

- If the clear or preset pins are present, they must have the same polarity.

- If the clear or preset pins are present, they must be driven by the same signal (net).

- 3. Registers connected to an I/O on the Output and Output Enable pins must have the same clock and enable function:

- Both the Output and Output Enable registers must have an E pin (clock enable), or none at all.

- If the E pins are present, they must have the same polarity. The CLK pins must also have the same polarity.

In some cases, the user may want registers to be combined with the input of a bibuf while maintaining the output as-is. This can be achieved by using PDC commands as follows:

```

set_io <signal name> -REGISTER yes -----register will combine

set_preserve <signal name> ----register will not combine

```

## Weak Pull-Up and Weak Pull-Down Resistors

When the I/O is pulled up, it is connected to the  $V_{CCI}$  of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to the datasheet for more information.

For low-power applications, configuration of the pull-up or pull-down of the I/O can be used to set the I/O to a known state while the device is in Flash\*Freeze mode. Refer to *Flash\*Freeze Technology and Low-Power Modes in IGLOO and ProASIC3L Devices* for more information.

The Flash\*Freeze (FF) pin cannot be configured with a weak pull-down or pull-up I/O attribute, as the signal needs to be driven at all times.

## **Output Slew Rate Control**

The slew rate is the amount of time an input signal takes to get from logic LOW to logic HIGH or vice versa.

It is commonly defined as the propagation delay between 10% and 90% of the signal's voltage swing. Slew rate control is available for the output buffers of low-power flash devices. The output buffer has a programmable slew rate for both HIGH-to-LOW and LOW-to-HIGH transitions. Slew rate control is available for LVTTL, LVCMOS, and PCI-X I/O standards. The other I/O standards have a preset slew value.

The slew rate can be implemented by using a PDC command (Table 6 on page 6), setting it "High" or "Low" in the I/O Attribute Editor in Designer, or instantiating a special I/O macro. The default slew rate value is "High."

IGLOOe and ProASIC3E devices support output slew rate control: high and low. Actel recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

## **Output Drive**

The output buffers of IGLOOe and ProASIC3E devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths. Other standards have a preset value.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V / 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For other IGLOOe and ProASIC3E devices, refer to Table 15 for more information about the slew rate and drive strength specification.

There will be a difference in timing between the Standard Plus I/O banks and the Advanced I/O banks. Refer to the I/O timing tables in the datasheet for the standards supported by each device.

| I/O Standards      | 2 mA | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | 24 mA | Sle  | w   |

|--------------------|------|------|------|------|-------|-------|-------|------|-----|

| LVTTL/LVCMOS 3.3 V | 1    | ✓    | ✓    | ✓    | 1     | 1     | 1     | High | Low |

| LVCMOS 2.5 V       | 1    | 1    | 1    | 1    | 1     | 1     | 1     | High | Low |

| LVCMOS 2.5/5.0 V   | ✓    | 1    | 1    | 1    | ~     | 1     | 1     | High | Low |

| LVCMOS 1.8 V       | ✓    | 1    | 1    | 1    | ~     | 1     | -     | High | Low |

| LVCMOS 1.5 V       | ~    | 1    | 1    | 1    | 1     | -     | -     | High | Low |

Table 15 • IGLOOe and ProASIC3E I/O Standards—Output Drive and Slew Rate

## Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout

Each I/O voltage bank has a separate ground and power plane for input and output circuits (VMV/GNDQ for input buffers and  $V_{CCI}$ /GND for output buffers). This isolation is necessary to minimize simultaneous switching noise from the input and output (SSI and SSO). The switching noise (ground bounce and power bounce) is generated by the output buffers and transferred into input buffer circuits, and vice versa.

Since voltage bounce originates on the package inductance, the VMV and  $V_{CCI}$  supplies have separate package pin assignments. For the same reason, GND and GNDQ also have separate pin assignments.

The VMV and  $V_{CCI}$  pins must be shorted to each other on the board. Also, the GND and GNDQ pins must be shorted to each other on the board. This will prevent unwanted current draw from the power supply.

SSOs can cause signal integrity problems on adjacent signals that are not part of the SSO bus. Both inductive and capacitive coupling parasitics of bond wires inside packages and of traces on PCBs will transfer noise from SSO busses onto signals adjacent to those busses. Additionally, SSOs can produce ground bounce noise and V<sub>CCI</sub> dip noise. These two noise types are caused by rapidly changing currents through GND and V<sub>CCI</sub> package pin inductances during switching activities (EQ 2 and EQ 3).

Ground bounce noise voltage =  $L(GND) \times di/dt$

EQ 2

$V_{CCI}$  dip noise voltage =  $L(V_{CCI}) \times di/dt$

EQ 3

Any group of four or more input pins switching on the same clock edge is considered an SSO bus. The shielding should be done both on the board and inside the package unless otherwise described.