# HA16150T/P

# High-Speed Current Mode Push-Pull PWM Control IC

REJ03F0146-0300 Rev.3.00 Jan 30, 2007

#### **Description**

The HA16150 is a high-speed current mode PWM control IC with push-pull dual outputs, suitable for high-reliability, high-efficiency, high-mounting-density isolated DC-DC converter and high-output AC-DC converter control.

The HA16150 can be used in various applications, including push-pull converters and half-bridge, double-forward, and single-forward applications.

The HA16150 incorporates 180-degree phase-inverted push-pull dual outputs, and directly drives a power MOS FET. Operation at a maximum of 1 MHz is possible on an oscillator reference frequency.

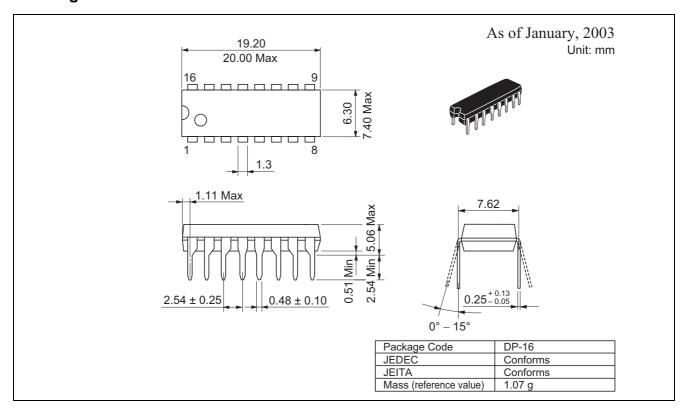

The package lineup comprises an ultra-thin surface-mount TSSOP-16 suitable for slim communication system modules, and a general-purpose insertion DILP-6 suitable for characteristics evaluation.

#### **Features**

#### <Maximum Ratings>

- Supply voltage Vcc: 20 V

- Peak output current Ipk-out: ±1.0 A

- Operating junction temperature Tjopr: -40°C to +125°C

#### <Electrical Characteristics>

- VREF output voltage VREF:  $5.0 \text{ V} \pm 1\%$

- UVLO start threshold VH:  $9.3 \text{ V} \pm 0.7 \text{ V}$

- UVLO shutdown threshold VL:  $8.3 \text{ V} \pm 0.7 \text{ V}$

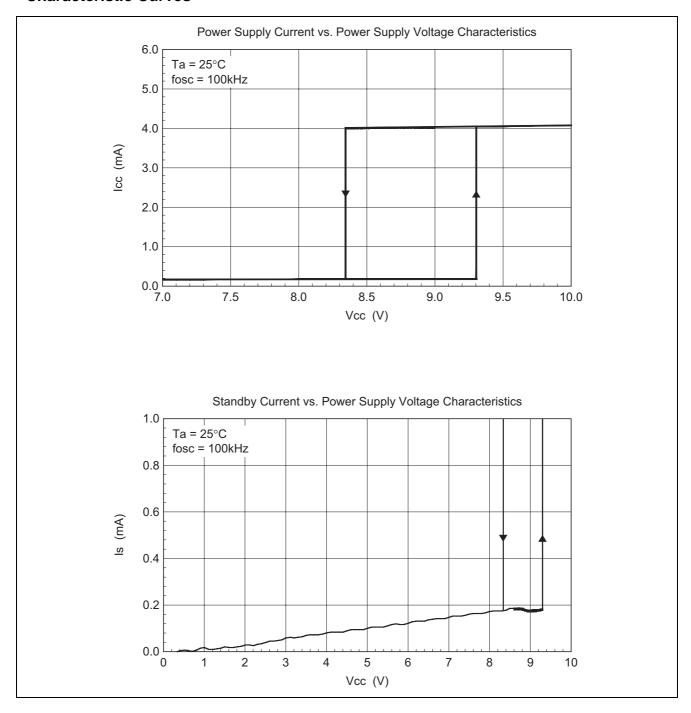

- Operating current Icc: 4 mA typ.

- Standby current Is: 150 μA typ.

#### <Functions>

- Soft start (one external timing capacitance)

- Remote on/off control

- Independent dead band time adjustment

- Current limiter adjustment (set drooping characteristic adjustment)

- Push-pull/single-end output switching

- Package lineup: TSSOP-16/DILP-16

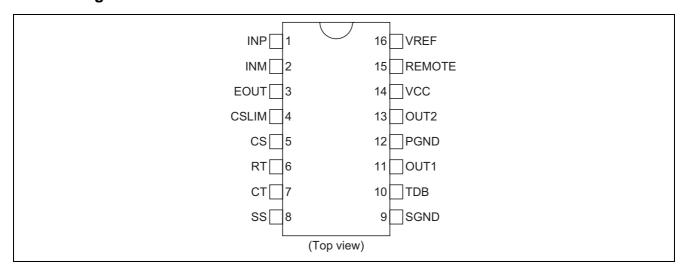

# **Pin Arrangement**

# **Pin Functions**

| Pin No. Pin Name |        | Pin Functions                                         |  |  |  |

|------------------|--------|-------------------------------------------------------|--|--|--|

| 1                | INP    | Error amplifier non-inverted (+) input                |  |  |  |

| 2                | INM    | Error amplifier inverted (–) input                    |  |  |  |

| 3                | EOUT   | Error amplifier output                                |  |  |  |

| 4                | CSLIM  | Current limiter level adjustment                      |  |  |  |

| 5                | CS     | Current sense signal input                            |  |  |  |

| 6                | RT     | Operating frequency setting resistance connection     |  |  |  |

| 7                | СТ     | Operating frequency setting capacitance connection    |  |  |  |

| 8                | SS     | Soft start time setting timing capacitance connection |  |  |  |

| 9                | SGND   | Small signal system ground                            |  |  |  |

| 10               | TDB    | Dead band time setting timing capacitance connection  |  |  |  |

| 11               | OUT1   | Power MOS FET driver output 1                         |  |  |  |

| 12               | PGND   | Power system ground                                   |  |  |  |

| 13               | OUT2   | Power MOS FET driver output 2                         |  |  |  |

| 14               | VCC    | Supply voltage                                        |  |  |  |

| 15               | REMOTE | Remote on/off control                                 |  |  |  |

| 16               | VREF   | Reference voltage                                     |  |  |  |

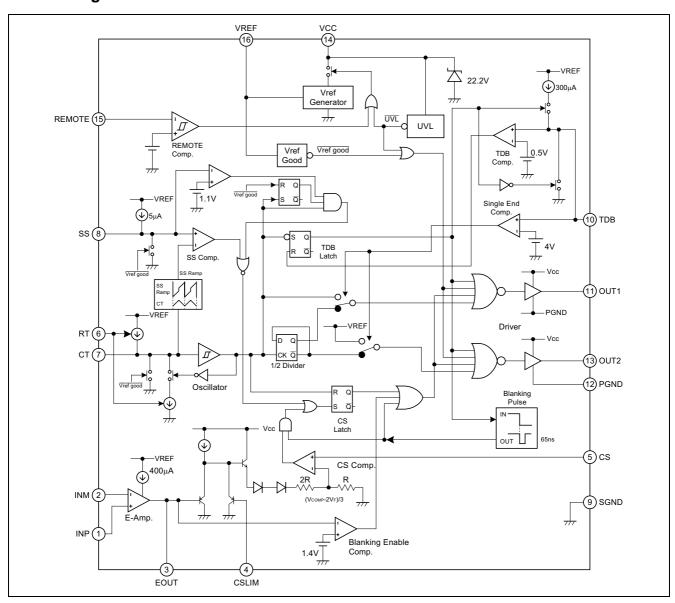

# **Block Diagram**

# **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                           | Symbol   | Ratings      | Unit | Note |

|--------------------------------|----------|--------------|------|------|

| Power supply voltage           | Vcc      | 20           | V    |      |

| OUT1 output current (peak)     | lpk-out1 | ±1.0         | Α    | 3    |

| OUT2 output current (peak)     | lpk-out2 | ±1.0         | Α    | 3    |

| OUT1 output current (DC)       | ldc-out1 | ±0.1         | Α    |      |

| OUT2 output current (DC)       | ldc-out2 | ±0.1         | Α    |      |

| OUT1 output voltage            | Vout1    | -0.3 to Vcc  | V    |      |

| OUT2 output voltage            | Vout2    | -0.3 to Vcc  | V    |      |

| INM pin voltage                | Vinm     | -0.3 to Vcc  | V    |      |

| REMOTE pin voltage             | Vremote  | -0.3 to Vcc  | V    |      |

| REMOTE pin current             | Iremote  | +0.2         | mA   |      |

| INP pin voltage                | Vinp     | -0.3 to Vcc  | V    |      |

| SS pin voltage                 | Vss      | −0.3 to Vref | V    |      |

| RT pin voltage                 | Vrt      | −0.3 to Vref | V    |      |

| RT pin current                 | Irt      | -0.2         | mA   |      |

| CT pin voltage                 | Vct      | −0.3 to Vref | V    |      |

| CSLIM pin voltage              | Vcslim   | -0.3 to Vref | V    |      |

| EOUT pin voltage               | Veout    | −0.3 to Vref | V    |      |

| VREF pin voltage               | Vref     | −0.3 to Vref | V    |      |

| TDB pin voltage                | Vtdb     | −0.3 to Vref | V    |      |

| CS pin voltage                 | Vcs      | −0.3 to Vref | V    |      |

| Operating junction temperature | Tj-opr   | -40 to +125  | °C   | 4    |

| Storage temperature            | Tstg     | -55 to +150  | °C   |      |

Notes: 1. Rated voltages are with reference to the GND (SGND, PGND) pin.

- 2. For rated currents, inflow to the IC is indicated by (+), and outflow by (-).

- 3. Shows the transient current when driving a capacitive load.

- 4. HA16150T (TSSOP):  $\theta$ ja = 250°C/W

This value is based on actual measurements on a 110% wiring density glass epoxy circuit board (55 mm  $\times$  45 mm  $\times$  1.6 mm).

HA16150P (DILP):  $\theta$ ja = 124°C/W

# **Electrical Characteristics**

$(Ta = 25^{\circ}C, Vcc = 12 V, Fosc = 100 kHz)$

|            | Item                                        | Symbol     | Min  | Тур  | Max  | Unit   | Test Conditions                                               |

|------------|---------------------------------------------|------------|------|------|------|--------|---------------------------------------------------------------|

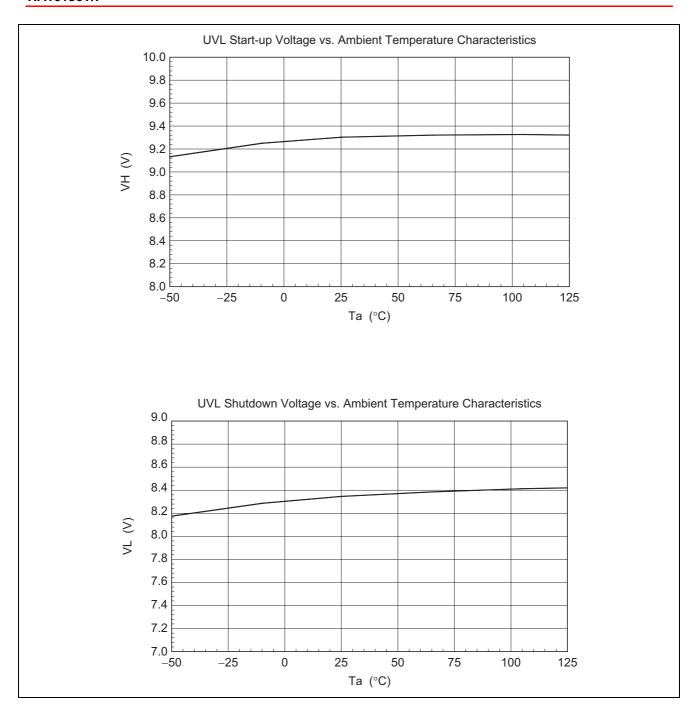

| Supply     | Start threshold                             | VH         | 8.6  | 9.3  | 10.0 | V      |                                                               |

|            | Shutdown threshold                          | VL         | 7.6  | 8.3  | 9.0  | V      |                                                               |

|            | UVLO hysteresis                             | $dV_{UVL}$ | 0.7  | 1.0  | 1.3  | V      |                                                               |

|            | Start-up current                            | Is         | 100  | 150  | 250  | μΑ     | Vcc = 8V                                                      |

|            | Operating current                           | Icc        | _    | 4    | 6    | mA     | Vinm = 1.0V, Vinp = 1.25V,<br>Vcs = 0V                        |

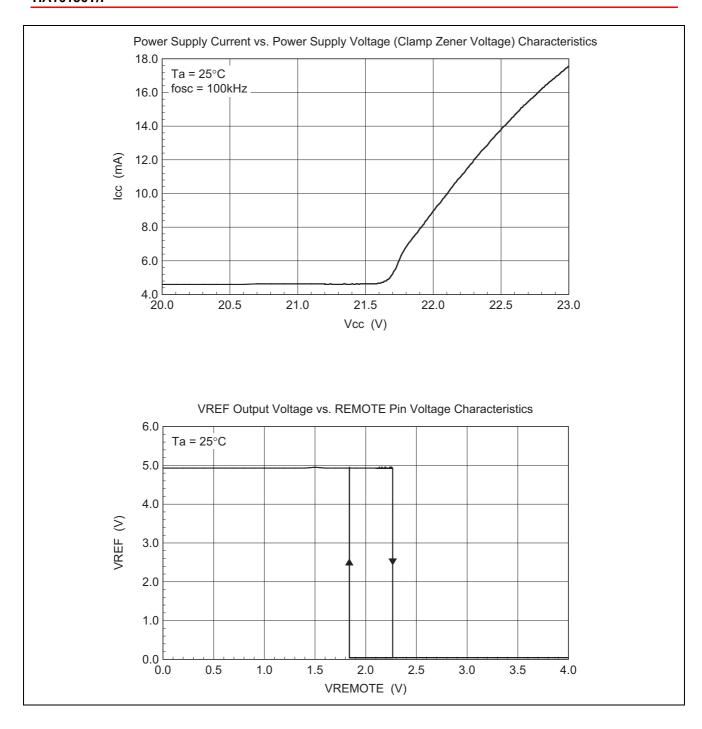

|            | Vcc zenner shunt voltage                    | Vz         | 21.2 | 22.2 | 23.2 | V      | Icc = 10mA                                                    |

|            | Vz temperature stability                    | dVz/dTa    | _    | 4.5  | ı    | mV/°C  | Icc = 10mA *1                                                 |

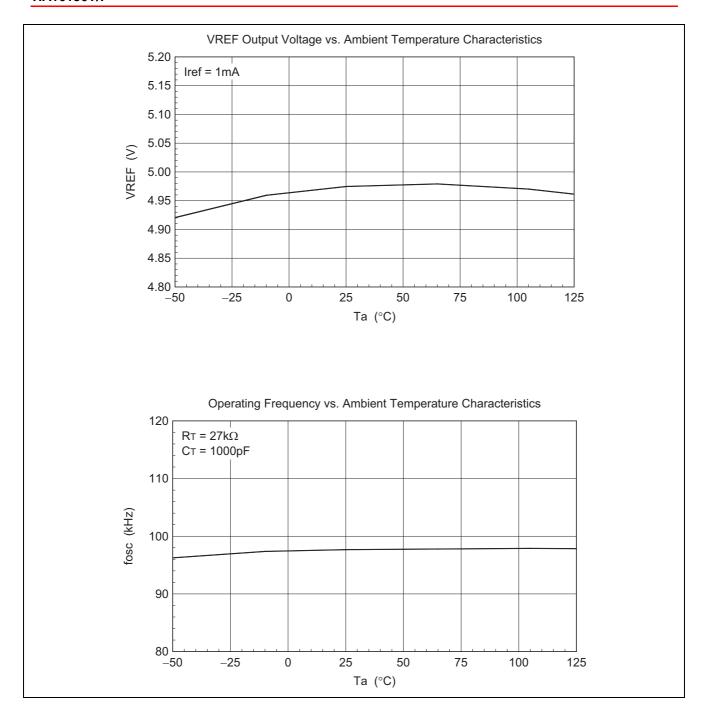

| VREF       | Output voltage                              | Vref       | 4.95 | 5.0  | 5.05 | V      | Iref = −1mA                                                   |

|            | Line regulation                             | Vref-line  | _    | 5    | 20   | mV     | Vcc = 11V to 18V                                              |

|            | Load regulation                             | Vref-load  | _    | 5    | 20   | mV     | Iref = −1mA to −20mA                                          |

|            | Temperature stability                       | dVref/dTa  | _    | 80   | -    | ppm/°C | Ta = -40 to 125°C                                             |

| Oscillator | Oscillator frequency                        | fosc       | 88   | 100  | 112  | kHz    | Measured at OUT1 and OUT2<br>RT = $27k\Omega$ , CT = $1000pF$ |

|            | Temperature stability                       | dfosc/dTa  | _    | ±0.1 | _    | %/°C   | Ta = -40 to 125°C *1                                          |

| PWM        | High voltage                                | Vth        | -    | 3.0  | _    | V      | DC *1                                                         |

| Comparator | Low voltage                                 | VtI        | _    | 2.0  | _    | V      | DC *1                                                         |

|            | Differential voltage                        | dVt        | _    | 1.0  | _    | V      | DC *1                                                         |

| Error      | Input bias current                          | Ifb        | -1   | _    | +1   | μΑ     |                                                               |

| amplifier  | Open loop gain                              | Av         | _    | 70   | _    | dB     | f = 1.0kHz *1                                                 |

|            | EOUT sink current                           | Isnk-eout  | _    | 3.0  | _    | mA     | Veout = 1.1V *1                                               |

|            | EOUT source current                         | Isrc-eout  | _    | -0.4 | _    | mA     | Veout = 3.0V *1                                               |

|            | Low voltage                                 | Vol-eout   | -    | 0.8  | 1.1  | V      | EOUT : Open                                                   |

|            | High voltage                                | Voh-eout   | 4.7  | 5.0  | _    | V      | EOUT : Open                                                   |

| Current    | Voltage gain                                | Avcs       | 2.85 | 3.00 | 3.15 | V/V    |                                                               |

| sense      | Delay to output                             | td-cs      | _    | 150  | 230  | ns     |                                                               |

|            | Leading edge<br>blanking<br>time            | tbl        | -    | 65   | -    | ns     | *1                                                            |

|            | Leading edge<br>blanking<br>disable voltage | Vbl-off    | 1.3  | 1.4  | 1.5  | V      | Measured pin : EOUT                                           |

| Remote     | On threshold voltage                        | Von        | 1.40 | -    | -    | V      | *1                                                            |

|            | Off threshold voltage                       | Voff       | _    | -    | 3.00 | V      | *1                                                            |

|            | Sink current                                | Iremote    | 60   | 90   | 120  | μА     | Vremote = 4V                                                  |

| Soft start | Source current                              | Iss        | -7.0 | -5.0 | -3.0 | μА     | Vss = 1V                                                      |

Note: 1. Reference values for design.

# **Electrical Characteristics** (cont.)

$(Ta = 25^{\circ}C, Vcc = 12 V, Fosc = 100 kHz)$

|           | Item               | Symbol    | Min  | Тур  | Max | Unit | Test Conditions       |

|-----------|--------------------|-----------|------|------|-----|------|-----------------------|

| OUT1      | Minimum duty cycle | Dmin-out1 | _    | _    | 0   | %    | Veout = 0V            |

|           | Maximum duty       | Dmax-out1 | 48   | 49   | _   | %    | TDB : OPEN            |

|           | cycle              |           |      |      |     |      |                       |

|           | Rise time          | tr-out1   | _    | 30   | 65  | ns   | CL = 1000pF           |

|           | Fall time          | tf-out1   | _    | 30   | 65  | ns   | CL = 1000pF           |

|           | Low voltage        | Vol1-out1 | _    | 0.05 | 0.2 | ٧    | lout = 20mA           |

|           |                    | Vol2-out1 | _    | 0.5  | 2.0 | ٧    | lout = 200mA (pulse)  |

|           | High voltage       | Voh1-out1 | 11.5 | 11.9 | -   | V    | lout = -20mA          |

|           |                    | Voh2-out1 | 10.0 | 11.0 | -   | V    | lout = -200mA (pulse) |

| OUT2      | Minimum duty cycle | Dmin-out2 | -    | -    | 0   | %    | Veout = 0V            |

|           | Maximum duty       | Dmax-out2 | 48   | 49   | _   | %    | TDB : OPEN            |

|           | cycle              |           |      |      |     |      |                       |

|           | Rise time          | tr-out2   | _    | 30   | 65  | ns   | CL = 1000pF           |

|           | Fall time          | tf-out2   | _    | 30   | 65  | ns   | CL = 1000pF           |

|           | Low voltage        | Vol1-out2 | -    | 0.05 | 0.2 | V    | lout = 20mA           |

|           |                    | Vol2-out2 | _    | 0.5  | 2.0 | V    | lout = 200mA (pulse)  |

|           | High voltage       | Voh1-out2 | 11.5 | 11.9 | _   | V    | lout = -20mA          |

|           |                    | Voh2-out2 | 10.0 | 11.0 | _   | V    | lout = -200mA (pulse) |

| Dead-band | Dead-band time     | tdb0      | _    | 60   | _   | ns   | TDB : OPEN *1         |

| time      |                    | tdb       | -    | 140  | 1   | ns   | Ctdb = 47pF *1        |

Note: 1. Reference values for design.

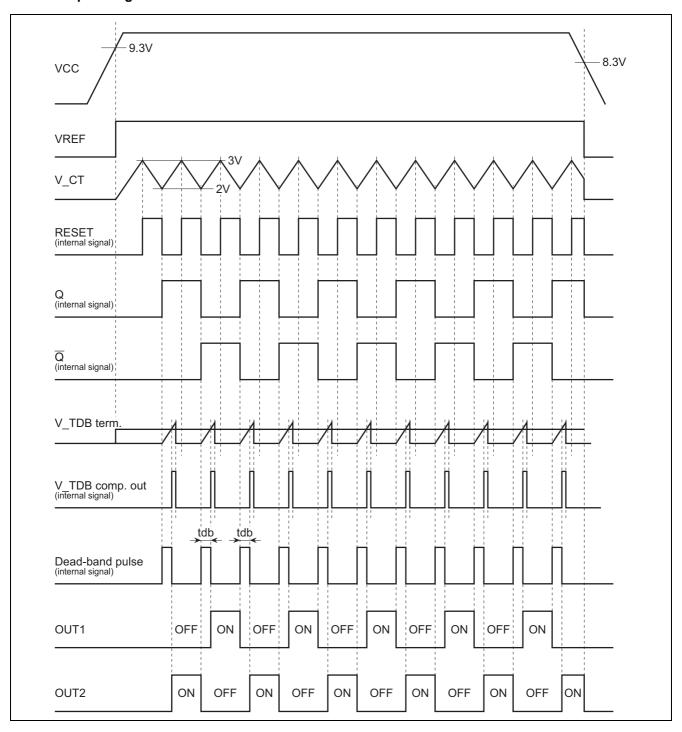

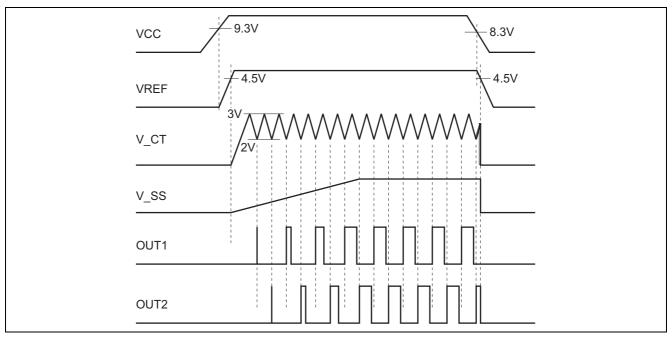

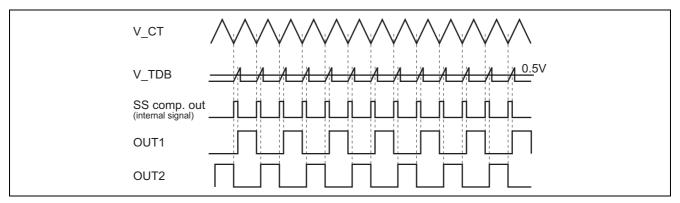

# **Timing Diagram**

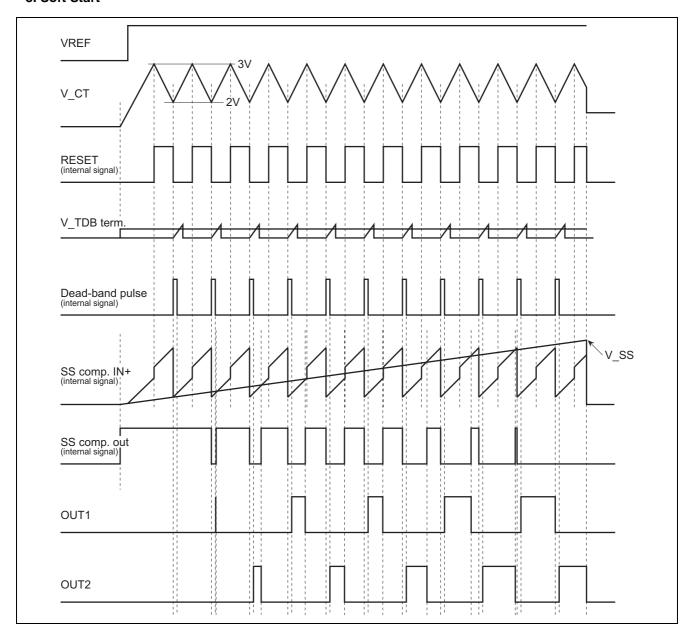

#### 1. Start-up Timing

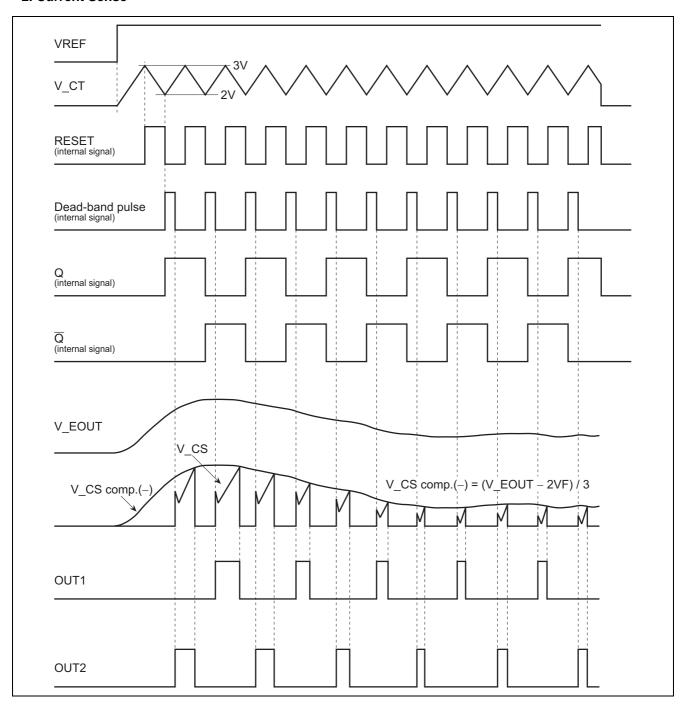

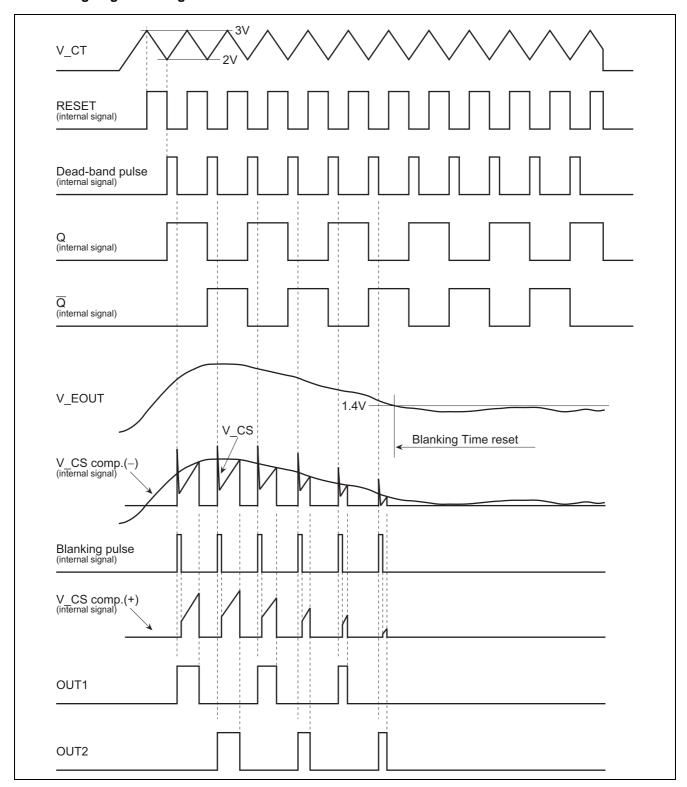

#### 2. Current Sense

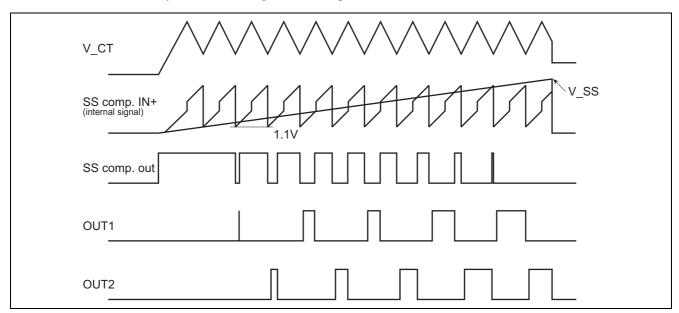

#### 3. Soft Start

# 4. Leading Edge Blanking

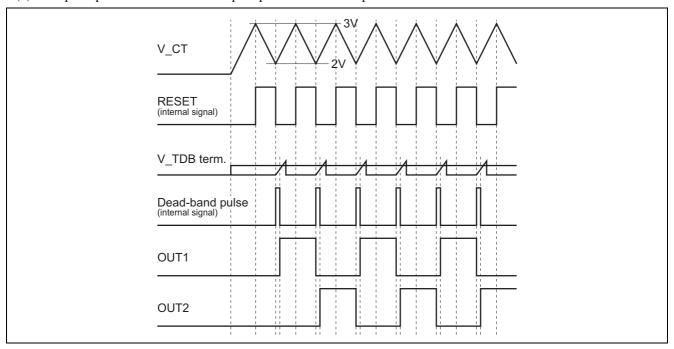

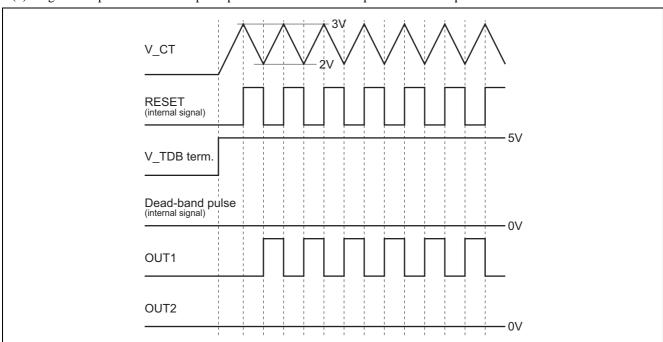

#### 5. Push-Pull/Single-End Switching

(1) Push-pull operation: Leave the TDB pin open or connect a capacitance to GND

(2) Single-end operation: Perform pull-up connection of the TDB pin to the VREF pin

#### **Functional Description**

#### 1. UVL Circuit

The UVL circuit monitors the Vcc voltage and halts operation of the IC in the event of a low voltage.

The voltage for detecting Vcc has a hysteresis characteristic, with 9.3 V as the start threshold and 8.3 V as the shutdown threshold.

When the IC has been halted by the UVL circuit, control is performed to fix driver circuit output low, halt VREF output and the oscillator, and reset the soft start circuit.

Figure 1

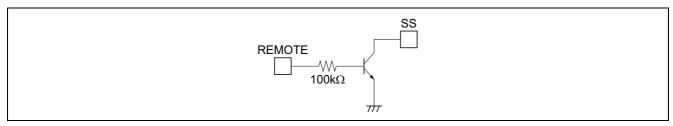

#### 2. Remote ON/OFF Circuit

A remote on/off control function is incorporated, enabling the IC to be halted without cutting the supply voltage by pulling the REMOTE pin up to 3.0~V or higher.

This function halts VREF output and driver output.

At this time the IC enters Remote-OFF mode and IC current dissipation can be decreased. This function can thus be used for power management, etc.

When remote off control is performed, the soft start circuit is also reset, and therefore a soft start is effected when restarting, preventing overshoot.

However, when restarting by the remote on control function before the SS pin is completely discharged, soft start operation may not be performed normally. In such a case, add a circuit to pull the SS pin out in conjunction with a remote off signal.

Figure 2 Example of Circuit to Pull out SS Pin

If the remote on/off control function is not used, the REMOTE pin should be permanently pulled down to GND with a resistance of about  $100 \text{ k}\Omega$ .

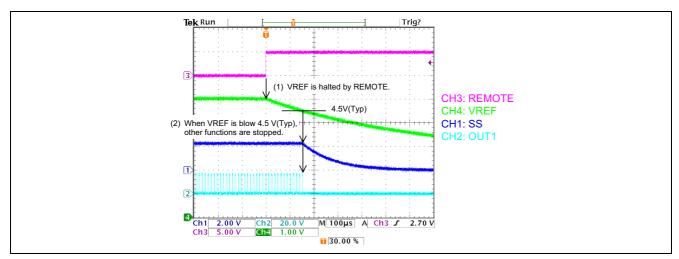

The remote on/off control function halts only reference voltage. Other functions will be stopped when the reference voltage is below 4.5 V (typ.). Large stabilizing capacitance of the VREF pin results in a difference between the timing of remote off signal and the timing to stop the IC

Figure 3 Operation When Remote is Off (Reference Data)

#### 3. Soft Start Circuit

This function gradually increases the pulse width of the OUT pin from 0% duty at start-up to prevent a sudden increase in the pulse width that may cause problems such as transient stress on external parts or overshoot of the secondary-side output voltage.

The soft start time can easily be set with a single external capacitance.

Figure 4

Soft start time tss is determined by SS pin connection capacitance Css and an internal constant, and can be estimated using the equation shown below.

Soft start time tss is the time until the first pulse is output to the driver output OUT pin after VREF starts up following UVLO release.

This is equivalent to the time until the SS pin voltage reaches IC-internal SS comparator reference voltage VTL (1.1 V), and can be calculated using the approximate equation shown below.

Soft start time tss when Css is 1000pF is given by the following equation.

tss =

$$\frac{\text{Css} \times \text{VTL}}{\text{Iss}}$$

=  $\frac{1000 \text{ [pF]} \times 1.1 \text{ [V]}}{5 \text{ [µA]}}$

$\approx 220 \text{ [µs]}$

Note: A soft start circuit operates only once at the start-up of the IC (after the VREF pin voltage is launched and the VrefGOOD circuit is operated). If the SS pin is lowered to 1.1 V or less after the SS pin becomes once high, the pulse of OUT1 and OUT2 is not halt. Each duty cycle of OUT1 and OUT2 is fixed to 25%.

#### 4. Dead Band Generation Circuit

"Dead band" refers to the time when both push-pull dual outputs are off.

By setting the dead band time arbitrarily, it is possible to configure a system in which the dual outputs are never on simultaneously with respect to input and load variations.

Figure 5

Dead band time tdb is determined by TDB pin connection capacitance Cdb and an internal constant, and can be estimated using the equation shown below.

Even when the TDB pin is open, the dead band time does not become zero due to floating capacitance of the IC package, etc. This dead band time is designated tdb0.

Dead band time tdb when Cdb is 47 pF is given by the following equation.

tdb = tdb0 +

$$\frac{\text{Cdb} \times \text{Vth}}{\text{Idb}}$$

= tdb0 +  $\frac{47 \text{ [pF]} \times 0.5 \text{ [V]}}{300 \text{ [}\mu\text{A]}}$

= 60 [ns] + 78 [ns]

= 138 [ns]

- \* Idb: TDB pin source current, 300 μA typ.

- \* Vth: IC-internal TDB comparator reference voltage

<sup>\*</sup> Iss: SS pin source current, 5 μA typ.

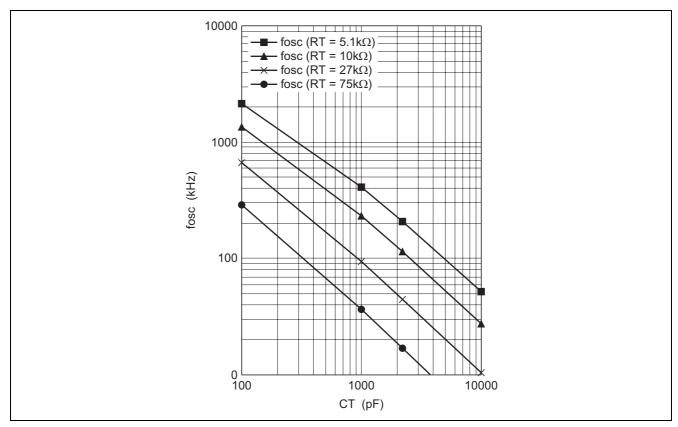

# 5. Operating Frequency

The operating frequency is adjusted by means of CT and RT.

Adjustment examples are shown in the graph below. This graph shows driver output operating frequencies. The reference operating frequency generated at the CT pin is twice the driver output frequency.

The driver output operating frequency can be estimated using the approximate equation shown below.

This is only an approximate equation, and the higher the frequency, the greater will be the degree of error of the approximate equation due to the effects of CT pin voltage overshoot, undershoot and so forth.

When the operating frequency is adjusted, it is essential to confirm operation using the actual system.

$$\begin{aligned} \text{fosc} &= \frac{8}{3 \times \text{CT} \times \text{RT}} = \frac{8}{3 \times \text{C6} \times \text{R7}} \\ &= \frac{8}{3 \times 470 \text{ [pF]} \times 27 \text{ [k}\Omega\text{]}} \\ &= 210 \text{ [kHz]} \end{aligned}$$

Figure 6

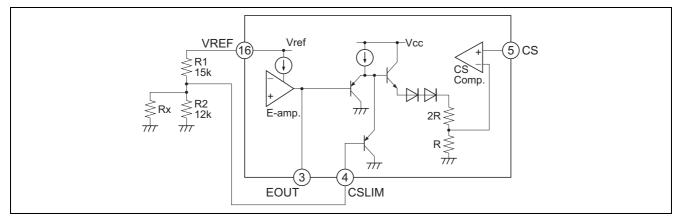

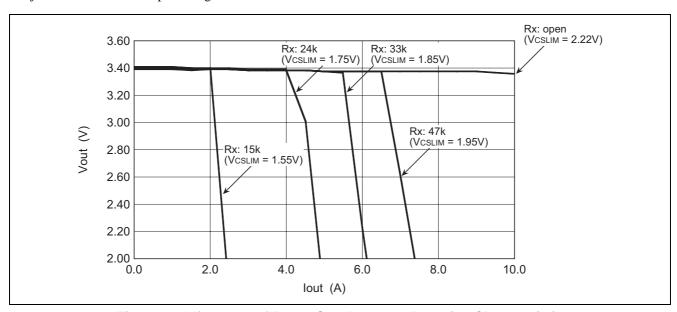

#### 6. Current Limiter Level

The drooping characteristic of the power supply output can be adjusted by adjusting the CSLIM pin voltage.

For example, the drooping characteristic can easily be adjusted, as shown in the figure below, by setting VREF to a divided value with resistances R1 and R2 and connecting adjustment resistance Rx in parallel to R2.

Figure 7 CSLIM Peripheral Circuit

The graph below shows examples of power supply output drooping characteristic adjustment in a push-pull converter.

As shown in this graph, the point at which the power supply output current limit begins to be applied can be adjusted by adjustment of the CSLIM pin voltage.

Figure 8 Adjustment of Power Supply Output Drooping Characteristic

#### 7. VREF Circuit

- (1) For the VREF pin, make sure to connect stabilizing capacitance to GND.

- (2) When the value of stabilizing capacitance is small or the load of VREF pin is heavy, either OUT1 or OUT2 may be halted at high level if the IC is stopped by a remote off function. In such a case, increase the capacitance value. The minimum value of capacitance to be connected is approximated by the following equation.

Cref >

$$\frac{10\mu s \times (Iref + 6mA)}{4.95V}$$

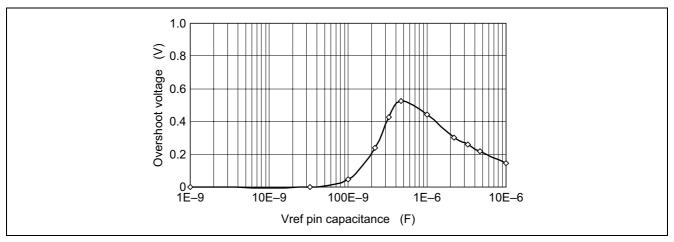

(3) Depending on the value of capacitance to be connected, overshoot may result at the rising of the VREF pin (see the figure below). Take extra care when the VREF pin voltage is used as the power supply and reference voltage of external circuit.

Figure 9 Overshoot Voltage of Vref Pin (Reference Data)

#### 8. CS Pin

RC filter is generally inserted into the CS pin to prevent the pin from malfunction due to noise. The CS pin has an internal circuit to pull out electric charge while both of the OUT1 and OUT2 are at the low level (dead band time). However, please be aware that the electric charge may not be pulled out when the duration of dead band time is short and the filter constant is not appropriate.

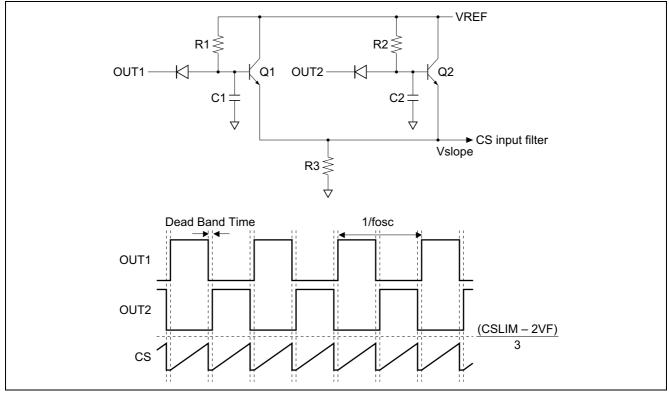

# 9. Usage on Half-bridge Power Supply

The HA16150 is operated in the current mode. However, the half-bridge power supply becomes unstable in principle by using current mode control. The HA16150, therefore, cannot be used basically. In order to use the HA16150 with the half-bridge power supply, add a circuit as shown below and operate the HA16150 in the voltage mode.

Figure 10 Example of Circuit for Voltage Mode Operation

Design the charging circuits for R1 (R2), C1 (C2), Q1 (Q2) and R3 so that the peak voltage of CS is lower than (CSLIM-2VF)/3 at the maximum ON pulse width of OUT1 and OUT2.

Furthermore, set the input filter values between R3 and CS pin so that the CS voltage is discharged assuredly while both of the OUT1 and OUT2 are at low level.

# **Characteristic Curves**

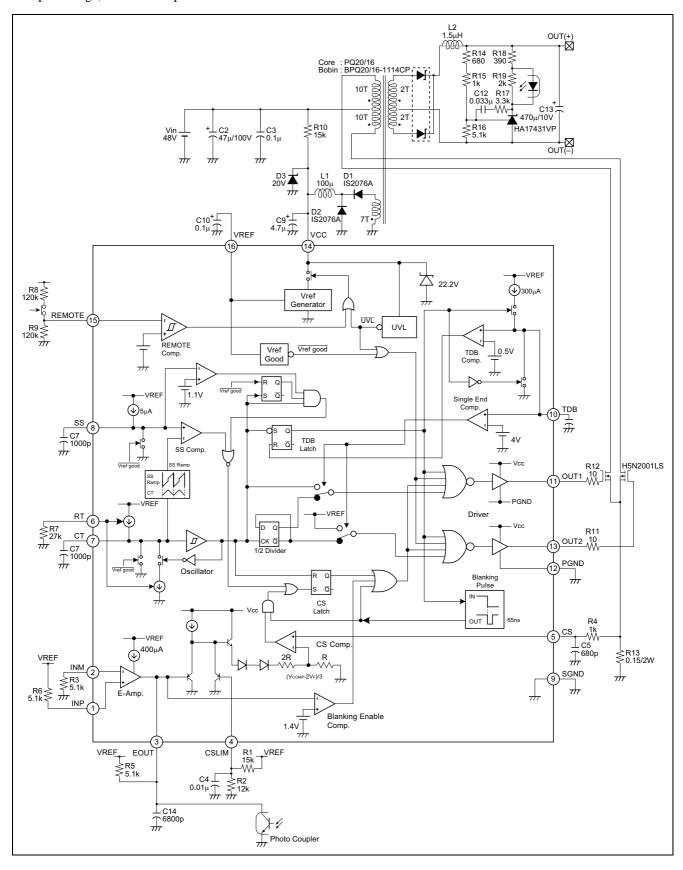

# **Application Circuit Example**

The following diagram shows a sample application circuit for a push-pull converter with a 48~V input voltage, 3.3~V output voltage, and 10~A output current.

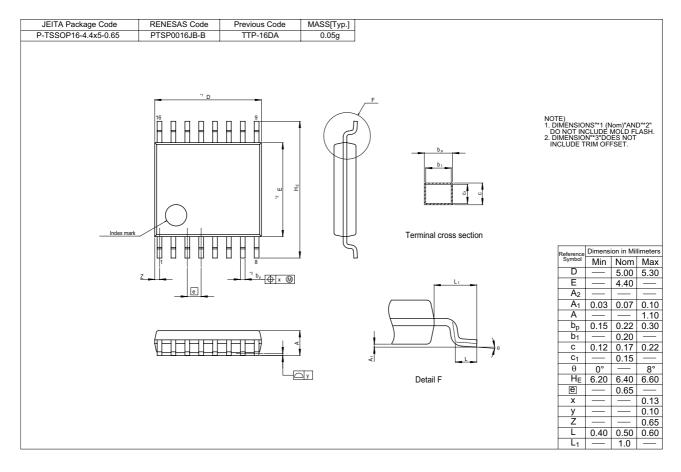

# **Package Dimensions**

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property rights or any other rights of Renesas or shy third party with respect to the information in this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, but not limited to, product data, diagrams, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass and regulations, and procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations, and procedures are such as a result of errors or omissions in the information with a Renesas sales office of the date of

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

RENESAS SALES OFFICES

**Renesas Technology America, Inc.** 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com