# **RNA51xx Series**

## CMOS system-RESET IC

REJ03D0505-0300 Rev.3.00 Oct 10, 2008

### **General Description**

The RNA51xx series provide system reset signal for microprocessor and electrical systems.

Threshold voltage is 1.4 V, 2.6 V, 2.7 V, 2.8 V, 2.9 V, 3.0 V, 3.1 V, 4.4 V, 4.5 V, 4.6 V, 5.0 V and accuracy is ±1.0%.

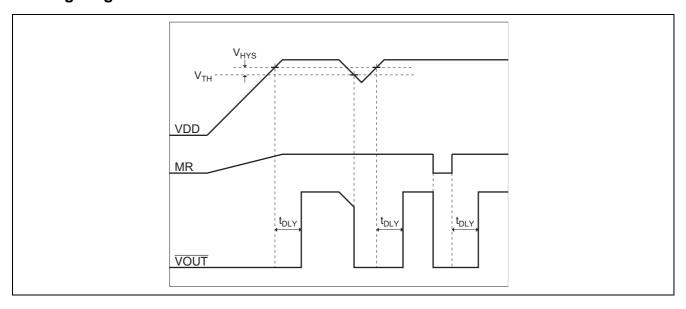

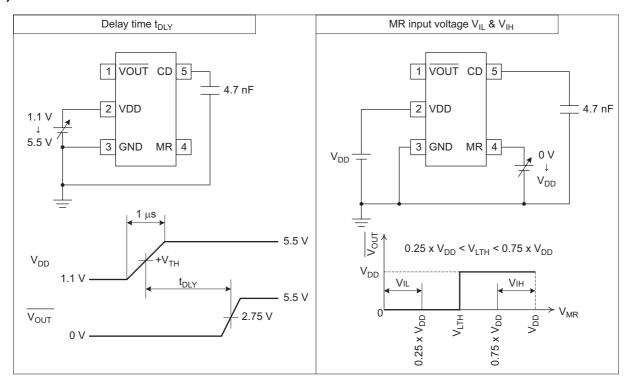

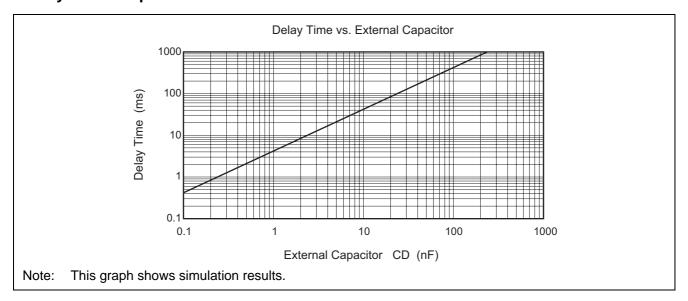

The reset output delay time can be set by external capacitor connected to CD pin.

Manual reset input is available and input resistance is 2 M $\Omega$  typ.

This series have two output types (active-low CMOS output and active-low open-drain output).

#### **Features**

Threshold voltage: 1.4 V, 2.6 V, 2.7 V, 2.8 V, 2.9 V, 3.0 V, 3.1 V, 4.4 V, 4.5 V, 4.6 V, 5.0 V

Threshold voltage accuracy: ±1.0%

Threshold voltage hysteresis: 5% typ.

• Low supply current: 0.7 μA typ.

• Capacitor-adjustable output delay time

· Manual reset

• VOUT CMOS output, or open-drain output

• 5-pin SOT-23 package

• Temperature range: -40°C to 85°C

• Ordering Information

| Part Name     | Package Type | Package Code | Package<br>Abbreviation | Taping Abbreviation (Quantity) |

|---------------|--------------|--------------|-------------------------|--------------------------------|

| RNA51A26FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A27FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A28FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A29FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A30FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A31FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A44FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A45FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51A46FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51B14FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51B27FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

| RNA51B50FLPEL | MPAK-5pin    | PLSP0005ZB-A | LP                      | EL (3,000pcs/Reel)             |

### **Applications**

- Power supply voltage monitoring for microprocessors

- Battery-powered portable equipment

- Computers and notebook computers

- Wireless Communication Systems

- Digital still camera, digital video camera, PDA

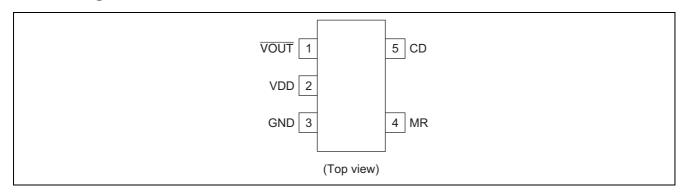

## **Pin Arrangement**

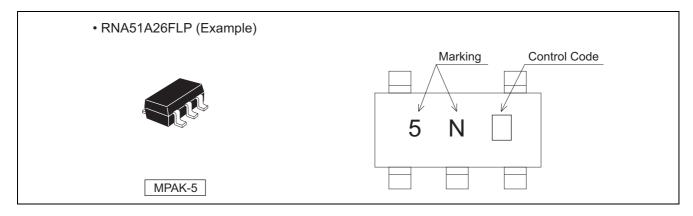

## **Product list**

| Threshold Voltage –V <sub>TH</sub> | Open-Dra         | ain output | CMOS output |         |  |

|------------------------------------|------------------|------------|-------------|---------|--|

| [V]                                | Type No. Marking |            | Type No.    | Marking |  |

| 1.4                                | _                | _          | RNA51B14FLP | 6P      |  |

| 2.6                                | RNA51A26FLP      | 5N         | _           | _       |  |

| 2.7                                | RNA51A27FLP      | 5P         | RNA51B27FLP | 7C      |  |

| 2.8                                | RNA51A28FLP      | 5Q         | _           | _       |  |

| 2.9                                | RNA51A29FLP      | 5R         | _           | _       |  |

| 3.0                                | RNA51A30FLP      | 5S         | _           | _       |  |

| 3.1                                | RNA51A31FLP      | 5T         | _           | _       |  |

| 4.4                                | RNA51A44FLP      | 6G         | _           | _       |  |

| 4.5                                | RNA51A45FLP      | 6H         | _           | _       |  |

| 4.6                                | RNA51A46FLP      | 6J         | _           | _       |  |

| 5.0                                | _                | _          | RNA51B50FLP | 3R      |  |

## **Outline and Article Indication**

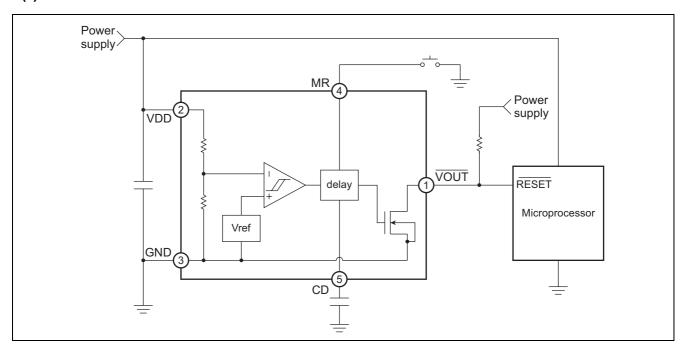

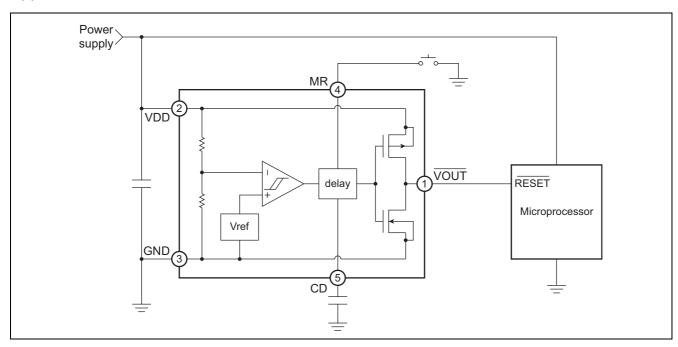

## Functional block diagram & typical application circuit

### (1) RNA51Axx Products

#### (2) RNA51Bxx Products

Notes: 1. It is good for stable operation to use a decoupling capacitor with excellent high frequency characteristics between VDD and GND pin.

2. Capacitor value is determined by system conditions.

## **Timing Diagram**

## **Absolute Maximum Ratings**

### (1) RNA51Axx Products

Temperature condition  $Ta = 25^{\circ}C$

|                              |                  |                                 | Tomperature t                |      |

|------------------------------|------------------|---------------------------------|------------------------------|------|

| Item                         | Symbol           | Pin                             | Ratings                      | Unit |

| Supply voltage               | $V_{DD}$         | $V_{DD}$                        | 6.0                          | V    |

| Output voltage               | V <sub>OUT</sub> | $\overline{V}_{\overline{OUT}}$ | -0.3 to 6.0                  | V    |

| Input voltage                | V <sub>IN</sub>  | MR, MD                          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current               | l <sub>оит</sub> | V <sub>OUT</sub>                | ±50                          | mA   |

| Continuous power dissipation | P <sub>D</sub>   | _                               | 120                          | mW   |

| Operating temperature range  | $T_OPR$          | _                               | -40 to +85                   | °C   |

| Storage temperature range    | T <sub>STG</sub> | _                               | -55 to +125                  | °C   |

## (2) RNA51Bxx Products

Temperature condition  $Ta = 25^{\circ}C$

| Item                         | Symbol           | Pin                             | Ratings                      | Unit |  |

|------------------------------|------------------|---------------------------------|------------------------------|------|--|

| Supply voltage               | $V_{DD}$         | $V_{DD}$                        | 6.0                          | V    |  |

| Output voltage               | V <sub>OUT</sub> | $\overline{V}_{\overline{OUT}}$ | -0.3 to V <sub>DD</sub> +0.3 | V    |  |

| Input voltage                | V <sub>IN</sub>  | MR, MD                          | -0.3 to V <sub>DD</sub> +0.3 | V    |  |

| Output current               | I <sub>OUT</sub> | V <sub>OUT</sub>                | ±50                          | mA   |  |

| Continuous power dissipation | P <sub>D</sub>   | _                               | 120                          | mW   |  |

| Operating temperature range  | T <sub>OPR</sub> | _                               | -40 to +85                   | °C   |  |

| Storage temperature range    | T <sub>STG</sub> | _                               | -55 to +125                  | °C   |  |

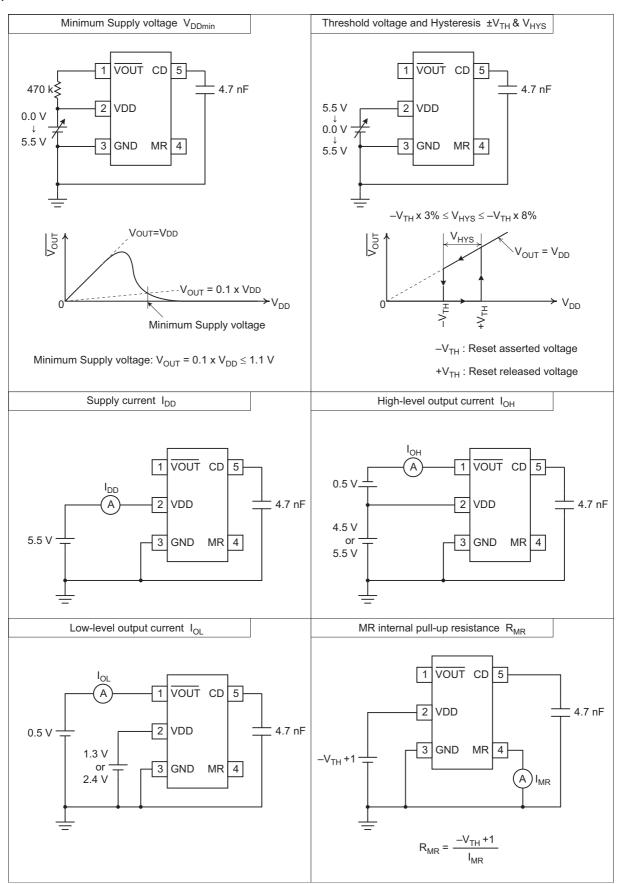

### **Electrical characteristics**

#### (1) RNA51Axx Products

Temperature condition  $Ta = 25^{\circ}C$

| Item                                                                 | Symbol                                             | Min                    | Тур                  | Max                    | Unit       | Conditions                                                   |  |

|----------------------------------------------------------------------|----------------------------------------------------|------------------------|----------------------|------------------------|------------|--------------------------------------------------------------|--|

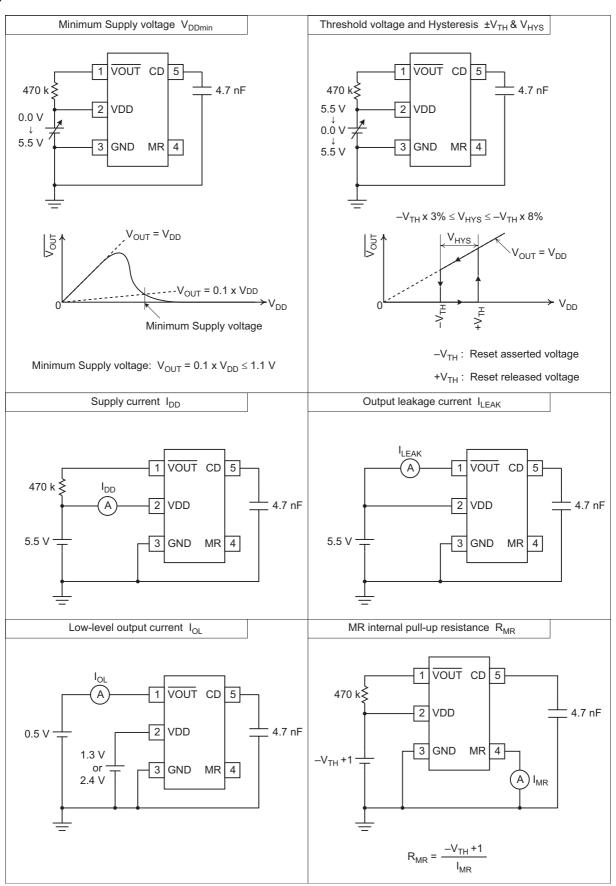

| Supply voltage                                                       | $V_{DD}$                                           | 1.1                    | _                    | 5.5                    | V          | pull-up resistor = 470 kΩ $V_{OUT} \le 0.1 \times VDD$       |  |

| Supply current                                                       | I <sub>DD</sub>                                    | _                      | 0.7                  | 4.2                    | μΑ         | V <sub>DD</sub> = 5.5 V                                      |  |

| Threshold voltage                                                    | -V <sub>TH</sub>                                   | -V <sub>TH</sub> ×0.99 | _                    | −V <sub>TH</sub> ×1.01 | V          |                                                              |  |

| Temperature coefficiency of the thereshold voltage (Reference value) | <u>∆(−V<sub>тн</sub>)</u><br>−V <sub>тн</sub> ·∆Та | _                      | ±100                 | _                      | ppm/<br>°C | Ta = -40 to 85°C                                             |  |

| Threshold voltage hysteresis                                         | V <sub>HYS</sub>                                   | -V <sub>TH</sub> ×3%   | –V <sub>TH</sub> ×5% | -V <sub>TH</sub> ×8%   | V          |                                                              |  |

| VOUT low-level output current                                        | I <sub>OL</sub>                                    | 0.2                    | 1.2                  | _                      | mA         | $V_{OUT} = 0.5 \text{ V}$ $V_{DD} = 1.3 \text{ V}$           |  |

| ·                                                                    |                                                    | 3.4                    | 7.0                  | _                      |            | $V_{DD} = 2.4 \text{ V}$<br>$(-V_{TH} \ge 2.7 \text{ V})$    |  |

| VOUT Output leakage current (open drain output)                      | I <sub>LEAK</sub>                                  | _                      | _                    | 0.1                    | μА         | $V_{DD} = V_{OUT} = 5.5 \text{ V}$                           |  |

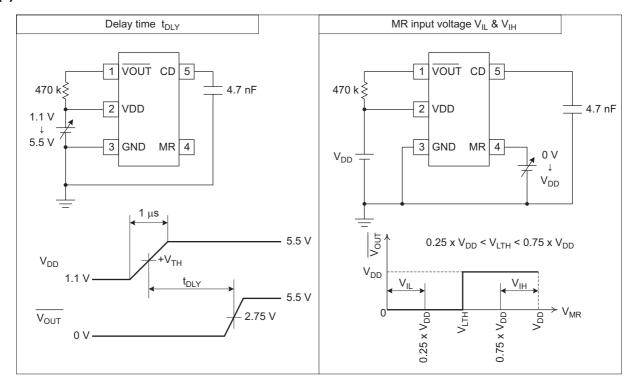

| Delay time Note1                                                     | t <sub>DLY</sub>                                   | 10                     | 20                   | 35                     | ms         | $V_{DD}$ = 1.1 to 5.5V, $t_{TLH}$ = 1 $\mu s$ $C_D$ = 4.7 nF |  |

| MR Low-level input voltage Note2                                     | V <sub>IL</sub>                                    | _                      | _                    | V <sub>DD</sub> ×0.25  | V          |                                                              |  |

| MR High-level input voltage                                          | V <sub>IH</sub>                                    | V <sub>DD</sub> ×0.75  | _                    | _                      | V          |                                                              |  |

| MR internal pull-up resistance                                       | R <sub>MR</sub>                                    | 1                      | 2                    | 7                      | МΩ         |                                                              |  |

#### (2) RNA51Bxx Products

#### Temperature condition $Ta = 25^{\circ}C$

| Item                                                                        | Symbol                                             | Min                    | Тур                  | Max                    | Unit       | Conditions                                                         |                                                           |

|-----------------------------------------------------------------------------|----------------------------------------------------|------------------------|----------------------|------------------------|------------|--------------------------------------------------------------------|-----------------------------------------------------------|

| Supply voltage                                                              | V <sub>DD</sub>                                    | 1.1                    | _                    | 5.5                    | V          | pull-up resistor = 470 kΩ $V_{OUT} \le 0.1 \times VDD$             |                                                           |

| Supply current                                                              | I <sub>DD</sub>                                    | _                      | 0.7                  | 4.2                    | μΑ         | $V_{DD} = 5.5 \text{ V}$                                           |                                                           |

| Threshold voltage                                                           | -V <sub>TH</sub>                                   | -V <sub>TH</sub> ×0.99 | _                    | −V <sub>TH</sub> ×1.01 | V          |                                                                    |                                                           |

| Threshold voltage<br>temperature dependency<br>(Reference value for design) | <u>∆(−V<sub>тн</sub>)</u><br>−V <sub>тн</sub> ·∆Та | _                      | ±100                 | _                      | ppm/<br>°C | Ta = -40 to 85°C                                                   |                                                           |

| Threshold voltage hysteresis                                                | V <sub>HYS</sub>                                   | -V <sub>TH</sub> ×3%   | -V <sub>TH</sub> ×5% | -V <sub>TH</sub> ×8%   | V          |                                                                    |                                                           |

| VOUT low-level output current                                               | I <sub>OL</sub>                                    | 0.2                    | 1.2                  | _                      | mA         | $V_{OUT} = 0.5 \text{ V}$                                          | $V_{DD} = 1.3 \text{ V}$                                  |

|                                                                             |                                                    | 3.4                    | 7.0                  | _                      |            |                                                                    | $V_{DD} = 2.4 \text{ V}$<br>$(-V_{TH} \ge 2.7 \text{ V})$ |

| VOUT High-level output current (CMOS output)                                | I <sub>OH</sub>                                    | -1.4                   | -2.7                 | _                      | mA         | $V_{OUT} = V_{DD} - 0.5 V$                                         | $V_{DD} = 4.5 \text{ V}$<br>$(-V_{TH} \le 4.0 \text{ V})$ |

| `                                                                           |                                                    | -1.5                   | -3.0                 | _                      |            |                                                                    | $V_{DD} = 5.5 \text{ V}$                                  |

| Delay time Note1                                                            | t <sub>DLY</sub>                                   | 10                     | 20                   | 35                     | ms         | $V_{DD} = 1.1 \text{ to } 5.5 \text{ V}, t_{TLH} = 1 \mu \text{s}$ |                                                           |

| Nuc                                                                         |                                                    |                        |                      |                        |            | $C_D = 4.7 \text{ nF}$                                             |                                                           |

| MR Low-level input voltage Note2                                            | V <sub>IL</sub>                                    | _                      | _                    | $V_{DD} \times 0.25$   | V          |                                                                    |                                                           |

| MR High-level input voltage                                                 | V <sub>IH</sub>                                    | $V_{DD} \times 0.75$   | _                    | _                      | V          |                                                                    |                                                           |

| MR internal pull-up resistance                                              | R <sub>MR</sub>                                    | 1                      | 2                    | 7                      | $M\Omega$  |                                                                    |                                                           |

Note:

- 1. Delay time is specified when charging starts in the condition that CD pin is completely discharged. When discharging of CD pin is not complete because of immediate stop and other reasons, the delay time is not guaranteed. Therefore, when passing of VDD pin input voltage immediately stops (the period of condition that VDD pin input voltage is lower than the detected voltage is short), discharging of external capacitor CD is inadequate, and the delay time becomes much shorter than the minimum guaranteed value. Be sure to fully check that there are no problems as the system.

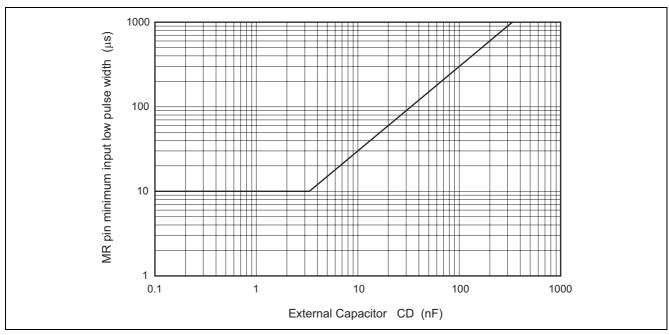

- 2. Minimum value of low-pulse width to be input to MR pin depends on the value of external capacitor CD. Therefore, set the low-pulse width to be input to MR pin to the minimum input low-pulse width shown in figure 1 or more.

Figure 1 Dependence of MR pin minimum input low pulse width and external capacitor CD

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                 |

|-----|------|----------------------------------------------------------------------------------------------------------|

| 1   | VOUT | VOUT changes from high to low whenever VDD drops below –V <sub>TH</sub> .                                |

|     |      | A pull-up resistor from 470 k $\Omega$ to 1 M $\Omega$ should be used on this pin for open-drain output. |

| 2   | VDD  | Supply voltage and input for voltage detector.                                                           |

|     |      | A decoupling capacitor with excellent high frequency characteristics should be placed near VDD           |

|     |      | pin and connected between VDD and GND pin.                                                               |

| 3   | GND  | Ground                                                                                                   |

| 4   | MR   | Active-low Manual Reset Input. VOUT is low-level while MR is low.                                        |

|     |      | Once MR is disabling, VOUT turn to high-level after delay time.                                          |

|     |      | MR pin is internally pulled up to VDD through 2 M $\Omega$ .                                             |

| 5   | CD   | Connect capacitor between CD and GND pin to set programmable delay time.                                 |

|     |      | Ceramic capacitor from 100 pF to 0.1 µF is recommended.                                                  |

### **Test Circuit**

#### (1) RNA51Axx Products

## **Test Circuit (Cont.)**

## (1) RNA51Axx Products

## **Test Circuit (Cont.)**

### (2) RNA51Bxx Products

## **Test Circuit (Cont.)**

## (2) RNA51Bxx Products

## **Delay Time Graph**

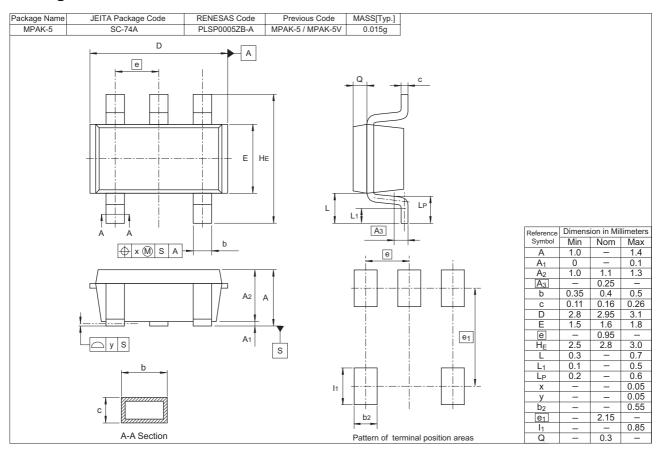

## **Package Dimensions**

#### Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the such procedure in the procedure of the development of the development of the development of the procedure of the development of the de

### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510