# Agilent HMMC-3102 DC - 16 GHz Packaged Divide-by-2 Prescaler

HMMC-3102-TR1 - 7" diameter reel/500 each HMMC-3102-BLK - Bubble strip/10 each Data Sheet

Package Type: 8-lead SSOP Plastic

Package Dimensions: 4.9 × 3.9 mm Typ.

Package Thickness: 1.55 mm Typ.

Lead Pitch: 1.25 mm Nom.

Lead Width: 0.42 mm Nom.

#### **Features**

- Wide Frequency Range: 0.2–16 GHz

- High Input Power

Sensitivity:

On-chip pre- and post-amps

-20 to +10 dBm (1–10 GHz)

-15 to +10 dBm (10–12 GHz)

-10 to +5 dBm (12–15 GHz)

- P<sub>out</sub>: +6 dBm (0.99 V<sub>p-p</sub>) will drive ECL

- Low Phase Noise:

-153 dBc/Hz @ 100 kHz Offset

- (+) or (-) Single Supply Bias with wide range: 4.5 to 6.5 V

- Differential I/0 with on-chip  $50\Omega$  matching

## Absolute Maximum Ratings<sup>[1]</sup>

(@ T<sub>A</sub>=25°C, unless otherwise indicated)

### Description

The HMMC-3102 is a packaged GaAs HBT MMIC prescaler which offers DC to 16 GHz frequency translation for use in communications and EW systems incorporating high-frequency PLL oscillator circuits and signal-path down conversion applications. The prescaler provides a large input power sensitivity window and low phase noise.

| Symbol                               | Parameters/Conditions                                                       | Min.                 | Max.                 | Units |

|--------------------------------------|-----------------------------------------------------------------------------|----------------------|----------------------|-------|

| V <sub>CC</sub>                      | Bias Supply Voltage                                                         |                      | +7                   | volts |

| V <sub>EE</sub>                      | Bias Supply Voltage                                                         | -7                   |                      | volts |

| V <sub>CC</sub> -<br>V <sub>EE</sub> | Bias Supply Delta                                                           |                      | +7                   | volts |

| $V_{Logic}$                          | Logic Threshold Voltage                                                     | V <sub>CC</sub> -1.5 | V <sub>CC</sub> -1.2 | volts |

| P <sub>in(CW)</sub>                  | CW RF Input Power                                                           |                      | +10                  | dBm   |

| V <sub>RFin</sub>                    | DC Input V <u>olt</u> age<br>(@ RF <sub>in</sub> or RF <sub>in</sub> Ports) |                      | $V_{CC} \pm 0.5$     | volts |

| T <sub>BS</sub> <sup>[2]</sup>       | Backside Operating Temp.                                                    | -40                  | +85                  | °C    |

| T <sub>st</sub>                      | Storage Temperature                                                         | -65                  | +165                 | °C    |

| T <sub>max</sub>                     | Maximum Assembly Temp.<br>(60 seconds max.)                                 |                      | 310                  | °C    |

<sup>[1]</sup>Operation in excess of any parameter limit (except T<sub>BS</sub>) may cause permanent damage to the device.

$<sup>^{[2]}</sup>$ MTTF >5×10<sup>5</sup> hours @ T\_BS <85°C. Operation in excess of maximum operating temperature (T\_BS) will degrade MTTF.

DC Specifications/Physical Properties ( $T_A = 25^{\circ}\text{C}$ ,  $V_{CC}$  -  $V_{EE} = 5.0$  volts, unless otherwise listed)

| Symbol                                | Parameters/Conditions                                                                     | Min.                   | Тур.                  | Max.                  | Units |

|---------------------------------------|-------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|-------|

| V <sub>CC</sub> - V <sub>EE</sub>     | Operating bias supply difference <sup>[1]</sup>                                           | 4.5                    | 5.0                   | 6.5                   | volts |

| I <sub>CC</sub>   or  I <sub>EE</sub> | Bias supply current                                                                       | 68                     | 80                    | 92                    | mA    |

| $V_{RFin(q)}$<br>$V_{RFout(q)}$       | Quiescent DC voltage appearing at all RF ports                                            |                        | $V_{CC}$              |                       | volts |

| $V_{Logic}$                           | Nominal ECL Logic Level (V <sub>Logic</sub> contact self-bias voltage, generated on-chip) | V <sub>CC</sub> - 1.45 | V <sub>CC</sub> -1.35 | V <sub>CC</sub> -1.25 | volts |

<sup>[1]</sup> Prescaler will operate over full specified supply voltage range. V<sub>CC</sub> or V<sub>EE</sub> not to exceed limits specified in Absolute Maximum Ratings

#### **RF Specifications**

$(T_A = 25^{\circ}C, Z_0 = 50\Omega, V_{CC} - V_{EE} = 5.0 \text{ volts})$

| Symbol                           | Parameters/Conditions                                                                                                                                                                | Min. | Тур. | Max. | Units  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| $f_{in(max)}$                    | Maximum input frequency of operation                                                                                                                                                 | 16   | 18   |      | GHz    |

| $f_{in(min)}$                    | Minimum input frequency of operation <sup>[1]</sup> (P <sub>in</sub> = -10 dBm)                                                                                                      |      | 0.2  | 0.5  | GHz    |

| $f_{Self	ext{-}Osc.}$            | Output Self-Oscillation Frequency <sup>[2]</sup>                                                                                                                                     |      | 3.4  |      | GHz    |

|                                  | @ DC, (Square-wave input)                                                                                                                                                            | -15  | >-25 | +10  | dBm    |

|                                  | @ $f_{in}$ = 500 MHz, (Sine-wave input)                                                                                                                                              | -15  | >-20 | +10  | dBm    |

| P <sub>in</sub>                  | $f_{\text{in}}$ = 1 to 10 GHz                                                                                                                                                        | -15  | >-25 | +10  | dBm    |

|                                  | f <sub>in</sub> = 10 to 12 GHz                                                                                                                                                       | -10  | >-15 | +10  | dBm    |

|                                  | f <sub>in</sub> = 12 to 15 GHz                                                                                                                                                       | -4   | >-10 | +4   | dBm    |

| RL                               | Small-Signal Input/Output Return Loss<br>(@f <sub>in</sub> < 12 GHz)                                                                                                                 |      | 15   |      | dB     |

| S <sub>12</sub>                  | Small-Signal Reverse Isolation ( $@f_{in}$ < 12 GHz)                                                                                                                                 |      | 30   |      | dB     |

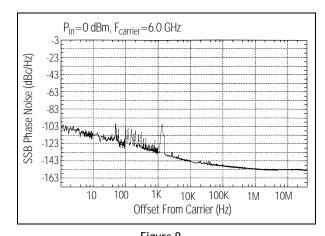

| $\phi_{ m N}$                    | SSB Phase noise (@ $P_{in}$ = 0 dBm, 100kHz offset from a $f_{out}$ = 1.2 GHz Carrier)                                                                                               |      | -153 |      | dBc/Hz |

| Jitter                           | Input signal time variation @ zero-crossing $(f_{in} = 10 \text{ GHz}, P_{in} = -10 \text{ dBm})$                                                                                    |      | 1    |      | ps     |

| T <sub>r</sub> or T <sub>f</sub> | Output transition time (10% to 90% rise/fall time)                                                                                                                                   |      | 70   |      | ps     |

|                                  | @ $f_{\text{out}} < 1 \text{ GHz}$                                                                                                                                                   | 4    | 6    |      | dBm    |

| P <sub>out</sub> <sup>[3]</sup>  | @ $f_{\text{out}}$ = 2.5 GHz                                                                                                                                                         | 3.5  | 5.5  |      | dBm    |

|                                  | @ $f_{\text{out}} = 3.5 \text{ GHz}$                                                                                                                                                 | 0    | 2.0  |      | dBm    |

|                                  | @ $f_{\text{out}}$ <1 GHz                                                                                                                                                            |      | 0.99 |      | volts  |

| $ V_{out(p-p)} ^{[4]}$           | @ $f_{\text{out}}$ = 2.5 GHz                                                                                                                                                         |      | 0.94 |      | volts  |

|                                  | @ $f_{\text{out}} = 3.5 \text{ GHz}$                                                                                                                                                 |      | 0.63 |      | volts  |

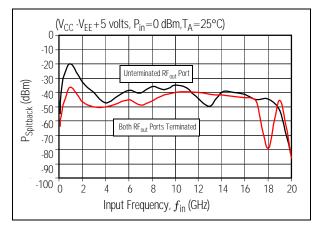

| P <sub>Spitback</sub>            | $f_{ m out}$ power level appearing at RF $_{ m in}$ or $\overline{ m RF}_{ m in}$ (@ $f_{ m in}$ 12 GHz, Unused RF $_{ m out}$ or $\overline{ m RF}_{ m out}$ unterminated)          |      | -40  |      | dBm    |

|                                  | $f_{ m out}$ power level appearing at ${ m RF}_{ m in}$ or ${ m \overline{RF}}_{ m in}$ (@ $f_{ m in}$ = 12 GHz, Both ${ m RF}_{ m out}$ & ${ m \overline{RF}}_{ m out}$ terminated) |      | -47  |      | dBm    |

| P <sub>feedthru</sub>            | Power level of $f_{in}$ appearing at RF <sub>out</sub> or $\overline{\text{RF}}_{out}$ (@ $f_{in}$ = 12 GHz, P <sub>in</sub> = 0 dBm, Referred to P <sub>in</sub> ( $f_{in}$ ))      |      | -23  |      | dBc    |

| H <sub>2</sub>                   | Second harmonic distortion output level (@ $f_{out}$ = 3.0 GHz, Referred to $P_{out}(f_{out})$ )                                                                                     |      | -25  |      | dBc    |

<sup>[1]</sup> For sine-wave input signal. Prescaler will operate down to D.C. for square-wave input signal. Minimum divide frequency limited by input

6-54 HMMC-3102/rev.3.3

<sup>[2]</sup> Prescaler can exhibit this output signal under bias in the absence of an RF input signal. This condition can be eliminated by use of the Input DC offset technique described on page 3.

[3] Fundamental of output square wave's Fourier Series.

$<sup>^{[4]}</sup>$ Square wave amplitude calculated from  $P_{out}$ .

#### **Applications**

The HMMC-3102 is designed for use in high frequency communications, microwave instrumentation, and EW radar systems where low phase-noise PLL control circuitry or broad-band frequency translation is required.

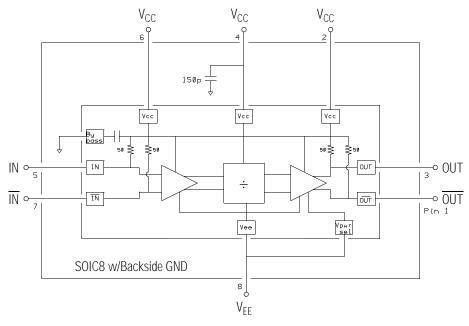

#### Operation

The device is designed to operate when driven with either a single-ended or differential sinusoidal input signal over a 200 MHz to 16 GHz bandwidth. Below 200 MHz the prescaler input is "slew-rate" limited, requiring fast rising and falling edge speeds to properly divide. The device will operate at frequencies down to DC when driven with a square-wave.

Due to the presence of an off-chip RF-bypass capacitor inside the package (connected to the  $V_{CC}$  contact on the device), and the unique design of the device itself, the component may be biased from either a single positive or single negative supply bias. The backside of the package is not DC connected to any DC bias point on the device.

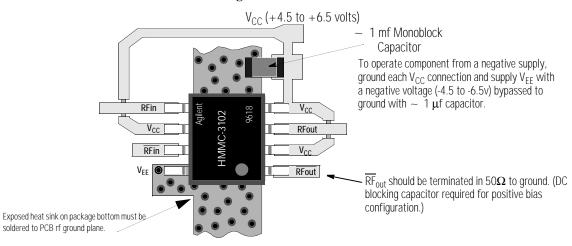

For positive supply operation,  $V_{CC}$  pins are nominally biased at any voltage in the +4.5 to +6.5 volt range with pin 8 ( $V_{EE}$ ) grounded. For negative bias operation  $V_{CC}$  pins are typically grounded and a negative voltage between -4.5 to -6.5 volts is applied to pin 8 ( $V_{EE}$ ).

#### AC-Coupling and DC-Blocking

All RF ports are DC connected on-chip to the V<sub>CC</sub> contact through on-chip  $50\Omega$  resistors. Under any bias conditions where VCC is not DC grounded the RF ports should be AC coupled via series capacitors mounted on the PC-board at each RF port. Only under bias conditions where V<sub>CC</sub> is DC grounded (as is typical for negative bias supply operation) may the RF ports be direct coupled to adjacent circuitry or in some cases, such as level shifting to subsequent stages. In the latter case the package heat sink may be "floated" and bias applied as the difference between V<sub>CC</sub> and  $V_{EE}$ .

#### **Input DC Offset**

If an RF signal with sufficient sig-

nal to noise ratio is present at the RF input lead, the prescaler will operate and provide a divided output equal the input frequency divided by the divide modulus. Under certain "ideal" conditions where the input is well matched at the right input frequency, the component may "self-oscillate", especially under small signal input powers or with only noise present at the input This "self-oscillation" will produce a undesired output signal also known as a false trigger. To prevent false triggers or self-oscillation conditions, apply a 20 to 100 mV DC offset voltage between the RF<sub>in</sub> and RF<sub>in</sub> ports. This prevents noise or spurious low level signals from triggering the divider.

Adding a  $10 \text{K}\Omega$  resistor between the unused RF input to a contact point at the V<sub>EE</sub> potential will result in an offset of  $\approx 25 \text{mV}$  between the RF inputs. Note however, that the input sensitivity will be reduced slightly due to the presence of this offset.

#### Assembly Notes

Independent of the bias applied to the package, the backside of

Figure 1. Simplified Schematic

HMMC-3102/rev.3.3 6-55

the package should always be connected to both a good RF ground plane and a good thermal heat sinking region on the PC-board to optimize performance. For single-ended output operation the unused RF output lead should be terminated into  $50\Omega$  to a contact point at the  $V_{CC}$  potential or to RF ground through a DC blocking capacitor.

A minimum RF and thermal PC

board contact area equal to or greater than 2.67 x 1.65 mm (0.105" x 0.065") with eight 0.020" diameter plated-wall thermal vias is recommended.

.GaAs MMICs are ESD sensitive. ESD preventive measures must be employed in all aspects of storage, handling, and assembly.

MMIC ESD precautions, handling considerations, die attach and bonding methods are critical fac-

tors in successful GaAs MMIC performance and reliability.

Agilent application note #54, "GaAs MMIC ESD, Die Attach and Bonding Guidelines" provides basic information on these subjects.

#### Additional References:

PN #18, "HBT Prescaler Evaluation Board."

#### Notes:

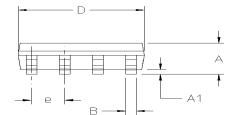

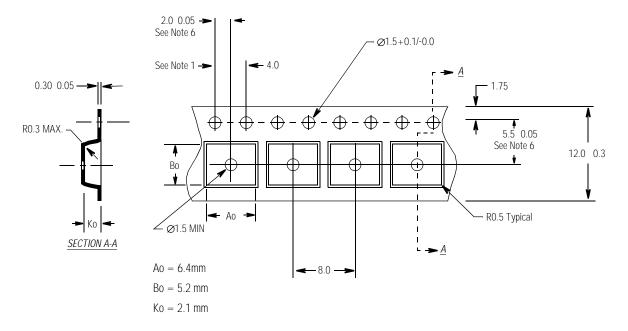

- All dimensions in millimeters.

- Refer to JEDEC Outline MS-012 for additional tolerances

| SYMBOL | MIN.     | MAX. |  |

|--------|----------|------|--|

| А      | 1.35     | 1.75 |  |

| A1     | 0.0      | .25  |  |

| В      | 0.33     | 0.51 |  |

| С      | 0.19     | .025 |  |

| D      | 4.80     | 5.00 |  |

| E      | 3.80     | 4.00 |  |

| е      | 1.27 BSC |      |  |

| Н      | 5.80     | 6.20 |  |

| L      | 0.40     | 1.27 |  |

| а      | 0°       | 8°   |  |

- Exposed heat slug area on pkg bottom = 2.67 × 1.65.

- Exposed heat sink on package bottom must be soldered to PCB rf ground plane.

Figure 2. **Package & Dimensions**

Figure 3.

Assembly Diagram

(Single-Supply, positive-bias configuration shown)

6-56 HMMC-3102/rev.3.3

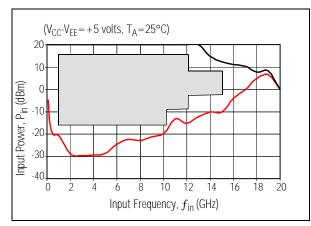

#### Supplemental Data:

Figure 4.

Typical Input Sensitivity Window

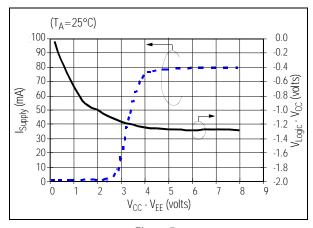

Figure 5.

Typical Supply Current & V<sub>Logic</sub>

vs. Supply Voltage

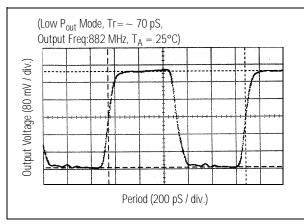

Figure 6.

Typical Output Voltage Waveform

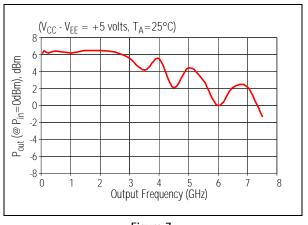

Figure 7. Typical Output Power vs. Output Frequency,  $f_{\rm out}$  (GHz)

Figure 8.

Typical Phase Noise Performance

Figure 9. Typical HMMC-3102 *"Spitback"* Power

HMMC-3102/rev.3.3 6-57

#### **Device Orientation**

#### **Tape Dimensions and Product Orientation**

#### Notes:

- 1. 10 sprocket hole pitch cumulative tolerance: 0.2mm.

- 2. Camber not to exceed 1mm in 100mm.

- 3. Material: Black Conductive Advantek Polystyrene.

- 4. Ao and Bo measured on a plane 0.3mm above the bottom of the pocket.

- 5. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier.

- 6. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.

This data sheet contains a variety of typical and guaranteed performance data. The information supplied should not be interpreted as a complete list of circuit specifications. In this data sheet the term *typical* refers to the 50th percentile performance. For additional information contact your local Agilent Technologies sales representative.

6-58 HMMC-3102/rev.3.3