### Toshiba BiCD Integrated Circuit Silicon Monolithic

# **TB7100F**

## **Step-down DC-DC Converter IC**

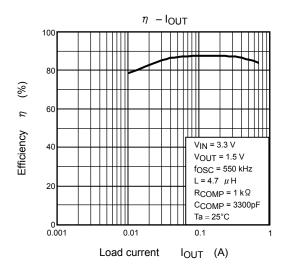

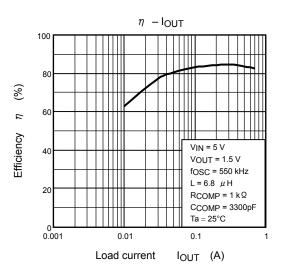

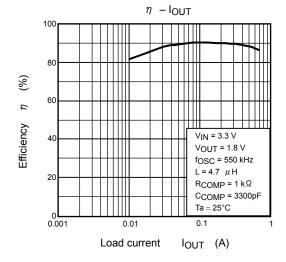

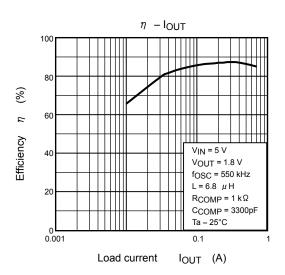

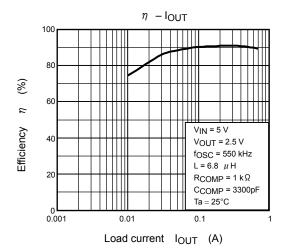

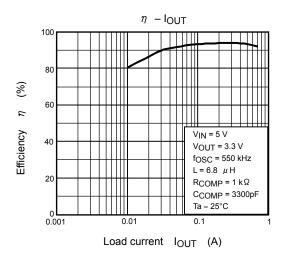

The TB7100F is a single-chip step-down DC-DC converter IC. Equipped with a built-in high-speed and low on-resistance power MOSFET, and utilizing a chopper circuit, this IC can achieve a high efficiency in a wide load current range.

### **Features**

- Capable of high current drive (I<sub>OUT</sub> = maximum of 700 mA), using only a few external components

- High efficiency ( $\eta$  = 90% or higher) (@V<sub>IN</sub> = 5V, V<sub>OUT</sub> = 3.3V, and I<sub>OUT</sub> = 300 mA).

- Operating voltage (V<sub>IN</sub>) range: 3 to 5.5 V

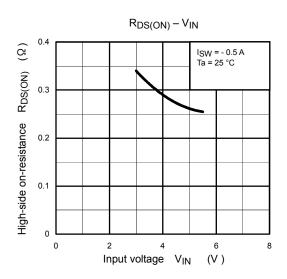

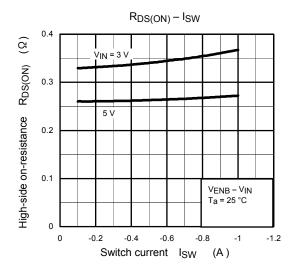

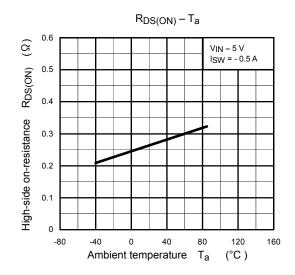

- Low on-resistance (R<sub>DS(ON)</sub>): 0.27  $\Omega$  (typ.) if V<sub>IN</sub> = 5 V

- High oscillation frequency of 550 kHz (typ.), making it possible to use small external components.

- Uses external phase compensation, assuring a high degree of design freedom in selecting external components and determining a loop response.

- Employs a current mode architecture with excellent fast load response.

- A small surface mount-type ceramic capacitor can be used as an output smoothing capacitor.

- Housed in a small surface-mount package (PS-8) with a low thermal resistance.

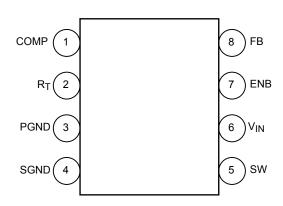

### **Pin Assignment**

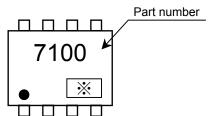

### Marking

SON8-P-0303-0.65A(PS-8)

Weight: 0.016 g (Typ.)

- •The dot (•) on the top surface indicates pin 1.

- \*: Lot number

Due to its MOS structure, this product is sensitive to electrostatic discharge. Handle with care.

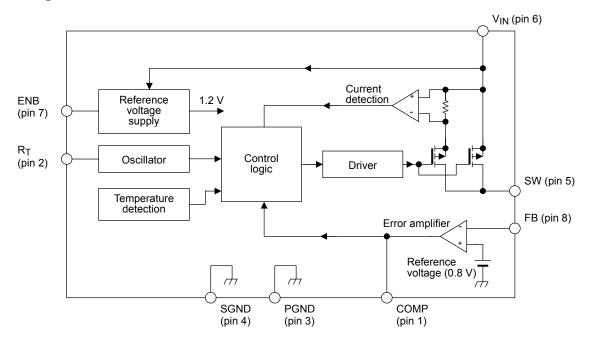

### **Block Diagram**

## **Pin Descriptions**

| Pin No. | Pin Symbol                                                                                                            | Pin Description                                                                                                                                                                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | COMP                                                                                                                  | Pin for connecting an error amplifier phase compensation resistor and capacitor.                                                                                                                                                                                       |

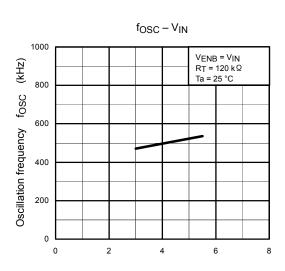

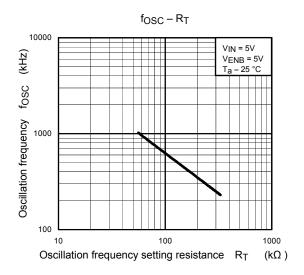

| 2       | R <sub>T</sub>                                                                                                        | Oscillation frequency setting pin for connecting a resistor to the internal oscillation circuit. Connecting 120 k $\Omega$ to this pin operates the oscillation circuit at 550 kHz (typ.).                                                                             |

| 3       | PGND                                                                                                                  | Power ground                                                                                                                                                                                                                                                           |

| 4       | SGND                                                                                                                  | Signal ground                                                                                                                                                                                                                                                          |

| 5       | SW                                                                                                                    | Switching pin. A P-channel MOSFET is connected between the V <sub>IN</sub> and SW pins.  The peak switch current corresponding to the voltage that is generated at the COMP pin flows through the power MOSFET. The rating of this peak switch current is 1.0 A (min). |

| 6       | 6 V <sub>IN</sub> Input pin. This pin is placed in the standby state if $V_{ENB}$ = low. 1 $\mu$ A or lower operation |                                                                                                                                                                                                                                                                        |

| 7       | ENB                                                                                                                   | Enable pin. This pin is connected to the CMOS inverter. Applying 3.5 V or higher (@ $V_{IN} = 5$ V) to this pin starts the internal circuit to perform switching control.                                                                                              |

| 8       | FB                                                                                                                    | Output voltage feedback pin. This is connected to the internal error amplifier, which is supplied with a reference voltage of 0.8 V (typ.).                                                                                                                            |

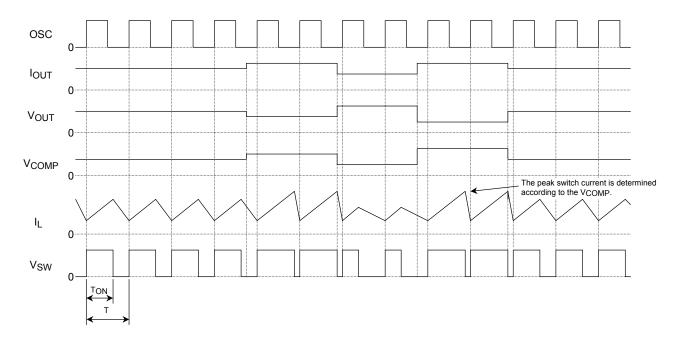

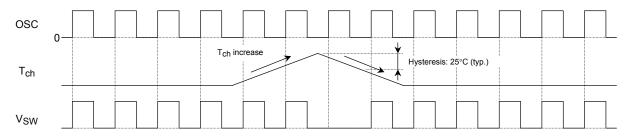

## **Timing Chart**

### Overheat state operation

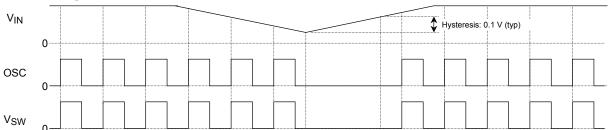

## Low Voltage operation

3

osc : Internal oscillator output voltage

Internal oscillator output

IOUT : Load current

VOUT : Output voltage

VCOMP : COMP pin voltage

IL : Inductor current

VSW : SW pin voltage

VIN : Input pin voltage

Tch : Channel temperature

# Maximum Ratings (Ta = 25°C)

| Characteristics            | Symbol                            | Rating                                 | Unit |

|----------------------------|-----------------------------------|----------------------------------------|------|

| Input voltage              | V <sub>IN</sub>                   | -0.3~6                                 | V    |

| Switch pin voltage         | V <sub>SW</sub>                   | -0.3~6                                 | V    |

| Feedback pin voltage       | V <sub>FB</sub>                   | -0.3~6                                 | V    |

| Enable pin voltage         | V <sub>ENB</sub>                  | -0.3~6                                 | V    |

| Input-enable pin voltage   | V <sub>ENB</sub> -V <sub>IN</sub> | V <sub>ENB</sub> -V <sub>IN</sub> <0.3 | V    |

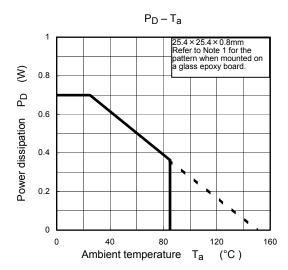

| Power dissipation (Note 1) | PD                                | 0.7                                    | W    |

| Operating temperature      | Topr                              | -40 <b>~</b> 85                        | °C   |

| Channel temperature        | T <sub>ch</sub>                   | 150                                    | °C   |

| Storage temperature        | T <sub>stg</sub>                  | -55 <b>~</b> 150                       | °C   |

## **Thermal Resistance Characteristic**

| Characteristics                         | Symbol                 | Max            | Unit  |

|-----------------------------------------|------------------------|----------------|-------|

| Thermal resistance, channel and ambient | R <sub>th (ch-a)</sub> | 178.6 (Note 1) | °C /W |

(Note 1)

Glass epoxy board

Material : FR-4 25.4 × 25.4 × 0.8 (Unit: mm)

# Electrical Characteristics (unless otherwise specified: Ta = 25 $^{\circ}$ C and V<sub>IN</sub> = 3 to 5.5 V)

| Characteristics               |                | Symbol                | Test<br>circuit | Test condition                                                                                           | Min   | Тур. | Max   | Unit |

|-------------------------------|----------------|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Operating supply voltage      |                | V <sub>IN(OPR)</sub>  | _               | -                                                                                                        | 3     | 5    | 5.5   | V    |

| Load current                  |                | lout                  | _               | _                                                                                                        | _     | _    | 700   | mA   |

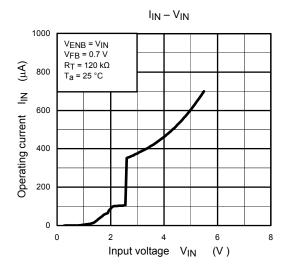

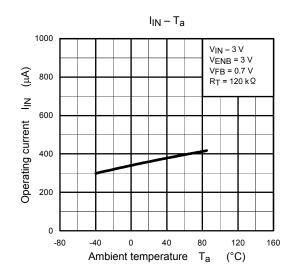

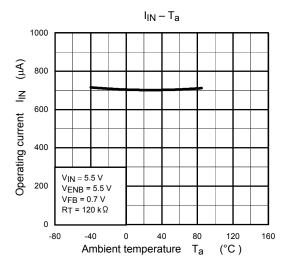

| Operating current             |                | I <sub>IN</sub>       | ı               | $V_{IN} = 5 \text{ V}, V_{ENB} = 5 \text{ V}, V_{FB} = 0.7 \text{ V}$<br>R <sub>T</sub> = 120 k $\Omega$ | ı     | 570  | 750   | μΑ   |

| Standby currer                | nt             | I <sub>IN(STBY)</sub> | 1               | V <sub>IN</sub> = 5 V, V <sub>ENB</sub> = 0 V, V <sub>FB</sub> = 0.9 V                                   | ı     | _    | 1     | μΑ   |

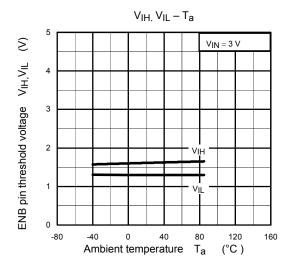

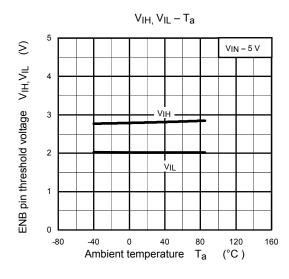

| Enable pin threshold voltage  |                | V <sub>IH</sub>       | 1               | V <sub>IN</sub> = 5 V                                                                                    | 3.5   | _    | _     | V    |

| Lilable pili tille            | siloid voitage | V <sub>IL</sub>       | ı               | V <sub>IN</sub> = 5 V                                                                                    | _     | _    | 1.5   | V    |

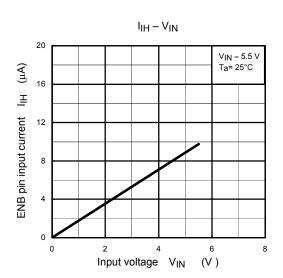

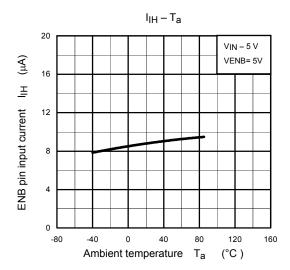

| Enable pin inpu               | ut current     | l <sub>IH</sub>       |                 | V <sub>IN</sub> = 5 V, V <sub>ENB</sub> = 5 V                                                            | _     | _    | 20    | μΑ   |

| Feedback pin current          |                | I <sub>FB</sub>       | ı               | _                                                                                                        | -1    | _    | 1     | μΑ   |

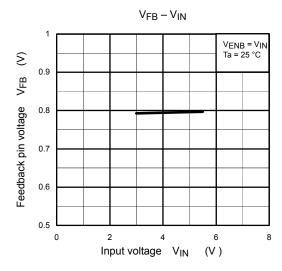

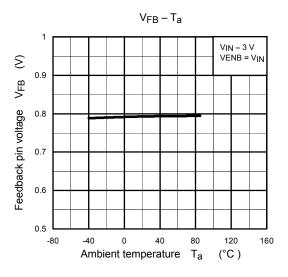

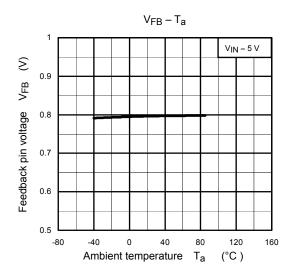

| Feedback pin voltage          |                | $V_{FB}$              | 1               | _                                                                                                        | 0.776 | 0.8  | 0.824 | V    |

| Feedback pin line regulation  |                | $\Delta V_{FB(LINE)}$ | 1               | V <sub>IN</sub> = V <sub>ENB</sub> = 3 V~5 V                                                             | _     | 1.6  | 5     | mV/V |

| High-side on-state resistance |                | R <sub>DS(ON)</sub>   | -               | V <sub>IN</sub> = 5 V, V <sub>ENB</sub> = 5 V, I <sub>SW</sub> = -0.5<br>A                               | Ι     | 0.27 | 0.6   | Ω    |

| High-side leakage current     |                | I <sub>LEAK</sub>     | ı               | V <sub>IN</sub> = 5 V, V <sub>ENB</sub> = 0 V, V <sub>SW</sub> = 0 V                                     | _     | _    | -1    | μΑ   |

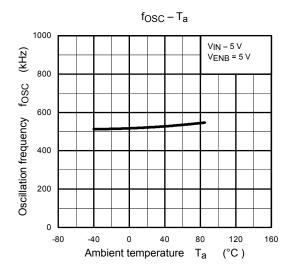

| Oscillation frequency         |                | fosc                  | -               | $V_{IN} = 5 \text{ V}, V_{ENB} = 5 \text{ V}, R_T = 120 \text{ k}$ $\Omega$                              | -     | 550  | _     | kHz  |

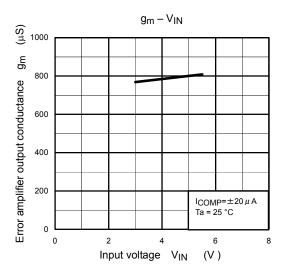

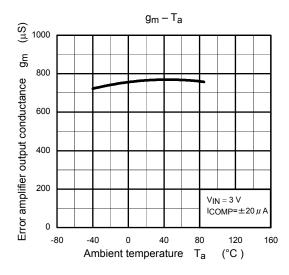

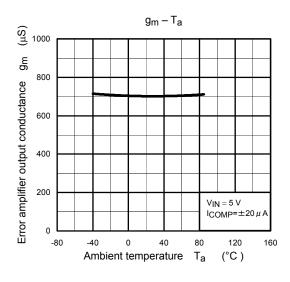

| Error amplifier conductance   |                | 9m                    | ı               | $V_{IN} = 5 \text{ V}, V_{ENB} = 5 \text{ V}$<br>$I_{COMP} = \pm 20 \mu \text{ A}$                       | ı     | 800  | _     | μS   |

| Peak switch current           |                | I <sub>SW(PEAK)</sub> | 1               | _                                                                                                        | 1.0   | 1.5  | _     | Α    |

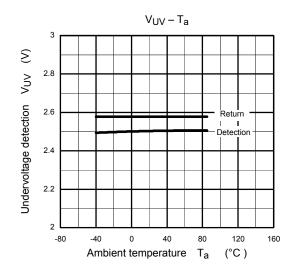

| Undervoltage                  | Detection      | V <sub>UV</sub>       | 1               | _                                                                                                        | 2.3   | 2.5  | 2.7   | V    |

| protection                    | Hysteresis     | ΔV <sub>UV</sub>      | -               | _                                                                                                        | _     | 0.1  | _     | V    |

| Overheat                      | Detection      | T <sub>SD</sub>       | _               | _                                                                                                        | 125   | 145  | _     | °C   |

| protection                    | Hysteresis     | $\Delta T_{SD}$       |                 |                                                                                                          | _     | 25   | _     | °C   |

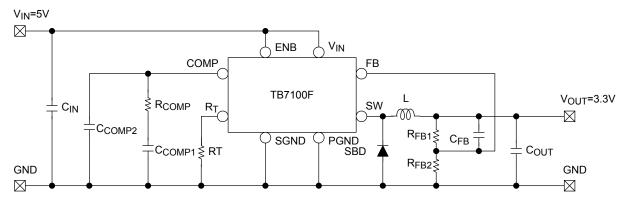

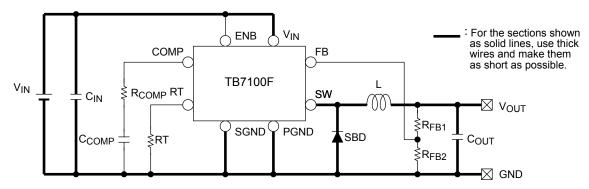

### **Application Circuit Example**

Figure 1: TB7100F application circuit example

Component constants

The following values are given only for your reference and may need tuning depending on your input/output conditions and board layout.

$C_{\text{IN}}$ : Input smoothing capacitance of 10  $\mu\text{F}$  (multilayer ceramic capacitor JMK212BJ106KG, manufactured by Taiyo Yuden Co., Ltd.)

$C_{\mbox{\scriptsize OUT}}\!\!:$  Output smoothing capacitance of 10  $\mu\mbox{\scriptsize F}$

(multilayer ceramic capacitor JMK212BJ106KG manufactured by Taiyo Yuden Co., Ltd.)

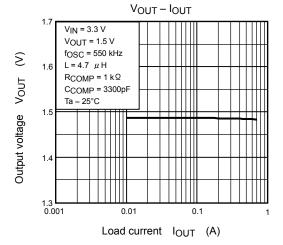

$C_{COMP1}$ : Error amplifier phase compensation capacitance of 3300 pF (@  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V, and  $R_T$  = 120 k $\Omega$ )

C<sub>COMP2</sub>: Error amplifier phase compensation capacitance (not used if phase compensation is possible only with R<sub>COMP</sub> and C<sub>COMP1</sub>)

$C_{FB}$ : Error amplifier phase compensation capacitance (not used if phase compensation is possible only with  $R_{COMP}$  and  $C_{COMP1}$ )

R<sub>COMP</sub>: Error amplifier phase compensation resistance of 1 k $\Omega$  (@ V<sub>IN</sub> = 5 V, V<sub>OUT</sub> = 3.3 V, and R<sub>T</sub> = 120 k $\Omega$ )

R<sub>T</sub>: Oscillation frequency setting resistance of 120 k $\Omega$  (@ f<sub>OSC</sub> = 550 kHz)

$R_{FB1}$ : Output voltage setting resistance of 75 k $\Omega$  (@  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V, and  $R_{T}$  = 120 k $\Omega$ )

$R_{FB2}$ : Output voltage setting resistance of 24 k $\Omega$  (@  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V, and  $R_{T}$  = 120 k $\Omega$ )

L: Inductor 6.8  $\mu$ H (@ V<sub>IN</sub> = 5 V, V<sub>OUT</sub> = 3.3 V, and R<sub>T</sub> = 120 k $\Omega$ ); CDRH4D28C/LD series, manufactured by Sumida Corporation SBD: Schottky barrier diode CRS06 (@ V<sub>RRM</sub> = 20 V and I<sub>F(AV)</sub> = 1 A), manufactured by Toshiba Corporation

### How to use

### **Setting the Inductance**

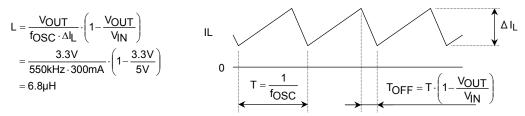

The required inductance can be calculated by using the following equation:

$$L = \frac{V_{OUT}}{f_{OSC} \cdot \Delta I_L} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \quad \cdots \quad (1)$$

$\begin{array}{ll} V_{IN}\!\!: \text{Input voltage (V)} & \text{f}_{OSC}\!\!: \text{Oscillation frequency (Hz)} \\ V_{OUT}\!\!: \text{Output voltage (V)} & \Delta \, I_L\!\!: \text{Inductor ripple current (A)} \end{array}$

\* Generally, ∆<sub>IL</sub> should be set to 30% to 40% of the peak current flowing through the inductor. For the TB7100F, set ∆I<sub>L</sub> to 0.3 A, as its peak switch current [I<sub>SW(PEAK)</sub>] is 1 A (min). Therefore select an inductor whose current rating is no lower than the peak switch current [1 A (min)] of the TB7100F. If the current rating is exceeded, the inductor becomes saturated, leading to an unstable DC-DC converter operation.

If  $V_{IN}$  = 5 V and  $V_{OUT}$  = 3.3 V, the required inductance can be calculated as below. Be sure to select an inductor with an optimum constant by taking  $V_{IN}$  variations into consideration.

Figure 2: Inductor current waveform

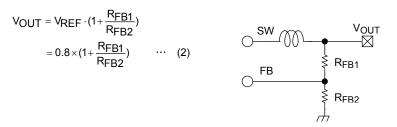

### Setting the output voltage

For the TB7100F, the output voltage is set using the voltage dividing resistors  $R_{FB1}$  and  $R_{FB2}$  according to the reference voltage [0.8 V (typ.)] of the error amplifier connected to the FB pin. If the  $R_{FB1}$  value is extremely large, a delay can occur due to a parasitic capacitance at the FB pin. Keep the  $R_{FB1}$  value within approximately 100 k $\Omega$ . The output voltage can be calculated by using equation 2 below. It is recommended that a resistor with a precision of  $\pm 1\%$  or higher be used for setting the output voltage.

Figure 3: Output voltage setting resistors

### Setting the COMP pin for phase compensation

The COMP pin is intended to compensate for any phase delay that may occur inside or outside the TB7100F. Phase compensation is carried out using resistors and capacitors connected to the COMP pin. The constants of the phase compensation components are selected by first specifying  $R_{COMP}$  and  $C_{COMP}$  to be, respectively, 1 k $\Omega$  and 3300 pF. However, it is necessary to measure the SW pin oscillation waveform and load response characteristics and tune the component constants, optimizing them so as to optimize the influence of your board layout and component characteristics. When tuning component constants, carefully evaluate them while taking component variations and temperature characteristics into consideration.

| Table 1 lists the relationships between the Discussional Constitution               | annotanta. I lan thann an a guidalina in galantina annotanta |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Table 1 lists the relationships between the R <sub>COMP</sub> and C <sub>COMP</sub> | CONSTANTS TUSE THESE AS A ODIOETHE IN SELECTION CONSTANTS    |

|                                                                                     |                                                              |

|                   |       | SW pin waveform<br>stability | Load response characteristic |

|-------------------|-------|------------------------------|------------------------------|

| R <sub>COMP</sub> | Large | Decreased                    | Increased                    |

|                   | Small | Increased                    | Decreased                    |

| ССОМР             | Large | Increased                    | Decreased                    |

|                   | Small | Decreased                    | Increased                    |

Table 1: Relationships between R<sub>COMP</sub> and C<sub>COMP</sub> values

#### **Output capacitor**

The capacitance of the output ceramic capacitor is greatly affected by temperature. Select a product whose temperature characteristics (such as B-characteristic) are excellent. Set the capacitance to an optimum value that meets the set's ripple requirement and is not lower than 10  $\mu$ F. It is more difficult to achieve phase compensation with ceramic capacitors than with tantalum electrolytic capacitors because the equivalent series resistance (ESR) of the former is much lower than that of the latter. For this reason, perform a careful evaluation when using ceramic capacitors.

#### **Miscellaneous**

Generally, a DC-DC converter under current mode control may fail to operate at a constant duty ratio if the duty ratio is 50% or higher. This IC incorporates slope compensation to achieve as stable an operation as possible.

However, a delay in the internal circuit may prevent the IC from operating at a constant duty ratio when the duty ratio is 50% or so depending on your input/output and load conditions.

### **Board layout**

Figure 4: TB7100F board layout

- For the supply voltage, output, and ground lines, which carry high current, use thick wires and make them as short as possible so as to keep their impedance low.

- Place the input/output smoothing capacitors and inductor as close to the IC as possible.

- For the output voltage monitoring FB line, keep the wire as short as possible to counter the effects of noise.

- Design the layout to ensure that no voltage potential difference occurs between the SGND and PGND pins. Otherwise, the operation of the IC may become unstable.

- It is recommended you place the components connected to the COMP and R<sub>T</sub> pins as close to the IC as possible and ground them at a single point so as stabilize the voltage at these pins. Otherwise, the operation of the IC may become unstable.

- The leakage current of the SBD may increase at high temperatures, leading to a thermal runaway. Ensure, therefore, that no problem with the SBD will occur even under the worst-case conditions.

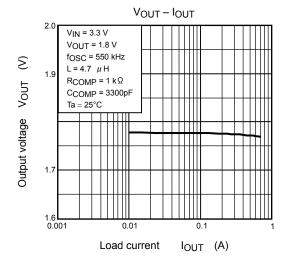

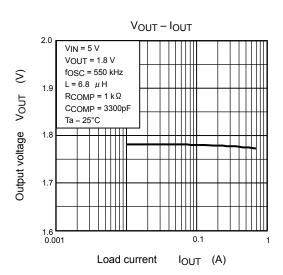

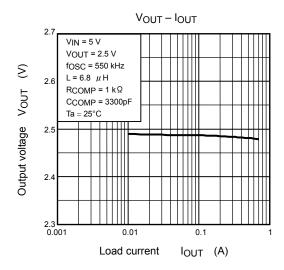

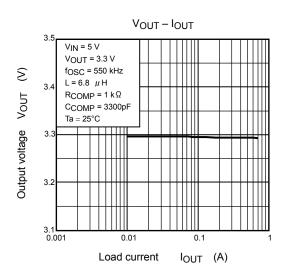

A DC-DC converter using this IC is greatly affected by the characteristics of external components and the impedance of the PCB. Make sure that there is no problem with the dependency of the load current on its output voltage and load response even when any component constant deviates from the corresponding value given above for reference purposes. Also, design the DC-DC converter by selecting optimum external components and a suitable board layout so that no rating of this IC will be exceeded.

### **Precautions**

- If the voltage between the input and output is low, the influence of the on-state voltage of the switch power MOSFET is greater, causing the voltage across the inductor to decrease. For this reason, it may become impossible for the required inductor current to flow, resulting in lower performance or unstable operation of the DC-DC converter. As a rough standard, keep the input-output voltage potential difference at or above 1 V, taking the on-state voltage of the power MOSFET into consideration.

- The lowest output voltage that can be set is 0.8 V (typ.).

- There is an antistatic diode between the ENB and V<sub>IN</sub> pins. The voltage between the ENB and V<sub>IN</sub> pins should satisfy the rating

V<sub>ENB</sub> V<sub>IN</sub> < 0.3 V</li>

9

13

14

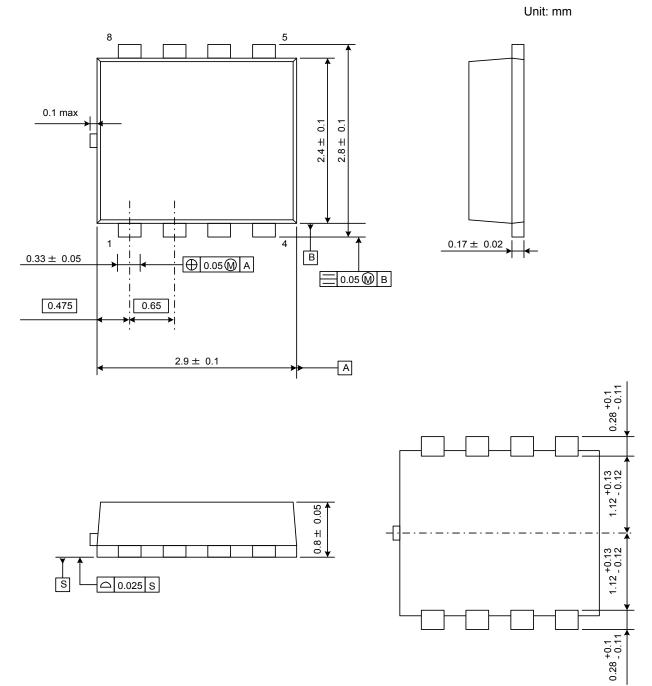

## Package dimensions

SON8-P-0303-0.65A

Weight: 0.016 g (Typ.)

### **RESTRICTIONS ON PRODUCT USE**

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations

that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses

occurring as a result of noncompliance with applicable laws and regulations.