ZL38005 Enhanced Voice Processor with Dual Wideband Codecs

Data Sheet

#### Features

- 100 MHz (200 MIPs) Zarlink voice processor with hardware accelerator.

- Dual narrow band (8 KHz)  $\Delta\Sigma$  ADCs with input buffer gain selection

- Dual narrow band (8 KHz)  $\Delta\Sigma$  DACs

- Dual function Inter-IC Sound (I<sup>2</sup>S) port

- PCM port supports TDM (ST BUS, GCI or McBSP framing) or SSI modes at bit rates of 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 Kb/sec

- Separate slave (microcontroller) and master (Flash) SPI ports, maximum clock rate = 25 MHz

- 11 General Purpose Input/Output (GPIO) pins

- General purpose UART port

- Bootloadable for future Zarlink software upgrades

- External oscillator or crystal/ceramic resonator

- 1.2 V Core; 3.3 V IO with 5 V-tolerant inputs

- IEEE-1149.1 compatible JTAG port

| Se | otem | ber | 2007 |

|----|------|-----|------|

#### **Ordering Information**

| ZL38005QCG1        | 100 Pin LQFP* | Trays, Bake &<br>Drypack |  |  |

|--------------------|---------------|--------------------------|--|--|

| ZL38005GGG2        | 96 Pin CABGA* | Trays, Bake &<br>Drypack |  |  |

| *Pb Free Matte Tin |               |                          |  |  |

-40°C to +85°C

#### **Applications**

- Hands-free car kits

- Full duplex speaker-phone for digital telephone

- Echo cancellation for video conferences

- Intercom Systems

- Security Systems

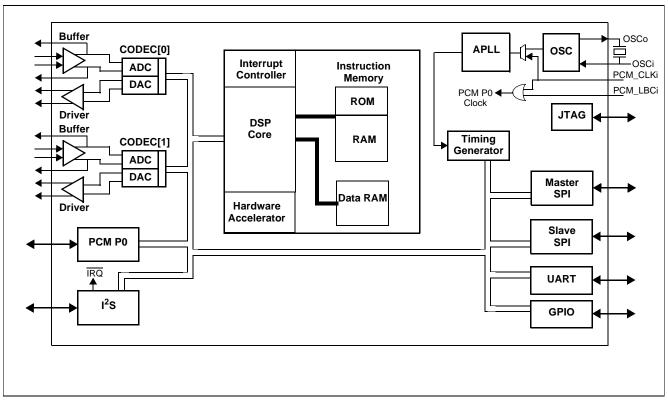

#### Figure 1 - Functional Block Diagram

## **1.0** Functional Description

The ZL38005 is a hardware platform designed to support advanced acoustic echo canceller (with noise reduction) firmware applications available from Zarlink Semiconductor. These applications are resident in external memory and are down-loaded by the ZL38005 resident boot code during initialization.

The firmware product and manual available at the release of this data sheet is the ZLS38501: Acoustic Echo Canceller with Noise Reduction. If these applications do not meet your requirements, please contact your local Zarlink Sales Office for the latest firmware releases.

The ZL38005 Advanced Acoustic Echo Canceller with Noise Reduction platform integrates Zarlink's Voice Processor (ZVP) DSP Core with a number of internal peripherals. These peripherals include the following:

- Two independent  $\Delta\Sigma$  CODECs

- Two PCM ports ST BUS, GCI, McBSP or SSI operation

- An I<sup>2</sup>S interface port

- A 2048 tap Filter Co-processor (LMS, FIR and FAP realizations)

- Two Auxiliary Timers and a Watchdog Timer

- 11 GPIO pins

- A UART interface

- A Slave SPI port and a Master SPI port

- A timing block that supports master and slave operation

- An IEEE 1149.1 compatible JTAG port

The DSP Core can process up to four 8-bit audio channels, two 16-bit audio channels or two 8-bit and one 16-bit audio channel. These audio channels may originate and terminate with the  $\Sigma\Delta$  CODECs, or be communicated to and from the DSP Core through the PCM ports or the I<sup>2</sup>S port.

## 2.0 Core DSP Functional Block

The ZL38005 DSP Core functional block, illustrated in Figure 1, is made up of a DSP Core, Interrupt Controller, Data RAM, Instruction RAM, BOOT ROM Hardware Accelerators. This block controls the timing (APLL and Timing Generator), peripheral interfaces through a peripheral address/data/control bus.

The ZL38005 implementation of DSP core and Filter Co-processor have been optimized to efficiently support voice processing applications. These applications are described in detail in the Firmware Manuals associated with this hardware platform.

#### 2.1 DSP

The Core DSP is a 100 MIPS processor realized with two internal memory busses (Harvard architecture) to allow multiple accesses during the same instruction cycle. In addition the DSP uses hardware accelerators and a filter co processor that can be reused for different applications.

The Filter Co-Processor is used by the application firmware to realize the LMS filters up to a maximum of 2048 coefficients (taps).

## 3.0 Codec[1:0]

The ZL38005 has two 16-bit fully differential  $\Delta\Sigma$  DACs (DAC 0/1) that meets G.712 requirements at 8 kHz sampling The ADC path consists of input signal pins C0/1\_ADCi+ and C0/1\_ADCi- (buffer output pins C0/1\_BF0+ and C0/1\_BFo-), which feed selectable Microphone Amplifier or Line Amplifier options. The ADC sampling is 8KHz.

## 4.0 PCM Port

#### 4.1 PCM Port

The PCM port support data communication between an external peripheral device and the ZL38005 DSP Core using separate input (PCMi) and output (PCMo) serial streams with TDM (i.e., ST-BUS, GCI or McBSP) or SSI interface timing. Access to the control and status registers associated with these ports is through the Slave SPI port UART. These port signals are either in their input or high impedance states after a power-on reset and outputs signals PCMo may be put in a high impedance state at any time during normal operation. Refer to the associated Firmware Manual for PCM port control, status and mode selection.

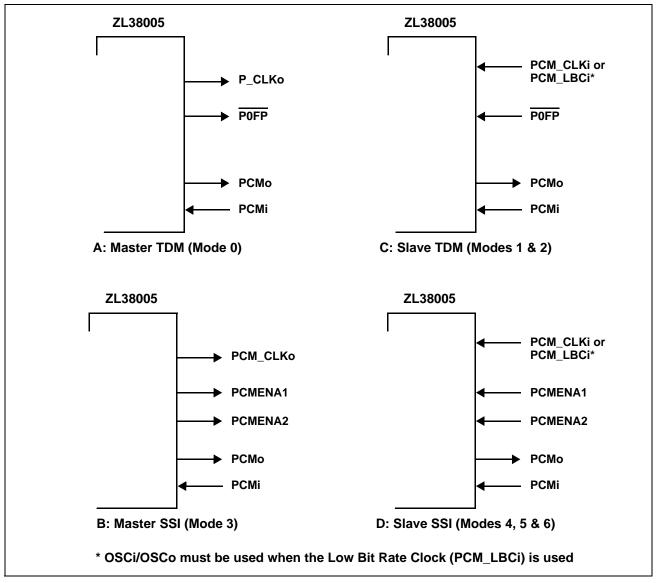

Figure 2 illustrates the signals associated with the Master and Slave timing modes of operation for PCM Port. Insert A: PCM port Master TDM (Mode 0), shows data clock (PCM\_CLKo) and frame pulse (PCMFP) as outputs derived from the ZL<u>38005</u> internal PLL. PCM\_CLKo clocks data into the ZL<u>38005</u> on PCMCMi and out of the ZL<u>38005</u> on PCMO, and PCMFP delineates the 8 kHz frame boundaries for these signals. Insert B: PCM Master SSI (Mode3), functions the same way as the TDM Master except that selected channels are defined by enable outputs P0ENA1 and P0ENA2.

With slave operation the source of timing is not the ZL38005, so PCM\_CLKi is the input clock and PCMFP is the 8 kHz input frame pulse. This is illustrated by Figure 2 C: PCM Port Slave TDM (Modes 1 & 2) and D: PCM Port Slave SSI (Modes 4, 5 & 6).

Figure 2 - PCM Port Signal Configurations for Master/Slave Operation

The ZL38005 will process audio channels of up to 16 bits in length. Audio channel sizes are designated as either 8bit (Short) or 16-bit (Long) on the PCM interfaces. With TDM operation each audio channel is mapped on to one or more 8-bit time slots that are defined by the associated frame alignment signal. Each PCM port (0 & 1) supports from 1 to 4 Short Channels; 1 or 2 Short Channels and 1 Long (16-bit) Channel; or 2 Long Channels. Audio channels are defined as First and Second Long, and First, Second, Third and Fourth Short, see the Firmware Manual for assignment details. These channels may be assigned to different time slots on the input and output streams.

In SSI mode each PCM port supports 1 or 2 Short or Long channels, which are defined on PCMi0 by the position and length of enable signals P0ENA1 and P0ENA2. Audio channels are defined as First and Second Long, and First and Third Short, see the Firmware Manual for assignment details. Channel positions and length are common to input and output signals.

### 4.2 SSI Operation

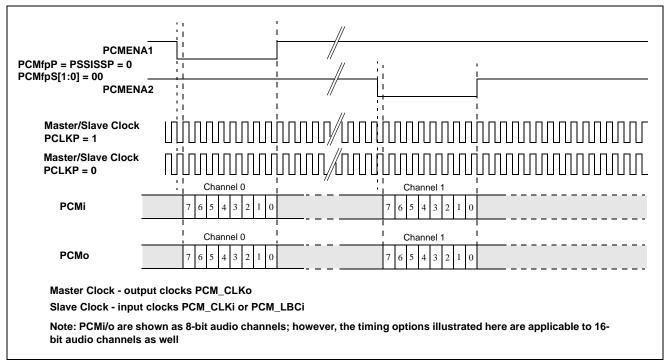

Figures 3 illustrates the SSI functional timing used when the two enable strobes (audio channels) are separated by a non-zero number of bit clock cycles. Here the enable signal polarities are active low, either bit clock polarity may be selected. In this format frames are delineated by the active edge of PCMENA1 minus 1/2 bit clock cycle. The frame repetition rate is 8 kHz. See Firmware Manual to program the positions of the Audio Channels within the 8 kHz frame.

Figure 3 - SSI Mode: Separated Channels Functional Timing

## 4.3 I<sup>2</sup>S Port Description

The I<sup>2</sup>S (Inter-IC Sound) port and PCM Port One share the same physical pins of the ZL38005. Selection of either I<sup>2</sup>S port operation or PCM Port One operation is done through the Port One PCM/I<sup>2</sup>S Select Register. See Firmware Manual.

The I<sup>2</sup>S port can be used to connect external Analog-to-Digital Converters or CODECs to the internal DSP. This port can operate in master mode, where the ZL38005 is the source of the port clocks, or slave mode, where the bit and sampling clocks (I<sup>2</sup>S\_SCK and I<sup>2</sup>S\_LRCK) are inputs to the ZL38005. The master clock (I<sup>2</sup>S\_MCLK) is always an output. In I<sup>2</sup>S port master mode the clock signal at output pin I<sup>2</sup>S\_LRCK is the sampling frequency (f<sub>S</sub>), the clock signal at output I<sup>2</sup>S\_SCK is 32 x f<sub>S</sub>, and the clock signal at output I<sup>2</sup>S\_MCLK is 256 x f<sub>S</sub>. In I<sup>2</sup>S port slave mode the relationship between the clock signal at input pin I<sup>2</sup>S\_LRCK and the clock signal at input I<sup>2</sup>S\_SCK must be 32 x f<sub>S</sub>. In slave mode the 256 x f<sub>S</sub> relationship between f<sub>S</sub> and the I<sup>2</sup>S\_MCLK is not mandatory, and the I<sup>2</sup>S\_MCLK output pin will be in a high impedance state. See Firmware Manual for I<sup>2</sup>S programming options.

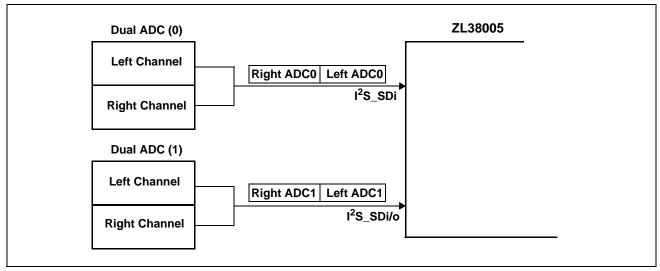

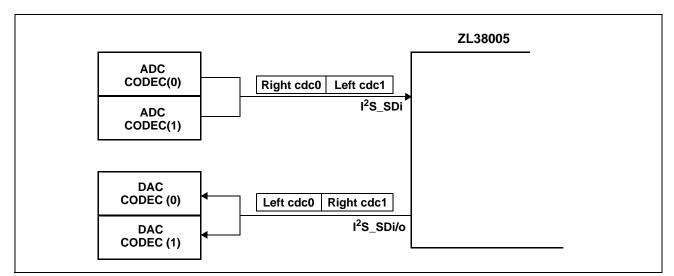

The I<sup>2</sup>S interface can support two dual channel Analog-to-Digital Converters (Figure 4) or one dual channel CODEC (Figure 5). In Figure 4 pin I<sup>2</sup>S\_SDi/o is configured as an input (control bit I<sup>2</sup>SSDi/oSel = 0) so that the four 16-bit channel processing capacity of the DSP is spread across the two input channels from Dual ADC (0) plus the two input channels from Dual ADC (1). See Firmware Manual for I<sup>2</sup>S port setup.

Figure 4 - Dual Analog-to-Digital Converter Configuration

In Figure 5 pin  $l^2S\_SDi/o$  is configured as an output (control bit  $l^2SSDi/oSel = 1$ ) so that the four 16-bit channel processing capacity of the DSP is spread across the two input channels from the ADCs of CODEC(0) and CODEC(1), as well as the two output channels from the ADCs of CODEC(0) and CODEC(1). See Firmware Manual for  $l^2S$  port setup.

Figure 5 - Dual CODEC Configuration

## 5.0 Host Microprocessor and Peripheral Interfaces

#### 5.1 Master SPI (FLASH Port)

The Master SPI port is used by the ZL38005 to access one or two peripheral devices (chip select signals SPIM\_CS[1:0]). It supports both SPI and MICROWIRE modes of operation and can write up to 40 bits or read up to 32 bits in a single access. The Chip Select output signals may be programmed for a single access or burst access. All communication is MSB first and all pins of the master SPI port are outputs controlled by the ZL38005, except SPIM\_MISO, se

#### 5.2 Host Interface Operation (Slave SPI and UART Ports)

The control/status registers and memory of the ZL38005 can be accessed (R/W) by an external host through the Slave SPI and the UART ports.

The slave SPI port may be used by an external host microprocessor to access (Read/Write) the ZL38005 internal control/status registers and memory. Access is initiated when the external host makes signal SPIS\_CS low and is ended when this signal goes high. The host will then apply a clock (maximum 25 MHz) to signal SPIS\_CLK to clock data out of SPIS\_MISO and in on SPIS\_MOSI.

The UART (Universal Asynchronous Receiver Transmitter) port may be used by an external host microprocessor to access (Read/Write) the ZL38005 internal control/status registers and memory. The ZL38005 DSP will set up the initial parameters of this port (i.e., master/slave, baud rate, stop bits, parity bit...) during the Boot process. After the device has been booted these port options can be changed as per the Firmware Manual.

The UART port will support 8-bit data only with any combination of 1 start bit, 0 or 1 parity bit(s) and 1, 1.5 or 2 stop bit(s).

#### 5.3 GPIO

The ZL38005 has 11 GPIO (General Purpose Input/Output) pins that can be individually configured as either input or output. These pins are intended for low frequency signalling.

When a GPIO pin is defined as an input the state of that input pin is sampled with the internal master clock (Mclk = 100 MHz) and latched into the GPIO Read Register.

Immediately after a power-on reset ( $\overline{RST}$  pin) the GPIO pins are defined as inputs and their state is captured in the GPIO Start-Up Status Register. The state of this register is used by the Boot program to determine the base functionality and programming options of the device.

Individual GPIO pins may also be defined as outputs with associated enable/disable (active/high impedance) control. See the Firmware Manual for control and status programming.

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE