# **TOSHIBA**

TOSHIBA Original CMOS 32-Bit Microcontroller

# TLCS-900/H1 Series

TMP92CA25FG

# **TOSHIBA CORPORATION**

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions".

#### CMOS 32-bit Microcontroller

#### TMP92CA25FG/JTMP92CA25

#### Outline and Device Characteristics

The TMP92CA25 is a high-speed advanced 32-bit Microcontroller developed for controlling equipment which processes mass data.

The TMP92CA25 has a high-performance CPU (900/H1 CPU) and various built-in I/Os.

The TMP92CA25FG is housed in a 144-pin flat package. The JTMP92CA25 is a chip form product.

Device characteristics are as follows:

- (1) CPU: 32-bit CPU (900/H1 CPU)

- Compatible with TLCS-900/L1 instruction code

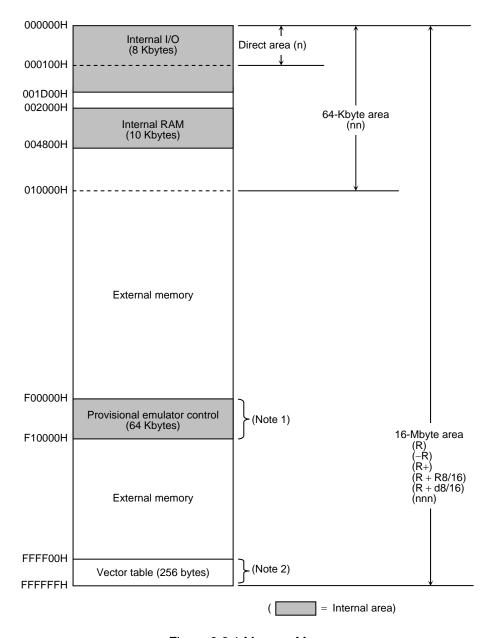

- 16 Mbytes of linear address space

- General-purpose register and register banks

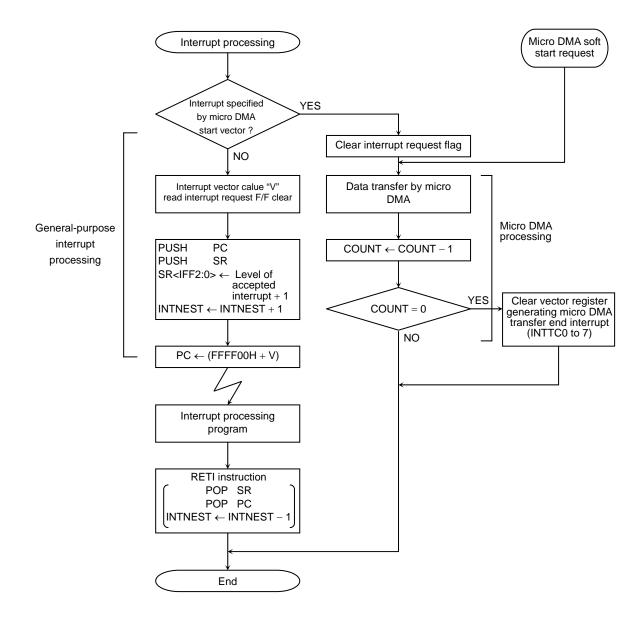

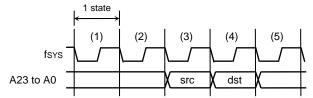

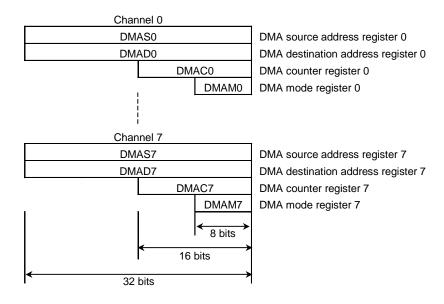

- Micro DMA: 8 channels (250 ns/4 bytes at fsys = 20 MHz, best case)

- (2) Minimum instruction execution time: 50 ns (at fSYS = 20 MHz)

#### **RESTRICTIONS ON PRODUCT USE**

070208EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties. 021023\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

- (3) Internal memory

- Internal RAM: 10 Kbytes (can be used for program, data and display memory)

- Internal ROM: 0 Kbytes (used as boot program)

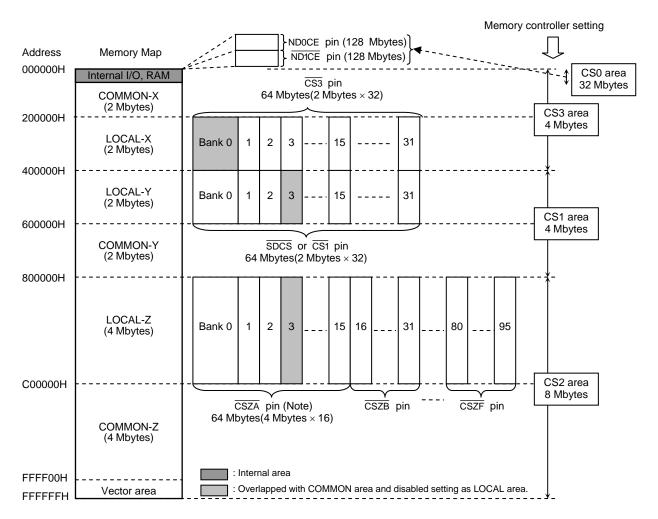

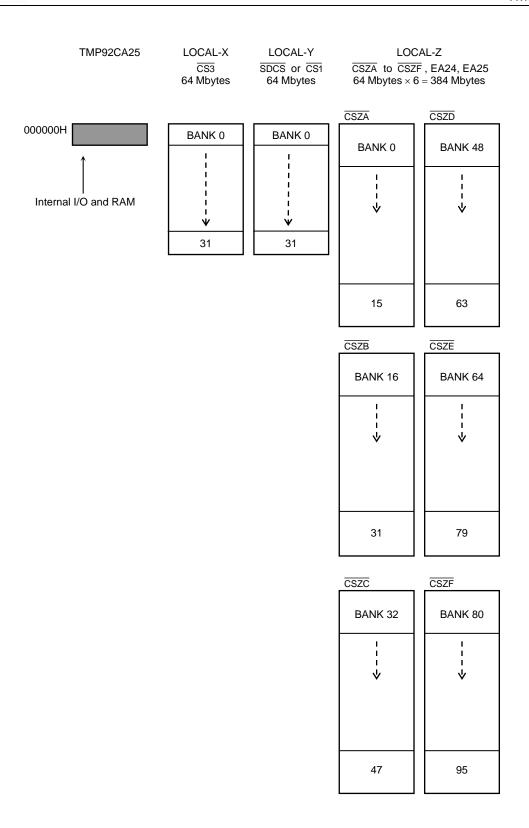

- (4) External memory expansion

- Expandable up to 512 Mbytes (shared program/data area)

- Can simultaneously support 8,- 16- or 32-bit width external data bus ... dynamic data bus sizing

- (5) Memory controller

- Chip select output: 4 channels

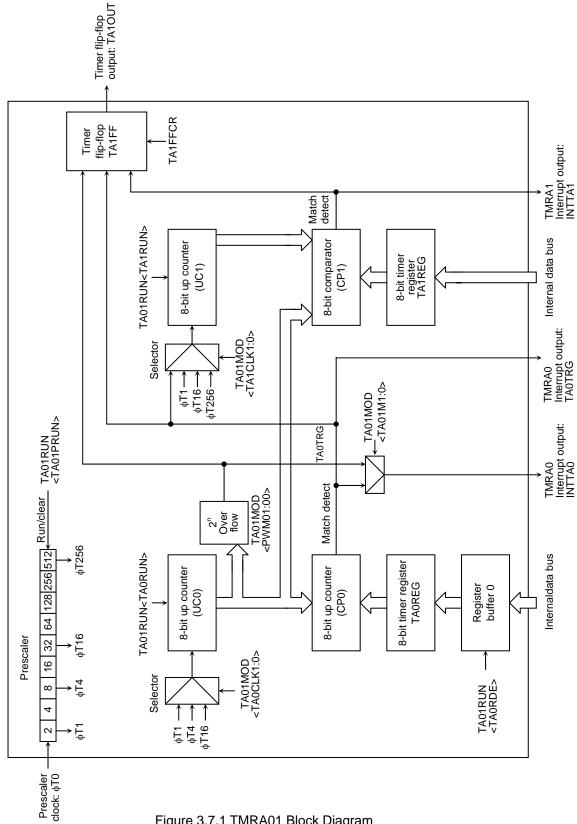

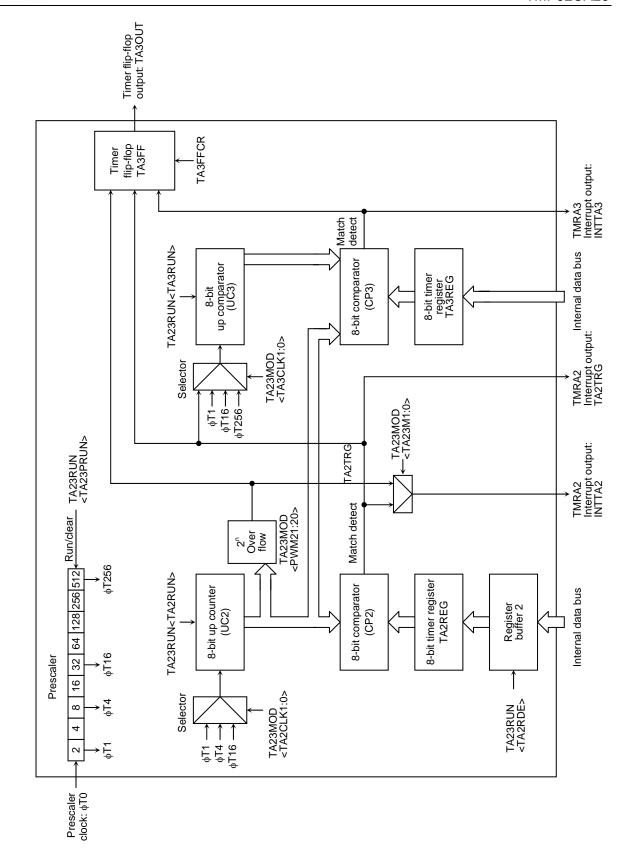

- (6) 8-bit timers: 4 channels

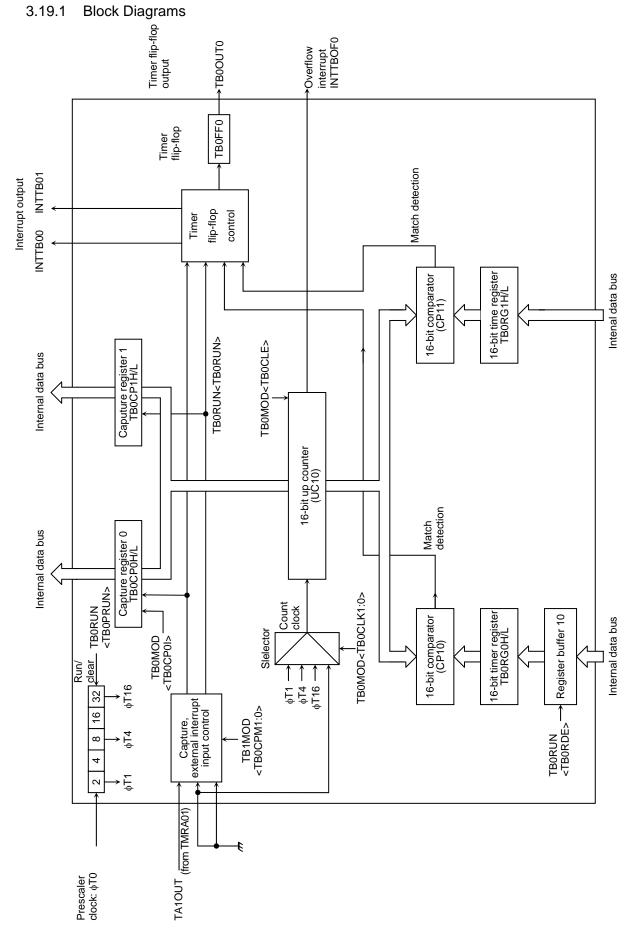

- (7) 16-bit timer/event counter: 1 channel

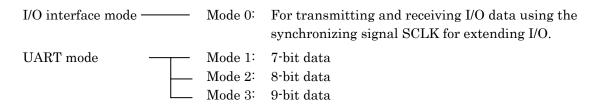

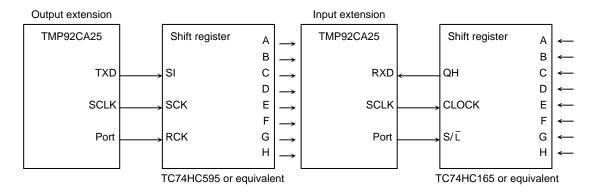

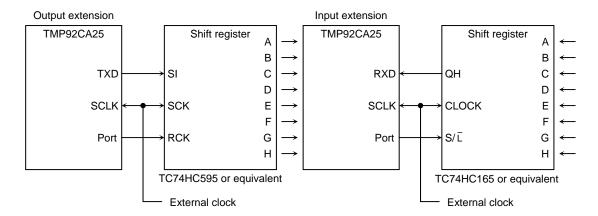

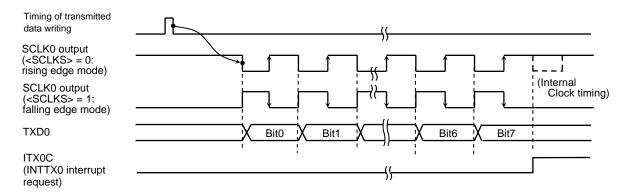

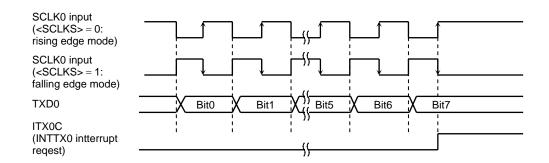

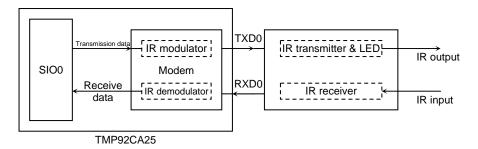

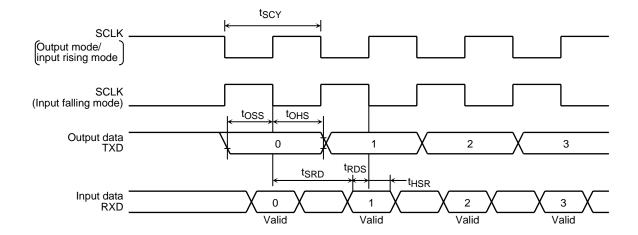

- (8) General-purpose serial interface: 1 channels

- UART/synchronous mode

- IrDA ver.1.0 (115 kbps) mode selectable

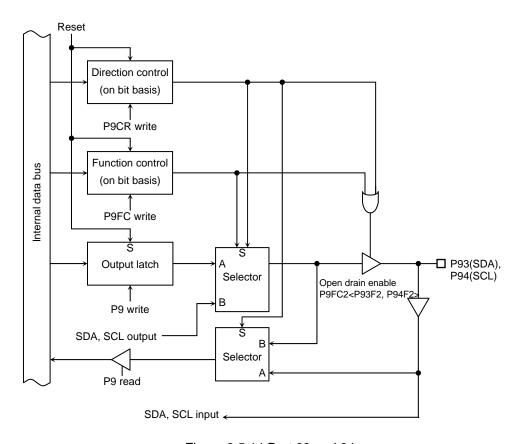

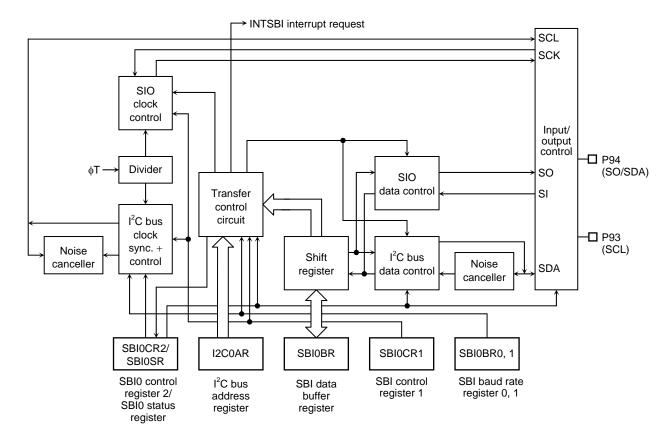

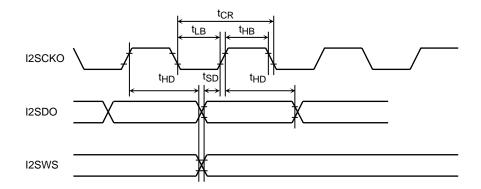

- (9) Serial bus interface: 1 channel: 1 channel

- I2C bus mode only

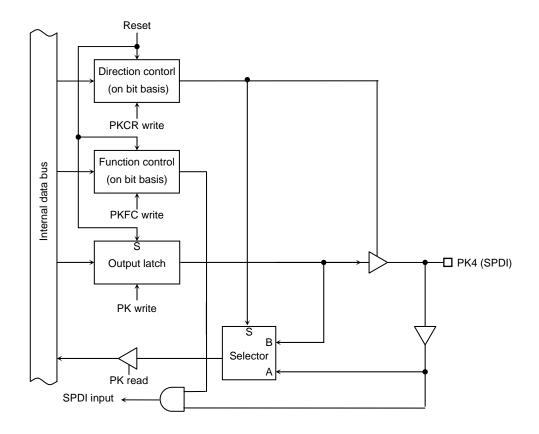

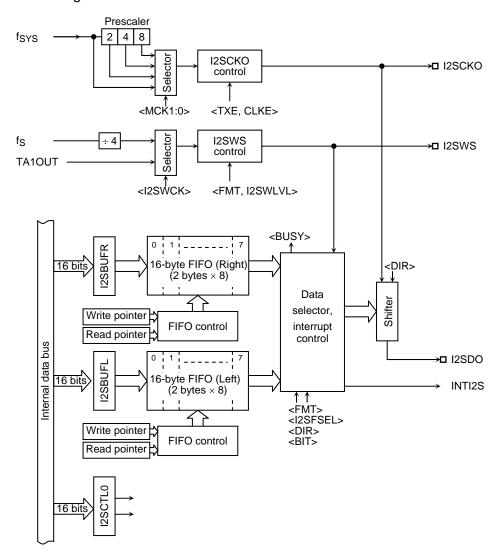

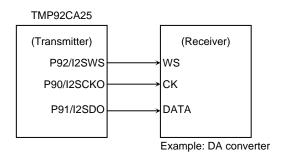

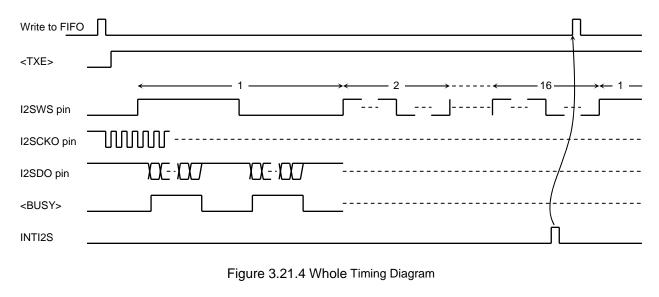

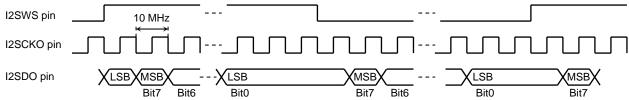

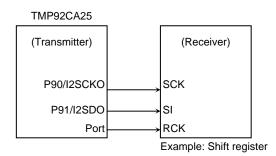

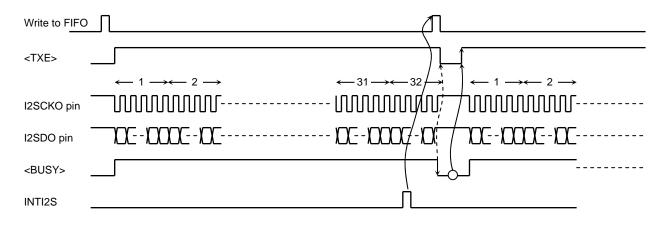

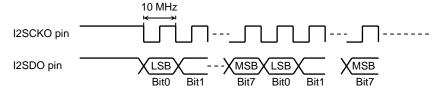

- (10) I2S (Inter-IC sound) interface: 1 channel

- I<sup>2</sup>S bus mode/SIO mode selectable (Master, transmission only)

- 32-byte FIFO buffer

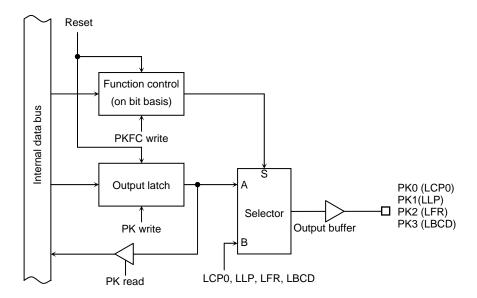

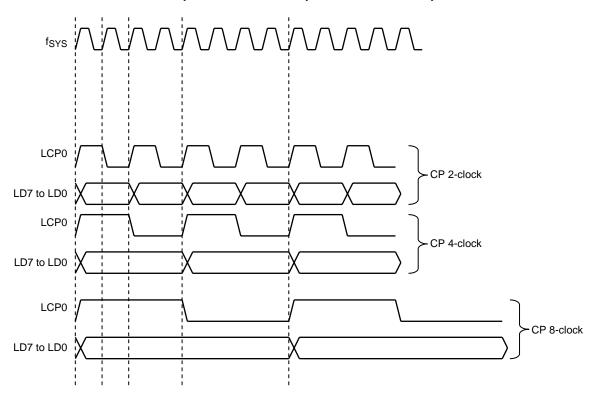

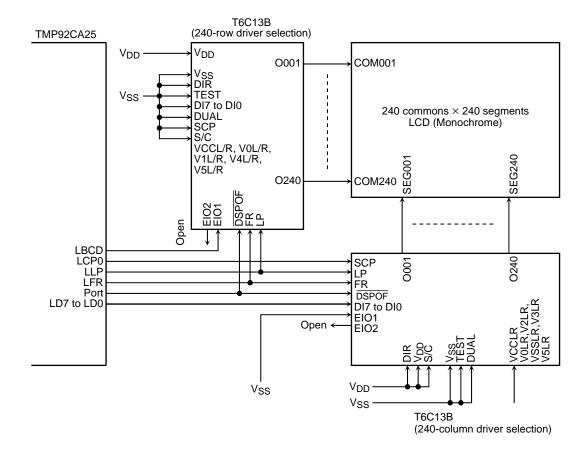

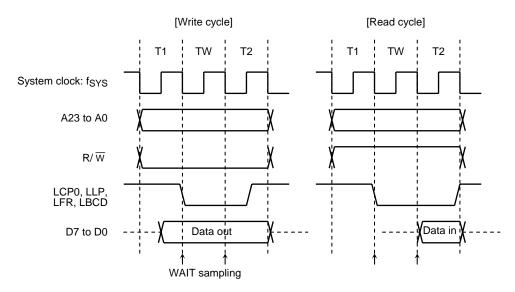

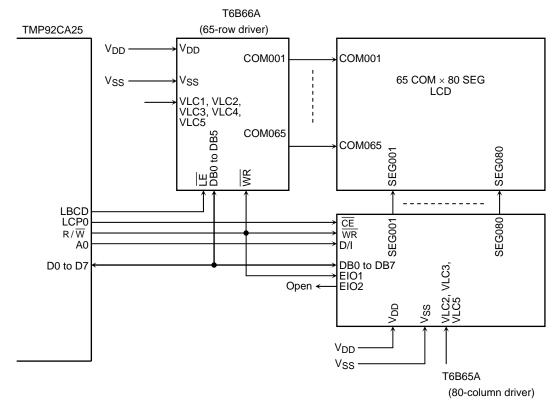

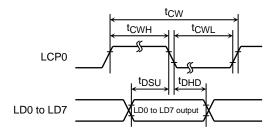

- (11) LCD controller

- Supports monochrome for STN

- Built-in RAM LCD driver

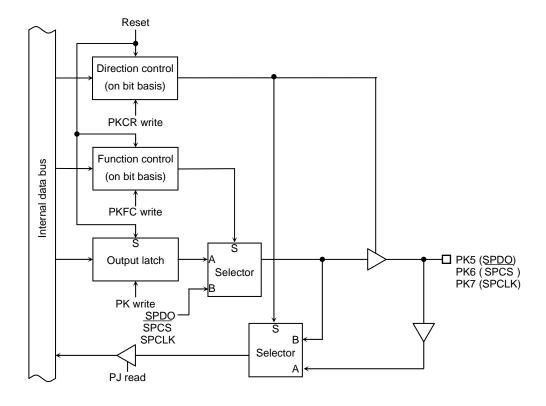

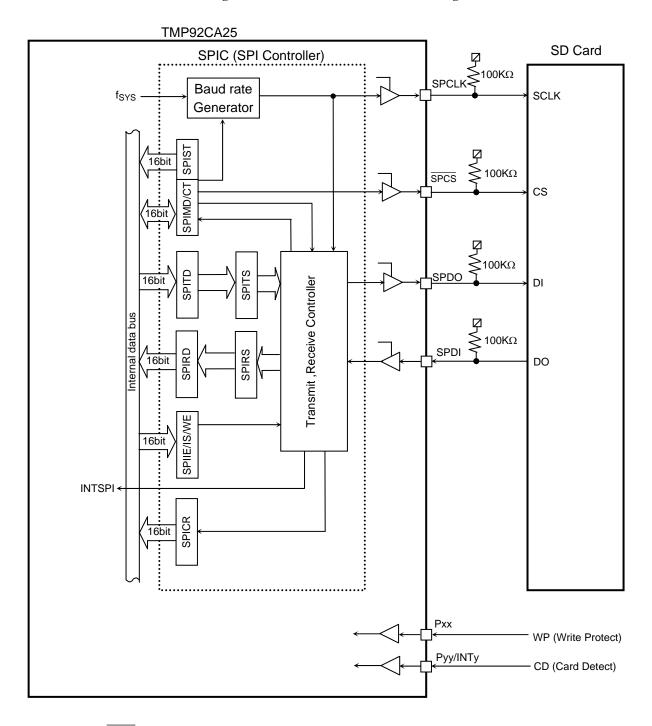

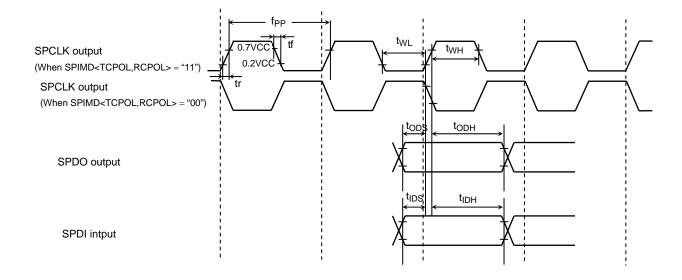

- (12) SPI controller

- Supported only SPI mode for SD card

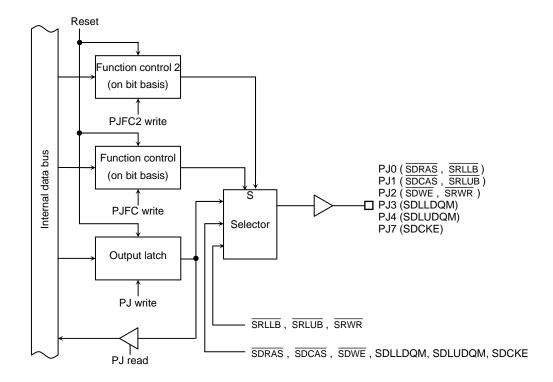

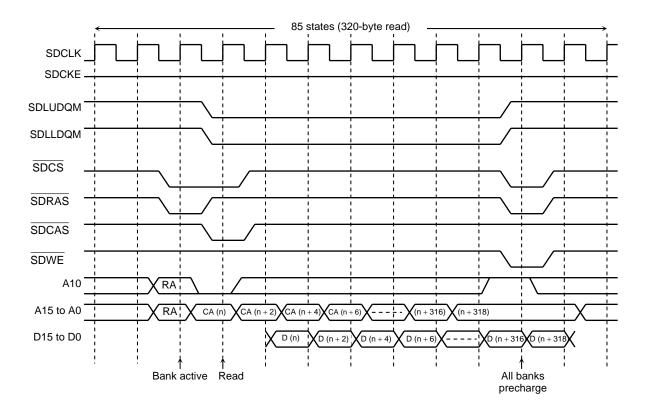

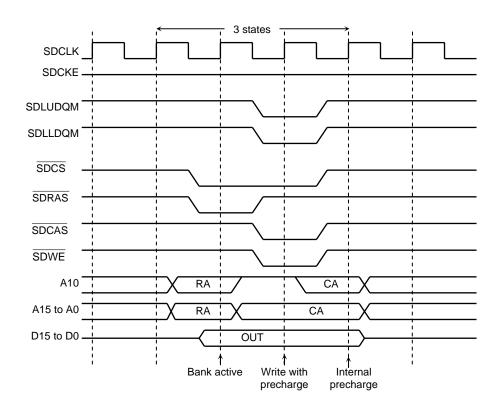

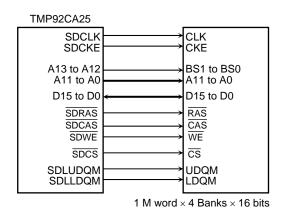

- (13) SDRAM controller: 1 channel

- Supports 16 M, 64 M, 128 M, 256 M, and up to 512-Mbit SDR (Single Data Rate)-SDRAM

- Supported not only operate as RAM and Data for LCD display but also programming directly from SDRAM

- (14) Timer for real-time clock (RTC)

- Based on TC8521A

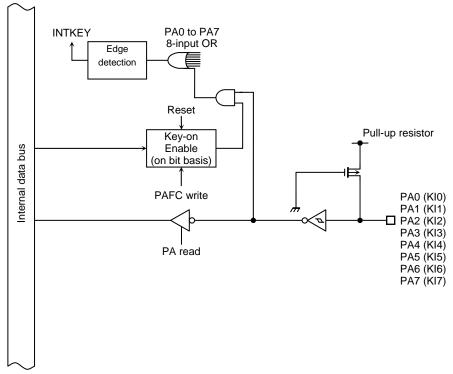

- (15) Key-on wakeup (Interrupt key input)

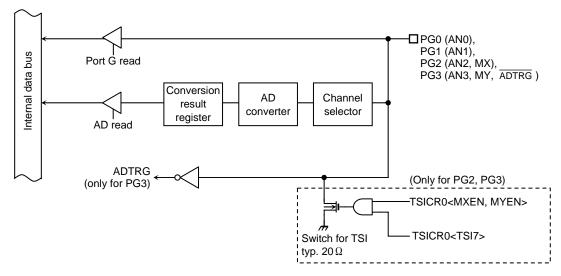

- (16) 10-bit AD converter (Built-in Sample Hold circuit): 4 channels

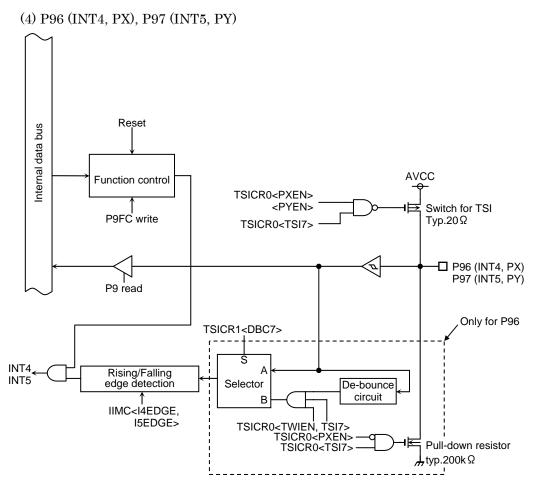

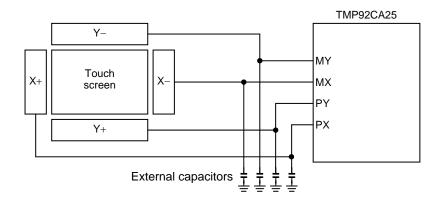

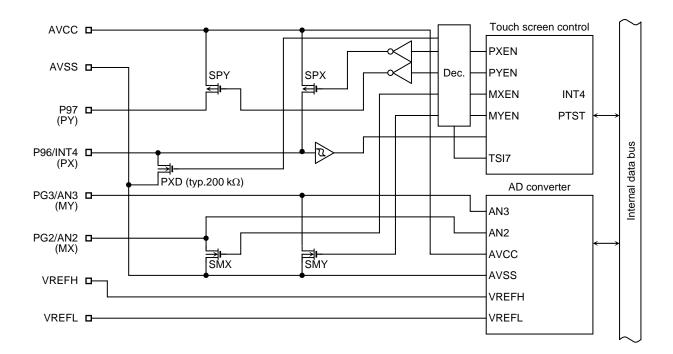

- (17) Touch screen interface

- Available to reduce external components

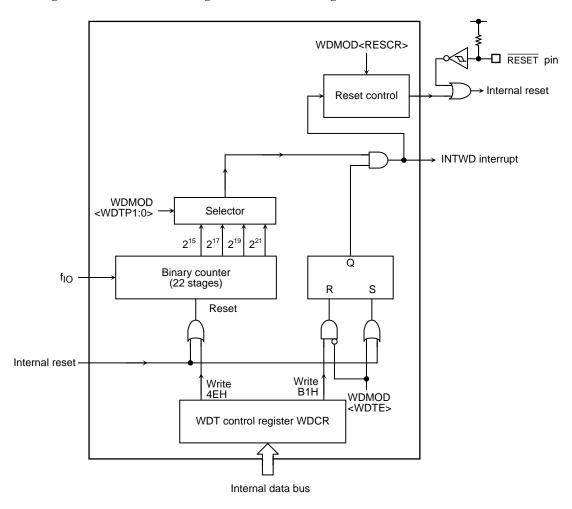

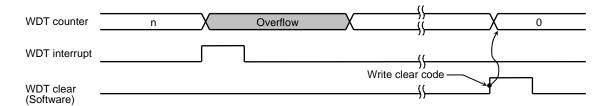

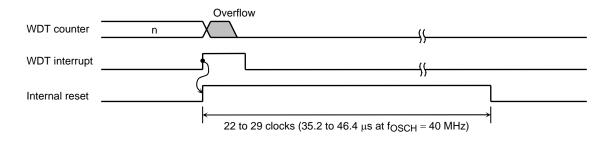

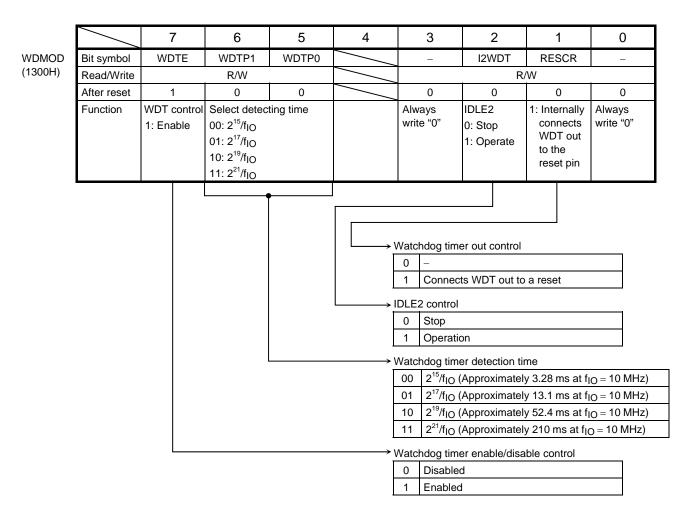

- (18) Watchdog timer

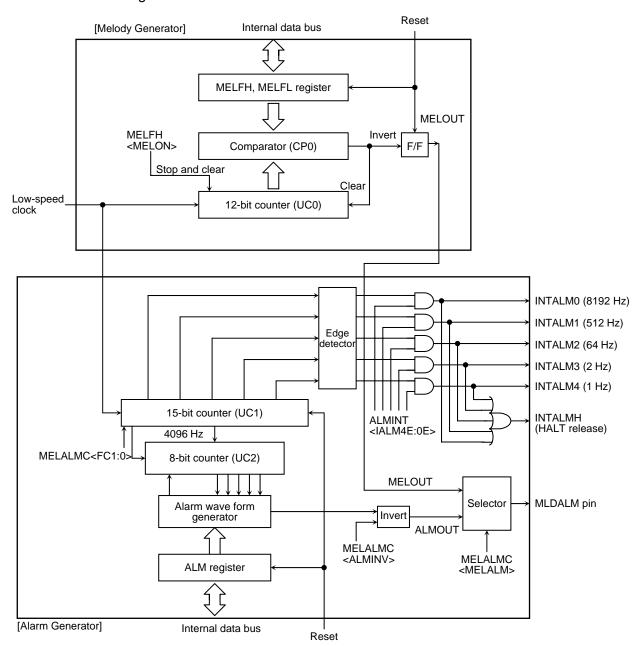

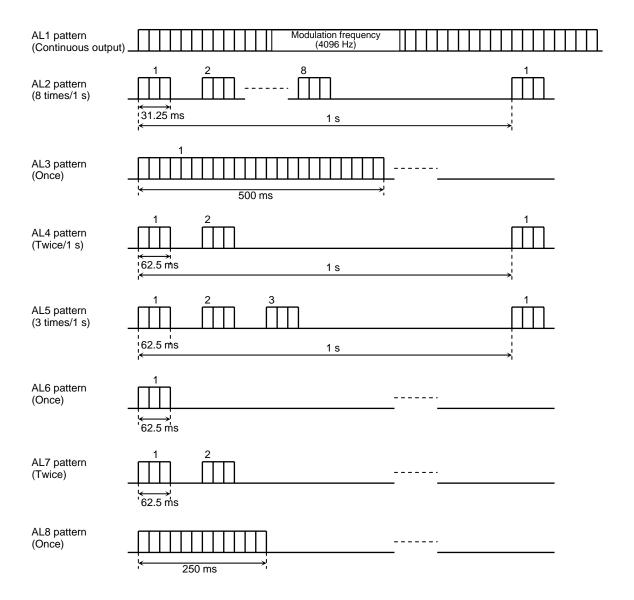

- (19) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of 8 kinds of alarm pattern and 5 kinds of interval interrupt

92CA25-2 2007-02-28

#### (20) MMU

- Expandable up to 512 Mbytes (3 local area/8 bank method)

- Independent bank for each program, read data, write data and LCD display data

#### (21) Interrupts: 49 interrupt

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 34 internal interrupts: Seven selectable priority levels

- 7 external interrupts: Seven selectable priority levels (6-edge selectable)

- (21) Input/output ports: 84 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)

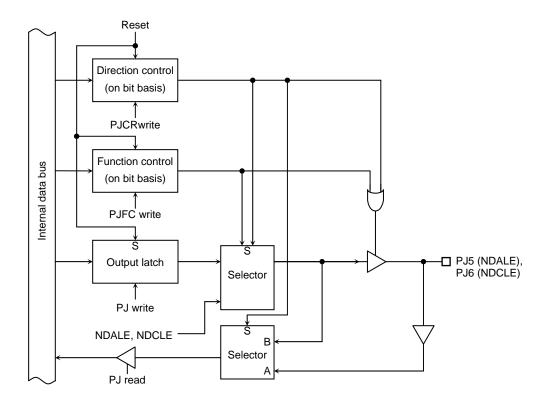

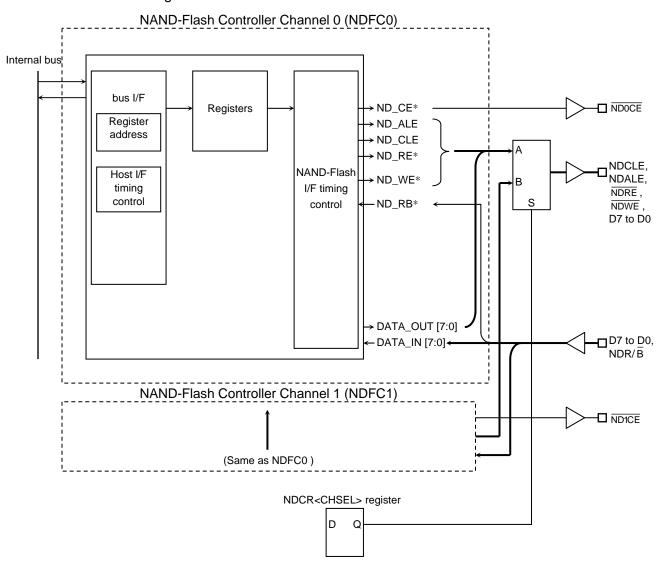

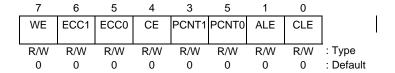

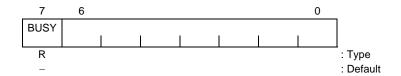

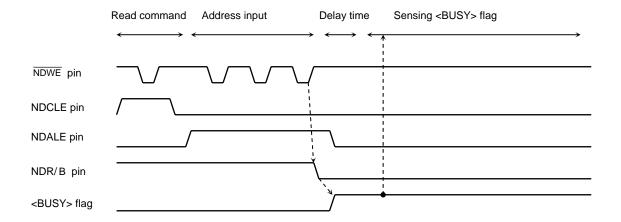

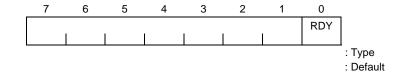

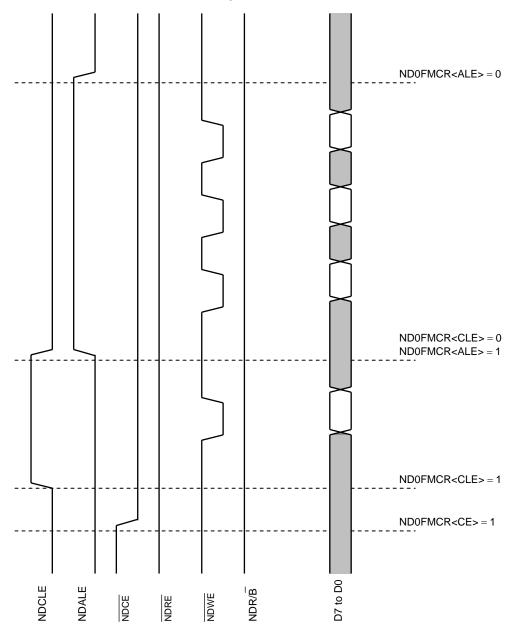

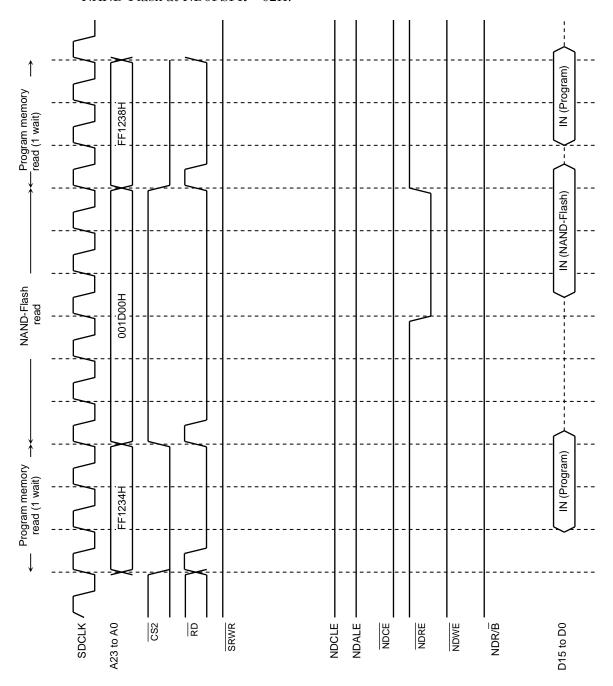

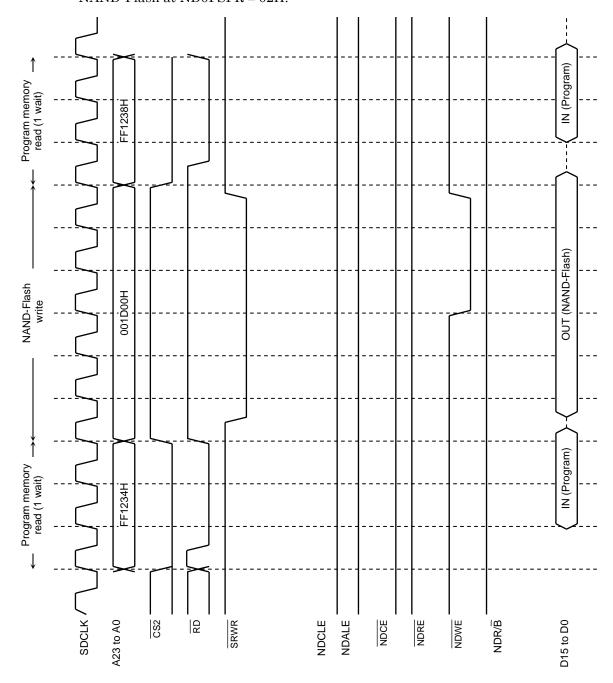

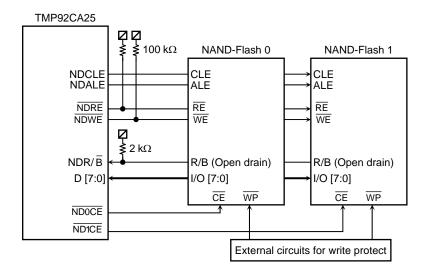

#### (22) NAND flash interface: 2 channels

- Direct NAND flash connection capability

- ECC (error detection) calculation (for SLC- type)

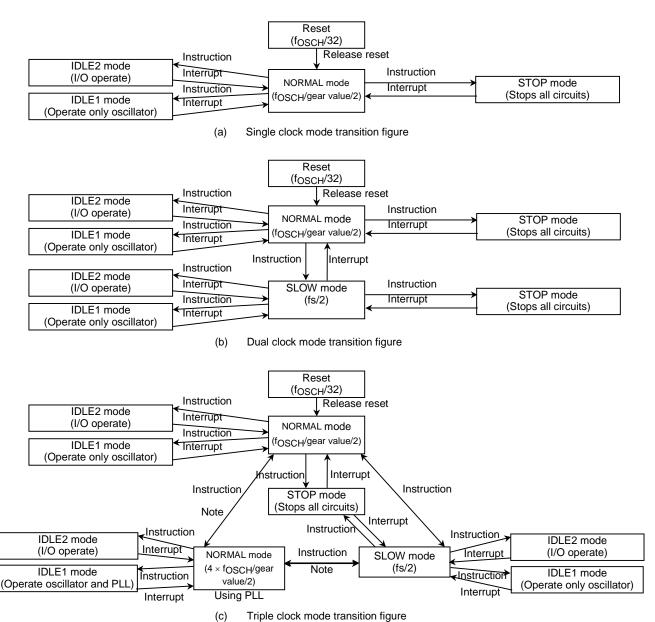

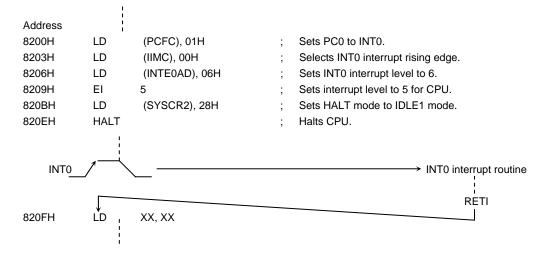

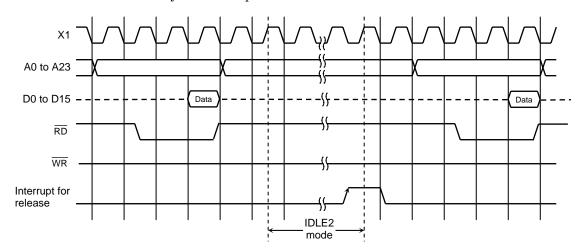

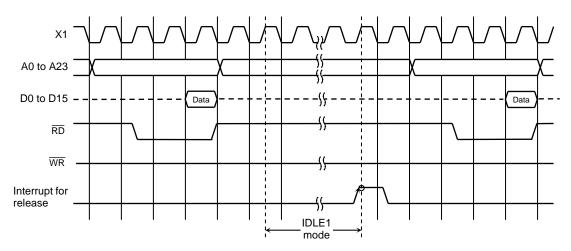

#### (23) Stand-by function

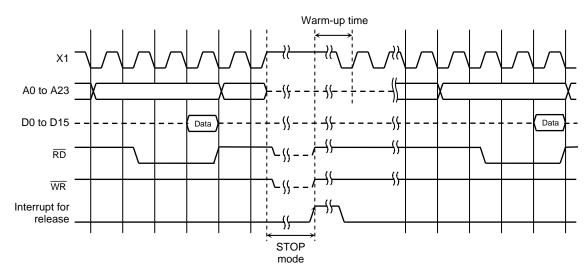

- Three HALT modes: IDLE2 (programmable), IDLE1, STOP

- Each pin status programmable for stand-by mode

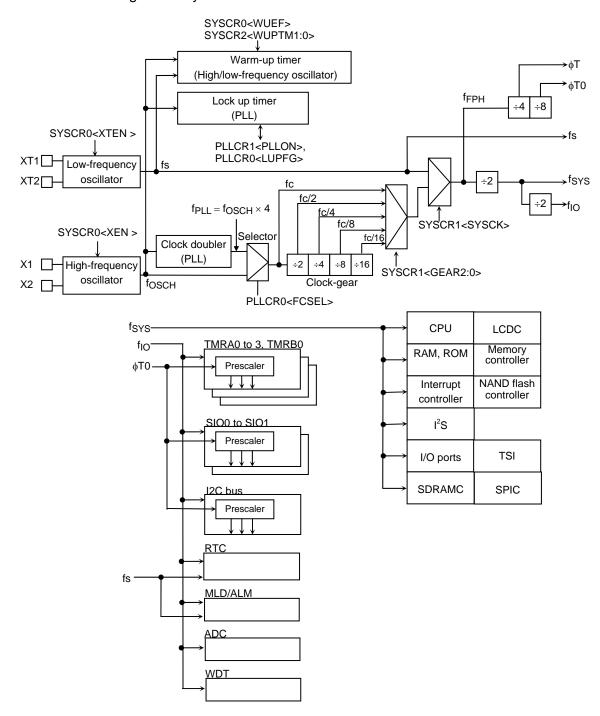

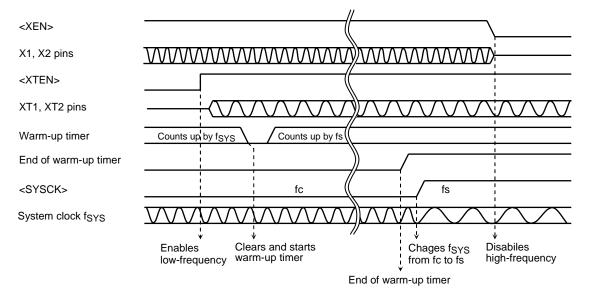

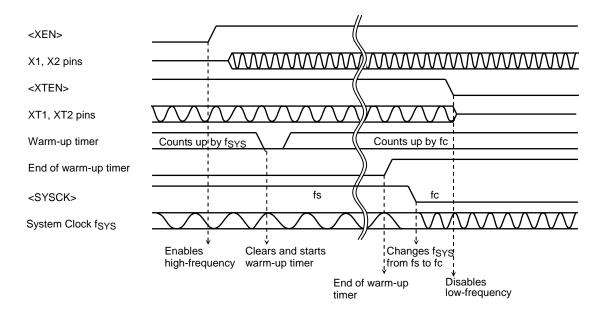

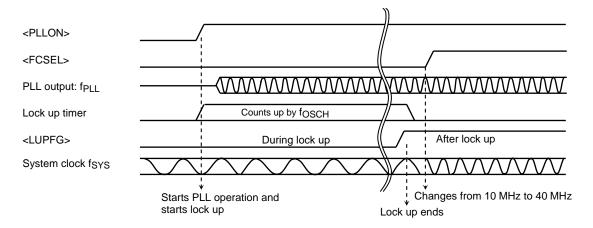

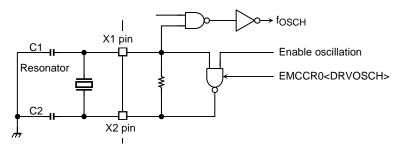

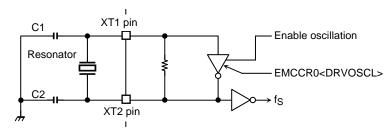

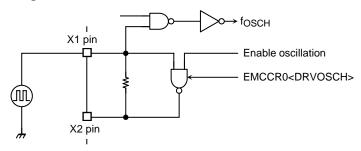

#### (24) Triple-clock controller

- Clock doubler (PLL) supplies 40 system-clock from external 10MHz oscillator to CPU

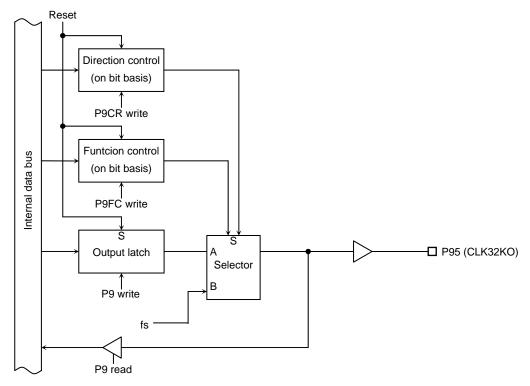

- Clock gear function: Select high-frequency clock fc to fc/16

- RTC (fs = 32.768 kHz)

#### (25) Operating voltage:

- VCC = 3.0 V to 3.6 V (fc max = 40 MHz)

- VCC = 2.7 V to 3.6 V (fc max = 27 MHz)

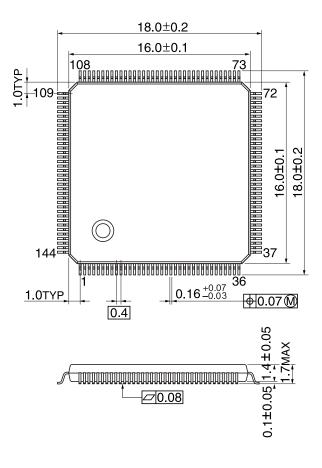

#### (26) Package:

- 144-pin QFP (P-LQFP144 -1616-0.40C)

- 144-pin chip form is also available. For details, contact your local Toshiba sales representative.

92CA25-3 2007-02-28

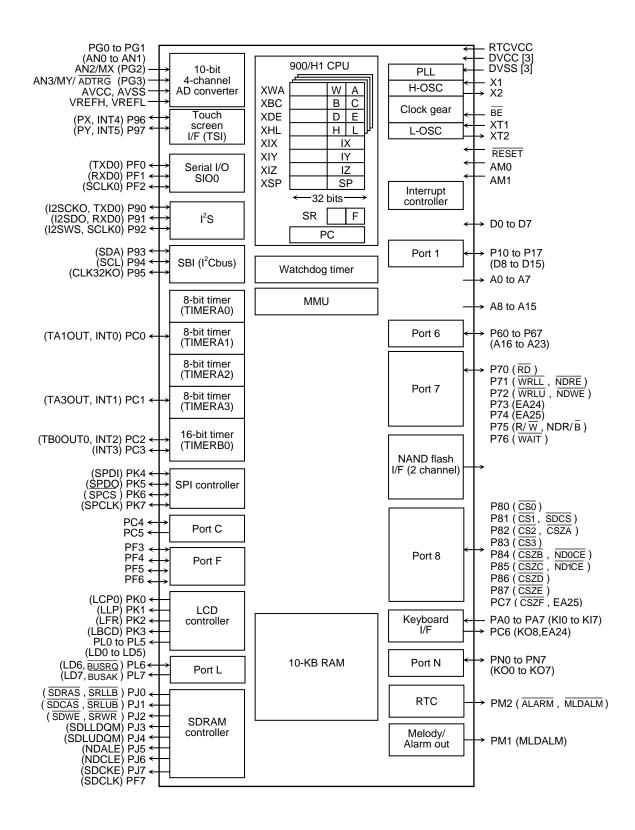

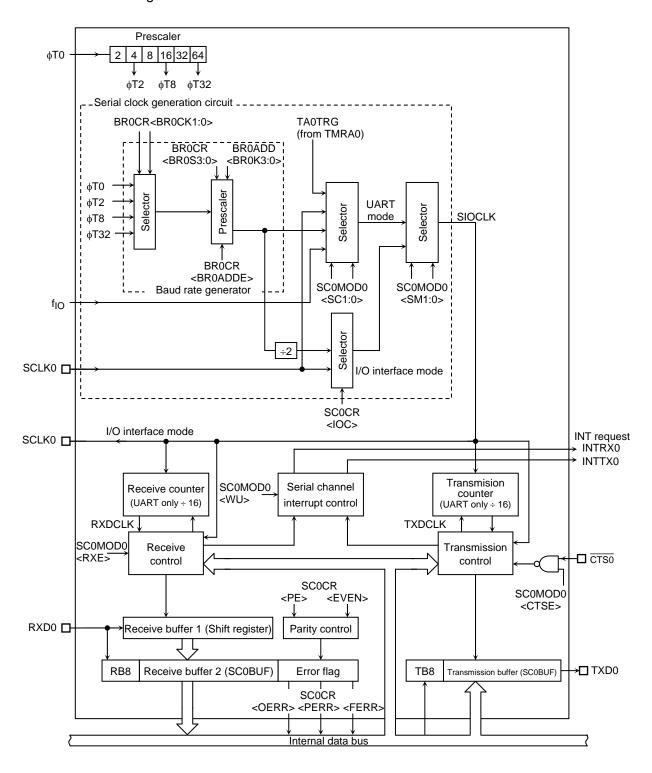

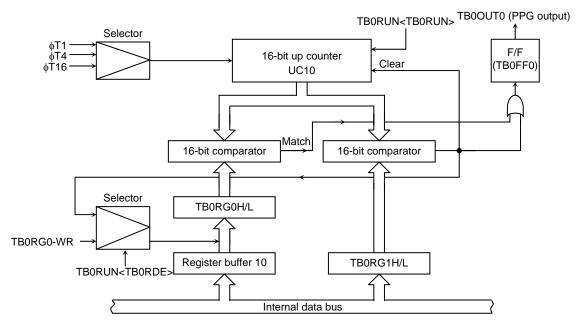

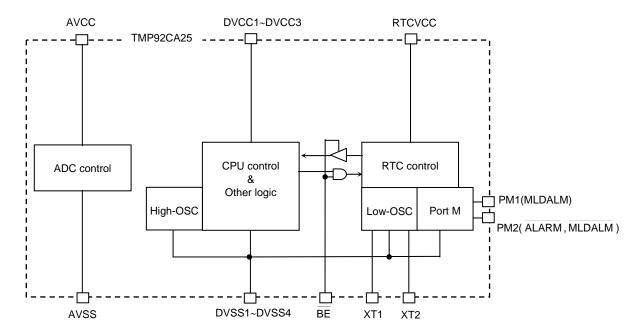

Figure 1.1 TMP92CA25 Block Diagram

# 2. Pin Assignment and Functions

The assignment of input/output pins for the TMP92CA25FG, their names and functions are as follows:

# 2.1 Pin Assignment

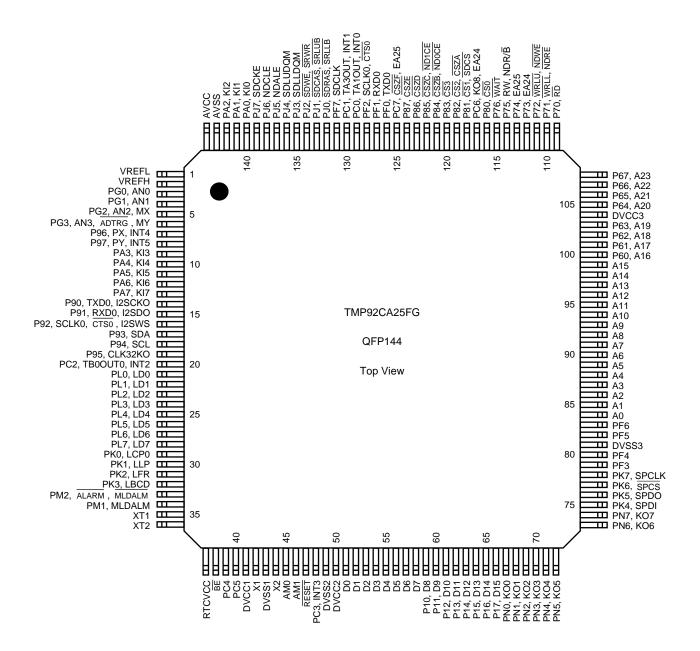

Figure 2.1.1 shows the pin assignment of the TMP92CA25FG.

Figure 2.1.1 Pin Assignment Diagram (144-pin QFP)

# 2.2 PAD Assignment

(Chip size 4.98 mm  $\times$  5.61 mm)

Table 2.2.1 Pad Assignment Diagram (144-pin chip)

Unit: µm

| Pin No.         Name         X point         Y point Point No.         Pin No.         Name Point Point No.         X point Point No.         Pin No.         Name Point No.         X Point Point No.         Pin No.         Name Point No.         Name | 2359<br>2359<br>2359<br>2359<br>2359<br>2359<br>2359 | Y<br>point<br>822<br>939<br>1055<br>1171 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------|

| 1     VREFL     -2363     2309     49     DVSS2     -447     -2678     97     A13       2     VREFH     -2363     2189     50     DVCC2     -297     -2678     98     A14       3     PG0     -2363     1934     51     D0     -172     -2678     99     A15       4     PG1     -2363     1593     52     D1     -72     -2678     100     P60       5     PG2     -2363     1493     53     D2     28     -2678     101     P61       6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2359<br>2359<br>2359<br>2359<br>2359<br>2359         | 822<br>939<br>1055                       |

| 2     VREFH     -2363     2189     50     DVCC2     -297     -2678     98     A14       3     PG0     -2363     1934     51     D0     -172     -2678     99     A15       4     PG1     -2363     1593     52     D1     -72     -2678     100     P60       5     PG2     -2363     1493     53     D2     28     -2678     101     P61       6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2359<br>2359<br>2359<br>2359<br>2359                 | 939<br>1055                              |

| 3     PG0     -2363     1934     51     D0     -172     -2678     99     A15       4     PG1     -2363     1593     52     D1     -72     -2678     100     P60       5     PG2     -2363     1493     53     D2     28     -2678     101     P61       6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2359<br>2359<br>2359<br>2359                         | 1055                                     |

| 4     PG1     -2363     1593     52     D1     -72     -2678     100     P60       5     PG2     -2363     1493     53     D2     28     -2678     101     P61       6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2359<br>2359<br>2359                                 |                                          |

| 5     PG2     -2363     1493     53     D2     28     -2678     101     P61       6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2359<br>2359                                         | 1171                                     |

| 6     PG3     -2363     1393     54     D3     128     -2678     102     P62       7     P96     -2363     1293     55     D4     228     -2678     103     P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2359                                                 | 4000                                     |

| 7 P96 -2363 1293 55 D4 228 -2678 103 P63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 1288                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      | 1400                                     |

| 8 DU/ 1 73631 1107 56 1 15 1 2001 7670 107 107 107 107 107 107 107 107 107 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2359                                                 | 1514                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                    | 1643                                     |

| 9 PA3 -2363 1088 57 D6 429 -2678 105 P64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2359                                                 | 1779                                     |

| 10 PA4 -2363 988 58 D7 529 -2678 106 P65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2359                                                 | 1902                                     |

| 11 PA5 -2363 888 59 P10 629 -2678 107 P66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2359                                                 | 2027                                     |

| 12 PA6 -2363 788 60 P11 729 -2678 108 P67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2359                                                 | 2309                                     |

| 13 PA7 -2363 688 61 P12 829 -2678 109 P70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1994                                                 | 2675                                     |

| 14 P90 -2363 587 62 P13 929 -2678 110 P71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1874                                                 | 2675                                     |

| 15 P91 -2363 487 63 P14 1029 -2678 111 P72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1753                                                 | 2675                                     |

| 16 P92 -2363 387 64 P15 1129 -2678 112 P73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1633                                                 | 2675                                     |

| 17 P93 -2363 287 65 P16 1229 -2678 113 P74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1527                                                 | 2675                                     |

| 18 P94 -2363 187 66 P17 1329 -2678 114 P75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1420                                                 | 2675                                     |

| 19 P95 -2363 87 67 PN0 1429 -2678 115 P76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1316                                                 | 2675                                     |

| 20 PC2 -2363 -13 68 PN1 1529 -2678 116 P80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1211                                                 | 2675                                     |

| 21 PL0 -2363 -113 69 PN2 1630 -2678 117 PC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1104                                                 | 2675                                     |

| 22 PL1 -2363 -213 70 PN3 1753 -2678 118 P81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 999                                                  | 2675                                     |

| 23 PL2 -2363 -313 71 PN4 1873 -2678 119 P82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 893                                                  | 2675                                     |

| 24         PL3         -2363         -413         72         PN5         1994         -2678         120         P83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 787                                                  | 2675                                     |

| 25 PL4 -2363 -514 73 PN6 2359 -2313 121 P84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 682                                                  | 2675                                     |

| 26         PL5         -2363         -614         74         PN7         2359         -2049         122         P85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 574                                                  | 2675                                     |

| 27 PL6 -2363 -714 75 PK4 2359 -1708 123 P86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 468                                                  | 2675                                     |

| 28 PL7 -2363 -814 76 PK5 2359 -1587 124 P87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 363                                                  | 2675                                     |

| 29 PK0 -2363 -914 77 PK6 2359 -1472 125 PC7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 259                                                  | 2675                                     |

| 30 PK1 -2363 -1014 78 PK7 2359 -1359 126 PF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 154                                                  | 2675                                     |

| 31 PK2 -2363 -1114 79 PF3 2359 -1243 127 PF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                   | 2675                                     |

| 32 PK3 -2363 -1215 80 PF4 2359 -1131 128 PF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -55                                                  | 2675                                     |

| 33 PM2 -2363 -1473 81 DVSS3 2359 -1012 129 PC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -158                                                 | 2675                                     |

| 34 PM1 -2363 -1594 82 PF5 2359 -885 130 PC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -261                                                 | 2675                                     |

| 35 XT1 -2363 -1935 83 PF6 2359 -749 131 PF7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -364                                                 | 2675                                     |

| 36 XT2 -2363 -2313 84 A0 2359 -639 132 PJ0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -467                                                 | 2675                                     |

| 37 RTCVCC -1986 -2678 85 A1 2359 -530 133 PJ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -568                                                 | 2675                                     |

| 38 BE -1853 -2678 86 A2 2359 -420 134 PJ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -669                                                 | 2675                                     |

| 39 PC4 -1732 -2678 87 A3 2359 -311 135 PJ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -771                                                 | 2675                                     |

| 40 PC5 -1612 -2678 88 A4 2359 -199 136 PJ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -872                                                 | 2675                                     |

| 41 DVCC1 -1499 -2678 89 A5 2359 -88 137 PJ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -972                                                 | 2675                                     |

| 42 X1 -1386 -2678 90 A6 2359 23 138 PJ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1074                                                | 2675                                     |

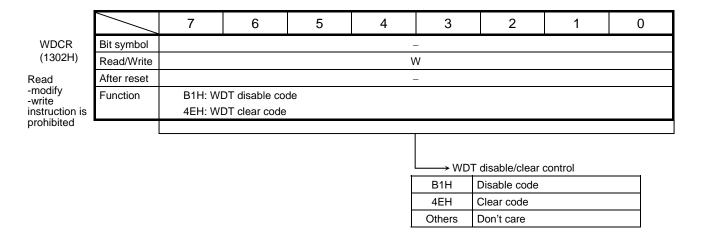

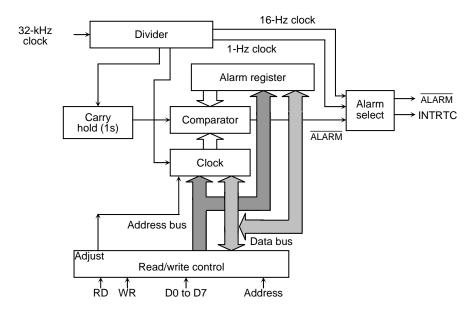

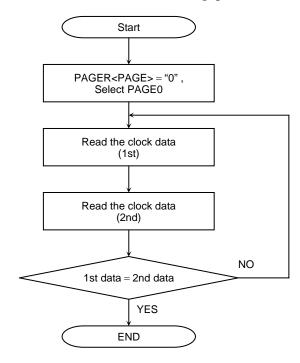

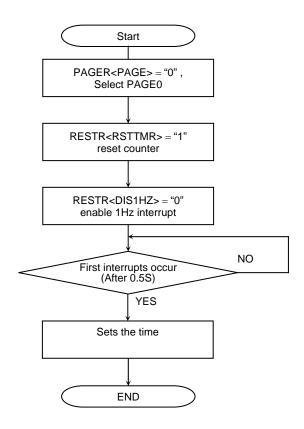

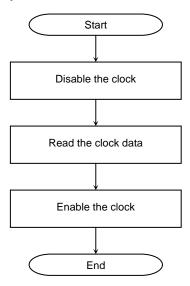

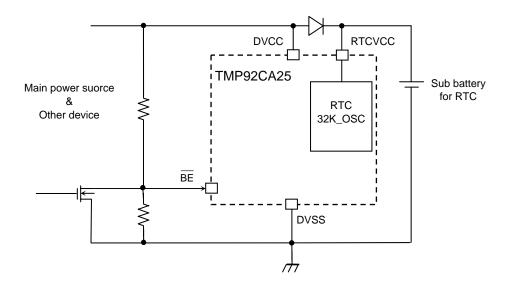

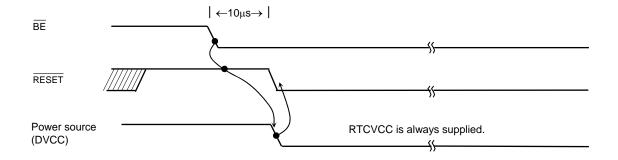

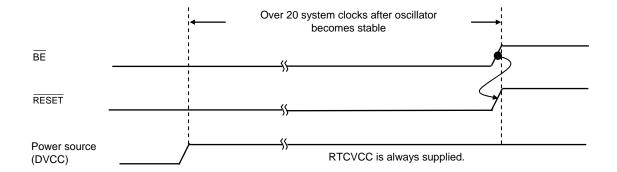

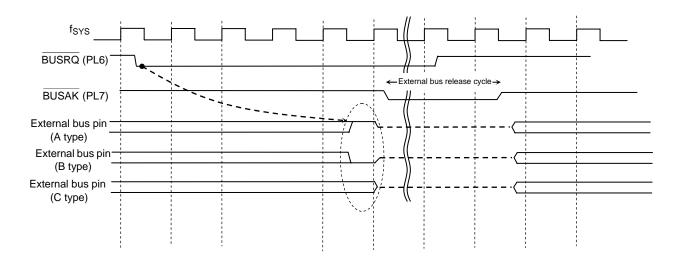

| 43 DVSS1 -1261 -2678 91 A7 2359 134 139 PJ7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1175                                                | 2675                                     |