## SC905A CDMA Cellular Phone Power Management IC

## POWER MANAGEMENT

#### Description

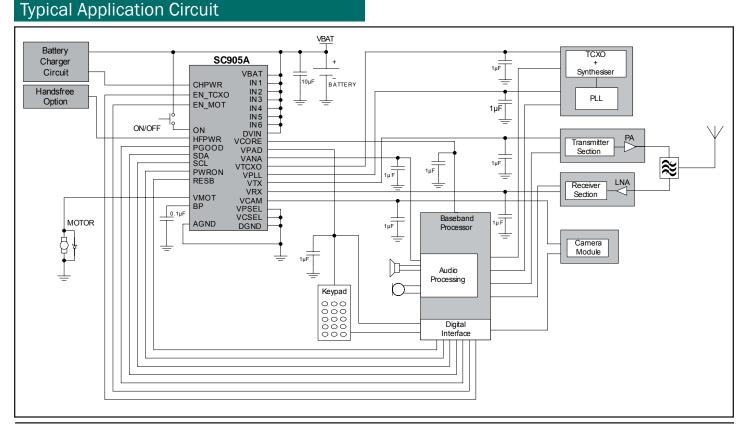

The SC905A is a power management integrated circuit (PMIC) designed for the latest CDMA chip sets. The device provides four general purpose low dropout regulators (LDOs), and five low noise LDOs designed for analog circuits. The VMOT LDO can be used as a general purpose regulator or as an adjustable motor drive output that can supply up to 150mA to drive a vibrator motor.

Each LDO's enable and output voltage are controlled via the  $I^2C$  bus. The VTCXO output has an external enable pin that can be used instead of the register bit when timing is critical for minimizing sleep current. The VMOT also has an external enable pin for additional flexibility.

Initial power-on is achieved by activating either the ON button, the battery charger, or the HFPWR signal, and the PGOOD input is used by the microprocessor to latch power on or disable the device.

The thermally-efficient MLPQ-32 package combined with miniature ceramic bypass capacitors minimize required PCB area, making the SC905A ideal for space-conscious portable applications.

### Features

- 9 LDO Linear Regulators

- CORE: 1.35V 2.90V @ 300mA

- ANA: 2.55V 2.90V @ 200mA

- PAD: 1.75V 3.30V @ 300mA

- RX: 2.75V 3.10V @ 150mA

- TX: 2.75V 3.10V @ 150mA

- ◆ TCX0: 2.75V 3.10V @ 80mA

- PLL: 2.75V 3.10V @ 80mA

- Camera: 1.75V 3.30V @ 100mA

- Motor Drive: 1.75V 3.30V @ 150mA

- I<sup>2</sup>C Interface for Microprocessor Control

- Less than 1µA Quiescent Current in Shutdown

- 65dB PSRR for Analog LDOs

- Over-Temperature Protection

- Power-On Control

- Small 5mm x 5mm 32-Pin MLPQ Package

#### Applications

- CDMA Cellular Handsets

- PDAs/Smartphones

- Wireless VOIP Handsets

SC905A

## POWER MANAGEMENT

### Absolute Maximum Ratings

EMTECH

Exceeding the specifications below may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                                             | Symbol            | Maximum                      | Units |

|-------------------------------------------------------|-------------------|------------------------------|-------|

| Input Supply Voltage                                  | V <sub>IN</sub>   | -0.3 to +7                   | V     |

| Digital Input Voltage                                 | V <sub>DIG</sub>  | -0.3 to V <sub>IN</sub> +0.3 | V     |

| Operating Ambient Temperature Range                   | T <sub>A</sub>    | -40 to +85                   | °C    |

| Operating Junction Temperature Range                  | TJ                | -40 to +125                  | °C    |

| Peak IR Reflow Temperature                            | T <sub>LEAD</sub> | 260                          | °C    |

| Storage Temperature                                   | Т <sub>stg</sub>  | -60 to +150                  | °C    |

| Thermal Resistance Junction to Ambient <sup>(1)</sup> | θ <sub>JA</sub>   | 26                           | °C/W  |

| ESD Protection Level <sup>(2)</sup>                   | ESD               | 2                            | kV    |

Notes:

(1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad as per JESD51 standards. (2) Tested according to JEDEC standard JESD22-A114-B.

#### **Electrical Characteristics**

Unless otherwise noted V<sub>IN</sub> = 3.7V, T<sub>A</sub> = -40 to +85 °C. Typical values are at T<sub>A</sub> = +25 °C.

| Parameter                              | Symbol              | Condition                                                                              | Min  | Тур  | Max | Units |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------|------|------|-----|-------|

| General                                |                     | ·                                                                                      |      |      |     |       |

| Supply Voltage                         | V <sub>IN</sub>     |                                                                                        | 2.7  |      | 5.5 | V     |

| Shutdown Current                       | I <sub>sd</sub>     | ON = 0V, HFPWR = 0V, CHPWR = 0V,<br>PGOOD = 0V                                         |      |      | 1   | μA    |

| Quiescent Supply Current               | l <sub>su</sub>     | Default Start-Up Mode                                                                  |      | 300  |     | μA    |

|                                        | I <sub>STBY</sub>   | $I^{2}C$ , $V_{REF}$ Active, All Outputs Disabled                                      |      | 30   | 60  | μA    |

| Supply Bypass Capacitor                | C <sub>vcc</sub>    | At Each Power Input Pin                                                                |      | 1    |     | μF    |

| Start-Up Time                          | t <sub>su</sub>     | C <sub>BP</sub> = 0.1μF                                                                |      | 25   |     | ms    |

| Under-Voltage Lockout                  | UVLO                | Descending, Hysteresis = 50mV                                                          |      | 2.5  |     | V     |

| Over-Temperature                       | ОТ                  | Hysteresis = 20°C                                                                      |      | 160  |     | °C    |

| Digital Inputs                         | •                   | •                                                                                      | •    |      |     |       |

| Digital Input Voltage <sup>(1)</sup>   | V <sub>IL</sub>     |                                                                                        |      |      | 0.4 | V     |

|                                        | V <sub>IH</sub>     |                                                                                        | 1.25 |      |     | V     |

| Digital Input Current                  | I <sub>DIG</sub>    | Logic Level High or Low                                                                | -0.2 |      | 0.2 | μA    |

| Digital Outputs                        | -                   |                                                                                        | -    | -    | -   |       |

| Disital Output Valtage <sup>(2)</sup>  | V <sub>ol</sub>     | I <sub>SINK</sub> = 1.2mA                                                              |      | 2    | 10  | %VPAD |

| Digital Output Voltage <sup>(2)</sup>  | V <sub>OH</sub>     | I <sub>SOURCE</sub> = 0.5mA, VPAD ≥ 1.8V                                               | 90   | 98   |     | %VPAD |

| LDO Regulator (CORE) - 300             | mA                  | •                                                                                      |      |      |     |       |

| Output Voltage Accuracy <sup>(3)</sup> | ΔV <sub>OUT</sub>   | $1.35V \le V_{OUT} \le 2.90V, I_{OUT} = 1mA,$<br>$V_{OUT} + 0.35V \le V_{IN} \le 5.5V$ |      |      | +75 | mV    |

| Current Limit                          | I                   | V <sub>CORE</sub> = 0V                                                                 | 350  |      | 900 | mA    |

|                                        | V <sub>OUT-HI</sub> | VCSEL - High                                                                           |      | 1.80 |     | V     |

| Default At Start-Up: ON                | V <sub>OUT-LO</sub> | VCSEL - Low                                                                            |      | 1.35 |     | V     |

## **POWER MANAGEMENT**

## Electrical Characteristics (Cont.)

| Parameter                              | Symbol               | Condition                                                                                                     | Min | Тур  | Max | Units             |

|----------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| LDO Regulator (CORE) - 300m            | nA (Cont.)           |                                                                                                               |     |      |     |                   |

| Line Regulation                        | REG                  | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> +0.35V < V <sub>IN</sub> < 5.5V                                      |     | 2.5  | 12  | mV                |

| Load Regulation                        |                      | 1mA < I <sub>out</sub> < 300mA                                                                                |     | -3   | -30 | mV                |

| Dropout Voltage                        | V <sub>DO</sub>      | V <sub>OUT</sub> = 2.90V, I <sub>OUT</sub> = 300mA                                                            |     | 300  | 350 | mV                |

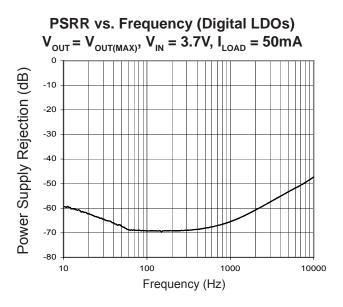

| Power Supply Rejection Ratio           | PSRR <sub>CORE</sub> | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                                              |     | 50   |     | dB                |

| LDO Regulator (PAD) - 300mA            | <u> </u>             |                                                                                                               |     |      |     |                   |

| Output Voltage Accuracy <sup>(3)</sup> | $\Delta V_{OUT}$     | 1.75V ≤ V <sub>OUT</sub> ≤ 3.30V, I <sub>OUT</sub> =1mA,<br>V <sub>OUT</sub> +0.35V ≤ V <sub>IN</sub> ≤ 5.5V  | -75 |      | +75 | mV                |

| Current Limit                          | I <sub>LIM</sub>     | V <sub>PAD</sub> = 0V                                                                                         | 350 |      | 900 | mA                |

| Default at Start-Up: ON                | V <sub>OUT-HI</sub>  | VPSEL - High                                                                                                  |     | 3.00 |     | V                 |

| Delaut at Start-Op. ON                 | V <sub>OUT-LO</sub>  | VPSEL - Low                                                                                                   |     | 2.20 |     | V                 |

| Line Regulation                        | REG                  | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> +0.35V < V <sub>IN</sub> < 5.5V                                      |     | 2.5  | 12  | mV                |

| Load Regulation                        | $REG_{LOAD}$         | 1mA < I <sub>out</sub> < 300mA                                                                                |     | -3   | -30 | mV                |

| Dropout Voltage                        | V <sub>DO</sub>      | V <sub>OUT</sub> = 3.30V, I <sub>OUT</sub> = 300mA                                                            |     | 300  | 350 | mV                |

| Power Supply Rejection Ratio           | PSRR <sub>PAD</sub>  | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                                              |     | 50   |     | dB                |

| LDO Regulator (ANA) - 200mA            | N                    |                                                                                                               |     | -    |     |                   |

| Output Voltage Accuracy <sup>(4)</sup> | $\Delta V_{out}$     | $2.55V \le V_{OUT} \le 2.90V, I_{OUT} = 1mA, V_{OUT} + 0.35V \le V_{IN} \le 5.5V$                             | -75 |      | +75 | mV                |

| Current Limit                          | I <sub>LIM</sub>     | $V_{ANA} = 0V$                                                                                                | 250 |      | 650 | mA                |

| Default At Start-Up: ON                | V <sub>OUT</sub>     |                                                                                                               |     | 2.60 |     | V                 |

| Line Regulation                        | REG                  | $I_{_{ m OUT}}$ = 1mA, $V_{_{ m OUT}}$ +0.35V $$ < $V_{_{ m IN}}$ < 5.5V                                      |     | 2.5  | 12  | mV                |

| Load Regulation                        |                      | 1mA < I <sub>out</sub> < 200mA                                                                                |     | -3   | -20 | mV                |

| Dropout Voltage                        | V <sub>DO</sub>      | V <sub>OUT</sub> = 2.90V, I <sub>OUT</sub> = 200mA                                                            |     | 200  | 250 | mV                |

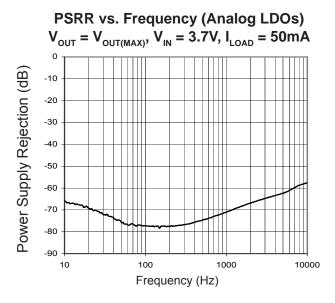

| Power Supply Rejection Ratio           | PSRR                 | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                                              |     | 65   |     | dB                |

| Output Voltage Noise                   | e <sub>n</sub>       | f = 10Hz to 100kHz, $I_{OUT}$ = 50mA,<br>$C_{BP}$ = 0.1µF, $C_{OUT}$ = 1µF                                    |     | 45   |     | $\mu V_{_{RMS}}$  |

| LDO Regulator (TCXO) - 80m             | A                    |                                                                                                               |     |      |     |                   |

| Output Voltage Accuracy <sup>(4)</sup> | $\Delta V_{OUT}$     | 2.75V ≤ V <sub>OUT</sub> ≤ 3.10V, I <sub>OUT</sub> = 1mA,<br>V <sub>OUT</sub> +0.35V ≤ V <sub>IN</sub> ≤ 5.5V | -75 |      | +75 | mV                |

| Current Limit                          | I                    | V <sub>TCXO</sub> = 0V                                                                                        | 250 |      | 650 | mA                |

| Default At Start-Up: ON                | V <sub>OUT</sub>     |                                                                                                               |     | 3.05 |     | V                 |

| Line Regulation                        | REG <sub>LINE</sub>  | I <sub>ουτ</sub> = 1mA, V <sub>ουτ</sub> +0.35V < V <sub>IN</sub> < 5.5V                                      |     | 2.5  | 12  | mV                |

| Load Regulation                        | REG                  | 1mA < I <sub>OUT</sub> < 80mA                                                                                 |     | -3   | -20 | mV                |

| Dropout Voltage                        | V <sub>DO</sub>      | V <sub>OUT</sub> = 3.10V, I <sub>OUT</sub> = 80mA                                                             |     | 200  | 250 | mV                |

| Power Supply Rejection Ratio           | PSRR <sub>TCXO</sub> | $f = 10Hz - 1kHz, C_{OUT} = 1\mu F, I_{OUT} = 50mA$                                                           |     | 65   |     | dB                |

| Output Voltage Noise                   | e <sub>n</sub>       | $f = 10Hz - 100kHz, I_{OUT} = 50mA,$<br>$C_{BP} = 0.1\mu F, C_{OUT} = 1\mu F$                                 |     | 45   |     | μV <sub>RMS</sub> |

## **POWER MANAGEMENT**

## Electrical Characteristics (Cont.)

| Parameter                              | Symbol              | Condition                                                                                      | Min | Тур  | Max | Units            |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------------------|

| LDO Regulator (TX) - 150mA             |                     |                                                                                                |     |      |     |                  |

| Output Voltage Accuracy <sup>(4)</sup> | ΔV <sub>out</sub>   | $2.75V \le V_{OUT} \le 3.10V, I_{OUT} = 1mA, V_{OUT} + 0.35V \le V_{IN} \le 5.5V$              | -75 |      | +75 | mV               |

| Current Limit                          | I <sub>LIM</sub>    | $V_{TX} = 0V$                                                                                  | 250 |      | 650 | mA               |

| Default At Start-Up: OFF               | V <sub>OUT</sub>    |                                                                                                |     | 3.05 |     | V                |

| Line Regulation                        |                     | $I_{out}$ = 1mA, $V_{out}$ +0.35V < $V_{IN}$ < 5.5V                                            |     | 2.5  | 12  | mV               |

| Load Regulation                        | $REG_{LOAD}$        | 1mA < I <sub>out</sub> < 150mA                                                                 |     | -3   | -20 | mV               |

| Dropout Voltage                        | V <sub>DO</sub>     | V <sub>OUT</sub> = 3.10V, I <sub>OUT</sub> = 150mA                                             |     | 200  | 250 | mV               |

| Power Supply Rejection Ratio           | $PSRR_{TX}$         | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                               |     | 65   |     | dB               |

| Output Voltage Noise                   | e <sub>n</sub>      | f = 10Hz - 100kHz, Ι <sub>ουτ</sub> = 50mA,<br>C <sub>BP</sub> = 0.1μF, C <sub>ουτ</sub> = 1μF |     | 45   |     | $\mu V_{_{RMS}}$ |

| LDO Regulator (RX) - 150mA             |                     | -                                                                                              |     |      | -   |                  |

| Output Voltage Accuracy <sup>(4)</sup> | $\Delta V_{out}$    | $2.75V \le V_{OUT} \le 3.10V, I_{OUT} = 1mA, V_{OUT} + 0.35V \le V_{IN} \le 5.5V$              | -75 |      | +75 | mV               |

| Current Limit                          | I <sub>LIM</sub>    | V <sub>RX</sub> = 0V                                                                           | 250 |      | 650 | mA               |

| Default At Start-Up: OFF               | V <sub>OUT</sub>    |                                                                                                |     | 3.05 |     | V                |

| Line Regulation                        |                     | I <sub>ουτ</sub> = 1mA, V <sub>ουτ</sub> +0.35V < V <sub>IN</sub> < 5.5V                       |     | 2.5  | 12  | mV               |

| Load Regulation                        |                     | 1mA < I <sub>out</sub> < 150mA                                                                 |     | -3   | -20 | mV               |

| Dropout Voltage                        | V <sub>DO</sub>     | V <sub>OUT</sub> = 3.10V, I <sub>OUT</sub> = 150mA                                             |     | 200  | 250 | mV               |

| Power Supply Rejection Ratio           | PSRR <sub>RX</sub>  | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                               |     | 65   |     | dB               |

| Output Voltage Noise                   | e <sub>n</sub>      | f = 10Hz - 100kHz, $I_{OUT}$ = 50mA,<br>$C_{BP}$ = 0.1µF, $C_{OUT}$ = 1µF                      |     | 45   |     | $\mu V_{_{RMS}}$ |

| LDO Regulator (CAM) - 100m             | 4                   | •                                                                                              | L   | I    |     |                  |

| Output Voltage Accuracy <sup>(3)</sup> | $\Delta V_{OUT}$    | $1.75V \le V_{OUT} \le 3.30V, I_{OUT} = 1mA$<br>$V_{OUT} + 0.35V \le V_{IN} \le 5.5V$          | -75 |      | +75 | mV               |

| Current Limit                          | I <sub>LIM</sub>    | V <sub>CAM</sub> = 0V                                                                          | 250 |      | 650 | mA               |

| Default At Start-Up: OFF               | V <sub>OUT</sub>    |                                                                                                |     | 2.20 |     | V                |

| Line Regulation                        | REG                 | I <sub>ουτ</sub> = 1mA, V <sub>ουτ</sub> +0.35V < V <sub>IN</sub> < 5.5V                       |     | 2.5  | 12  | mV               |

| Load Regulation                        | REG <sub>LOAD</sub> | 1mA < I <sub>оит</sub> < 100mA                                                                 |     | -3   | -20 | mV               |

| Dropout Voltage                        | V <sub>DO</sub>     | V <sub>OUT</sub> = 3.30V, I <sub>OUT</sub> = 100mA                                             |     | 200  | 250 | mV               |

| Power Supply Rejection Ratio           | PSRR                | f = 10Hz - 1kHz, C <sub>ουτ</sub> = 1μF, I <sub>ουτ</sub> = 50mA                               |     | 50   |     | dB               |

| LDO Regulator (PLL) - 80mA             |                     |                                                                                                |     |      |     |                  |

| Output Voltage Accuracy <sup>(4)</sup> | $\Delta V_{OUT}$    | $2.75V \le V_{OUT} \le 3.10V, I_{OUT} = 1mA, V_{OUT} + 0.35V \le V_{IN} \le 5.5V$              | -75 |      | +75 | mV               |

| Current Limit                          | I <sub>LIM</sub>    | V <sub>PLL</sub> = 0V                                                                          | 250 |      | 650 | mA               |

## POWER MANAGEMENT

## Electrical Characteristics (Cont.)

| Parameter                              | Symbol              | Condition                                                                                      | Min | Тур  | Max | Units            |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------------------|

| Default At Start-Up: OFF               | V <sub>OUT</sub>    |                                                                                                |     | 3.05 |     | V                |

| Line Regulation                        | REG                 | I <sub>ουτ</sub> = 1mA, V <sub>ουτ</sub> +0.35V < V <sub>IN</sub> < 5.5V                       |     | 2.5  | 12  | mV               |

| Load Regulation                        |                     | 1mA < I <sub>out</sub> < 80mA                                                                  |     | -3   | -20 | mV               |

| Dropout Voltage                        | V <sub>DO</sub>     | V <sub>OUT</sub> = 3.10V, I <sub>OUT</sub> = 80mA                                              |     | 200  | 250 | mV               |

| Power Supply Rejection Ratio           | PSRR <sub>PLL</sub> | f = 10Hz - 1kHz, C <sub>out</sub> = 1µF, I <sub>out</sub> = 50mA                               |     | 65   |     | dB               |

| Output Voltage Noise                   | e <sub>n</sub>      | f = 10Hz - 100kHz, Ι <sub>ουτ</sub> = 50mA,<br>C <sub>BP</sub> = 0.1μF, C <sub>ουτ</sub> = 1μF |     | 45   |     | $\mu V_{_{RMS}}$ |

| LDO Regulator (MOT) - 150m             | A                   |                                                                                                |     |      |     |                  |

| Output Voltage Accuracy <sup>(3)</sup> | $\Delta V_{OUT}$    | $1.75V \le V_{OUT} \le 3.30V, I_{OUT} = 1mA, V_{OUT} + 0.35V \le V_{IN} \le 5.5V$              | -75 |      | +75 | mV               |

| Current Limit                          | I <sub>LIM</sub>    | V <sub>MOT</sub> = 0V                                                                          | 250 |      | 650 | mA               |

| Default at Start-Up: OFF               | V <sub>OUT</sub>    |                                                                                                |     | 1.80 |     | V                |

| Line Regulation                        |                     | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> +0.35V < V <sub>IN</sub> < 5.5V                       |     | 2.5  | 12  | mV               |

| Load Regulation                        |                     | 1mA < I <sub>оит</sub> < 150mA                                                                 |     | -3   | -20 | mV               |

| Dropout Voltage                        | V <sub>DO</sub>     | V <sub>OUT</sub> = 3.30V, I <sub>OUT</sub> = 150mA                                             |     | 200  | 250 | mV               |

| Power Supply Rejection Ratio           | PSRR <sub>MOT</sub> | f = 10Hz - 1kHz, C <sub>out</sub> = 1µF, I <sub>out</sub> = 50mA                               |     | 50   |     | dB               |

## **POWER MANAGEMENT**

### **Electrical Characteristics (Cont.)**

| Parameter                                                                    | Symbol                             | Condition                                           | Min         | Тур         | Мах         | Units |

|------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------|-------------|-------------|-------------|-------|

| I <sup>2</sup> C Interface <sup>(5)</sup><br>Interface complies with slave m | node l <sup>2</sup> C interface as | described by Philips I <sup>2</sup> C specification | n version 2 | 2.1 dated J | anuary, 200 | 00.   |

|                                                                              | V <sub>IL</sub>                    |                                                     |             |             | 0.4         | V     |

| Digital Input Voltage                                                        | V <sub>IH</sub>                    |                                                     | 1.25        |             |             | V     |

| SDA Output Low Level                                                         |                                    | $I_{_{DIN}}$ (SDA) $\leq$ 3mA                       |             |             | 0.4         | V     |

| Digital Input Current                                                        | I <sub>DG</sub>                    |                                                     | -0.2        |             | 0.2         | μA    |

| Hysteresis of Schmitt<br>Trigger Inputs                                      | V <sub>HYS</sub>                   |                                                     |             | 0.1         |             | V     |

| Maximum Glitch<br>Pulse Rejection                                            | t <sub>sP</sub>                    |                                                     |             | 50          |             | ns    |

| I/O Pin Capacitance                                                          | C <sub>IN</sub>                    |                                                     |             | 10          |             | pF    |

| I <sup>2</sup> C Timing <sup>(5)</sup>                                       |                                    |                                                     |             |             |             |       |

| Clock Frequency                                                              | SCL                                |                                                     |             | 400         | 440         | kHz   |

| SCL Low Period                                                               | t <sub>LOW</sub>                   |                                                     | 1.3         |             |             | μs    |

| SCL High Period                                                              | t <sub>HIGH</sub>                  |                                                     | 0.6         |             |             | μs    |

| Data Hold Time                                                               | t <sub>HD_DAT</sub>                |                                                     | 0           |             |             | μs    |

| Data Setup Time                                                              | t <sub>su_dat</sub>                |                                                     | 100         |             |             | ns    |

| Setup Time for Repeated START Condition                                      | t <sub>su_sta</sub>                |                                                     | 0.6         |             |             | μs    |

| Hold Time for Repeated START Condition                                       | t <sub>HD_STA</sub>                |                                                     | 0.6         |             |             | μs    |

| Setup Time for<br>STOP Condition                                             | t <sub>su_sто</sub>                |                                                     | 0.6         |             |             | μs    |

| Bus-Free Time Between<br>STOP and START                                      | t <sub>BUF</sub>                   |                                                     | 1.3         |             |             | μs    |

| RESET Timeout Delay                                                          | t <sub>RD</sub>                    |                                                     | 75          | 100         | 125         | ms    |

| Power-up Delay Between<br>PAD, ANA, TXCO                                     | t <sub>DELAY</sub>                 | Delay Between<br>Each Output Activating             |             | 100         |             | μs    |

| Maximum Glitch<br>Pulse Rejection                                            | t <sub>sP</sub>                    |                                                     |             | 50          |             | ns    |

| Interface Start-up Time                                                      | t <sub>en</sub>                    | Bus Start-up Time After EN Pin<br>is Pulled High    |             |             | 350         | μs    |

Notes:

(1) Applies to pin names, ON, HFPWR, CHPWR, PGOOD, VCSEL, VPSEL, EN\_MOT, EN\_TCXO.

(2) Applies to pin names, PWRON, RESB.

(2) Applied by inflations, Puriod

(3) For V<sub>out</sub> settings see Table A.

(4) For V<sub>out</sub> settings see Table B.

(5) Guaranteed by design.

## SC905A

## POWER MANAGEMENT

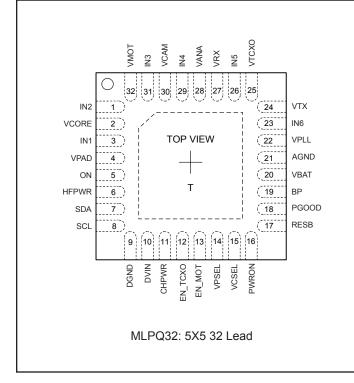

## **Pin Configuration**

## Ordering information

| DEVICE                        | PACKAGE          |

|-------------------------------|------------------|

| SC905AMLTRT <sup>(1)(2)</sup> | MLP 5x5 32L      |

| SC905AEVB                     | Evaluation Board |

#### Notes:

(1) Available in tape and reel only. A reel contains 3,000 devices.(2) Available in lead-free package only. Device is WEEE and RoHS compliant.

SEMTECH

## **Pin Descriptions**

| Pin # | Pin Name    | I/O          | Pin Function                                                                                           |

|-------|-------------|--------------|--------------------------------------------------------------------------------------------------------|

| 1     | IN2         | Input        | Input voltage terminal to VCORE LDO.                                                                   |

| 2     | VCORE       | Output       | 300mA LDO output for MSM core processor supply.                                                        |

| 3     | IN1         | Input        | Input voltage terminal to VPAD LDO.                                                                    |

| 4     | VPAD        | Output       | 300mA LDO PAD output to MSM I/O circuits.                                                              |

| 5     | ON          | Input        | Active high power on/off key. When the push button is closed it is shorted to battery.                 |

| 6     | HFPWR       | Input        | Power on input from accessory, active high.                                                            |

| 7     | SDA         | Input/Output | Bi-directional open drain digital I/O. I <sup>2</sup> C serial data.                                   |

| 8     | SCL         | Input        | Digital input. I <sup>2</sup> C serial clock.                                                          |

| 9     | DGND        | -            | Digital ground.                                                                                        |

| 10    | DVIN        | Input        | Main digital input voltage terminal.                                                                   |

| 11    | CHPWR       | Input        | Logic input. OR'd with ON and HFPWR.                                                                   |

| 12    | EN_TCXO     | Input        | Logic input. External enable for VTCXO LDO. State is recorded in bit 0 of the status register.         |

| 13    | EN_MOT      | Input        | Logic input. External enable for VMOT LDO. State is recorded in bit 2 of the status register.          |

| 14    | VPSEL       | Input        | Default control for VPAD LDO supply. Ground for 2.20V default, tie high for 3.00V.                     |

| 15    | VCSEL       | Input        | Default control for VCORE LDO supply. Ground for 1.35V default, tie high for 1.80V.                    |

| 16    | PWRON       | Output       | Logic OR output of ON, HFPWR and PGOOD. Active high.                                                   |

| 17    | RESB        | Output       | Reset output. Active low.                                                                              |

| 18    | PGOOD       | Input        | Logic input signal from MSM to indicate power is good, latches the SC905A on. Low disables the SC905A. |

| 19    | BP          | Output       | LDO bypass output. Bypass with a 0.1µF capacitor.                                                      |

| 20    | VBAT        | Input        | Main battery supply input terminal.                                                                    |

| 21    | AGND        | -            | Analog ground pin.                                                                                     |

| 22    | VPLL        | Output       | LDO output for PLL power.                                                                              |

| 23    | IN6         | Input        | Input voltage terminal for VPLL & VTX LDOs.                                                            |

| 24    | VTX         | Output       | LDO output for transmitter power.                                                                      |

| 25    | VTCXO       | Output       | LDO output for TCXO power.                                                                             |

| 26    | IN5         | Input        | Input voltage terminal for VTCXO & VRX LDOs.                                                           |

| 27    | VRX         | Output       | LDO output for receiver power.                                                                         |

| 28    | VANA        | Output       | LDO output for analog power.                                                                           |

| 29    | IN4         | Input        | Input voltage terminal to VANA LDO.                                                                    |

| 30    | VCAM        | Output       | LDO output for camera power.                                                                           |

| 31    | IN3         | Input        | Input voltage terminal to VCAM & VMOT LDOs.                                                            |

| 32    | VMOT        | Output       | LDO output voltage for vibrator motor power. Can also be a general purpose output.                     |

| Т     | Thermal Pad | -            | Pad for heatsinking purposes. Connect to ground plane using multiple vias. Not connected internally.   |

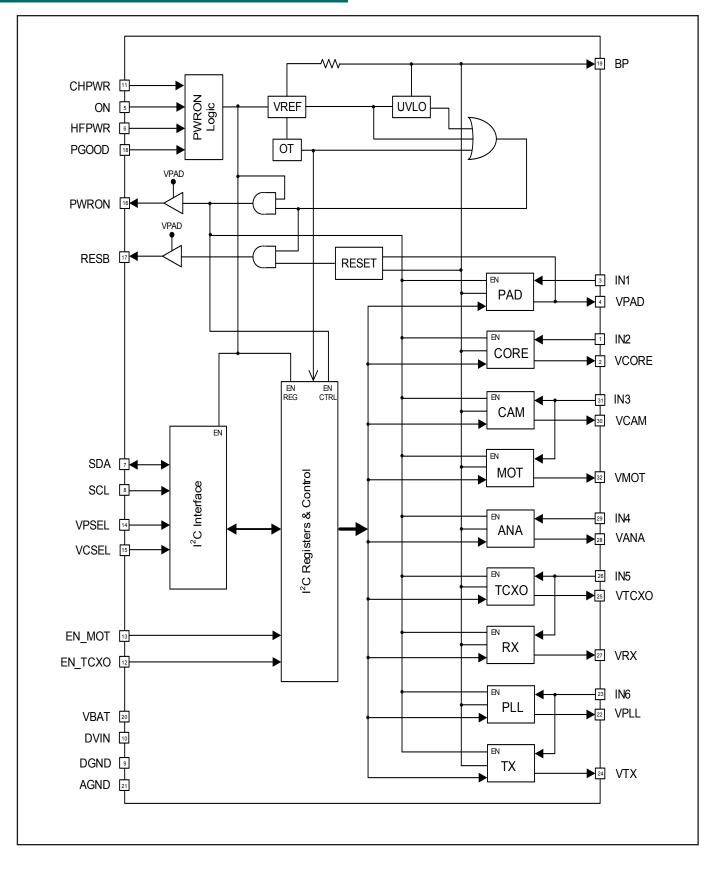

**Block Diagram**

#### Applications Information

#### **General Description**

The SC905A includes nine low dropout (LDO) voltage regulators to provide complete power regulation capability for CDMA handsets or other portable electronic equipment.

Five of the LDOs are designed to be used with analog circuitry such as audio, radio frequency, or oscillator circuits. These devices have very low noise levels and high power supply rejection. The output voltage range for four of these LDOs, VTCXO, VPLL, VTX and VRX, is 2.75V to 3.1V in 50mV steps, and for the fifth, VANA, the output voltage range is 2.55V to 2.9V in 50mV steps. The TCXO LDO has the additional feature of an external enable, EN\_TCXO, which can be used when timing is critical.

Two other LDOs are general purpose regulators designed to be used with digital circuits. The noise requirements for these LDOs are relaxed, but their voltage range is expanded to cover the wide range of voltages needed for different types of functions. The outputs for these LDOs are VCORE and VPAD.

Two other LDOs are general purpose regulators that can be used with other peripheral circuits. The VMOT and VCAM outputs can be programmed to supply from 1.75V to 3.3V in 50mV steps. The VMOT output is specifically designed to drive a vibrator motor. This output can supply up to 150mA at any of the output voltage settings, allowing designers the flexibility to select the output voltage that provides maximum vibration. The VMOT output also has its own external enable, EN\_MOT, to allow greater flexibility. When not used in conjunction with a vibrator, this output can be used as a general purpose digital regulator. The VCAM output is capable of supplying up to 100mA to drive a digital camera module or any other peripheral circuit found in a portable application.

#### **Power-On Control**

The SC905A is activated when the ON pin is pulled high, provided that the input voltage is within the specified operating range. The ON pin responds to logic-high edge triggering to power up the handset. The rising edge ON signal is latched when the CORE, PAD, ANA, and TCXO LDOs are turned on and PGOOD goes high. When the PAD LDO output voltage reaches 77% of its regulation point, the reset timer starts and the RESB signal transitions high after delay of typically 100ms. After a successful power up sequence,

any subsequent condition that toggles RESB (e.g. VPAD short-circuit, over-temperature, under voltage lockout, I<sup>2</sup>C disable of VPAD) will see a delay in the RESB transition back to high of typically 250ms. The microprocessor then raises PGOOD high to keep the SC905A powered on. There is no time limit for the MSM to activate PGOOD. If the MSM fails to raise PGOOD before the ON switch is released, the SC905A will transition back into standby mode.

Once the phone is powered on, the SC905A can only be directly powered off when the PGOOD signal goes low. Therefore, if the ON pin transitions high when the PGOOD signal is high, the LDOs and RESB signal will remain in their state until the microprocessor pulls the PGOOD signal low. Once the PGOOD signal is low, all the LDOs immediately power off and all the logic resets to the shutdown condition. The SC905A can be indirectly powered off by using the I<sup>2</sup>C command to turn off the core supply. This will result in a loss of power to the MSM causing PGOOD to go low, thus disabling the SC905A.

The HFPWR and CHPWR pins operate identically to the ON pin. These pins provide alternative sources for activating power so that remote devices such as battery chargers or system connector pins can be used to enable the device.

#### LDO Programmable Output Voltage

The output voltage of each LDO regulator is programmable. Each LDO has a program voltage register that can be accessed through the  $l^2C$  interface and the output voltage adjusted as necessary. (See the Tables on pages 14, 15 and 16 for more information.)

#### **ON/OFF Control Register**

Each individual LDO may be turned on or off by accessing the ON/OFF control register. LDOs are turned on by setting their respective on/off bits to 1 and disabled by setting the on/off bits to 0. This allows for on/off control with a single write command.

The register data is maintained when an on/off bit is toggled, but all programmed information will be lost when the PGOOD input goes low.

It should be noted that the enable signal control from the I<sup>2</sup>C for LDOs TCXO and MOT are OR'd with their respective external enable signals EN\_TCXO and EN\_MOT. This

#### Applications Information (Cont.)

means that these LDOs are on when there is a '1' in their respective bit locations (register 6, bit 3 for VTCXO, register 2, bit 6 for VMOT), or if their external enable pins are pulled HIGH. To turn these LDOs off the I<sup>2</sup>C on/off control bit must be '0' and the external enable must be pulled LOW. The state of EN\_TCXO and EN\_MOT can be established by reading bits 0 and 2, respectively, in the Status Register.

#### VCSEL & VPSEL Pin

The VCSEL & VPSEL pins set the default voltage of CORE and PAD LDOs respectively. When the VCSEL pin is set to VIN the default voltage for the CORE LDO is 1.80V. When this pin is set to GND the default voltage for the CORE LDO is 1.35V. Likewise, when the VPSEL pin is set to VIN the default voltage for the PAD LDO is 3.00V. When this pin is set to GND, the default voltage for the PAD LDO is 2.20V.

In both cases the VCSEL and VPSEL pins must be tied to GND or VIN prior to the device being powered on. This voltage cannot change on the fly by switching the pin voltage between VIN or GND once the device is on. The voltage can be changed from its default state after start-up by writing to the appropriate voltage code register.

#### **Active Shutdown**

The shutdown control bits determine how the on-chip active shutdown switches behave. Register 7 is the active shutdown control register and is used to control the shutdown behavior. Each LDO has a specific shutdown bit assigned to it. When the active shutdown bit is enabled (set to 1), the output capacitance on the LDO output is discharged by an on-chip FET when the LDO is disabled. When the active shutdown bit is disabled (set to 0), the output capacitance on the LDO output is discharged by the load. The default state for each LDO active shutdown bit is on.

#### **Default Status Bit**

In many multi-threaded environments it is necessary to maintain synchronization between the host micro-controller and the target IC. The SC905A has a default status bit (DSB) that will facilitate this task. The DSB can be useful in keeping the MSM and the SC905A synchronized. However, this is only useful if the MSM is powered by an external switching regulator such as Semtech's SC190A switching regulator.

The DSB is bit 7 of register 0, and shares this register space

with the PAD voltage control bits. The DSB is only set to 1 during power-up to indicate that the part is set to the default state. Moreover, the DSB cannot be written to a 1 through the I<sup>2</sup>C interface the way the other bits in this register can; it can only be cleared to 0 through the I<sup>2</sup>C interface. This feature prevents a software race condition by always writing to register 0 with bit 7 high when changing the PAD control voltage. To clear the bit simply write a 0 to bit 7.

#### Applying the DSB

Upon power-up, the SC905A LDOs and internal registers are set to their default state. The DSB is set to a 1 to indicate that the SC905A is in its default state. Upon reading this defaulted state condition, the MSM knows to perform whatever synchronization is needed to set the SC905A into a known user state. This user state is entered by a two-stage process.

1) The MSM writes a 0 to the DSB indicating its desire to modify the state of the SC905A. It then writes all of the correct register information to the SC905A to set it to the user state.

2) The MSM reads back all of the information to verify the data. Then it reads back the DSB again to ensure it is still set to 0. This verifies that no reset took place during the time that the multiple writes and read verifications happened. If the DSB has been reset to 1, this process needs to be repeated since the chip was reset sometime during the initialization. Once the MSM and the SC905A are synchronized, the DSB can be read back as a status check periodically, as needed. If it is ever set back to the default state, a new synchronization process is required. This handshake-style protocol makes sure that the MSM and SC905A are always synchronized.

#### LDO Power-On Sequence

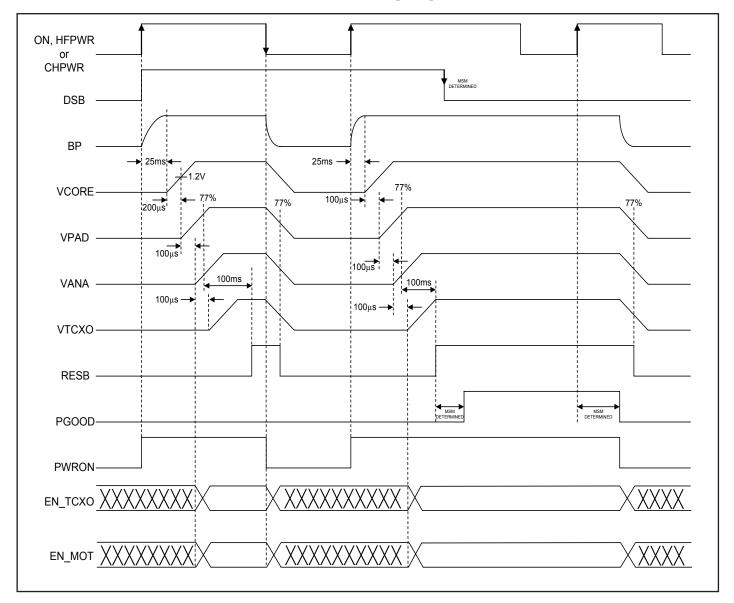

When the SC905A first turns on, the four LDOs that default on are sequenced in the following fashion: 1) CORE, 2) PAD, 3) ANA, 4) TCXO. During the power-on sequence, there is a 200µs delay between CORE and PAD to allow the output of CORE to reach 1.2V before PAD is turned on, a delay of 100µs between PAD and ANA turning on, and a delay of 100µs between ANA and TCXO turning on. This process eliminates large voltage spikes across the battery supply during power-up. (For further information on LDO power on sequencing, refer to the Timing Diagram on page 19.)

#### Applications Information (Cont.)

#### **Protection Circuitry**

The SC905A contains protection circuitry that prevents the device from operating in an unspecified state. These include Under-voltage Lockout Protection, Over-temperature Protection and Short-circuit Protection.

#### **Under-Voltage Lockout**

The SC905A provides an under-voltage lockout (UVLO) circuit to protect the device from operating in an unknown state if the input voltage supply is too low.

When the battery voltage drops below the UVLO threshold, as defined in the Electrical Characteristics section, the LDOs are disabled and RESB is held low. When the battery voltage is increased above the hysteresis level, the LDOs are re-enabled into their previous states, provided PGOOD has remained high. If PGOOD goes low, the SC905A will shut down. When powering-up with a battery voltage below the UVLO threshold, RESB will be held low.

#### **Over-Temperature Protection**

The SC905A provides an internal over-temperature (OT) protection circuit that monitors the internal junction temperature. When the temperature exceeds the OT threshold as defined in the Electrical Characteristics section, the OT protection disables all the LDO outputs, holds the RESB signal low and sets the OTF bit low in the status register. When the junction temperature drops below the hysteresis level, the OT protection resets the OTF bit high and re-enables all the LDOs in their previous states, provided PGOOD has remained high. If PGOOD goes low, the SC905A will shut down. This is only useful if the MSM is not powered by the SC905A, since during an OT fault the MSM will lose power. An external switching regulator such as Semtech's SC190A could power the MSM in the case where monitoring the OTF bit is desired.

#### **Short-Circuit Protection**

Each LDO output has short-circuit protection. If any output is short-circuited to ground, the output voltage will drop and the output current will be limited to the short circuit current until the short is removed.

#### **Status Register**

The status register monitors the OTF and the state of the external enable pins dedicated to the TCXO and MOT LDOs. The MSM can periodically poll this register to determine their status. This is a read-only register.

#### Layout Considerations

The PCB layout associated with the SC905A is straightforward, with the main consideration being given to the value and position of the input bypass capacitors. The device has eight input voltage pins which can be powered from a single supply or from a number of individual supplies depending on how much copper is available on the input voltage feed track and how much real estate is available on the PCB for components.

SC9054

If all the supply inputs are fed from one single supply trace or from a power plane, a  $10\mu$ F low ESR capacitor or two  $4.7\mu$ F low ESR capacitors should be used. Larger input capacitance and lower ESR provide better supply noise rejection and line transient response.

The copper trace to the inputs should be fairly thick in order to keep trace inductance to a minimum and the capacitors should be located as close to the SC905A as possible. If the supply trace is thin then the inputs should be treated as if they were powered from individual supplies; each input should be bypassed by at least one  $1\mu$ F low ESR capacitor located very close to each input pin.

The SC905A is designed to have excellent stability with a minimum output capacitance of  $1\mu$ F. Low ESR ceramic capacitors are recommended and should be located as close to the LDO output pins as possible.

EMTECH

## Register Map

| Register Name                     | Register<br>Address | В                | it 7                   | Bi            | t 6         | Bi           | t 5        | Bi           | t 4        | Ві     | it 3        | Bi           | it 2 | Bi          | t 1        | Bi     | it O       |     |      |

|-----------------------------------|---------------------|------------------|------------------------|---------------|-------------|--------------|------------|--------------|------------|--------|-------------|--------------|------|-------------|------------|--------|------------|-----|------|

| VPAD                              | 0                   | <u>D</u> :<br>1  | SB <sup>(1)</sup><br>0 |               | x           | х            |            | VP/          | AD 4       | VPAD 3 |             | VPAD 3       |      | VPAD 3 VPAD |            | VP/    | AD 1       | VPA | AD 0 |

|                                   |                     | Default<br>State | User<br>State          |               |             |              |            |              |            |        |             |              |      |             |            |        |            |     |      |

| VCORE                             | 1                   | 2                | x                      | ;             | <           |              | х          | VCC          | RE4        | VCC    | RE3         | VCO          | RE2  | VCO         | RE1        | VCC    | DRE0       |     |      |

| VMOT                              | 2                   | VMO              | T_EN                   | VM<br>Active  | OT<br>SHDN  |              | х          | VM           | OT4        | VM     | OT 3        | VM           | OT2  | VM          | OT1        | VM     | OT 0       |     |      |

|                                   |                     | 1                | 0                      | 1             | 0           |              |            |              |            |        |             |              |      |             |            |        |            |     |      |

|                                   |                     | ON               | OFF                    | ON            | OFF         |              |            |              |            |        |             |              |      |             |            |        |            |     |      |

| VANA //CAM                        | 3                   | VAN              | IA2                    | VAV           | NA1         | VAI          | NA0        | VC/          | AM4        | VC/    | AM 3        | VC           | AM2  | VC/         | AM1        | VCAM 0 |            |     |      |

| VTCXO/VRX                         | 4                   | :                | x                      | VR            | X2          | VF           | RX1        | VF           | RX0        | ;      | x           | VTC          | XO 2 | VTCXO1      |            | VTCXO0 |            |     |      |

| VPLL //TX                         | 5                   | :                | x                      | VT            | X2          | VI           | TX1        | VT           | X0         | ;      | x           | VPI          | LL2  | VPLL1       |            | VP     | LL0        |     |      |

| ON/OFF<br>CONTROL                 | 6                   | VPAC             | _EN                    | VCOR          | E_EN        | VAN          | A_EN       | VCA          | M_EN       | ∨тс×   | (O_EN       | VPLI         | L_EN | VTX         | _EN        | VRX    | _EN        |     |      |

| 00.111.02                         |                     | 1                | 0                      | 1             | 0           | 1            | 0          | 1            | 0          | 1      | 0           | 1            | 0    | 1           | 0          | 1      | 0          |     |      |

|                                   |                     | ON               | OFF                    | ON            | OFF         | ON           | OFF        | ON           | OFF        | ON     | OFF         | ON           | OFF  | ON          | OFF        | ON     | OFF        |     |      |

| ACTIVE <sup>(2)</sup><br>SHUTDOWN | 7                   | VP.<br>Active    |                        | VC0<br>Active | ORE<br>SHDN | VA<br>Active | NA<br>SHDN | VC<br>Active | AM<br>SHDN |        | CXO<br>SHDN | VP<br>Active |      | V<br>Active | rx<br>Shdn |        | RX<br>SHDN |     |      |

|                                   |                     | 1                | 0                      | 1             | 0           | 1            | 0          | 1            | 0          | 1      | 0           | 1            | 0    | 1           | 0          | 1      | 0          |     |      |

|                                   |                     | ON               | OFF                    | ON            | OFF         | ON           | OFF        | ON           | OFF        | ON     | OFF         | ON           | OFF  | ON          | OFF        | ON     | OFF        |     |      |

| STATUS<br>(READ ONLY)             | 8                   | :                | x                      | ;             | <           |              | x          | :            | x          | 0      | TF          | EN_          | мот  |             |            | EN_    | тсхо       |     |      |

| · · · · · ·                       |                     |                  |                        |               |             |              |            |              |            | 1      | 0           | 1            | 0    |             |            | 1      | 0          |     |      |

|                                   |                     |                  |                        |               |             |              |            |              |            | ок     | FAULT       | ON           | OFF  |             | ×          | ON     | OFF        |     |      |

Defaults are indicated in BOLD.

#### **SC905A Slave Address:**

|   | DEVICE ADDRESS |   |   |   |   |   |   |  |  |

|---|----------------|---|---|---|---|---|---|--|--|

| 0 | 0              | 0 | 1 | 0 | 0 | 0 | х |  |  |

Notes:

(1) The default status bit (DSB) is set to 1 only when the SC905A is enabled by either the HFPWR pin or the ON pin being pulled high, and it cannot be set to one through the I<sup>2</sup>C interface. When changing the VPAD control voltage, always write to register 0 with bit seven high. Set bit seven low only when the DSB is to be cleared by the MSM. This will prevent any software race condition in a multi-tasking environment. See the applications section for more information on using the DSB.

(2) The Active Shutdown defaults ON at power-up, but the registers maintain their settings as the LDOs are enabled and disabled during normal operation.

**SC905A**

#### Register Map (Cont.)

#### Digital LDO Voltage Tables A and B

A 5-bit linear DAC controls the output voltage of each LDO. The DAC and error-amp gain are scaled so that the LSB size at the output is 50mV. Output voltage can be set by writing the proper code to the desired LDO register. See Table A for the bitcodes and their corresponding voltages for LDO CORE, and Table B for bitcodes and their corresponding voltages for LDO SPAD, MOT and CAM.

| X4 | X3 | X2 | X1 | X0 | LDO Output<br>Voltage |

|----|----|----|----|----|-----------------------|

| 0  | 0  | 0  | 0  | 0  | 1.35V                 |

| 0  | 0  | 0  | 0  | 1  | 1.40V                 |

| 0  | 0  | 0  | 1  | 0  | 1.45V                 |

| 0  | 0  | 0  | 1  | 1  | 1.50V                 |

| 0  | 0  | 1  | 0  | 0  | 1.55V                 |

| 0  | 0  | 1  | 0  | 1  | 1.60V                 |

| 0  | 0  | 1  | 1  | 0  | 1.65V                 |

| 0  | 0  | 1  | 1  | 1  | 1.70V                 |

| 0  | 1  | 0  | 0  | 0  | 1.75V                 |

| 0  | 1  | 0  | 0  | 1  | 1.80V                 |

| 0  | 1  | 0  | 1  | 0  | 1.85V                 |

| 0  | 1  | 0  | 1  | 1  | 1.90V                 |

| 0  | 1  | 1  | 0  | 0  | 1.95V                 |

| 0  | 1  | 1  | 0  | 1  | 2.00V                 |

| 0  | 1  | 1  | 1  | 0  | 2.05V                 |

| 0  | 1  | 1  | 1  | 1  | 2.10V                 |

| 1  | 0  | 0  | 0  | 0  | 2.15V                 |

| 1  | 0  | 0  | 0  | 1  | 2.20V                 |

| 1  | 0  | 0  | 1  | 0  | 2.25V                 |

| 1  | 0  | 0  | 1  | 1  | 2.30V                 |

| 1  | 0  | 1  | 0  | 0  | 2.35V                 |

| 1  | 0  | 1  | 0  | 1  | 2.40V                 |

| 1  | 0  | 1  | 1  | 0  | 2.45V                 |

| 1  | 0  | 1  | 1  | 1  | 2.50V                 |

| 1  | 1  | 0  | 0  | 0  | 2.55V                 |

| 1  | 1  | 0  | 0  | 1  | 2.60V                 |

| 1  | 1  | 0  | 1  | 0  | 2.65V                 |

| 1  | 1  | 0  | 1  | 1  | 2.70V                 |

| 1  | 1  | 1  | 0  | 0  | 2.75V                 |

| 1  | 1  | 1  | 0  | 1  | 2.80V                 |

| 1  | 1  | 1  | 1  | 0  | 2.85V                 |

| 1  | 1  | 1  | 1  | 1  | 2.90V                 |

#### TABLE A - Output Voltage Code Bits for VCORE

#### TABLE B - Output Voltage Code Bits for VPAD, VMOT and VCAM

| X4 | X3 | X2 | X1 | X0 | LDO Output<br>Voltage |

|----|----|----|----|----|-----------------------|

| 0  | 0  | 0  | 0  | 0  | 1.75V                 |

| 0  | 0  | 0  | 0  | 1  | 1.80V                 |

| 0  | 0  | 0  | 1  | 0  | 1.85V                 |

| 0  | 0  | 0  | 1  | 1  | 1.90V                 |

| 0  | 0  | 1  | 0  | 0  | 1.95V                 |

| 0  | 0  | 1  | 0  | 1  | 2.00V                 |

| 0  | 0  | 1  | 1  | 0  | 2.05V                 |

| 0  | 0  | 1  | 1  | 1  | 2.10V                 |

| 0  | 1  | 0  | 0  | 0  | 2.15V                 |

| 0  | 1  | 0  | 0  | 1  | 2.20V                 |

| 0  | 1  | 0  | 1  | 0  | 2.25V                 |

| 0  | 1  | 0  | 1  | 1  | 2.30V                 |

| 0  | 1  | 1  | 0  | 0  | 2.35V                 |

| 0  | 1  | 1  | 0  | 1  | 2.40V                 |

| 0  | 1  | 1  | 1  | 0  | 2.45V                 |

| 0  | 1  | 1  | 1  | 1  | 2.50V                 |

| 1  | 0  | 0  | 0  | 0  | 2.55V                 |

| 1  | 0  | 0  | 0  | 1  | 2.60V                 |

| 1  | 0  | 0  | 1  | 0  | 2.65V                 |

| 1  | 0  | 0  | 1  | 1  | 2.70V                 |

| 1  | 0  | 1  | 0  | 0  | 2.75V                 |

| 1  | 0  | 1  | 0  | 1  | 2.80V                 |

| 1  | 0  | 1  | 1  | 0  | 2.85V                 |

| 1  | 0  | 1  | 1  | 1  | 2.90V                 |

| 1  | 1  | 0  | 0  | 0  | 2.95V                 |

| 1  | 1  | 0  | 0  | 1  | 3.00V                 |

| 1  | 1  | 0  | 1  | 0  | 3.05V                 |

| 1  | 1  | 0  | 1  | 1  | 3.10V                 |

| 1  | 1  | 1  | 0  | 0  | 3.15V                 |

| 1  | 1  | 1  | 0  | 1  | 3.20V                 |

| 1  | 1  | 1  | 1  | 0  | 3.25V                 |

| 1  | 1  | 1  | 1  | 1  | 3.30V                 |

SC905A

## Register Map (Cont.)

## Analog LDO Voltage Tables C and D

The bit code controls the output voltage of each LDO. The LSB size at the output is 50mV. Output voltage can be set by writing the proper code to the desired LDO register. See Table C for the bitcodes and their corresponding voltages for LDO ANA, and Table D for the bitcodes and their corresponding voltages for LDOs TCXO, TX, RX and PLL.

| X2 | X1 | X0 | LDO Output<br>Voltage |

|----|----|----|-----------------------|

| 0  | 0  | 0  | 2.55V                 |

| 0  | 0  | 1  | 2.60V                 |

| 0  | 1  | 0  | 2.65V                 |

| 0  | 1  | 1  | 2.70V                 |

| 1  | 0  | 0  | 2.75V                 |

| 1  | 0  | 1  | 2.80V                 |

| 1  | 1  | 0  | 2.85V                 |

| 1  | 1  | 1  | 2.90V                 |

#### TABLE C - Output Voltage Code Bits for LDO VANA

#### TABLE D - Output Voltage Code Bits for LDOs VTCXO, VTX, VRX, VPLL

| X2 | X1 | X0 | LDO Output<br>Voltage |

|----|----|----|-----------------------|

| 0  | 0  | 0  | 2.75V                 |

| 0  | 0  | 1  | 2.80V                 |

| 0  | 1  | 0  | 2.85V                 |

| 0  | 1  | 1  | 2.90V                 |

| 1  | 0  | 0  | 2.95V                 |

| 1  | 0  | 1  | 3.00V                 |

| 1  | 1  | 0  | 3.05V                 |

| 1  | 1  | 1  | 3.10V                 |

#### Using the I<sup>2</sup>C Serial Port

#### The I<sup>2</sup>C General Specification

The SC905A is a read-write slave-mode I<sup>2</sup>C device and complies with the Philips I<sup>2</sup>C standard Version 2.1 dated January, 2000. The SC905A has eight user-accessible internal 8-bit registers. The I<sup>2</sup>C interface has been designed for program flexibility, in that once the slave address has been sent to the SC905A enabling it to be a slave transmitter/receiver, any register can be written or read independently of each other. While there is no auto increment/decrement capability in the SC905A I<sup>2</sup>C logic, a tight software loop can be designed to randomly access the next register independent of which register you begin accessing. The start and stop commands frame the data-packet and the repeat start condition is allowed if necessary.

#### SC905A Limitations to the I<sup>2</sup>C Specifications

Seven bit addressing is used and ten bit addressing is not allowed. Any general call address will be ignored by the SC905A. The SC905A is not CBUS compatible. The SC905A can operate in standard mode (100kbit/s) or fast mode (400kbit/s).

#### **Supported Formats**

#### **Direct Format - Write**

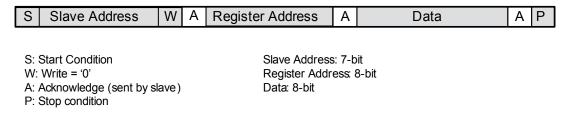

The simplest format for an I<sup>2</sup>C write is given below. After the start condition [S], the slave address is sent, followed by an eighth bit indicating a write. The SC905A I<sup>2</sup>C then acknowledges that it is being addressed, and the master responds with an 8-bit data byte consisting of the register address. The slave acknowledges and the master sends the appropriate 8-bit data byte. Once again the slave acknowledges and the master terminates the transfer with the stop condition [P].

#### I<sup>2</sup>C Direct Format - Write

#### **Combined Format - Read**

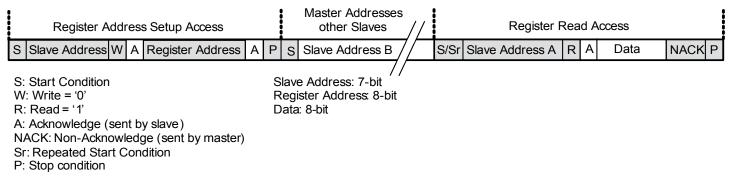

After the start condition [S], the slave address is sent, followed by an eighth bit indicating a write. The SC905A I<sup>2</sup>C then acknowledges that it is being addressed, and the master responds with an 8-bit data byte consisting of the register address. The slave acknowledges and the master sends the repeated start condition [Sr]. Once again, the slave address is sent, followed by an eighth bit indicating a read. The slave responds with an acknowledge and the previously addressed 8-bit data byte; the master then sends a non-acknowledge (NACK). Finally, the master terminates the transfer with the stop condition [P].

#### I<sup>2</sup>C Combined Format- Read

| S Slave Address                                                                                                                                               | WA       | Register Address                                         | A | Sr | Slave Address | R | Α | Data | NACK P |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------|---|----|---------------|---|---|------|--------|

| S: Start Condition<br>W: Write = '0'<br>R: Read = '1'<br>A: Acknowledge (sent by s<br>NACK: Non-Acknowledge<br>Sr: Repeated Start Condit<br>P: Stop condition | (sent by | Slave Address<br>Register Addr<br>Data: 8-bit<br>master) |   |    |               |   |   |      |        |

SC905/

## Using the I<sup>2</sup>C Serial Port (Cont.)

#### **Stop-Separated Reads**

Stop-separated reads can also be used. This format allows a master to set up the register address pointer for a read and return to that slave at a later time to read the data. In this format the slave address followed by a write command are sent after a start [S] condition. The SC905A then acknowledges it is being addressed, and the master responds with the 8-bit register address. The master sends a stop or restart condition and may then address another slave. After performing other tasks, the master can send a start or restart condition to the SC905A with a read command. The SC905A acknowledges this request and returns the data from the register location that had previously been set up.

#### I<sup>2</sup>C Stop Separated Format- Read

SC905A

Timing Diagram

**Power On-Off Timing Diagram**

SC905A

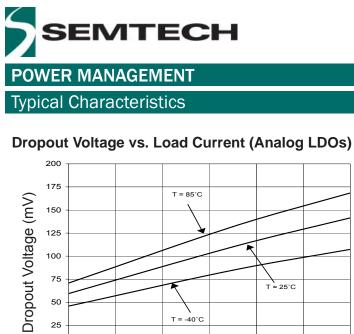

Dropout Voltage vs. Load Current (Digital LDOs) T = 85° Dropout Voltage (mV) T = 25°C Load Current (mA)

Load Current (mA)

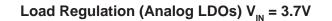

Load Regulation (Digital LDOs)  $V_{IN} = 3.7V$

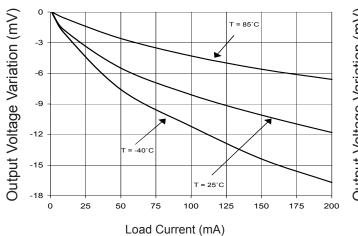

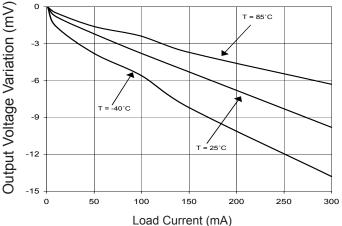

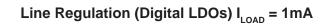

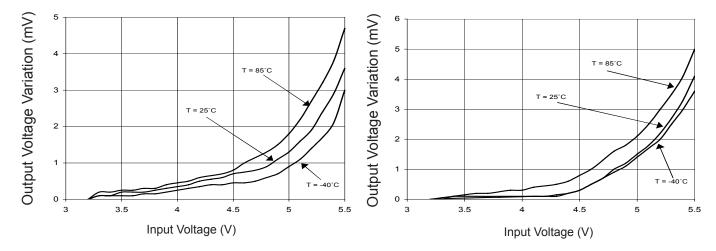

Line Regulation (Analog LDOs) I<sub>LOAD</sub> = 1mA

## SC905A

## POWER MANAGEMENT

## Typical Characteristics (Cont.)

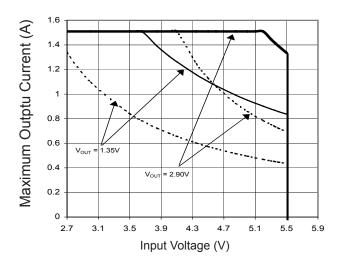

Safe Operating Limits

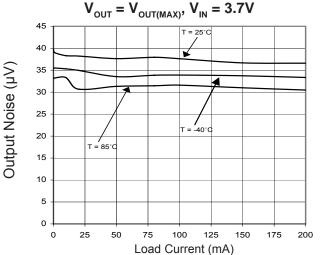

Output Noise vs. Load Current (Analog LDOs)

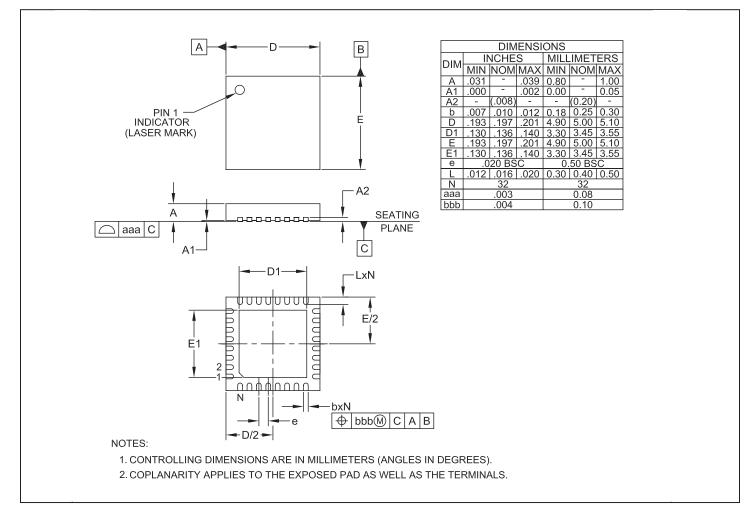

Outline Drawing - MLPQ-32 5x5

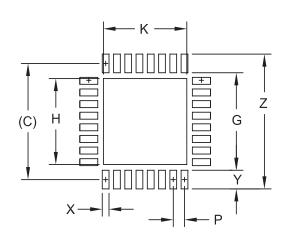

## Land Pattern - MLPQ-32 5x5

|     | DIMENSIONS |             |  |  |  |

|-----|------------|-------------|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |

| С   | (.197)     | (5.00)      |  |  |  |

| G   | .165       | 4.20        |  |  |  |

| Н   | .146       | 3.70        |  |  |  |

| K   | .146       | 3.70        |  |  |  |

| Ρ   | .020       | 0.50        |  |  |  |

| X   | .012       | 0.30        |  |  |  |

| Y   | .031       | 0.80        |  |  |  |

| Ζ   | .228       | 5.80        |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

- 4. SQUARE PACKAGE DIMENSIONS APPLY IN BOTH " X " AND " Y " DIRECTIONS.

## **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 FAX (805)498-3804