# MU9C8248 FDDI SRT Interface

# PRELIMINARY DATA SHEET

### **DISTINCTIVE CHARACTERISTICS**

- High-speed FDDI Source Routing and Transparent Bridging address filter supports up to sixteen ports

- Glue-free operation with the MUSIC MU9C1480 LANCAM and AMD, National Semiconductor, and Motorola FDDI chip sets

- Configurable for both Motorola and Intel processor addressing modes

- Complies with the ISO 9314 standard for FDDI

- 64-entry Instruction Buffer holds up to six downloadable filtering and purging routines

- 64-entry Data Buffer or internal FIFO

- Automatic selection of Source Routing or Transparent filtering routines based on Transceiver output data

- Supplies proper XDAMAT, XSAMAT, SRMAT, ABORT, and CIP signals to the FDDI chip sets

- · Selectable filtering options for each frame type

- · Checks validity of Routing Information Field

- TTL-compatible interfaces

- Manufactured in CMOS technology

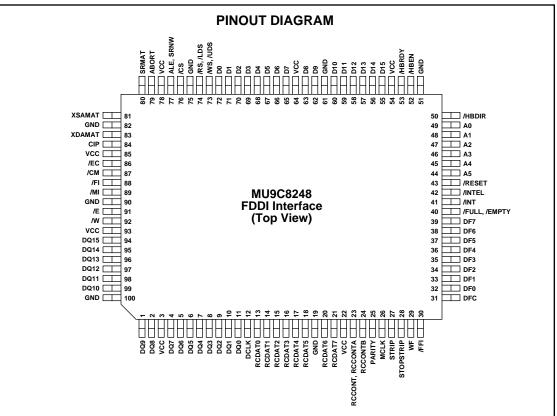

- Available in 100-pin PQFP package

### **GENERAL DESCRIPTION**

The MU9C8248 is a Source Routing Transparent (SRT) Interface to the MUSIC Semiconductors LANCAM for use in FDDI LAN Bridges and Brouters. This interface operates in accordance with ISO standards while supporting address filtering rates up to 500,000 frames/sec for minimum-length frames.

The MU9C8248 has five interfaces to provide "glue-free" address filtering. The Transceiver interface monitors receive data between the Physical Layer device and the MAC and determines whether to filter according to Source Routing or Transparent Bridging standards. The MAC interface supplies signals to instruct the FDDI chip set to reject or copy a frame. The LANCAM interface controls the companion LANCAM(s) for Transparent filtering. The Host Processor interface allows direct initialization of the MU9C8248, and downloading of the filtering and purging routines. The FIFO interface outputs new addresses received from the FDDI network.

The MU9C8248 can choose to copy or reject a frame depending on the frame's DA, RIF, and/or the frame type (MAC, LLC, or Reserved), and can perform multiple validity checks within the Routing Information Field (RIF), including general checks on every Routing Control Field (RCF) as well as multiple frame related checks.

The internal RAM can store up to 64 instructions at initialization for the LANCAM to execute matching, learning, aging, and purging operations. Up to six routines can be stored here and started by the network or the Node Processor. Internal arbitration prioritizes execution of instructions by the LANCAM. A second internal RAM, which contains 64 16-bit words, is used for data buffering operations or as an internal FIFO.

With sixteen Ring-Bridge-Ring number combinations stored internally, the MU9C8248 is very well suited to operate as an address filter in multi-port Source Routing Bridge/Brouter environments.

MUSIC is a trademark of MUSIC Semiconductors. LANCAM, the MUSIC logo, and the phrase "MUSIC Semiconductors" are registered trademarks of MUSIC Semiconductors. AMD is a registered trademark of Advanced Micro Devices, Inc. National Semiconductor is a registered trademark of National Semiconductor Corporation. Motorola is a registered trademark of Motorola, Inc. Intel is a registered trademark of Intel Corporation. 15 April 1997 Rev. 2.5 Web

### **PIN DESCRIPTIONS**

(/X indicates an active LOW function)

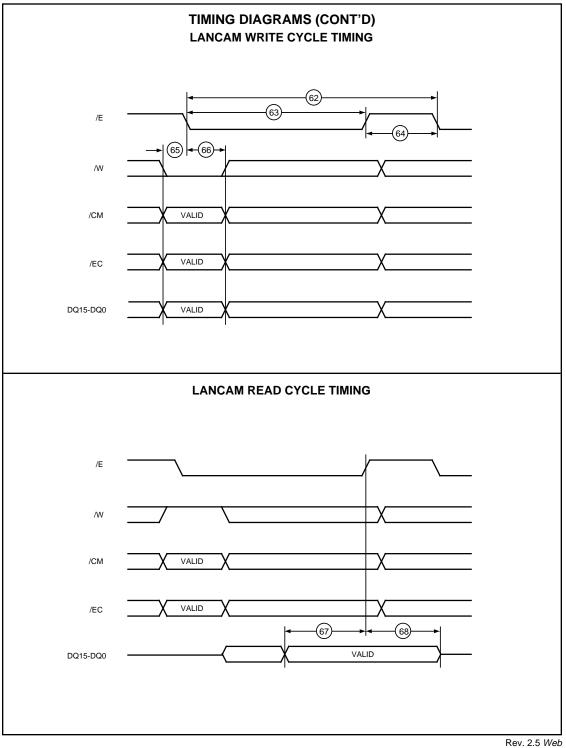

### LANCAM Interface:

#### DQ15-DQ0 (Data Bus, Common I/O, TTL)

The DQ15–DQ0 lines transfer data, commands and status between the MU9C8248 and the LANCAM. The direction and nature of the information that flows between the devices are determined by the states of /CM and /W.

### /E (Chip Enable, Output, TTL)

The /E output enables the LANCAM while LOW and registers /W, /CM, /EC and DQ15–DQ0 (if /W is LOW) on the falling edge of /E. If /W is HIGH, data on DQ15–DQ0 from the LANCAM is valid on the rising edge of /E.

#### /W (Write Enable, Output, TTL)

The /W output selects the direction of data flow during a LANCAM cycle. DQ15–DQ0 write to the LANCAM if /W is LOW at the falling edge of /E. Read data is output from the LANCAM to DQ15–DQ0 on the rising edge of /E if /W is HIGH at the falling edge of /E.

Rev. 2.5 Web

### /CM (Data/Command Select, Output, TTL)

The /CM signal determines whether DQ15–DQ0 contain LANCAM data or commands. /CM is LOW at the falling edge of /E for Command cycles and HIGH for Data cycles.

#### /EC (Enable Comparison, Output, TTL)

The /EC signal enables the LANCAM /MF pin to output the results of a comparison. If /EC is LOW at the falling edge of /E for a given cycle, the LANCAM /MF output is enabled on the rising edge of /E. If /EC is HIGH, the LANCAM /MF output is held HIGH.

#### /MI (Match Flag, Input, TTL)

The LANCAM /MF pin takes the MU9C8248's /MI input LOW if a valid match occurs during a Comparison cycle, and /EC was also LOW at the start of that cycle. The state of the /MI pin controls branching in the MU9C8248's routines and signalling to the FDDI chipset.

### **PIN DESCRIPTIONS (CONT'D)**

#### /FI (Full Flag, Input, TTL)

The /FI input will be driven LOW by the LANCAM /FF output pin if all the LANCAM memory locations have valid contents. The status of the /FI pin can be read by the Host processor from the MU9C8248's Control register and is also used to prevent learning of new network addresses.

#### Transceiver Interface:

#### RCDAT7-RCDAT0 (Receive Data, Input, TTL)

The RCDAT pins monitor the data received by the Physical layer device from the FDDI network. RCDAT7-RCDAT0 are clocked on the rising edge of DCLK. The first symbol received from the fiber is placed on RCDAT7-RCDAT4 whereby the first bit received from the fiber is placed on RCDAT7. For chipsets using two associated Receive Data Control bits, each four-bit symbol has an associated RCCONT bit to indicate whether the four-bit symbol is to be considered a Data symbol or a Control symbol. RCCONT B is associated with RCDAT7-RCDAT4 and RCCONT A is associated Receive Data Control bit, RCCONT A becomes RCCONT and is the indicator for both symbols.

#### RCCONT A or RCCONT (Receive Data Control Bit, Input, TTL)

For chipsets providing two Receive Data Control bits, RCCONT A is associated with RCDAT3-RCDAT0 to indicate that the four-bit symbol being presented on RCDAT3-RCDAT0 is a Control symbol (RCCONT A is HIGH) or a Data symbol (RCCONT A is LOW).

For chipsets using only one Control bit for each symbol pair, RCCONT A becomes RCCONT and is the only Receive Data Control bit used. If RCCONT is HIGH, both RCDAT7-RCDAT4 and RCDAT3-RCDAT0 are Control symbols. If RCCONT is LOW, both RCDAT7-RCDAT4 and RCDAT3-RCDAT0 are Data symbols. RCCONT A or RCCONT is valid on the rising edge of DCLK.

#### RCCONT B (Receive Data Control Bit, Input, TTL)

RCCONT B is provided by the Physical layer devices, is valid on the rising edge of DCLK, and is used to indicate that the four-bit symbol being presented on RCDAT7-RCDAT4 is a Control symbol (RCCONT B is HIGH) or a Data symbol (RCCONT B is LOW). For FDDI chipsets which use only one control bit RCCONT B should be tied to GND.

### PARITY (Parity, Input, TTL)

This input signal is the ODD parity of the RCDAT bus and RCCONT when the MU9C8248 is used in National Semiconductors (NS) mode. It is the ODD parity of the RCDAT bus and RCCONT A and -B when the MU9C8248 is programmed in not NS mode.

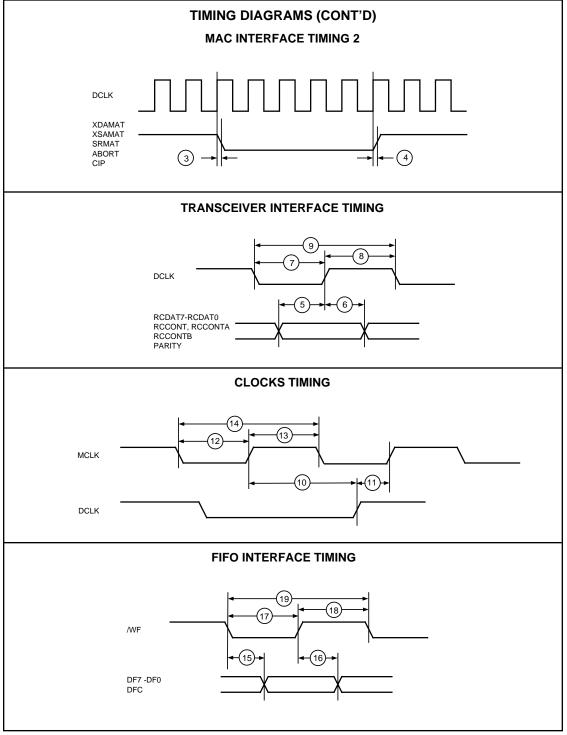

#### DCLK (Data Clock, Input, TTL)

The rising edge of DCLK clocks the RCDAT7-RCDAT0 data, RCCONT, RCCONTA, RCCONTB and PARITY received from the Physical layer device, which composed this data out of the data received from the FDDI network.

#### MAC Interface:

#### XDAMAT (External Destination Address Match, Output, Three-state TTL)

XDAMAT indicates, when made active, the FDDI chipset to copy a FDDI frame (this decision is made on basis of the Destination Address of the frame currently being received). The duration and polarity of XDAMAT are set in the Transparent Bridging/MAC register.

#### XSAMAT (External Source Address Match, Output, Three-state TTL)

XSAMAT, when active, indicates that the Source Address of the frame currently being received is found in the LANCAM database. The duration and polarity of XSAMAT are set in the Transparent Bridging/MAC register.

#### SRMAT (Source Routing Match, Output, Three-state TTL)

SRMAT, when active, indicates that the frame currently being received should be copied and forwarded based on information in the Routing Information Field of that frame. The duration and polarity of SRMAT are set in the Transparent Bridging/MAC register.

#### ABORT (Abort, Output, Three-state TTL)

ABORT is used to notify the FDDI chipset that the frame currently being received should not be copied and forwarded. The duration and polarity of ABORT are set in the Transparent Bridging/MAC register.

#### CIP (Compare in Progress, Output, TTL)

CIP is an output signal that National Semiconductors needs to notify their system interface that a Compare is in Progress. CIP goes HIGH on the third rising edge of DCLK after the edge that loaded a valid FC field into the MU9C8248. CIP returns LOW on the seventh rising edge of DCLK after the last byte of the Source Address field for frames not containing a Routing Information Field (RIF), or on the seventh rising edge of DCLK after the last byte of the RIF, if the frame contains such a field.

### PIN DESCRIPTIONS (CONT'D)

#### Host Processor Interface:

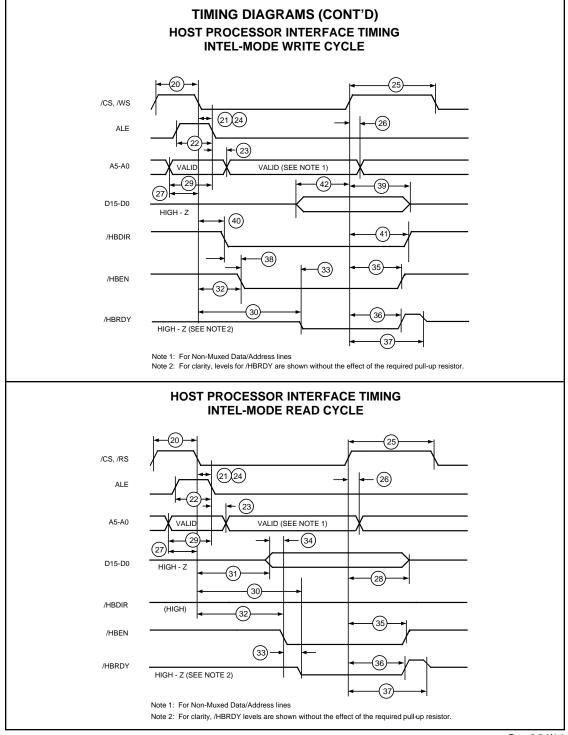

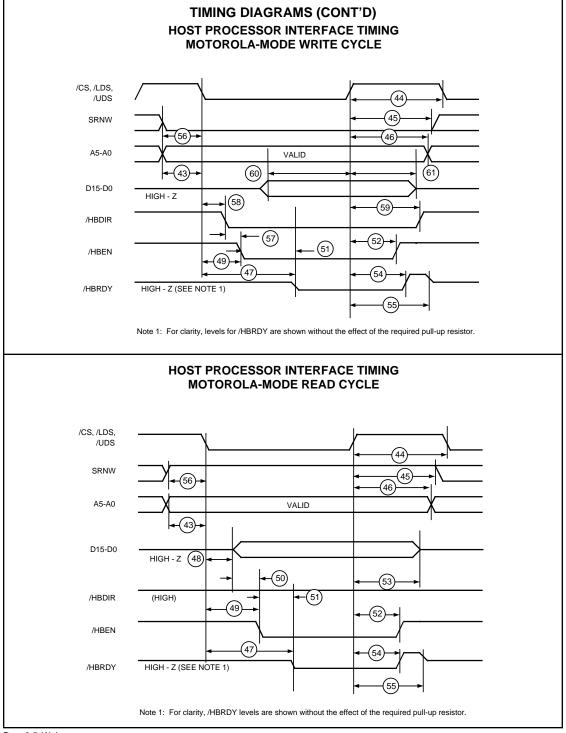

#### ALE, SRNW (Address Latch Enable/System Read Not Write, Input, TTL)

This pin is ALE when the MU9C8248 is used in the Intel mode. A positive pulse on ALE latches the address from the multiplexed data/address lines. If the MU9C8248 is in the Motorola mode, this pin becomes SRNW, and is HIGH for a Host Processor Read cycle and LOW for a Write cycle.

#### /CS (Chip Select, Input, TTL)

/CS going LOW enables the Host Processor interface of the MU9C8248 for a Host Processor read or write. When /CS is HIGH, the Host Processor interface is not active.

### A5–A0 (Address, Input, TTL)

The Address pins select the internal register for Host processor reads and writes. Depending on the Processor interface, the Address pins are latched by a positive pulse on ALE, or must remain stable until the rising edge of /RS, /WS, or /LDS and /JDS, as shown in the Timing diagrams.

#### D15–D0 (Data, Common I/O, TTL)

The Data pins transfer data between the Host Processor and the internal registers of the MU9C8248. Depending on the Processor Interface, the data pins are registered on the rising edge of /WS, or /LDS and /UDS; or must remain stable until the rising edge of /RS, or /LDS and /UDS, as shown in the Timing diagrams.

#### /RS, /LDS (Read Strobe/Lower Data Strobe, Input, TTL)

If the MU9C8248 is used in the Intel mode, this pin is /RS and goes LOW to begin a read cycle to the Host Processor interface. If the MU9C8248 is used in the Motorola mode, this pin is /LDS for Host processor read and write cycles and should be asserted in combination with /UDS. Data is read by the Host processor on the rising edge of /RS or /LDS, or is written into the MU9C8248 on the rising edge of /LDS.

#### /WS, /UDS (Write Strobe/Upper Data Strobe, Input, TTL)

If the MU9C8248 is used in the Intel mode, this pin is /WS, and goes LOW to begin a write cycle from the Host Processor interface. If the MU9C8248 is used in the Motorola mode, this pin is /UDS for Host processor read and write actions and should be asserted in combination with /LDS. Data is written into the MU9C8248 on the rising edge of /WS or /UDS, or is read from the MU9C8248 on the rising edge of /UDS.

#### /HBRDY (Ready, Output, Three-state TTL)

/HBRDY goes LOW to indicate to the Host processor that a data transfer is completed. After the Host processor has made

/RS, /WS, or /LDS and /UDS HIGH, the MU9C8248 takes /HBRDY HIGH. /HBRDY becomes three-state one MCLK period later.

#### /HBEN (Data Buffer Enable, Output, TTL)

If external bi-directional buffers are needed on the D15–D0 lines, /HBEN goes LOW to enable the external buffers. /HBEN goes HIGH to disable the external buffers.

#### /HBDIR (Data Buffer Direction, Output, TTL)

/HBDIR controls the direction of external bi-directional buffers. /HBDIR goes LOW to read from the registers of the MU9C8248 and HIGH to write to the MU9C8248 registers.

#### External FIFO Interface:

#### DF7-DF0 (FIFO data, Output, TTL)

On the rising edge of /WF, DF7-DF0 contain a part of a new Source Address (SA), which is just learned by the LANCAM. This new SA is written into an external FIFO connected to these DF7-DF0 in six cycles.

#### DFC (FIFO Control data, Output, TTL)

On the rising edge of /WF, DFC indicates whether the part of the new SA present on DF7-DF0 is the first part of this SA. If this is the first of the six write cycles DFC is HIGH. For the other five cycles, DFC is LOW.

#### /WF (FIFO Write, Output, TTL)

On the rising edge of /WF, data on DF7-DF0 and DFC is present and can be written to e.g. an external FIFO.

#### /FFI (FIFO Full, Input, TTL)

When /FFI is LOW, the MU9C8248 is indicated that the external FIFO is full and can't accept new SAs. Learning of new SAs in the LANCAM is then also disabled. When /FFI is HIGH learning of new SAs both in the external FIFO and LANCAM is enabled.

#### Miscellaneous:

#### /RESET (Hardware Reset, Input, TTL)

Taking /RESET LOW for at least 1 MCLK cycle sets the MU9C8248 to a predefined state. The contents of all registers are 0000H after a Hardware reset.

#### /INT (Interrupt, Output, Open Drain)

This pin goes LOW to notify the Host processor that the MU9C8248 is accessing the LANCAM. /INT is synchronized on /HBRDY and becomes active directly if no Host Processor LANCAM access cycle is active or after a possible pending Host Processor LANCAM access cycle has been completed (/HBRDY is HIGH) succesfully.

### **PIN DESCRIPTIONS (CONT'D)**

#### /FULL, /EMPTY (Full/Empty, Output, Open Drain)

If part of the Instruction buffer in the MU9C8248 is configured as a FIFO, this active-LOW pin can be configured to signal whether the FIFO is full (all entries contain valid data) or empty (no entry contains data). The definition of this signal is programmed in the FIFO Control/Delay register.

#### /INTEL (HPI Selection, Input, TTL)

The /INTEL pin identifies which type of microcontroller is connected to the Host Processor interface. This pin is set LOW for Intel-type addressing modes and HIGH for Motorola-type addressing modes.

#### STRIP (Strip, Input, TTL)

When STRIP has been asserted HIGH for only one MCLK period and STOP STRIP is kept LOW, the MU9C8248 stops the execution of the Routines 0 and 1 for the next FDDI frame. The result is that no signalling on the MAC interface and SA learning takes place. After STOP STRIP has been asserted for one MCLK period or any token or void frame has been received, signalling and learning is enabled again for the next FDDI frame.

STRIP is the overrulling signal which means that if STRIP is continuously kept HIGH, the assertion of STOP STRIP or the reception of a void frame or token doesn't enable the signalling and learning features of the MU9C8248.

#### STOP STRIP (Stop Strip, Input, TTL)

When STOP STRIP has been asserted for one MCLK period after STRIP has been HIGH for at least one MCLK period (and STRIP is LOW now), the MU9C8248 stops stripping and enables signalling and learning for the next FDDI frame.

#### MCLK (Master Clock, Input, TTL)

MCLK is the 25 MHz master clock. MCLK is used to clock all system parts of the MU9C8248.

#### VCC, GND (Positive Power Supply and Ground)

These pins are the main power supply connections to the MU9C8148. VCC must be held at +5V  $\pm$  10% relative to the GND pin, which is at 0V (system reference potential), for correct operation of the device.

### FUNCTIONAL DESCRIPTION

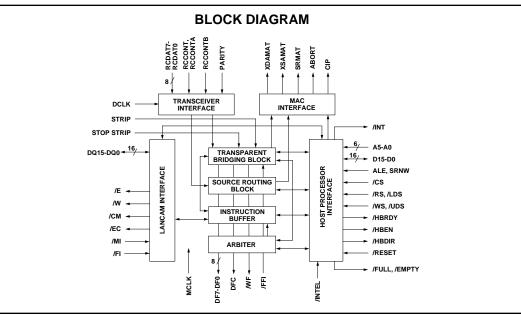

Referring to the Block diagram shown on Page 1, the MU9C8248 consists of four functional blocks: the Transparent Bridging Block (TBB), the Source Routing Block (SRB), the Instruction/Data Buffer (IB), and the Arbiter. Five interfaces connect the MU9C8248 to the FDDI Physical Layer device, the MAC controller or System interface, the Host processor, an external FIFO and the LANCAM. For a detailed description of FDDI frames, refer to the ISO9314-2 Standard.

#### Transparent Bridging Block

For all frames which do not contain a Routing Information Field (RIF), the TBB makes decisions whether to copy or discard a frame based on the Destination address (DA) and the Frame Control field (FC). If the MU9C8248 is not used in a Transparent Bridging Only mode and a frame containing an RIF is received the Source Routing Block performs the filtering actions and no DA comparison takes place. If the bridge is set for Transparent Bridging Only (the TBO bit in the Control register is HIGH), the TBB also makes copy or discard decisions (based on DA and/or FC) for frames which do contain an RIF.

The TBB parses the data as received from the Physical Layer device off the FDDI network, and indicates to the MAC interface whether to assert the XDAMAT, XSAMAT, ABORT and CIP signals. For each frame, the TBB examines the Frame Control field (FC), the Destination address (DA), and the Source address (SA), which contains the Routing Information indicator (RII). If this RII is HIGH that frame contains a RIF.

The FC field indicates whether the current frame is a Token or a regular frame. If a Token (Restricted or Non Restricted) is being received the TBB discards it, thereby having the 8248 not asserting any signals on the MAC interface. For a regular frame, the bits in the Frame Control field signify the type of frame (VOID, SMT, LLC, MAC, or Reserved) being received. The TBB decides either to copy or discard the frame directly, based on the settings in the Frame Type Selection register or to filter on the DA.

Positive or negative filtering on the DA is selected by the PONNE bit in the Transparent Bridging/MAC register. Filtering on the DA is done on all frames except for VOID-, SMT- and other types of frames with 16-bit addresses. No filtering and signalling takes place for these frames.

Positive filtering implies that a frame should be forwarded if its DA is found in the LANCAM address database. Routine 0 in the instruction buffer examines the DA to determine whether a frame should be copied or not. The results of this comparison are used to notify the FDDI chip set to copy or discard the frame. Negative filtering implies that a frame should be forwarded if its DA is not found in the address database. In this case, the MU9C8248 checks the DA and destinguishes between MAC, Broadcast, Functional and Group addresses. Based upon the settings of the Transparent Bridging/MAC register, the TBB discards a frame whose DA is either a Broadcast, Functional and/or Group address.

| Гуре                      | Condition                                                                                                       | Action                                                                              |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| me                        | A prestored LIN-BN-LOUT combination is found in the RIF & that LOUT has occurred only once in the RIF.          | Copy frame<br>Signal MAC Interface                                                  |  |

| Specifically Routed Frame | A prestored LIN-BN-LOUT combination is found in the RIF & that LOUT has occurred more than one time in the RIF. | Discard frame<br>Signal MAC Interface<br>Increment DUPLOUT counter                  |  |

| lly Ro                    | No prestored LIN-BN-LOUT combination is found in the RIF.                                                       | Discard frame<br>Signal MAC Interface                                               |  |

| cifica                    | #RDs > SRFRD                                                                                                    | Discard frame<br>Signal MAC Interface                                               |  |

| Spe                       | Prestored LIN is found more than once in the RIF.                                                               | Discard frame<br>Signal MAC interface                                               |  |

| r Frame                   | Last LOUT in RIF ≠ LIN                                                                                          | Discard frame<br>Signal MAC Interface<br>Increment LANIDMISMATCH<br>counter         |  |

| All Routes Explorer Frame | #RDS > ARERD                                                                                                    | Discard frame<br>Signal MAC Interface<br>Increment ARERDLIMIT-<br>EXCEEDED counter  |  |

| Route                     | Not all prestored LOUTs in RIF<br>#RDs < ARERD                                                                  | Copy frame<br>Signal MAC Interface                                                  |  |

| AII                       | All prestored LOUTs in RIF                                                                                      | Discard frame<br>Signal MAC Interface                                               |  |

| mes                       | Last LOUT in RIF ≠ LIN                                                                                          | Discard frame<br>Signal MAC Interface<br>Increment LANIDMISMATCH<br>counter         |  |

| ning Tree Explorer Frames | #RDs > STERD                                                                                                    | Discard frame<br>Signal MAC Interface<br>Increment STERDLIMIT-<br>EXCEEDED counter  |  |

| Lree E                    | Not all prestored LOUTs in RIF<br>#RDs < STERD                                                                  | Copy frame<br>Signal MAC Interface                                                  |  |

| Spanning <sup>1</sup>     | All prestored LOUTs in RIF                                                                                      | Discard frame<br>Signal MAC Interface<br>Increment DUPLANIDOR-<br>TREEERROR counter |  |

| 0)                        | Bit DISSTE = ONE                                                                                                | Discard frame<br>Signal MAC Interface                                               |  |

### FUNCTIONAL DESCRIPTION (CONT'D)

The Source Address (SA) of a frame can be used to update the database of addresses stored in the LANCAM. Routine 0 not only checks the DA but also the SA of a frame against all the entries in the database. If the SA is not found (the address is new) and if the frame received is error free, the address can be learned by adding it to the LANCAM database (by starting Routine 1) and at the same time writing it into the internal or external FIFO. The learning Routine 1 can be activated for specific frame types by setting the bits MLRN-FSLRN HIGH in the Transparent Briding/MAC register. Even SA's of erroneous frames can be learned when bit NOER of the Control register is programmed HIGH. If the SA is found in the database, XSAMAT is asserted.

Note that learning can only take place when the RII of the frame is ZERO, or for every frame when the TBO bit is HIGH. Thus, Routine 0 (performing a DA and SA comparison) is always started after the SD is received and stopped when the results of the DA and SA comparison are not needed. Routine 1 is started by the TBB block after the Error Indicator of the Frame Status field is received and all programmed conditions are met.

#### Source Routing Block

The Source Routing Block (SRB) only decides to copy or discard a frame if it contains an RIF.

When a frame is received, the SRB checks whether the Frame Control field indicates if a Token (Restricted or Non Restricted) is being received and no further processing is necessary. If a regular frame is being received and its RII bit is HIGH, the SRB signals the MAC interface, based on the frame type and the settings in the Frame Type Selection register, either to discard the frame; to continue to check the RIF of the frame, or to accept the frame immediately thereby having the MAC interface asserting XDAMAT.

If the RII is LOW, the SRB is not allowed to process the frame any further and waits for the next frame to arrive.

If a copy/discard decision is made based on the information in the RIF the FDDI chip set is signalled by SRMAT. The SRB examines the information contained in the Routing Control Field (RCF) which is part of the RIF. If the length (LTH) bits of the RCF indicate a length equal to zero, or contain an odd length, or if the length of the RIF is longer than the allowed length stored in the RIF Length register, reception of the frame is stopped, and the SRB indicates that the frame is to be discarded (SRMAT is not asserted). The D-bit of the RCF is used by the SRB to correctly interpret the Routing Descriptors (RDs) of the RIF.

The SRB provides for sixteen Ring(in)–Bridge–Ring(out) combinations (LIN-BN-LOUT) stored in the Source Ring Number register and Bridge/Destination Ring Number registers. LIN is the LAN ID of the ring connected to that specific port, while the BN(s) and LOUT(s) depend on the topology of the network and the bridge design. The SRB provides for checks between the LAN ring numbers and bridge numbers contained in every RD with every LIN-BN-LOUT stored, allowing the user to develop an SR(T) bridge with an internal virtual ring, or a bridge with a Full Mesh architecture.

If the Routing Type (RT) bits are equal to 0XXB, a Specifically-Routed Frame (SRF) is being received, and should be forwarded on the conditions shown in Table 1. If the RT bits are equal to 10XB, the frame is an All Routes Explorer (ARE) frame, and should be handled as shown in Table 1. If the RT bits are equal to 11XB, the frame is a Spanning Tree Explorer (STE) frame, and should be dealt with as shown in Table 1. Also described in Table 1 are the conditions on which the Error counters (Register 1DH) are incremented.

#### Instruction Buffer

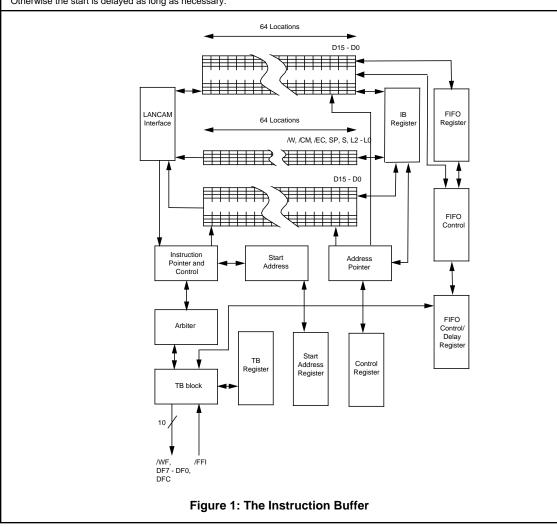

The Instruction buffer (IB) shown in Figure 1 consists of the following: the 64-entry Instruction Storage (IS), the 64-entry Data Storage (DS), the Instruction pointer (IP), the Address pointer, the Start address registers, the FIFO, and FIFO control registers.

The IS can store up to six down-loaded routines which contain instructions for the LANCAM to execute. The IS location accessed by the Host Processor port is controlled by an auto-incrementing Address pointer, which is part of the Control register. Each instruction is a 16-bit LANCAM op-code or data word along with 3 bits that indicate the level of /W, /CM, /EC during the instruction. An S-bit is used to indicate whether this entry is a LANCAM instruction or a MU9C8248 instruction. The ST-bit indicates whether this instruction is the last instruction in a routine while bits L2-L0 indicate the length of the instruction.

The Instruction pointer (IP) points to the instruction currently being fetched. At the start of a routine (only for Routine 2-5) the IP is loaded with the appropriate Start address after which the IP is used for instruction prefetches during execution. At the start of Routine 0 and 1 the IP points at the second instruction address because of the standard instruction prefetch of the Start address used for a fast start of Routine 0 and 1. The IP can also be loaded from addresses contained in an instruction itself. For example, when a "Wait for a match" instruction is executed and no match has occurred, the IP is loaded with the address of the next instruction to execute.

The Start Address registers contain the start addresses of all six routines. When a routine is started (Routine 2-5), this address is copied into the IP and execution is started while for Routine 0 and 1 the IP is loaded with the second instruction of that routine.

Part of the ID may be used as a FIFO for data storage. Data from the routines can be moved either to or from the Host Processor interface through the FIFO or new network addresses can be moved into the FIFO by the learning process. The functionallity of the /FULL or /EMPTY flag is programmed in the FIFO Control register to prevent FIFO overflow or underflow situations.

#### **Programming of Routines**

The IS is loaded and read through the IB register in two 16-bit cycles. The first 16-bit cycle moves the data on the D15–D0 lines of the Host Processor interface into the data field of the location in the IB indicated by the Address pointer in the Control register, or vice-versa in case of a read from the IB

### FUNCTIONAL DESCRIPTION (CONT'D)

register. The second 16-bit word is written to or read from the /W, /CM, /EC, /SP, S, L2-L0 bits of that same location.

The Control register contains an Address pointer that selects the accessed location in the IS (location 00H-3FH) and DS (location 40H-7FH). The Address pointer can be read out or overwritten. It is incremented when the Host processor has completed the two write or read cycles to/from one location of the IB.

### Execution of Routines

Routines in the instruction buffer can be started either by the Host processor (Routines 2-5 only) or the Transparent Bridging Block (Routines 0-1 only). If a routine is started by the Host processor, it is started immediatly if the arbiter allows it. Otherwise the start is delayed as long as necessary. The TBB starts Routine 0 and/or 1 when the enable bit of that routine is set HIGH. Routines 0, used for DA and SA comparison is started directly after the SD has been received or is started with a delay if this is programmed in the delay bits of the FIFO Control/Delay register, while Routine 1, used for the learning of network addresses, is started after the Error indicator of the FS field has been received.

#### Arbiter

The Arbiter block has two tasks: 1) Arbitration between the execution of different routines stored in the Instruction Buffer, 2) Arbitration between the execution of routines in the Instruction buffer and Host Processor access to the LANCAM.

### FUNCTIONAL DESCRIPTION (CONT'D)

#### **Routine Priorities**

Of the six routines stored in the Instruction buffer, execution of Routines 0–1 is time critical because there is a direct relation to the incoming data stream of the FDDI network; therefore, they have the highest priority and cannot be interrupted by other routines. The time length of Routines 0 plus Routine 1 must fit in the time interval of a minimum length frame. Routines 2-5 have a lower priority and a routine can be interrupted by all routines having a lower number.

During execution of Routine 0–1, no lower priority routine can be started. When during the execution of a routine, a second routine is programmed to be started and execution of the first routine has ended, this second routine is started immediately afterward. A currently running routine can be interrupted by a higher priority routine, and the lower priority routine will re-start from the beginning immediately after the interrupting routine has finished.

#### **Host Processor Access**

The Host processor is able to control the LANCAM directly via the MU9C8248, but is given access only when no pre-stored routine is being executed. The /INT pin will indicate when a pre-stored routine is exercizing the LANCAM. If execution of a pre-stored routine takes place during Host processor interaction, the current processor cycle is completed before the Host processor is interrupted, so that while the results of the Host processor interactions can not be guaranteed, it is notified that it has been interrupted. The MU9C8248 releases /INT after it has finished its LANCAM access. If /INT remains deasserted during Host processor activity, the Host processor has been able to complete its instruction sequence.

#### **MAC Interface**

The TBB and/or the SRB notify the MAC interface to copy or reject a frame through the XDAMAT, XSAMAT, SRMAT, ABORT and CIP pins. Polarity and assertion length of the signals can be programmed in the Transparent Bridging/MAC register.

#### **Transceiver Interface**

The MU9C8248 connects to the received data bus between the Physical Layer and MAC device. The encoded data received from the FDDI Physical Layer Device is input to the RCDAT pin clocked by the DCLK clock.

The Transceiver interface notifies the TBB and the SRB that it has detected a Starting Delimiter in the incoming data stream and to begin parsing the other fields of the frame. The Transceiver interface performs a number of error checks: whether the data contained any control characters before an ED was received; that no second SD is received before an ED is received. In any of these cases, both the TBB and SRB are notified and reception of data is cancelled. Also checked are: the correctness of the FCS, the value of the Error indicator symbol in the ED.

#### Host Processor Interface

The Host Processor interface is configured for Intel or Motorola addressing modes using the /INTEL pin. In both modes the MU9C8248 is a slave on the processor bus and can be programmed using the registers described in this document. The MU9C8248 provides /HBEN and /HBDIR to enable the user to add external bi-directional buffers in the D15-D0 datalines. In Intel mode the Host Processor interface can be used in a system with multiplexed or non-multiplexed data and address lines. The Host Processor interface can only be used for 16-bit transfers.

#### The Register Set

The internal Register set is detailed following the description of the Instruction set. The registers are selected by the A5–A0 Address bus, and written to or read from as shown in the Timing diagrams.

### INSTRUCTION SET DESCRIPTION

E

Instruction: LANCAM Instruction

Binary Op Code: iiii iiii iiii iiii wce0 slll

- Instruction Code (see The LANCAM Handbook)

- w The state of /W

- c The state of /CM

- e The state of /EC

- s Stop routine

- I Instruction length

This instruction transfers data or commands to or from the LANCAM. Instructions from the LANCAM instruction set are described in the LANCAM Handbook. The state of the control outputs /W, /CM and /EC at the falling edge of /E for this cycle are defined by w, c, and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

### Instruction: Wait for match for yyyyB + 5 cycles, if no match then execute at address aaaaaaB. Binary Op Code: 0010 yyyy rraa aaaa xxx1

- y Wait period

- r Reserved (set LOW)

- a Address

- x Don't Care

This instruction waits for a maximum period of yyyyB + 5 clock cycles for the /MI input to become active. If no match condition occurs during that period, a branch is executed to the address which is stored in the "a" bits of the instruction. If a match condition is detected, execution proceeds to the instruction in the next address. This instruction is not needed for the basic DA and/or SA comparison.

#### Instruction: Move DA part 0 to DQ15–DQ0. Binary Op Code: 0011 0000 0000 0000 0ce1 slll

- c The state of /CM

- e The state of /EC

- s Stop routine

- I Instruction length

The "Move DA part 0 to DQ15–DQ0" instruction places the least significant part of the DA address (bits 15–0) on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by l. For the coding of the l bits refer to Table 2.

#### Instruction: Move DA part 1 to DQ15–DQ0. Binary Op Code: 0011 0000 0000 0001 0ce1 slll

- c The state of /CM

- e The state of /EC

- s Stop routine

- I Instruction length

The "Move DA part 1 to DQ15–DQ0" instruction places DA address bits 31–16 on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped

after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

#### Instruction: Move DA part 2 to DQ15–DQ0. Binary Op Code: 0011 0000 0000 0010 0ce1 slll

- c The state of /CM

- e The state of /EC

- s Stop routine

- I Instruction length

This instruction places the most significant part of the DA address (bits 47–32) on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

| nstruction:     | Move SA part 0 to DQ15–DQ0.   |

|-----------------|-------------------------------|

| Binary Op Code: | 0011 0000 0000 0011 0ce1 slll |

| c The sta       | te of /CM                     |

- e The state of /EC

- s Stop routine

- I Instruction length

The "Move SA part 0 to DQ15–DQ0" instruction places the least significant part of the SA address (bits 15–0) on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by l. For the coding of the l bits refer to Table 2.

| Instruction:    | Move SA part 1 to DQ15–DQ0.   |

|-----------------|-------------------------------|

| Binary Op Code: | 0011 0000 0000 0100 0ce1 slll |

| c The sta       | ate of /CM                    |

|                 |                               |

- e The state of /EC s Stop routine

- Instruction length

- i instruction length

The "Move SA part 1 to DQ15–DQ0" instruction places SA address bits 31–16 on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

| Instruction:    | Move SA part 2 to DQ15–DQ0.   |

|-----------------|-------------------------------|

| Binary Op Code: | 0011 0000 0000 0101 0ce1 sill |

| c The sta       | te of /CM                     |

| o Thosta        | te of /EC                     |

- s Stop routine

- I Instruction length

This instruction places the most significant part of the SA address (bits 47–32) on the DQ15–DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last

### **INSTRUCTION SET DESCRIPTION (CONT'D)**

instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2

#### Instruction: Move data from address 1aaaaaaB to DQ15-DQ0.

Binary Op Code: 0100 rrrr r1aa aaaa 0ce1 slll

- Reserved

- Address а

- The state of /CM С

- The state of /EC е

- Stop routine s

- Instruction length н

The "Move data from address 1aaaaaaB to DQ15-DQ0" instruction places the contents of the address specified by the "a" bits on the DQ15-DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

#### Instruction: Move data from DQ15-DQ0 to address 1aaaaaaB.

Binary Op Code: 0101 rrrr r1aa aaaa 1ce1 slll

- Reserved а

- Address

с

- The state of /CM

- е The state of /EC

- Stop routine s

- Instruction length н

This instruction places the values on the DQ15-DQ0 lines in the address specified by the "a" bits. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

#### Move data from the FIFO to DQ15-DQ0. Instruction: Binary Op Code: 0110 rrrr rrrr rrrr 0ce1 slll

- Reserved

- С The state of /CM

- е The state of /EC

- Stop routine s

- н Instruction length

The "Move data from the FIFO to DQ15-DQ0" instruction places the contents of the next FIFO location on the DQ15-DQ0 lines. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

Move data from DQ15-DQ0 to the FIFO. Instruction: Binary Op Code: 0111 rrrr rrrr rrrr 1ce1 slll Reserved

- r The state of /CM С

- е The state of /EC

- Stop routine s

- Т Instruction length

This instruction places the values on the DQ15-DQ0 lines into the FIFO. The control outputs /CM and /EC at the falling edge of /E for this cycle are defined by c and e. If s is set HIGH, the instruction is the last instruction of the routine and execution of the routine is stopped after this instruction has been executed. The length of the instruction is determined by I. For the coding of the I bits refer to Table 2.

| Ш    | /E HIGH | /E LOW | Instruction Length |

|------|---------|--------|--------------------|

| 000B | 1 MCLK  | 1 MCLK | 2 MCLK             |

| 001B | 1 MCLK  | 2 MCLK | 3 MCLK             |

| 010B | 1 MCLK  | 3 MCLK | 4 MCLK             |

| 011B | 2 MCLK  | 1 MCLK | 3 MCLK             |

| 100B | 3 MCLK  | 1 MCLK | 4 MCLK             |

Note: An 300XH instruction executed after an not 300XH instruction takes one extra MCLK cycle.

#### Table 2: Instruction Length

| BIT         NAME         DESCRIPTION           00H: Control Register         15         RESET         If RESET is HIGH, a reset of the MU9C8248 is programmed for the Notorola or AMD FDDI chipset. If NNS is HIGH, the MU9C8248 is programmed for the Notorola or AMD FDDI chipset. If NNS is HIGH, learning of new network addresses is enabled for frames containing a RIF. is LSASR is HIGH, learning of new addresses of frames with RIF is disabled. If TBO is HIGH this LSASF care <sup>1</sup> .           12         TBO         If TBO is HIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.           11         DISSTE         If IDS is TIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.           10         NFF         INF indicates the level of the /FI input.           9         /INT is read-only. If /INT is LOW and mitere LANCAM access by the Host Processor has been in by the execution of AIWSC244 oroutine. If /INT is HIGH all direct LANCAM accesses by Host were successful. /INT is reset HIGH after read out.           8         RDFCP         If RDCP is HIGH, access to the Torr Counter 1DH is reset to point to DUPL7-0 and IRI7-0. If NOER is LOW only network addresses from frames, not containing an RI7-0. If NOER is LOW only network addresses from frames not containing an RI7-0. If NOER is LOW only network addresses from frames not containing an RI7-0. If NOER is LOW only network addresses from frames not containing an RI7-0. If NOER IS LOW only network addresses from frames not containing an RI7-0. If NOER IS LOW only network addresses from frames not containing an RI7-1. If MERHIME is LOW, the MU9C2248 signals the FDDI chipset is for directly.                                                                                                                                                                                                                                                                                                                                          | REGISTER SET DESCRIPTION                                                                                                                                                                |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15         RESET         If RESET is HIGH, a reset of the MU9C8248 takes place.           14         NNS         If NNS is HIGH, the MU9C8248 is programmed for the Motorola or AMD FDDI chipset. If NNS LOW, the MU9C8248 is programmed for the Motorola or AMD FDDI chipset. If SASR is HIGH, learning of new network addresses is enabled for frames containing a RIF. is LOW, learning of new addresses of trames with RIF is disabled. If TBO is HIGH this LSASR care*.           12         TBO         If TBO is HIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.           11         DISSTE         If JDISTE is HIGH, all Spanning Tree Explorer frames are discarded. The MU9C8248 signals chipset to flush these frames. If DISSTE is LOW, STE frames are accepted per the programm criteria.           10         NFF         NFF indicates the level of the /Fi input.           9         /INT         /INT is read-only. If /INT is LOW an direct LANCAM access by the Host Processor has been in by the execution of a MU9C8248 routine. If /INT is HIGH all direct LANCAM accesses by Hos were successtill. /INT is reset HIGH after read out.           8         RDFCP         If RDFC is HIGH, access to the Error Counter 10H is reset to point to DUPL7–0 and IRT-0.           7         NOER         If NOER is programmed HIGH, learning of new network addresses is enabled for frame sthat errors. If NOER is LOW only network addresses from frames, not containing any errors, are id fush the frame. If MSRENEL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is signality of the SRENEL is LOW. Newary MAC frame containing an RIF is discarded. The F                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                         |  |  |  |  |

| <ul> <li>If NNS is HIGH, the MU9C8248 is programmed for the Motorola or AMD FDDI chipset. If NNS LOW, the MU9C8248 is programmed for the NS FDDI chipset.</li> <li>LSASR if LSASR is HIGH, learning of new network addresses is enabled for frames containing a RIF. is LSW, learning of new addresses of trames with RIF is disabled. If TBD is HIGH this LSASR care<sup>5</sup>.</li> <li>TBO If TBO is HIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.</li> <li>DISSTE If DISSTE is HIGH, all Spanning Tree Explorer frames are discarded. The MU9C8248 signals chipset to flush these frames. If DISSTE is LOW, STE frames are accepted per the programm criteria.</li> <li>NFR NFF indicates the level of the /Fi input.</li> <li>INT // INT is read-only. If /INT is LOW an direct LANCAM access by the Host Processor has been in by the execution of a MU9C8248 routine. If /INT is HIGH at licet LANCAM accesses by Hos were successfull. /INT is reset HIGH after read out.</li> <li>RDFCP If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7–0 and IRI7-0.</li> <li>NOCR if NOCR is LOW only network addresses from frames, not ontaining any errors, are left.</li> <li>APR6–0 APR6–0 APR6-0 APR6-0 aprint to BU9C8248 signals the FDDI chipset to successful to the location in the IB which can be accessed through the IB Register.</li> <li>MSRENBL If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is a flush the frame. If MSRENBL is HIGH, the MSRFILT bit determines if the frame is filtered or or directly. MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is signalled to flush the frame. If MSRENBL is HIGH, the MU9C8248 signals the FDDI chipset to copy every MAC frame containing an RIF. It MSRFILT is HIGH, the MU9C8248 signals the FDDI chipset to copy every MAC frame containing an RIF. It SIRENBL is LOW, every RESRENG The TDI SHGH.</li> <li>LSRENBL If LSRENBL is LOW, every MSRENIL To it determ</li></ul>                                                            | 00H: Control Register                                                                                                                                                                   |  |  |  |  |

| <ul> <li>LSASR If LSASR is HIGH, learning of new network addresses is enabled for frames containing a RIF is LOW, learning of new addresses of frames with RIF is disabled. If TBO is HIGH this LSASR care'.</li> <li>TBO If TBO is HIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.</li> <li>DISSTE If DISSTE is HIGH, all Spanning Tree Explorer frames are discarded. The MU9C8248 signals chipset to flux these frames. If DISSTE is LOW, STE frames are accepted per the programm criteria.</li> <li>NFF MICHEATES the level of the /F1 input.</li> <li>/INT //INT is read-only. If /INT is LOW an direct LANCAM access by the Host Processor has been in by the execution of a MU3C6248 routine. If /INT is HIGH all direct LANCAM accesses by Hos were successful. /INT is reset HIGH after read out.</li> <li>RDFCP If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7–0 and IRT-0.</li> <li>NOER If NOER is troggrammed HIGH, learning of new network addresses is enabled for frames that errors. If NOER is toW only network addresses from frames, not containing an yerrors, are lied-0 APR6–0 point to the location in the IB which can be accessed through the IB Register.</li> <li>MSRENBL</li> <li>If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If MSRENBL is HIGH, the MSRFILT bit determines if the frame is filtered or or directly. MSRENBL is 'don't care' if TBO is HIGH.</li> <li>MSRFILT If IGSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If LSRENBL is HIGH, the US28248 checks the RIF and forwards the frame if the programmed fluces244 signals the FDDI chipset to copy every MAC frame contain frame. If LSRENBL is HIGH, the MU9C8248 signals the FDDI chipset to copy every MCC frame contain for RIF. If GSRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If LSR</li></ul>                                                                 | grammed for the Motorola or AMD FDDI chipset. If NNS is set                                                                                                                             |  |  |  |  |

| 12         TBO         If TBO is HIGH, all incoming frames are filtered by the Transparent Bridging block only. No SF takes place.           11         DISSTE         If DISSTE is HIGH, all Spanning Tree Explorer frames are discarded. The MU9C8248 signals chipset to flush these frames. If DISSTE is LOW, STE frames are accepted per the programm criteria.           10         NFF         NFF indicates the level of the /FI input.           9         //INT         //INT is read-only. If /INT is ISOW an direct LANCAM access by the Host Processor has been in by the execution of a MU9C8248 routine. If /INT is HIGH all direct LANCAM accesses by Hos were successfull. /INT is reset HIGH after read out.           8         RDFCP         If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7-0 and IRI7-0.           7         NOER         If MORE is LOW only network addresses is onabled for frames that errors. It NOER is LOW only network addresses is on for frames, not containing any errors. are lease of the frame is filtered or condirectly. MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is s flush the frame. If MSRFILT is 'don't care'' if TBO is HIGH.           14         MSRFILT         If MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every MAC frame containing an RIF is discarded. The FDDI chipset is signific flush the frame. If MSRFILE is 'don't care'' if TBO is HIGH.           13         LSRENBL         If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is signalled to flush the frame. If LSRENBL is 'don't care'' if TBO is HIGH.           14                                                                                                                                                                                                                                                                                                                                                                                                                                 | work addresses is enabled for frames containing a RIF. If LSASR                                                                                                                         |  |  |  |  |

| 11       DISSTE       If DISSTE is HIGH, all Spanning Tree Explorer frames are discarded. The MU9C8248 signals chipset to flush these frames. If DISSTE is LOW, STE frames are accepted per the programm criteria.         10       NFF       NFF indicates the level of the /FI input.         9       /INT is read-only. If /INT is LOW an direct LANCAM access by the Host Processor has been in by the execution of a MU9C8248 routine. If /INT is HIGH all direct LANCAM accesses by Host were successful. /INT is read-only. If /INT is HIGH all direct LANCAM accesses by Host were successful.         8       RDFCP       If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7–0 and IRI7–0.         7       NOER       If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7–0 and IRI7–0.         7       NOER       If RDFCP is LOW only network addresses from frames, not containing any errors, are I         6–0       APR6–0       APR6–0 point to the location in the IB which can be accessed through the IB Register.         15       MSRENBL       If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is s flush the frame. If MSRENL is HIGH, the MSRFILT bit determines if the frame is filtered or or directly. MSRENBL is 'CON', the MU9C8248 signals the FDDI chipset to copy every MAC frame contain RIF. If MSRFILT is LOW, werey LLC frame containing an RIF is discarded. The FDDI chipset is signaled to flush the frame. II LSRENBL is 'HGH, the LSRFILT bit determines if the frame is filtered or or directly. LSRENBL is 'GON' care' if TBO is HIGH.         14       MSRFILT       If MSRFILT is                                                                                                                                                                                                                                                                                                                                                                                                                                            | e filtered by the Transparent Bridging block only. No SR bridging                                                                                                                       |  |  |  |  |

| 10         NFF         NFF indicates the level of the /FI input.           9         /INT         /INT is read-only. If /INT is LOW an direct LANCAM accesses by the dost Processor has been in by the execution of a MU9G2248 routine. If /INT is HIGH all direct LANCAM accesses by Hos were successfull. /INT is reset HIGH after read out.           8         RDFCP         If RDFCP is FIHGH, accesses to the Error Counter 10H is reset to point to DUPL7-0 and IRI7-0.           7         NOER         If NOER is programmed HIGH, learning of new network addresses is enabled for frames that errors. If NOER is LOW only network addresses from frames, not containing any errors, are leader of the OAPR6-0 point to the location in the IB which can be accessed through the IB Register.           01H: Frame Type Selection Register         If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is a flush the frame. If MSRENBL is HIGH, the MSRFILT bit determines if the frame is filtered or c directly. MSRENBL is 'don't care' if TBO is HIGH.           14         MSRFILT         If MSRFILT is HIGH, the MU9C6248 checks the RIF and forwards the frame if the program forwarding conditions are met. MSRFILT is 'don't care' if TBO is HIGH.           13         LSRENBL         If LSRENBL is 'GM, ter MU9C8248 signals the FDDI chipset to copy every LLC frame containing an RIF is discarded. The FDDI chipset is ginglust the frame if the programme forwards the frame. If LSRENBL is 'don't care' if TBO is HIGH.           14         MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain if LSRENBL is LOW, every Reserved for Implementer frame containing an RIF is discar                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                         |  |  |  |  |

| 8         RDFCP         If RDFCP is HIGH, access to the Error Counter 1DH is reset to point to DUPL7–0 and IRI7–0.<br>If NOER is programmed HIGH, learning of new network addresses is enabled for frames that<br>errors. If NOER is LOW only network addresses from frames, not containing any errors, are li<br>errors. If NOER is LOW only network addresses from frames, not containing any errors, are li<br>errors. If NOER is LOW only network addresses from frames, not containing any errors, are li<br>difference in the location in the IB which can be accessed through the IB Register.           01H:         Frame Type Selection Register           15         MSRENBL         If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is s<br>flush the frame. If MSRENBL is ''don't care'' if TBO is HIGH.           14         MSRFILT         If MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every MAC frame containing an RIF is discarded. The FDDI chipset is sig<br>flush the frame. If LSRENBL is 'HOM' care'' if TBO is HIGH.           13         LSRENBL         If LSRENBL is 'HOM' care'' if TBO is HIGH.           14         MSRFILT         If LSRENBL is 'LoW, every LCC frame containing an RIF is discarded. The FDDI chipset is sig<br>flush the frame. If LSRENBL is HIGH, the USRFILT bit determines if the frame is filtered or co<br>directly. LSRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded.           14         FISRFILT         If LSRENBL is 'HOM', the MU9C8248 checks the RIF and forwards the frame if the programme<br>forwarding conditions are met. LSRFILT is 'HOM' care'' if TBO is HIGH.           13         LSRFILT         If SSRENBL         If                                                                                                                                                                                                                                                                                                                                                                  | ect LANCAM access by the Host Processor has been interrupted<br>ne. If /INT is HIGH all direct LANCAM accesses by Host Processor                                                        |  |  |  |  |

| 01H: Frame Type Selection Register         15       MSRENBL       If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is s flush the frame. If MSRENBL is HIGH, the MSRFILT bit determines if the frame is filtered or condirectly. MSRENBL is "don't care" if TBO is HIGH.         14       MSRFILT       If MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every MAC frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is sig flush the frame. If LSRENBL is HIGH, the LSRFILT bit determines if the frame is filtered or condirectly. LSRENBL is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame containing the LSRFILT is LSRENBL is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame containing the LSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame containing the frame if the programme forwarding conditions are met. LSRFILT is "don't care" if TBO is HIGH.         11       FISRENBL       If LSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF is fiscarded. The fISRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded. The fISRENBL         10       FISRFILT       If FISRENBL is LOW, every Reserved for Full SRENBL is HIGH, the FISRENBL is HIGH.         9       FSSRENBL       IF FSSRENBL IS LOW, every Reserved for Full Signals the FDDI chipset to copy every Reserved for Full Standardization frame containing an RIF. If FSSRENBL is HIGH.         8                                                                                                                                                                                                                                                                                                                                  | Counter 1DH is reset to point to DUPL7–0 and IRI7–0.<br>g of new network addresses is enabled for frames that contain<br>addresses from frames, not containing any errors, are learned. |  |  |  |  |

| <ul> <li>MSRENBL</li> <li>If MSRENBL is LOW, every MAC frame containing an RIF is discarded. The FDDI chipset is a flush the frame. If MSRENBL is HIGH, the MSRFILT bit determines if the frame is filtered or a directly. MSRENBL is 'don't care" if TBO is HIGH.</li> <li>MSRFILT</li> <li>If MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every MAC frame conta RIF. If MSRFILT is HIGH, the MU9C8248 checks the RIF and forwards the frame if the progra forwarding conditions are met. MSRFILT is 'don't care" if TBO is HIGH.</li> <li>LSRENBL</li> <li>If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FDDI chipset is signification to a containing an RIF is discarded. The FISRENBL is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain forwarding conditions are met. LSRFILT is 'don't care' if TBO is HIGH.</li> <li>FISRENBL Is LOW, every Reserved for Implementer frame containing an RIF is discarded. The FISRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded. The FISRENBL is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF is DI os HIGH.</li> <li>FISRENBL</li> <li>FISRENBL</li> <li>FISRENBL IS LOW, every Reserved for Future Standardization frame containing an RIF is The FDDI chipset to copy every Reserved for Future Standardization frame containing an RIF is The FDDI chipset is signalled to flush the frame. If FISRENBL is HIGH, the FISRFILT bit determines if the programmed forwards the frame is filtered or copied directly. This bit is 'don't care' if TBO is HIGH.</li> <li>FSSRENBL IF FSSRFILT is LOW, the MU9C8248 signals the FDDI chipset</li></ul>                          |                                                                                                                                                                                         |  |  |  |  |

| <ul> <li>directly. MSRENBL is "don't care" if TBO is HIGH.</li> <li>If MSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every MAC frame conta<br/>RIF. If MSRFILT is LOW, the MU9C8248 checks the RIF and forwards the frame if the progra<br/>forwarding conditions are met. MSRFILT is "don't care" if TBO is HIGH.</li> <li>LSRENBL If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is signalled to flush the frame. If LSRENBL is HIGH, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain<br/>If LSRFILT is HIGH, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain<br/>If LSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain<br/>If LSRFILT is HIGH, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain<br/>If LSRFILT is HIGH, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain<br/>If LSRFILT is HIGH, the MU9C8248 signals the FDDI chipset to copy every LC frame contain<br/>If LSRFILT is HIGH, the MU9C8248 signals the FDDI chipset is discarded.</li> <li>FISRENBL IS LOW, every Reserved for Implementer frame containing an RIF is discarded.</li> <li>FISRFILT If FISRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Impl<br/>frame containing an RIF. If FISRFILT is HIGH, the MU9C8248 checks the RIF and forwards the<br/>the programmed forwarding conditions are met. This bit is "don't care" if TBO is HIGH.</li> <li>FSSRENBL If FSSRENBL is LOW, every Reserved for Future Standardization frame containing an RIF is<br/>The FDDI chipset is signalled to flush the frame. If FSSRENBL is HIGH, the FSSRFILT bit determines<br/>the frame is filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>FSSRFILT If FSSRENBL is LOW, every MAC frame not containing an RIF is discarded. The FDDI chipset<br/>to frame is filtered or copied directly. This bit is "don't care" if the frame.</li> <li>FSSRFILT Is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Fut<br/>Sta</li></ul> | 5                                                                                                                                                                                       |  |  |  |  |

| <ol> <li>LSRENBL If LSRENBL is LOW, every LLC frame containing an RIF is discarded. The FDDI chipset is signaling the frame. If LSRENBL is HIGH, the LSRFILT bit determines if the frame is filtered or condirectly. LSRENBL is "don't care" if TBO is HIGH.</li> <li>LSRFILT If LSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame containing the SRFILT is HIGH, the MU9C8248 checks the RIF and forwards the frame if the programme forwarding conditions are met. LSRFILT is "don't care" if TBO is HIGH.</li> <li>FISRENBL If FISRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded. The filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>FISRFILT IF SLOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF is discarded. The FISRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF. If FISRFILT is HIGH, the FDDI signal the FDDI chipset is copy every Reserved for Implementer frame containing an RIF. If FISRFILT is HIGH, the MU9C8248 checks the RIF and forwards the programmed forwarding conditions are met. This bit is "don't care" if TBO is HIGH.</li> <li>FISRFILT IF SSRENBL IS LOW, every Reserved for Future Standardization frame containing an RIF is The FDDI chipset is signalled to flush the frame. If FSSRFINE is HIGH, the FSSRFILT bit determines if the frame is filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>FSSRFILT IF SSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Future Standardization frame containing an RIF is The FDDI chipset is copied directly. This bit is "don't care" if the frame is filtered or copied directly. This bit is "don't care" if HIGH.</li> <li>MTRENBL If If MTRENBL is LOW, every MAC frame not containing an RIF is discarded. The FDDI chipset signalled to flush the frame. If MTRENBL is HIGH, the MTRFILT bit determines if the frame is</li></ol>                                                     | O is HIGH.<br>gnals the FDDI chipset to copy every MAC frame containing an<br>248 checks the RIF and forwards the frame if the programmed                                               |  |  |  |  |

| <ul> <li>12 LSRFILT If LSRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every LLC frame contain If LSRFILT is HIGH, the MU9C8248 checks the RIF and forwards the frame if the programme forwarding conditions are met. LSRFILT is "don't care" if TBO is HIGH.</li> <li>11 FISRENBL IF ISRENBL IS LOW, every Reserved for Implementer frame containing an RIF is discarded. If FISRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded. If FISRENIT IF ISRENIT IS LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF is discarded. If FISRENIT IS LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF is RISRENIT IF ISRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Implementer frame containing an RIF. If FISRFILT is HIGH.</li> <li>9 FSSRENBL IF FSSRENBL IS LOW, every Reserved for Future Standardization frame containing an RIF is The FDDI chipset is signalled to flush the frame. If FSSRENIS HIGH, the FSSRFILT bit determines if the frame is filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>9 FSSRENBL IF FSSRENBL IS LOW, every Reserved for Future Standardization frame containing an RIF is The FDDI chipset is signalled to flush the frame. If FSSRENBL is HIGH, the FSSRFILT bit det the frame is filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>8 FSSRFILT IF FSSRFILT IS LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Future Standardization frame containing an RIF. If FSSRFILT is HIGH, the MU9C8248 checks the RI forwards the frame if the programmed forwarding conditions are met. This bit is "don't care" if HIGH.</li> <li>7 MTRENBL</li> <li>17 MTRENBL IS LOW, every MAC frame not containing an RIF is discarded. The FDDI chipset signalled to flush the frame. If MTRENBL is HIGH, the MTRFILT bit determines if the frame is ignalled to flush the frame. If MTRENBL is H</li></ul>                                                     | containing an RIF is discarded. The FDDI chipset is signalled to the LSRFILT bit determines if the frame is filtered or copied                                                          |  |  |  |  |

| <ol> <li>FISRENBL If FISRENBL is LOW, every Reserved for Implementer frame containing an RIF is discarded.<br/>chipset is signalled to flush the frame. If FISRENBL is HIGH, the FISRFILT bit determines if th<br/>filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>FISRFILT If FISRFILT is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Imp<br/>frame containing an RIF. If FISRFILT is HIGH, the MU9C8248 checks the RIF and forwards th<br/>the programmed forwarding conditions are met. This bit is "don't care" if TBO is HIGH.</li> <li>FSSRENBL If FSSRENBL is LOW, every Reserved for Future Standardization frame containing an RIF is<br/>The FDDI chipset is signalled to flush the frame. If FSSRENBL is HIGH, the FSSRFILT bit det<br/>the frame is filtered or copied directly. This bit is "don't care" if TBO is HIGH.</li> <li>FSSRFILT If FSSRENL is LOW, the MU9C8248 signals the FDDI chipset to copy every Reserved for Fut<br/>Standardization frame containing an RIF. If FSSRFILT is HIGH, the MU9C8248 checks the RI<br/>forwards the frame if the programmed forwarding conditions are met. This bit is "don't care" if TBO<br/>Standardization frame containing an RIF. If FSSRFILT is HIGH, the MU9C8248 checks the RI<br/>forwards the frame if the programmed forwarding conditions are met. This bit is "don't care" if<br/>HIGH.</li> <li>MTRENBL If MTRENBL is LOW, every MAC frame not containing an RIF is discarded. The FDDI chipset<br/>signalled to flush the frame. If MTRENBL is HIGH, the MTRFILT bit determines if the frame is<br/>copied directly. If TBO is HIGH, filtering is also done on MAC frames containing an RIF.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                       | nals the FDDI chipset to copy every LLC frame containing an RIF.<br>necks the RIF and forwards the frame if the programmed                                                              |  |  |  |  |