# Genesys Logic, Inc.

# **GL9701**

# PCI Express<sup>TM</sup> to PCI Bridge

Datasheet Revision 0.90 Sep. 05, 2006

# **Copyright:**

Copyright © 2006 Genesys Logic Incorporated. All rights reserved. No part of the materials may be reproduced in any form or by any means without prior written consent of Genesys Logic Inc..

#### **Disclaimer:**

ALL MATERIALS ARE PROVIDED "AS IS" WITHOUT EXPRESS OR IMPLIED WARRANTY OF ANY KIND. NO LICENSE OR RIGHT IS GRANTED UNDER ANY PATENT OR TRADEMARK OF GENESYS LOGIC INC.. GENESYS LOGIC HEREBY DISCLAIMS ALL WARRANTIES AND CONDITIONS IN REGARD TO MATERIALS, INCLUDING ALL WARRANTIES, IMPLIED OR EXPRESS, OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. IN NO EVENT SHALL GENESYS LOGIC BE LIABLE FOR ANY DAMAGES INCLUDING, WITHOUT LIMITATION, DAMAGES RESULTING FROM LOSS OF INFORMATION OR PROFITS. PLEASE BE ADVISED THAT THE MATERIALS MAY CONTAIN ERRORS OR OMMISIONS. GENESYS LOGIC MAY MAKE CHANGES TO THE MATERIALS OR TO THE PRODUCTS DESCRIBED THEREIN AT ANY TIME WITHOUT NOTICE.

#### **Trademarks:**

**GENESYS** is a registered trademark of Genesys Logic, Inc. All trademarks are the properties of their respective owners.

#### Office:

Genesys Logic, Inc.

12F, No. 205, Sec. 3, Beishin Rd., Shindian City,

Taipei, Taiwan

Tel: (886-2) 8913-1888 Fax: (886-2) 6629-6168 http://www.genesyslogic.com

# **Revision History**

| Revision | Date       | Description          |  |

|----------|------------|----------------------|--|

| 0.90     | 2006/09/05 | First formal release |  |

# TABLE OF CONTENTS

| CHAPTER 1 GENERAL DESCRIPTION                           | 9    |

|---------------------------------------------------------|------|

| CHAPTER 2 FEATURES                                      | . 10 |

| 2.1 PCI Express Features                                | . 10 |

| 2.2 PCI INTERFACE FEATURES                              | . 10 |

| 2.3 POWER MANAGEMENT                                    | . 10 |

| 2.4 SMBUS INTERFACE                                     | . 11 |

| CHAPTER 3 PIN ASSIGNMENT                                | . 12 |

| 3.1 PIN CONFIGURATION                                   | . 12 |

| 3.2 PINOUT                                              | . 13 |

| 3.3Numeric Pin Assignment List                          | . 14 |

| 3.4 SIGNAL DESCRIPTION                                  | . 16 |

| 3.4.1 PCI-Express Interface                             | . 16 |

| 3.4.2 Secondary PCI Interface                           | . 17 |

| 3.4.3 EEPROM Signals                                    | . 18 |

| 3.4.4 Miscellaneous Signals                             | . 18 |

| 3.4.5 Power and Ground Signals                          | . 19 |

| CHAPTER 4 BLOCK DIAGRAM                                 |      |

| CHAPTER 5 FUNCTION DESCRIPTION                          | . 24 |

| 5.1 POWER MANAGEMENT                                    | . 24 |

| 5.1.1 PCI-PM Software Compatible Power Management       |      |

| 5.1.2 Hardware-Controlled Active State Power Management |      |

| 5.1.3 In-band Beacon                                    | . 24 |

| 5.1.4 Side-band WAKE_N                                  | . 25 |

| 5.1.5 Power Management System Messages                  | . 25 |

| 5.2 PCI CLOCK RUN                                       | . 25 |

| 5.3 PCI CLOCK                                           | . 25 |

| 5.4 Interrupt mapping                                   | . 26 |

| 5.5 INITIAL FLOW CONTROL ADVERTISEMENTS                 | . 27 |

| 5.6 IDSEL MAPPING                                       | . 28 |

| CHAPTER 6 REGISTER DESCRIPTION                          | . 29 |

| 6.1 Offset 00h: Device Identification                   | . 34 |

| 6.2 OFFSET 04H: COMMAND REGISTER                        | . 34 |

| 6.3 Offset 06h: Status Register                         | . 35 |

|                                                         |      |

| 6.4 Offset 08h: Revision ID                                                  | 37        |

|------------------------------------------------------------------------------|-----------|

| 6.5 Offset 09h: Class Code                                                   |           |

| 6.6 OFFSET 0CH: CACHE LINE SIZE REGISTER                                     | <b>38</b> |

| 6.7 Offset 0dh: Primary Latency Timer Register                               | 38        |

| 6.8 Offset 0eh: Header Type Register                                         | <b>38</b> |

| 6.9 Offset 0fh: Bist Register                                                | <b>38</b> |

| 6.10 Offset 10h: Base Register0                                              |           |

| 6.11 Offset 14h: Base Register1                                              | <b>38</b> |

| 6.12 Offset 18h: Primary Bus Number Register                                 | 39        |

| 6.13 Offset 19h: Secondary Bus Number Register                               | <b>39</b> |

| 6.14 Offset 1ah: Subordinate Bus Number Register                             | 39        |

| 6.15 Offset 1bh: Secondary Latency Timer Register                            | <b>39</b> |

| 6.16 OFFSET 1CH: IO BASE AND IO LIMIT REGISTER                               | <b>39</b> |

| 6.17 OFFSET 1EH: SECONDARY STATUS REGISTER                                   | 40        |

| 6.18 Offset 20h: Memory Base and Limit Register                              | 42        |

| 6.19 Offset 24h: Prefetchable M <mark>emory</mark> Base and Limit Register . | <b>42</b> |

| 6.20 Offset 28h: Prefetchable Base Upper 32-bits Register                    | <b>43</b> |

| 6.21 Offset 2ch: Prefetchable Limit Upper 32-bits Register                   | 43        |

| 6.22 Offset 30h: IO Base and Limit Upper 16-bits Register                    | <b>43</b> |

| 6.23 Offset 34h: Capabilities Pointer Register                               | 43        |

| 6.24 Offset 3ch: Interrupt Line Register                                     | 44        |

| 6.25 Offset 3dh: Interrupt Pin Register                                      | 44        |

| 6.26 Offset 3eh: Bridge Control Register                                     | 44        |

| 6.27 Offset 70h: PCI Express Capability List Register                        | <b>48</b> |

| 6.28 OFFSET 72H: PCI Express Capabilities Register                           | <b>48</b> |

| 6.29 Offset 74h: PCI Express Device Capabilities Register                    | <b>49</b> |

| 6.30 OFFSET 78H: PCI Express Device Control Register                         | <b>49</b> |

| 6.31 Offset 7ah: PCI Express Device Status Register                          | <b>50</b> |

| 6.32 Offset 7ch: PCI Express Link Capabilities Register                      | <b>51</b> |

| 6.33 OFFSET 80H: PCI EXPRESS LINK CONTROL REGISTER                           | <b>52</b> |

| 6.34 OFFSET 82H: PCI EXPRESS LINK STATUS REGISTER                            | 52        |

| 6.35 Offset 94h: PM Capability ID Register                                   | 53        |

| 6.36 OFFSET 95H: PM NEXT POINTER REGISTER                                    | 53        |

| 6.37 OFFSET 96H: POWER MANAGEMENT CAPABILITIES REGISTER                      | 53        |

|   | 6.38 OFFSET 98H: POWER MANAGEMENT CONTROL AND STATUS        |      |

|---|-------------------------------------------------------------|------|

|   | REGISTER                                                    | . 54 |

|   | 6.39 OFFSET A0H: SLOT NUMBERING CAPABILITIES ID REGISTER    | . 54 |

|   | 6.40 OFFSET A1H: SLOT NUMBERING POINTER TO NEXT ID REGISTER | . 55 |

|   | 6.41 OFFSET A2H: SLOT NUMBERING EXPANSION SLOT REGISTER     | . 55 |

|   | 6.42 OFFSET A3H: SLOT NUMBERING CHASSIS NUMBER REGISTER     | . 55 |

|   | 6.43 OFFSET 100H: ADVANCED ERROR REPORTING ENHANCED         |      |

|   | CAPABILITY HEADER REGISTER                                  | . 55 |

|   | 6.44 OFFSET 104H: UNCORRECTABLE ERROR STATUS REGISTER       |      |

|   | 6.45 OFFSET 108H: UNCORRECTABLE ERROR MASK REGISTER         | . 56 |

|   | 6.46 OFFSET 10CH: UNCORRECTABLE ERROR SEVERITY REGISTER     | . 57 |

|   | 6.47 OFFSET 110H: CORRECTABLE ERROR STATUS REGISTER         | . 57 |

|   | 6.48 OFFSET 114H: CORRECTABLE ERROR MASK REGISTER           | . 57 |

|   | 6.49 OFFSET 118H: ADVANCED ERROR CAPABILITIES AND CONTROL   |      |

|   | REGISTER                                                    | . 58 |

|   | 6.50 OFFSET 11CH: HEADER LOG REGISTER                       |      |

|   | 6.51 OFFSET 12CH: SECONDARY UNCORRECTABLE ERROR STATUS      |      |

|   | REGISTER                                                    | . 58 |

|   | 6.52 Offset 130h: Secondary Uncorrectable Error Mask        |      |

|   | REGISTER                                                    | . 59 |

|   | 6.53 OFFSET 134H: SECONDARY UNCORRECTABLE ERROR SEVERITY    |      |

|   | REGISTER                                                    | . 60 |

|   | 6.54 OFFSET 138H: SECONDARY ERROR CAPABILITIES AND CONTROL  |      |

|   | REGISTER                                                    | . 60 |

|   | 6.55 OFFSET 13CH: SECONDARY HEADER LOG REGISTER             |      |

|   | 6.56 OFFSET 150H: DEVICE SERIAL NUMBER ENHANCED CAPABILITY  |      |

|   | HEADER REGISTER                                             | . 61 |

|   | 6.57 OFFSET 154H: DEVICE SERIAL NUMBER REGISTER             | . 61 |

| C | CHAPTER 7 ELECTRICAL CHARACTERISTICS                        | . 62 |

|   | 7.1 OPERATION CONDITIONS                                    | . 62 |

|   | 7.3 DIFFERENTIAL RECEIVER (RX) INPUT SPECIFICATION          | . 68 |

|   | 7.4 PCI INTERFACE DC SPECIFICATIONS                         | . 70 |

|   | 7.5 PCI INTERFACE AC SPECIFICATIONS                         | . 71 |

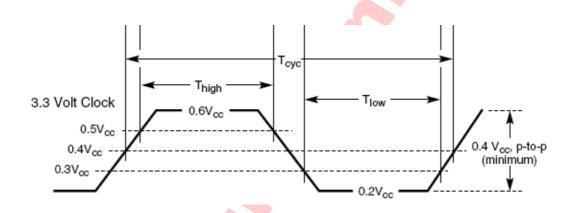

|   | 7.6 CLOCK AND RESET SPECIFICATIONS                          | . 72 |

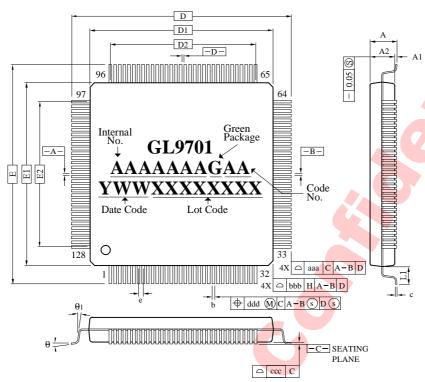

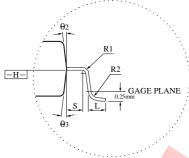

| C | CHAPTER 8 PACKAGE DIMENSION                                 | . 74 |

|   |                                                             |      |

# CHAPTER 9 ORDERING INFORMATION......75

# LIST OF FIGURES

| FIGURE 3.1—PIN CONFIGURATION             | <br> | 12 |

|------------------------------------------|------|----|

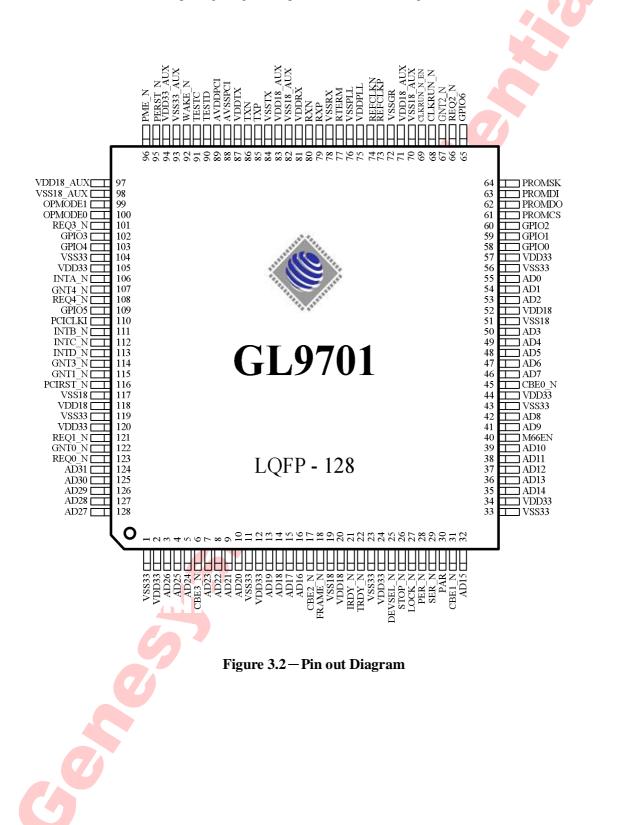

| FIGURE 3.2—PIN OUT DIAGRAM               |      |    |

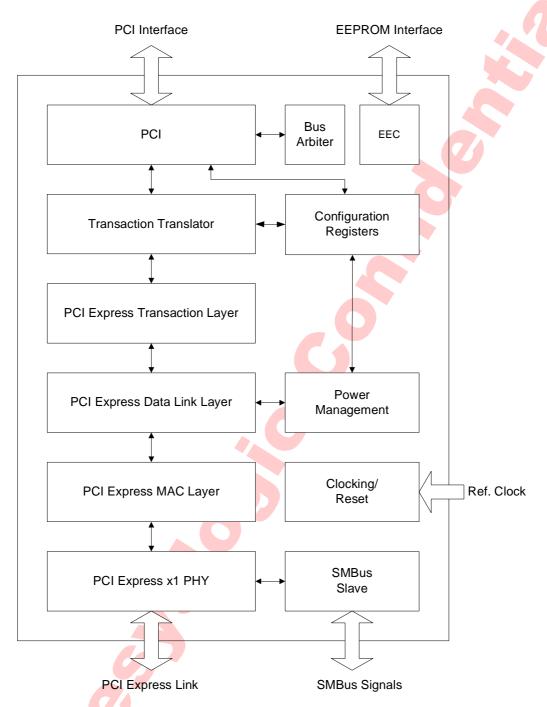

| FIGURE 4.1 – GL9701 BLOCK DIAGRAM        |      | 21 |

| FIGURE 6.1 – GL9701 CAPABILITIES         | <br> | 31 |

| FIGURE 9.1—CL 0701 129 DIN L OFD DACKAGE |      | 7/ |

# LIST OF TABLES

| TABLE 3.1—SIGNAL TYPE                | 14 |

|--------------------------------------|----|

| TABLE 4.1—SUPPORTED PCI COMMAND      |    |

| TABLE 6.1 — NOTATION FOR ATTRIBUTE   |    |

| TABLE 6.2—LEGACY CONFIGURATION SPACE |    |

| TABLE 6.3—PCI EXPRESS EXTENDED CONFI |    |

| TABLE 9.1 — ORDERING INFORMATION     |    |

#### **CHAPTER 1 GENERAL DESCRIPTION**

PCI Express is a general-purpose interconnection technology to achieve high performance and flexibility at competitive cost for future computing and communication platforms. The GL9701 PCI Express to PCI Bridge provides a solution to connect PCI Express with existing PCI domain. This is referred to as a "PCI Express to PCI bridge" or simply as a "bridge", which features a PCI Express primary interface and a PCI secondary interface. A bridge can be used to enable existing PCI based application to plug into a PCI Express based system.

#### **CHAPTER 2 FEATURES**

#### 2.1 PCI Express Features

- Compliant to PCI Express Base Specification Revision 1.0a

- Compliant to PCI Express to PCI Bridge Specification Revision 1.0

- Support Single One-Lane PCI Express Connection

- Support 32-bit CRC Covering All Transmitted Data Packets

- Support 16-bit CRC On All Link Message Information

- Support PCI Express Advanced Error Reporting Capability

- Support Error Forwarding Including Data Poisoning and PCI Bus Parity Errors.

- Support 100MHz PCI Express Differential Reference Clock.

- Secondary Side Initialization via Type 0 Configuration Cycles

- Support Variable Payload Size (up to 512 bytes)

- Support Variable Size of Read Request (up to 512 bytes)

#### 2.2 PCI Interface Features

- Compliant to PCI Local Bus Specification Revision 3.0

- Support PCI 32-bit, 33/66 MHz, 3.3V, NOT 5V tolerant

- Support Five External REQ/GNT Pairs For Internal Arbiter

- Support PCI LOCK Operation

- Support up to Two PCI Delayed Transaction (memory read, I/O read/write, and configuration read/write)

- Support Clock Run Operation

- Support Five 33MHz/66MHz PCI Clock Outputs

#### 2.3 Power Management

- Support D0, D1, D2, D3hot and D3cold device power states defined in PCI Power Management Specification Rev 1.1

- Support PME event propagation on behalf of PCI devices

- Side-band WAKE# signals

- PCI Express Active Power Management states (ASPM): L0s and L1

- Support link power management: L0, L0s, L1, L2

- In-band beacon generation

- Integrated AUX Power Plane

#### 2.4 SMBus Interface

- Compliant to System Management Bus Specification, Revision 2.0

- Support Slave-mode operation only

- Support configuration of PCI Express PHY via SMBus

# **CHAPTER 3 Pin Assignment**

The "\_N" symbol at the end of signal name indicates that the active (asserted) state occurs when the signal is at low voltage level. When "\_N" is not present after the signal name, the signal is asserted at the high voltage level.

#### 3.1 Pin Configuration

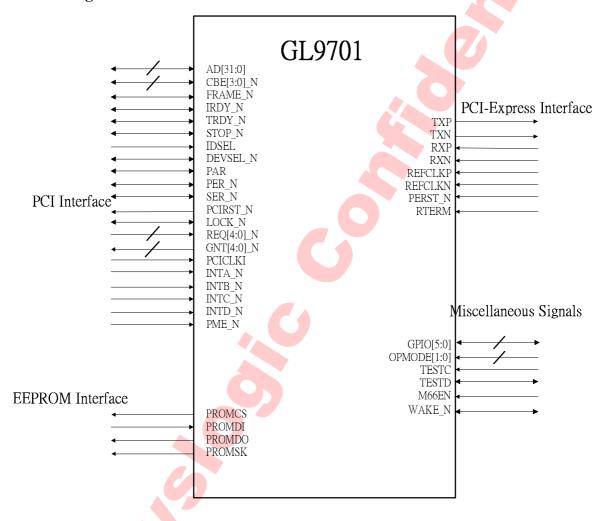

Figure 3.1—Pin Configuration

#### 3.2 PinOut

GL9701 uses LQFP128 package. Figure 4.2 presents the Pin out Diagram of GL9701.

The following notations are used to describe signal type:

| Signal Type | Description                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------|

| I           | Input pin.                                                                                                   |

| 0           | Output pin                                                                                                   |

| TS          | Tri-state input/output pin.                                                                                  |

| STS         | Sustained Tri-State is an active low tri-state  Signal owned and driven by one and only one agent at a time. |

| P           | Power pin                                                                                                    |

| OD          | Open Drain allows multiple devices to share as a wire-OR.                                                    |

| LVDO        | Low-voltage differential output                                                                              |

| LVDI        | Low-voltage differential input                                                                               |

Table 3.1—Signal Type

# 3.3Numeric Pin Assignment List

| Pin Number | Pin Name | Туре | Pin Number | Pin Name    | Туре |

|------------|----------|------|------------|-------------|------|

| 1          | VSS33    | P    | 65         | GPIO6       | TS   |

| 2          | VDD33    | P    | 66         | REQ2_N      | I    |

| 3          | AD26     | TS   | 67         | GNT2_N      | О    |

| 4          | AD25     | TS   | 68         | CLKRUN_N    | I    |

| 5          | AD24     | TS   | 69         | CLKRUN_N_EN | TS   |

| 6          | CBE3_N   | TS   | 70         | VSS18_AUX   | P    |

| 7          | AD23     | TS   | 71         | VDD18_AUX   | P    |

| 8          | AD22     | TS   | 72         | VSSGR       | P    |

| 9          | AD21     | TS   | 73         | REFCLKP     | LVDI |

| 10         | AD20     | TS   | 74         | REFCLKN     | LVDI |

| 11         | VSS33    | P    | 75         | VDDPLL      | P    |

| 12         | VDD33    | P    | 76         | VSSPLL      | P    |

| 13 | AD19     | TS  | 77  | RTERM     | I    |

|----|----------|-----|-----|-----------|------|

| 14 | AD18     | TS  | 78  | VSSRX     | P    |

| 15 | AD17     | TS  | 79  | RXP       | LVDI |

| 16 | AD16     | TS  | 80  | RXN       | LVDI |

| 17 | CBE2_N   | TS  | 81  | VDDRX     | P    |

| 18 | FRAME_N  | STS | 82  | VSS18_AUX | P    |

| 19 | VSS18    | P   | 83  | VDD18_AUX | P    |

| 20 | VDD18    | P   | 84  | VSSTX     | P    |

| 21 | IRDY_N   | STS | 85  | TXP       | LVDO |

| 22 | TRDY_N   | TS  | 86  | TXN       | LVDO |

| 23 | VSS33    | P   | 87  | VDDTX     | P    |

| 24 | VDD33    | P   | 88  | AVSSPCI   | P    |

| 25 | DEVSEL_N | STS | 89  | AVDDPCI   | P    |

| 26 | STOP_N   | STS | 90  | TESTD     | TS   |

| 27 | LOCK_N   | STS | 91  | TESTC     | Ι    |

| 28 | PER_N    | TS  | 92  | WAKE_N    | DO   |

| 29 | SER_N    | OD  | 93  | VSS33_AUX | P    |

| 30 | PAR      | TS  | 94  | VDD33_AUX | P    |

| 31 | CBE1_N   | TS  | 95  | PERST_N   | I    |

| 32 | AD15     | TS  | 96  | PME_N     | I    |

| 33 | VSS33    | P   | 97  | VDD18_AUX | P    |

| 34 | VDD33    | P   | 98  | VSS18_AUX | P    |

| 35 | AD14     | TS  | 99  | OPMODE1   | I    |

| 36 | AD13     | TS  | 100 | OPMODE0   | I    |

| 37 | AD12     | TS  | 101 | REQ3_N    | I    |

| 38 | AD11     | TS  | 102 | GPIO3     | TS   |

| 39 | AD10     | TS  | 103 | GPIO4     | TS   |

| 40 | M66EN    | I   | 104 | VSS33     | P    |

| 41 | AD9      | TS  | 105 | VDD33     | P    |

| 42 | AD8      | TS  | 106 | INTA_N    | TS   |

| 43 | VSS33    | P   | 107 | GNT4_N    | 0    |

| 44 | VDD33    | P   | 108 | REQ4_N    | I    |

| 45 | CBE0_N   | TS  | 109 | GPIO5     | TS   |

| 46 | AD7    | TS | 110 | PCICLKI  | I  |

|----|--------|----|-----|----------|----|

| 47 | AD6    | TS | 111 | INTB_N   | I  |

| 48 | AD5    | TS | 112 | INTC_N   | 1  |

| 49 | AD4    | TS | 113 | INTD_N   | I  |

| 50 | AD3    | TS | 114 | GNT3_N   | 0  |

| 51 | VSS18  | P  | 115 | GNT1_N   | О  |

| 52 | VDD18  | P  | 116 | PCIRST_N | О  |

| 53 | AD2    | TS | 117 | VSS18    | P  |

| 54 | AD1    | TS | 118 | VDD18    | P  |

| 55 | AD0    | TS | 119 | VSS33    | P  |

| 56 | VSS33  | P  | 120 | VDD33    | P  |

| 57 | VDD33  | P  | 121 | REQ1_N   | I  |

| 58 | GPIO0  | TS | 122 | GNT0_N   | 0  |

| 59 | GPIO1  | TS | 123 | REQ0_N   | I  |

| 60 | GPIO2  | TS | 124 | AD31     | TS |

| 61 | PROMCS | 0  | 125 | AD30     | TS |

| 62 | PROMDO | 0  | 126 | AD29     | TS |

| 63 | PROMDI | I  | 127 | AD28     | TS |

| 64 | PROMSK | 0  | 128 | AD27     | TS |

# 3.4 Signal Description

# **3.4.1 PCI-Express Interface**

| Name     | Type | Description                           |

|----------|------|---------------------------------------|

| TXP,     | LVDO | Transmitter differential pair         |

| TXN      |      |                                       |

| RXP,     | LVDI | Receiver differential pair            |

| RXN      |      |                                       |

| REFCLKP, | LVDI | 100 MHz differential clock input      |

| REFCLKN  |      |                                       |

| PERST_N  | I    | External reset, low active            |

| RTERM    | I    | Connect to a resistor for calibration |

# 3.4.2 Secondary PCI Interface

| Name       | Type | Description                                                                |  |

|------------|------|----------------------------------------------------------------------------|--|

| AD[31:0]   | TS   | Address/Data                                                               |  |

| CBE[3:0]_N | TS   | Command/Byte Enable                                                        |  |

| FRAME_N    | STS  | Secondary PCI interface frame                                              |  |

| IRDY_N     | STS  | Secondary PCI interface initiator ready                                    |  |

| TRDY_N     | STS  | Secondary PCI interface target ready                                       |  |

| STOP_N     | STS  | Secondary PCI interface stop indicator                                     |  |

| DEVSEL_N   | STS  | Secondary PCI interface device select                                      |  |

| PAR        | TS   | Secondary PCI interface parity                                             |  |

| PER_N      | STS  | Secondary PCI interface parity error detect                                |  |

| SER_N      | OD   | Secondary PCI interface system error                                       |  |

| PCIRST_N   | О    | Secondary PCI bus Reset                                                    |  |

| LOCK_N     | STS  | Secondary PCI interface target ready                                       |  |

| REQ[4:0]_N | I    | Requests 4-0, activated by the secondary bus masters to request the        |  |

|            |      | use of the secondary bus.                                                  |  |

|            |      | REQ0_N is a dual-purpose signal. When the bridge's internal arbiter        |  |

|            |      | is enabled, this signal is used as a request input, to be activated by a   |  |

|            |      | secondary bus master requesting the use of the secondary bus. When         |  |

|            |      | the internal arbiter is disabled, REQ0_N is used by the bridge as its      |  |

|            |      | grant input signal.                                                        |  |

| GNT[4:0]_N | О    | Grants 4-0, activated by the bridge's internal arbiter to grant usage of   |  |

|            |      | the secondary bus to the master that activated the corresponding           |  |

|            |      | request signal.                                                            |  |

|            |      | GNT0_N is a dual-purpose signal. When the bridge's internal arbiter        |  |

|            |      | is enabled, this signal is used as a grant output, activated by the bridge |  |

|            |      | to grant the use of the secondary bus to the master who requested the      |  |

|            |      | use with the GNT0_N signal. When the internal arbiter is disabled,         |  |

|            |      | this signal is used by the bridge as its request output signal.            |  |

| PCICLKI    | I    | PCI clock input.                                                           |  |

| INTA_N,    | I    | Interrupt from secondary interface.                                        |  |

| INTB_N,    |      |                                                                            |  |

| INTC_N,    |      |                                                                            |  |

| INTD_N |    |                                                 |

|--------|----|-------------------------------------------------|

| PME_N  | I  | Power management event from secondary interface |

| WAKE_N | OD | Used to implement wakeup mechanism.             |

# **3.4.3 EEPROM Signals**

| Name   | Type | Description                    |  |

|--------|------|--------------------------------|--|

| PROMCS | О    | Enable EEPROM interface        |  |

| PROMDO | О    | Serial data output for EEPROM  |  |

| PROMDI | I    | Serial data input from EEPROM  |  |

| PROMSK | О    | Serial clock output for EEPROM |  |

# 3.4.4 Miscellaneous Signals

| Name      | Type | Description                                                      |

|-----------|------|------------------------------------------------------------------|

| GPIO[6:0] | TS   | The output signals are determined by OPMODE[1:0],                |

|           |      | PCICLKx_MASK(x=0~5) in design option.                            |

|           |      | •For GPIO[2:0]:                                                  |

|           |      | Available only in normal mode. (OPMODE[1:0]=2'b00)               |

|           |      | ■ If PCICLKx_MASK (x=0~2) are not masked (=1'b0), then           |

|           |      | these three bits are used as PCI clock outputs. It's recommended |

|           |      | that GPIO[0] be routed to PCICLKI input.                         |

|           |      | ■ If PCICLKx_MASK (x=0~2) are masked (=1'b1) then these          |

|           |      | three bits are used as output of GPIO signal from design option. |

|           |      | •For GPIO[5:3]:                                                  |

|           |      | • If in normal function mode (OPMODE[1:0]=2'b00), then these     |

|           |      | three bits are used as PCI clock outputs when                    |

|           |      | PCICLKx_MASK(x=5~3) are not masked (=1'b0). These three          |

|           |      | bits are used as GPIO output from design option if               |

|           |      | PCICLKx_MASK(x=5~3) are masked (=1'b1).                          |

|           | 7/   | • If in test mode (OPMODE[1:0]=2'b01), then these three bits are |

|           |      | used as internal signal output.                                  |

|           |      | •For GPIO[6]:                                                    |

|           |      | • If in normal function mode (OPMODE[1:0]=2'b00), the bit is     |

|           |      | used as GPIO pins. Users can specify the output value and        |

|             |    | output enable via design option. Users can also probe the input     |  |

|-------------|----|---------------------------------------------------------------------|--|

|             |    | value by reading the design option.                                 |  |

|             |    | • If in normal function (OPMODE[1:0]=2'b01), then this bit is       |  |

|             |    | used as internal signal output.                                     |  |

| OPMODE[1:0] | I  | Operation mode setup                                                |  |

| TESTC       | I  | Test clock                                                          |  |

| TESTD       | TS | Test data                                                           |  |

| CLKRUN_N    | TS | A PCI device can request GL9701 to start, speed up, or maintain the |  |

|             |    | PCI clock by the assertion of CLKRUN_N. GL9701 is responsible       |  |

|             |    | for maintaining CLKRUN_N asserted, and for driving it high to the   |  |

|             |    | de-asserted state.                                                  |  |

| CLKRUN_N_E  | I  | Clock Run Enable                                                    |  |

| N           |    | 1'b1: Enable Clock Run                                              |  |

|             |    | 1'b0: Disable Clock Run                                             |  |

| M66EN       | I  | Enable PCI clock act as 33MHz or 66MHz.                             |  |

|             |    | 1: PCI Clocks are 66MHz.                                            |  |

|             |    | 0: PCI clocks are 33MHz                                             |  |

# **3.4.5 Power and Ground Signals**

| Name      | Type | Description                                   |  |

|-----------|------|-----------------------------------------------|--|

| VSS33     | P    | Ground for PCI PAD                            |  |

| VDD33     | P    | 3.3V Power Supplier for PCI PAD               |  |

| VSS18_AUX | P    | Ground for 1.8 Vaux                           |  |

| VDD18_AUX | P    | 1.8Vaux Power Supplies for core voltage       |  |

| VSS33_AUX | P    | Ground for 3.3 Vaux                           |  |

| VDD33_AUX | P    | 3.3 Vaux Power Supplies for core voltage      |  |

| VSS18     | P    | Digital ground                                |  |

| VDD18     | P    | 1.8V Power Supplies for core voltage          |  |

| VSSGR     | P    | Ground for the guard ring of the SerDes block |  |

| VDDPLL    | P    | 1.8V Power Supplies for internal PLL          |  |

| VSSPLL    | P    | Ground for internal PLL                       |  |

| VSSRX     | P    | 1.8V Power Supplies for receiver part         |  |

| VDDRX     |      |                                               |  |

| VSSTX<br>VDDTX     | Р | 1.8V Power Supplies for transceiver part |  |

|--------------------|---|------------------------------------------|--|

| AVSSPCI<br>AVDDPCI | P | 1.8V Power Supplier for PCI PLL          |  |

# **CHAPTER 4 Block Diagram**

Figure 4.1 – GL9701 block diagram

The GL9701 is composed of the following major functional blocks as shown in Figure 3-1:

#### PCI interface macro

The macro acts as either a bus master or a bus slave and handles the PCI protocol depending on the transaction types. GL9701 supports 32-bit PCI addressing with 0MHz~33MHz and 66MHz operation frequency.

Table 3.1 summarizes the PCI commands supported by GL9701

| Command Type         | Encoding |

|----------------------|----------|

| I/O Read             | 0010     |

| I/O Write            | 0011     |

| Memory Read          | 0110     |

| Memory Write         | 0111     |

| Configuration Read   | 1010     |

| Configuration Write  | 1011     |

| Memory Read Multiple | 1100     |

| Memory Read Line     | 1110     |

| Memory Write and     | 1111     |

| Invalidate           |          |

Table 4.1—Supported PCI Command

#### • Bus Arbiter

This block supports PCI bus arbiter for secondary PCI bus. The bus arbitration is provided by GL9701 and supports up to five external masters. The arbiter can be disabled by external EEPROM.

#### • Configuration Registers

This module supports two mechanisms for configuration space access: PCI compatible and PCI Express enhanced configuration mechanism.

#### • Power Management

The moudle is in charge of power management event signaling. This module enables GL9701 to enter software driven D-state transitions.

#### • Transaction Translator

The Transaction Translator manages all the bridge operation between PCI Express and PCI interface. It is responsible for PCI Express to PCI command translation, message translation and managing transaction ordering.

#### • PCI Express Transaction Layer

The layer's function is the assembly and disassembly of Transaction Layer Packets (TLPs). It is also responsible for managing credit-based flow control for TLPs.

#### • PCI Express Data Link Layer

The layer serves as an intermediate stage between the Transaction Layer and the Physical Layer. The responsibility is Link management and data integrity including error detection and error correction.

#### • PCI Express MAC Layer

The Layer can be taken as a part of Physical Layer. It includes link initialization, link state management, lane alignment, data scrambling and descrambling.

#### PCI Express x1 PHY

The PHY includes all circuitry for interface operation for an x1 link, including driver and input buffers, parallel-to-serial and serial-to-parallel conversion, PLL(s) and impedance matching circuitry. It also includes logical function related to 8b/10b encoding/decoding and PHY status report.

#### • SMBus Slave

The SMBus Slave handles SMBus protocol and provides the access to internal registers such as chip information, function options and some test setting.

#### • EEC, EERPOM Controller

Provide a download path for chip configuration and information.

#### • Clocking/Reset

Provide a clocking and reset to manage all blocks.

#### **CHAPTER 5 Function Description**

#### **5.1 Power Management**

GL9701 supports PCI-PM 1.1 Compatible Power Management and Active State Power Management (ASPM) defined in PCI Express Base Specification Revision 1.0a.

#### **5.1.1 PCI-PM Software Compatible Power Management**

GL9701 supports link states L0, L1 and L2 needed to implement PCI-PM compatible power states D0, D1, D2 and D3hot. All link states are determined by the D-state of the bridge. Because GL9711 provides Vaux, bridge will enter into L2 state when software direct bridge into D3hot state. Refer to the *PCI Express Base Specification Revision 1.0a* for more protocol information involved in transitioning the link to the L1 or L2 state.

#### 5.1.2 Hardware-Controlled Active State Power Management

GL9701 supports a hardware-initiated power management mechanism which is called Active State Power Management (ASPM). Once this feature is enabled, bridge will drive the link state into a low-power L0s link state or even lower-power L1 link state. Refer to the PCI Express Base Specification Revision 1.0a for more information about ASPM.

Once system software enables GL9701's ASPM capability by setting the ASPM Control bit of Link Control Register to high, GL9701 will behavior ASPM specified in PCI Express Base Specification Revision 1.0a by default. However, GL9701 can disable this mechanism via the optional setting specified in table6.1. The optional bit is the 30<sup>th</sup> bit of Configuration Space Register with offset 'hc8. If this bit is set to low, then GL9701 will never act ASPM behavior no matter what value of the ASPM Control bit of Link Control Register.

#### 5.1.3 In-band Beacon

Beacon is a in-band signal used to exit the L2 link power management state and informs the Root Complex to re-activate the link. When the bridge is directed into D3hot State, the link state will finally stay in L2 State. The device on the secondary PCI bus wakes up the system by asserting PME\_N. GL9701 then outputs the beacon signal on the upstream PCI Express link. Root complex should re-apply the power and reference clock again after detecting the beacon.

#### 5.1.4 Side-band WAKE\_N

GL9701 supports two means to signal the platform to re-establish the power and reference clock while the bridge is placed into D3hot state. One is Beacon, and the other is WAKE\_N. WAKE\_N.

WAKE\_N is a side-band signal and is low active. Similar with Beacon, the bridge only outputs WAKE\_N when the bridge detects PME\_N asserted by the device on the secondary PCI bus when the bridge is placed into D3hot state.

#### **5.1.5 Power Management System Messages**

GL9701 supports all messages involved in the Power Management. GL9701 either initiates or receives them. Table5-1 outlines their characteristics.

| Packet                     | Туре |

|----------------------------|------|

| PM_Enter_L1                | DLLP |

| PM_Enter_L23               | DLLP |

| PM_Active_State_Request_L1 | DLLP |

| PM_Request_Ack             | DLLP |

| PM_Active_State_Nak        | TLP  |

| PM_PME                     | TLP  |

| PME_Turn_Off               | TLP  |

| PME_TO_Ack                 | TLP  |

#### 5.2 PCI Clock Run

GL9701 supports Clock Run functionality specified in *PCI Mobile Design Guide v1.1*. CLKRUN\_N is an optional signal used by devices to request starting (or speeding up) the clock. A device requests the central resource to start, speed up, or maintain the PCI clock by the assertion of CLKRUN\_N. The central resource is responsible for maintaining CLKRUN\_N asserted, and for driving it high to the de-asserted state.

Clock Run functionality in GL9701 can be enabled by the asserting CLKRUN\_N\_EN (PIN69) to high. When the function is enabled, GL9701 plays the role of central resource. There is a ODT inside the CLKRUN\_N (PIN68), so there is no need to add an external pull up resistor on the CLKRUN\_N.

#### 5.3 PCI Clock

GL9701 supports five PCI slots on the secondary PCI interface. To provide the devices on these slots and GL9701 itself can work properly, GL9701 provides six PCI clock sources.

The operational frequency of these PCI clocks can be configured by M66EN (PIN40). When it's set to high, then the PCI clocks will operate at 66MHz. When it's set to low, then these clocks will operate at 33MHz.

The six clock output are at GLIO0 ~ GPIO5. It's recommended that GPIO0 be connected to PCICLKI (PIN110) to feed GL9701 itself. GPIO1 ~ GPIO5 then can be distributed to the five PCI slots. Users may optionally implement the number of PCI slots greater than one and less than five. Users can even use an external PCI clock source to maintain the normal operation of GL9701 and its secondary PCI slots.

If not all the five PCI slots are utilized, users can use the GPIOx ( $x=1\sim5$ , 0 is valid when an external PCI clock source is provided) for the use of General Purpose I/O. The optional use between PCI clock source and GPIO can be determined by the PCICLK\_MASKx ( $x=0\sim5$ ).

When PCICLK\_MASKx (x=0~5) is set, the PCI clock output of the corresponding GPIOx is masked. The GPIOx then becomes a General Purpose I/O. Users then can arbitrarily specify the output enable control (GPIOx\_OE) and the output value (GPIOxO) for the GPIOx.

GL9701 also provides a General Purpose I/O, GPIO6 (PIN65), for users to use. Unlike GPIO0~GPIO5, this pin does not Mux other functions. Users just have to control the output enable (GPIO6\_OE) and its output value (GPIO6O).

#### 5.4 Interrupt mapping

PCI INTx interrupts are "virtualized" in PCI Express using Assert\_INTx and Deassert\_INTx messages, where x is A, B, C, and D for the respective PCI INTx# interrupt signals defined in PCI 3.0. This message pairing provides a mechanism to preserve the level-sensitive semantics of the PCI interrupts. The Assert\_INTx and Deassert\_INTx messages transmitted on the PCI Express Link capture the asserting/deasserting edge of the respective PCI INTx# signal.

GL9701 is a multi-ported PCI Express bridge. A multi-ported PCI Express bridges must collapse the INTA#-INTD# pins from each of their downstream conventional PCI interface into four INTx "virtual wires" on their Upstream Port. The mapping between the INTx# pin on a PCI bus and the corresponding INTx messages on the PCI Express Link is based on the device number of the PCI bridge assigned to the port requesting the interrupt. The mapping is as follows:

| Device Number of    | INTx# Interrupt Line from | Mapping to INTx Virtual |

|---------------------|---------------------------|-------------------------|

| Conventional GL9701 | Downstream                | Wire on Primary Side of |

| Supporting          | Conventional PCI          | Bridge                  |

| Secondary Interface | Interface                 |                         |

| (Interrupt Source)  |                           |                         |

|                     | INTA#                     | INTA                    |

| 0, 4                | INTB#                     | INTB                    |

| 0,4                 | INTC#                     | INTC                    |

|                     | INTD#                     | INTD                    |

|                     | INTA#                     | INTB                    |

| 1                   | INTB#                     | INTC                    |

| 1                   | INTC#                     | INTD                    |

|                     | INTD#                     | INTA                    |

|                     | INTA#                     | INTC                    |

| 2                   | INTB#                     | INTD                    |

| 2                   | INTC#                     | INTA                    |

|                     | INTD#                     | INTB                    |

|                     | INTA#                     | INTD                    |

| 3                   | INTB#                     | INTA                    |

| 3                   | INTC#                     | INTB                    |

|                     | INTD#                     | INTC                    |

#### **5.5 Initial Flow Control Advertisements**

Flow control value for various credit type is advertised after the link is established. The initial value for each credit type in GL9701 is as followed:

| Credit Type                           | Initial Flow Control Value |

|---------------------------------------|----------------------------|

| Posted Request headers (PH)           | 04h                        |

| Posted Request Data payload (PD)      | 20h                        |

| Non-Posted Request headers (NPH)      | 04h                        |

| Non-Posted Request Data payload (NPD) | 04h                        |

| Completion headers (CPLH)             | 08h                        |

| Completion Data payload (CPLD)        | 20h                        |

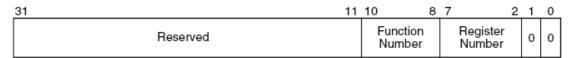

#### 5.6 IDSEL Mapping

While receiving a Type1 Configuration Cycle from the upstream PCI Express port, GL9701 will convert it into a Type0 Configuration Cycle if the bus number is within the range specified by the Primary Bus Number Register and the Secondary Bus Number Register.

The format of a Type0 Configuration Cycle is as followed:

Type 0

GL9701 converts the destination ID device number to one of the AD[31:16] as the IDSEL of the five PCI slots. The mapping between the AD[31:16] and Device Number is:

| Device Number [4:0] | AD[31:16]           |

|---------------------|---------------------|

| 00000               | 0000_0000_0000_0001 |

| 00001               | 0000_0000_0000_0010 |

| 00010               | 0000_0000_0000_0100 |

| 00011               | 0000_0000_0000_1000 |

| 00100               | 0000_0000_0001_0000 |

| 00101               | 0000_0000_0010_0000 |

# **CHAPTER 6 Register Description**

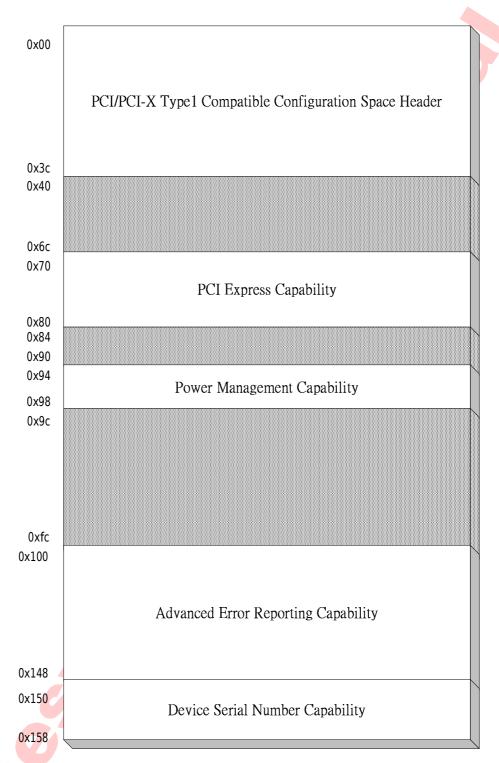

GL9701 implements the standard PCI Express-to-PCI Bridge configuration space format. Figure 5.1 shows the capabilities supported by GL9701. Table 5.1 and Table 5.2 represent the configuration registers of GL9701 and their address byte offset values.

Configuration register fields are assigned one of the attributes described in Table 5.1.

| Register Attribute | Description                                                     |  |

|--------------------|-----------------------------------------------------------------|--|

| HwInit             | Hardware Initialized: Register bits are initialized by          |  |

| 2211222            | firmware or hardware mechanisms such as pin strapping or        |  |

|                    | serial EEPROM. Bits are read-only after initialization and can  |  |

|                    | only be reset (for write-once by firmware) with Fundamental     |  |

|                    | Reset.                                                          |  |

| RO                 | Read-only register: Register bits are read-only and cannot be   |  |

|                    | altered by software. Register bits may be initialized by        |  |

|                    | hardware mechanisms such as pin strapping or serial             |  |

|                    | EEPROM.                                                         |  |

| RW                 | Read-Write register: Register bits are read-write and may be    |  |

|                    | either set or cleared by software to the desired state.         |  |

| RW1C               | Read-only status, Write-1-to-clear status register: Register    |  |

|                    | bits indicate status when read, a set bit indicating a status   |  |

|                    | event may be cleared by writing a 1. Writing a 0 to RW1C        |  |

|                    | bits has no effect.                                             |  |

| ROS                | Sticky - Read-only register: Registers are read-only and        |  |

|                    | cannot be altered by software. Registers are not initialized or |  |

|                    | modified by hot reset.                                          |  |

| RWS                | Sticky – Read-Write register: Registers are read-write and      |  |

|                    | may be either set or cleared by software to the desired state.  |  |

|                    | Bits are not initialized or modified by hot reset.              |  |

| RW1CS              | Sticky – Read-only status, Write-1-to-clear status register:    |  |

|                    | Registers indicate status when read, a set bit indicating a     |  |

|                    | status event may be cleared by writing a 1. Writing a 0 to      |  |

|                    | RW1CS bits has no effect. Bits are not initialized or modified  |  |

|                    | by hot reset.                                                   |  |

| RsvdP              | Reserved and Preserved: Reserved for future RW                  |  |

|       | implementations; software must preserve value read for   |  |

|-------|----------------------------------------------------------|--|

|       | writes to bits.                                          |  |

| RsvdZ | Reserved and Zero: Reserved for future RW1C              |  |

|       | implementations; software must use 0 for writes to bits. |  |

Table 6.1 – Notation for attribute

Figure 6.1 – GL9701 Capabilities

# Byte Offset

Bit31 0

|              | Device                           | e ID              | Ver                    | ndor ID              | 00h |

|--------------|----------------------------------|-------------------|------------------------|----------------------|-----|

|              | Stat                             | us                | Command                |                      | 04h |

|              |                                  | Class Code        |                        | Revision ID          | 08h |

|              | BIST                             | Header Type       | Primary                | Cache Line Size      | 0Ch |

|              |                                  |                   | <b>Latency Timer</b>   |                      |     |

|              |                                  | Base Ad           | ldress Register 0      |                      | 10h |

|              |                                  | Base Ad           | ldress Register 1      |                      | 14h |

|              | Secondary                        | Subordinate       | Secondary Bus          | Primary Bus          | 18h |

|              | Latency timer                    | <b>Bus Number</b> | Number                 | Number               |     |

| Type1 Header | Secondar                         | y Status          | I/O Limit              | I/O Base             | 1Ch |

|              | Memory                           | Limit             | Men                    | nory Base            | 20h |

|              | Prefetchable M                   | lemory Limit      | Prefetchab             | le Memory Base       | 24h |

|              |                                  | Prefetchable      | e Base Upper 32 B      | its                  | 28h |

|              | Prefetchable Limit Upper 32 Bits |                   |                        |                      |     |

|              | I/O Limit Upper 16 Bits          |                   | I/O Base Upper 16 Bits |                      | 30h |

|              |                                  | Reserved          |                        | Capabilities Pointer | 34h |

|              | Expansion ROM Base Address       |                   |                        |                      |     |

|              | Bridge (                         | Control           | Interrupt Pin          | Interrupt Line       | 3Ch |

|              | PCI Express                      | Capabilities      | Next Cap Pointer       | PCI Express          |     |

|              | Regis                            | ster              |                        | Cap ID               | 70h |

|              |                                  |                   |                        |                      |     |

|              |                                  | Device            | ce Capabilities        |                      | 74h |

| PCI Express  | Device                           | Status            | Devi                   | ce Control           | 78h |

| Capability   |                                  | Link              | Capabilities           |                      | 7Ch |

|              | Link S                           | Status            | Link Control           |                      | 80h |

|              | Reserved                         |                   |                        |                      |     |

|              | Rese                             | rved              | Reserved               |                      | 88h |

|              | Rese                             | rved              | Reserved               |                      | 8Ch |

|              |                                  | ]                 | Reserved               |                      | 90h |

| Power      | Power Management Capability |            | Next Pointer(43h) | PM Capability ID | 94h |

|------------|-----------------------------|------------|-------------------|------------------|-----|

| Management | register                    |            |                   |                  |     |

| Capability | Data PM Ctrl/Stat           |            | Power Manage      | ment Status and  | 98h |

|            |                             | Bridge Ext | Cor               | ntrol            |     |

**Table 6.2—Legacy Configuration Space**

#### **PCI Express Extended Capabilities Space**

|               | <b>Advanced Error Reporting</b>     | Next Cap Pointer                 | PCI Express       | 100h |  |  |

|---------------|-------------------------------------|----------------------------------|-------------------|------|--|--|

|               | Capability Header                   |                                  | Extended          |      |  |  |

|               |                                     |                                  | Capability ID     |      |  |  |

|               | Uncorrectable                       | Error Status Regis               | ster              | 104h |  |  |

|               | Uncorrectable                       | e Error Mask Regis               | ter               | 108h |  |  |

|               | Uncorrectable                       | Error Severity Reg               | ister             | 10Ch |  |  |

|               | Correctable 1                       | Error Status <mark>Regist</mark> | er                | 110h |  |  |

| Advanced      | Correctable                         | Error <mark>Mask Reg</mark> ist  | er                | 114h |  |  |

| Error         | Advanced Error Cap                  | abilities and Contro             | ol Register       | 118h |  |  |

| Reporting     |                                     |                                  |                   |      |  |  |

| Capability    |                                     |                                  |                   |      |  |  |

|               | Header Log Register                 |                                  |                   |      |  |  |

|               |                                     |                                  |                   |      |  |  |

|               | Root Error Command –Not Implemented |                                  |                   |      |  |  |

|               | Root Error Status –Not Implemented  |                                  |                   |      |  |  |

|               |                                     |                                  | Correctable Error | 134h |  |  |

|               | Error Source ID Register -N         | ot Implemented                   | Source ID         |      |  |  |

|               |                                     |                                  | Register – Not    |      |  |  |

|               |                                     | Implemented                      |                   |      |  |  |

| Device Serial | PCI Express Enh                     | anced Capability H               | leader            | 150h |  |  |

| Number        | Serial Number Register (Lower DW)   |                                  |                   |      |  |  |

| Capability    | Serial Number Register (Upper DW)   |                                  |                   |      |  |  |

|               |                                     |                                  |                   |      |  |  |

Table 6.3 – PCI Express Extended Configuration Space

#### 6.1 Offset 00h: Device Identification

Generic configuration software will be able to determine what devices are available on PCI bus via these information. All of these registers are read-only.

| Bits  | Type | Default | Description                                                              |

|-------|------|---------|--------------------------------------------------------------------------|

| 15:0  | RO   | 17a0h   | <b>Vendor ID</b> : This field identifies the manufacturer of the device. |

| 31:16 | RO   | 7163    | <b>Device ID</b> : This field identifies the particular device.          |

# 6.2 Offset 04h: Command Register

| Bits | Type | Default | Description                                                          |

|------|------|---------|----------------------------------------------------------------------|

|      |      |         | I/O Space: Controls a device's response to I/O Space accesses.       |

| 0    | RW   | 0b      | 0– Disables the device resp <mark>onse.</mark>                       |

|      |      |         | 1– Allows the device torespond to I/O Space accesses.                |

|      |      |         | Memory Space: Controls a device's response to Memory Space           |

| 1    | RW   | 0b      | accesses.                                                            |

| 1    | ΚW   | 00      | 0– Disables the device response.                                     |

|      |      |         | 1– Allows the device to respond to Memory Space accesses.            |

|      |      |         | Bus Master: Controls a device's ability to act as a master on the    |

|      | DW   | 01      | PCI bus.                                                             |

| 2    | RW   | 0b      | 0- Disables the device from generating PCI accesses.                 |

|      |      |         | 1- Allows the device to behave as a bus master.                      |

| 3    | RO   | 0b      | Special Cycles: Does not apply to PCI Express Bridge.                |

|      |      |         | Memory Write and Invalidate Enable: GL9701 does not                  |

| 4    | RO   | 0b      | optionally promote Memory Write Requests to Memory Write             |

|      |      |         | and Invalidate transactions on PCI.                                  |

| 5    | RO   | 0b      | VGA Palette Snoop: Does not apply to PCI Express bridges.            |

|      |      | 76)     | Parity Error Response:                                               |

|      |      |         | Controls the bridge's setting of the Master Data Parity Error bit in |

| 6    | RW   | 0b      | the Status register in response to a received poisoned TLP from      |

|      |      |         | PCI Express.                                                         |

|      |      |         | 0 – Disables the setting of the Master Data Parity Error bit.        |

|       |    |     | 1– Enables the setting of the Master Data Parity Error bit.                                                                                                                                |

|-------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | RO | 0b  | Reserved                                                                                                                                                                                   |

|       |    |     | <b>SERR# Enable:</b> This bit enables reporting of non-fatal and fatal errors to the Root Complex. In addition, this bit enables transmission by the primary interface of ERR_NONFATAL and |

|       |    |     | ERR_FATAL error messages on behalf of SERR# assertions detected on the secondary interface. Note that errors are reported if                                                               |

| 8     | RW | 0b  | enabled either through this bit or through the PCI Express specific bits in the Device Control register.                                                                                   |

|       |    |     | 0 – Disable the reporting of bridge non-fatal errors and fatal errors to the Root Complex.                                                                                                 |

|       |    |     | 1 – Enable the reporting of bridge non-fatal errors and fatal errors to the Root Complex.                                                                                                  |

| 9     | RO | 0b  | Fast Back-to-Back Transactions Enable: Does not apply to PCI Express bridges.                                                                                                              |

| 10    | RW | 0b  | Interrupt Disable: GL9701 does not generate INTx interrupt                                                                                                                                 |

|       | _  |     | messages on behalf of internal sources hence implements this bit as read-only with a value of $0$ .                                                                                        |

| 15:11 | RO | 00h | Reserved                                                                                                                                                                                   |

# 6.3 Offset 06h: Status Register

| Bits | Туре | Default | Description                                                     |

|------|------|---------|-----------------------------------------------------------------|

| 2:0  | RO   | 0h      | Reserved                                                        |

| 3    | RO   | 0b      | Interrupt Status – Indicates that an INTx interrupt message is  |

|      |      |         | pending on behalf of sources internal to the bridge.            |

| 4    | RO   | 1b      | Capabilities List – Indicates the presence of a Capability List |

|      |      |         | item.                                                           |

| 5    | RO   | 0b      | <b>66 MHz Capable</b> – Does not apply to PCI Express bridges.  |

| 6    | RO   | 0b      | Reserved                                                        |

| 7    | RO   | 0b      | Fast Back-to-Back Transactions Capable – Does not apply to      |

|      |      |         | PCI Express bridges.                                            |

|      |      |     | Master Data Parity Error – This bit is used to report the             |

|------|------|-----|-----------------------------------------------------------------------|

|      |      |     | detection of uncorrectable data errors by the bridge. This bit is set |

|      |      |     | if the Parity Error Response bit in the Command register is set and   |

|      |      |     | either of the following two conditions occur:                         |

|      |      |     | . The bridge receives a Completion with data marked                   |

| 8    | RW1C | 0b  | poisoned on the primary interface.                                    |

|      |      |     | . The bridge poisons a write Request on the primary interface.        |

|      |      |     | 0 – No uncorrectable data error detected on the primary               |

|      |      |     | interface.                                                            |

|      |      |     | 1- Uncorrectable data error detected on the primary                   |

|      |      |     | interface.                                                            |

| 10.0 | D.O. | 001 | DEVSEL# Timing – Does not apply to PCI Express bridges.               |

| 10:9 | RO   | 00b | Must be hardwired to 00b.                                             |

|      |      |     | Signaled Target-Abort – This bit is set when the bridge               |

|      |      |     | generates a completion with Completer Abort Completion Status in      |

|      |      |     | response to a request received on its primary interface.              |

| 11   | RW1C | 0b  | 0 – Completer Abort Completion not transmitted on the                 |

|      |      |     | primary interface.                                                    |

|      |      |     | 1 – Completer Abort Completion transmitted on the primary             |

|      |      |     | interface.                                                            |

|      |      |     | Received Target-Abort – This bit is set when the bridge               |

|      |      |     | receives a Completion with Completer Abort Completion Status on       |

|      |      |     | its primary interface.                                                |

| 12   | RW1C | 0b  | 0 - Completer Abort Completion Status not received on                 |

|      |      |     | primary interface.                                                    |

|      |      |     | 1 – Completer Abort Completion Status received on primary             |

|      |      |     | interface.                                                            |

|      |      |     | Received Master-Abort – This bit is set when the bridge               |

|      |      |     | receives a Completion with Unsupported Request Completion             |

|      |      | 7/  | Status on its primary interface.                                      |

| 13   | RW1C | 0b  | 0 – Unsupported Request Completion Status not received on             |

|      |      |     | primary interface.                                                    |

|      |      |     | 1 – Unsupported Request Completion Status received on                 |

|      |      |     | primary interface.                                                    |

|     | ī    |         | _                                                                        |

|-----|------|---------|--------------------------------------------------------------------------|

|     |      |         | <b>Signaled System Error</b> – This bit is set when the bridge sends an  |

|     |      |         | ERR_FATAL or ERR_NONFATAL message to the Root                            |

|     |      |         | Complex and the SERR# Enable bit in the Command register is              |

| 1.4 | DW1G | 01      | set.                                                                     |

| 14  | RW1C | 0b      | 0 – Neither ERR_FATAL nor ERR_NONFATAL transmitted                       |

|     |      |         | on primary interface.                                                    |

|     |      |         | 1 – ERR_FATAL or ERR_NONFATAL transmitted on                             |

|     |      |         | primary interface.                                                       |

|     |      | RW1C 0b | <b>Detected Parity Error</b> – This bit is set by the bridge whenever it |

|     |      |         | receives a poisoned TLP or, if supported, a TLP with bad ECRC            |

|     |      |         | (Read Completion or Write Request) on the primary interface,             |

|     |      |         | regardless of the state the Parity Error Response bit in the             |

| 15  | RW1C |         | Command register.                                                        |

|     |      |         | 0 – Data poisoning and bad ECRC not detected by the                      |

|     |      |         | bridge on its primary interface.                                         |

|     |      |         | 1 – Data poisoning or bad ECRC detected by the bridge on its             |

|     |      |         | primary interface.                                                       |

#### 6.4 Offset 08h: Revision ID

| Bits | Туре | Default | Description                                               |

|------|------|---------|-----------------------------------------------------------|

| 7:0  | RO   | 00h     | <b>Revision ID</b> : Indicates the die version of GL9701. |

### 6.5 Offset 09h: Class Code

| Bits  | Туре | Default | Description                                                                                               |

|-------|------|---------|-----------------------------------------------------------------------------------------------------------|

| 7:0   | RO   | 00h     | <b>Programming Interface (PIF):</b> This bit indicates that this device is standard PCI-to-PCI Bridge.    |

| 15:8  | RO   | 04h     | <b>Sub Class Code</b> ( <b>SCC</b> ): This 8-bit value indicates that this device is a PCI-to-PCI Bridge. |

| 23:16 | RO   | 06h     | <b>Base Class Code (BCC):</b> The value of 06h indicates that this is a bridge device.                    |

#### 6.6 Offset 0ch: Cache Line Size Register

| Bits | Туре | Default | Description                                                      |

|------|------|---------|------------------------------------------------------------------|

| 7:0  | RW   | 00h     | Cache Line Size: Specifies the system cacheline size in units of |

|      |      |         | DWORDs.                                                          |

#### 6.7 Offset 0dh: Primary Latency Timer Register

| Bits | Туре | Default | Description                                                  |

|------|------|---------|--------------------------------------------------------------|

| 7:0  | RO   | 00h     | Primary Latency Timer: The primary/master latency timer does |

| 7.0  | RO   |         | not apply to PCI Express bridges                             |

#### 6.8 Offset 0eh: Header Type Register

| Bits | Type | Default | Description                                                                                                                        |

|------|------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RO   | 01h     | <b>Header Type:</b> Indicates that the header is compatible with PCI system software developed for Type 01h PCI and PCI-X bridges. |

### 6.9 Offset 0fh: Bist Register

| Bits | Туре | Default | Description                         |

|------|------|---------|-------------------------------------|

| 7:0  | RO   | 00h     | BIST: GL9701 does not support BIST. |

#### 6.10 Offset 10h: Base Register0

| Bits | Type | Default | Description                                        |

|------|------|---------|----------------------------------------------------|

| 31:0 | RO   | 00h     | Base Register0: GL9701 does not use base register. |

### 6.11 Offset 14h: Base Register1

| Bits | Туре | Default | Description                                        |

|------|------|---------|----------------------------------------------------|

| 31:0 | RO   | 00h     | Base Register1: GL9701 does not use base register. |

#### 6.12 Offset 18h: Primary Bus Number Register

| Bits | Type | Default | Description                                                                                                                                                                                                                   |

|------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h     | <b>Primary Bus Number:</b> Used to record the Bus Number of the logical PCI bus segment to which the primary interface of the bridge is connected. Configuration software is required to program the value into this register |

#### 6.13 Offset 19h: Secondary Bus Number Register

| Bits | Туре | Default | Description                                                                                                                                                                                         |

|------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h     | Secondary Bus Number: Used to record the Bus Number of the PCI bus segment to which the secondary interface of the bridge is connected. Configuration software programs the value in this register. |

#### 6.14 Offset 1ah: Subordinate Bus Number Register

| Bits | Type | Default | Description                                                                                                                                                                                                             |

|------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h     | <b>Subordinate Bus Number:</b> Used to record the Bus Number of the highest numbered PCI bus segment which is downstream of (or subordinate to) the bridge. Configuration software programs the value in this register. |

### 6.15 Offset 1bh: Secondary Latency Timer Register

| Bits | Type | Default | Description                                                                                                                                             |

|------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h     | <b>Secondary Latency Timer:</b> This register specifies, in units of PCI bus clocks, the value of the Latency Timer for the secondary interface GL9701. |

#### 6.16 Offset 1ch: IO Base and IO Limit Register

| Bits | Туре | Default | Description                                                      |

|------|------|---------|------------------------------------------------------------------|

| 3:0  | RO   | 0h      | I/O Base Addressing Capability: Each of these bits is hard-wired |

|       |    |    | to 0, indicating support for 16-bit I/O addressing only.                                                                                                                                                                                                                       |

|-------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4   | RW | Oh | I/O Base Address Bits [15:12]: These bits define the bottom address of an address range to determine when to forward I/O transactions from one interface to another.  These bits correspond to address lines[15:12] for 4 KB alignment. Bits[11:0] are assumed to be 000h.     |

| 11:8  | RO | Oh | I/O Limit Addressing Capability (IOLC): Each of these bits is hard-wired to 0, indicating support for 16-bit I/O addressing only.                                                                                                                                              |

| 15:12 | RW | Oh | I/O Limit Address Bits [15:12] (IOLA): These bits define the top address of an address range to determine when to forward I/O transactions from PCI Express* to PCI. These bits correspond to address lines[15:12] for 4 KB aligned window. Bits[11:0] are assumed to be FFFh. |

# 6.17 Offset 1eh: Secondary Status Register

| Bits | Туре  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0  | RsvdZ | 00h     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5    | RO    | 1b      | <b>66 MHz Capable:</b> This bit indicates that the secondary interface of the bridge is 66 MHz-capable.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6    | RsvdZ | 0b      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7    | RO    | 0b      | Fast Back-to-Back Transactions Capable: This bit indicates that the secondary interface is not able to receive fast back-to-back cycles.                                                                                                                                                                                                                                                                                                                                                                                                |

| 8    | RW1C  | Ob      | Master Data Parity Error – This bit is used to report the detection of an uncorrectable data error by the bridge. This bit is set if the bridge is the bus master of the transaction on the secondary interface, the Parity Error Response Enable bit in the Bridge Control register is set, and either of the following two conditions occur:  . The bridge asserts PERR# on a read transaction.  . The bridge detects PERR# asserted on a write transaction.  Once set, this bit remains set until it is reset by writing a 1 to this |

|      |      |     | · · · · · · · · · · · · · · · · · · ·                                 |

|------|------|-----|-----------------------------------------------------------------------|

|      |      |     | bit location. If the Parity Error Response Enable bit is set to zero, |

|      |      |     | this bit will not be set when an error is detected.                   |

|      |      |     | 0 – No uncorrectable data error detected on the secondary             |