# **SL8X371**8-Bit Latched Bidirectional I/O Port

Legacy Device: Philips/Signetics S8X371

### DESCRIPTION

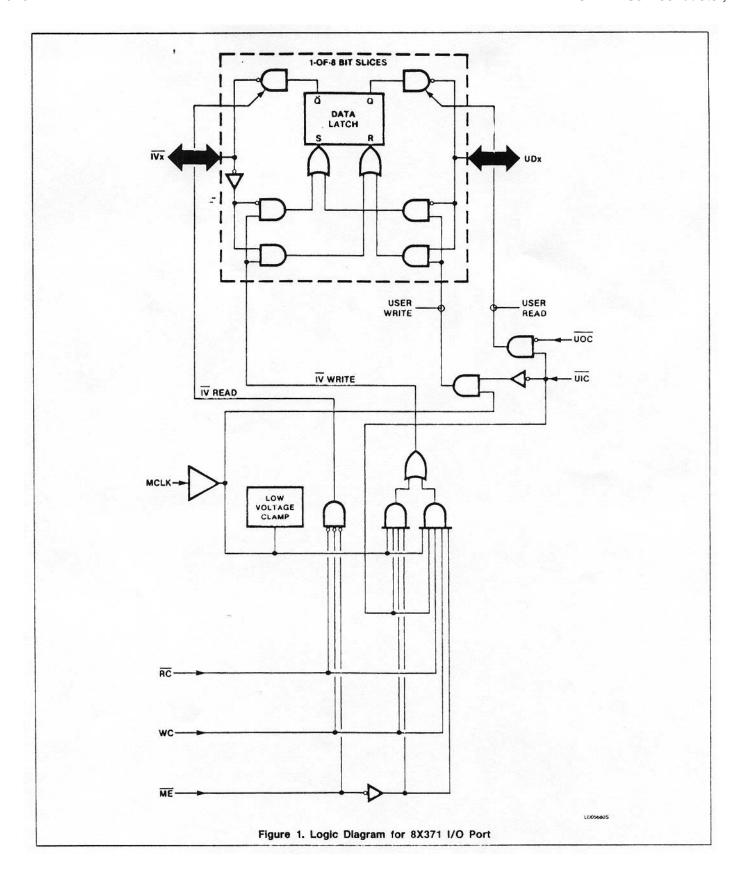

The 8X371 I/O Port is a bidirectional device designed for use as an interface element in systems that use TTL-compatible busses. Typically, the 8X371 is used with the 8X305 Microcontroller and its associated interface Vector (IV) bus; however, it can also be used with the 8X300 Microcontroller or an equivalent microprocessor. The 8X371 is functionally the same and pin-for pin compatible with the older 8T31/8X31 but features improved performance and increased drive current. As shown in the logic diagram of Figure 1, the 8X371 consists of eight identical data latches — bits 0 through 7. The latches are accessed from either of two 8-bit busses — the Microcontroller (IV bus) and the user data (UD bus). Separate controls are provided for each bus and both busses operate independently, except when both attempt to input data at the same time: in such situations, the user bus always has priority. A Master Enable ( $\overline{\text{ME}}$ ) input over the IV bus. The data latches are transparent, in that, while either bus is enabled for input, all input-data transitions are propagated to the other bus, if enabled for output.

### **FEATURES**

- Two bidirectional 8-bit busses

- Independent bus operation (user-bus priority for data entry)

- User data input synchronous with respect to MCLK

- 3-State TTL outputs with high-drive capabilities

- Power-up to predetermined logic state

- Directly compatible with 8X305 (or 8X300) Microcontrollers

- Single +5V supply

- 0.4" 24-pin DIP

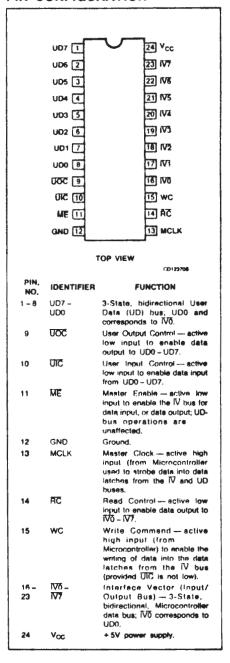

### PIN CONFIGURATION

### **FUNCTIONAL OPERATION**

### **UD Bus Control**

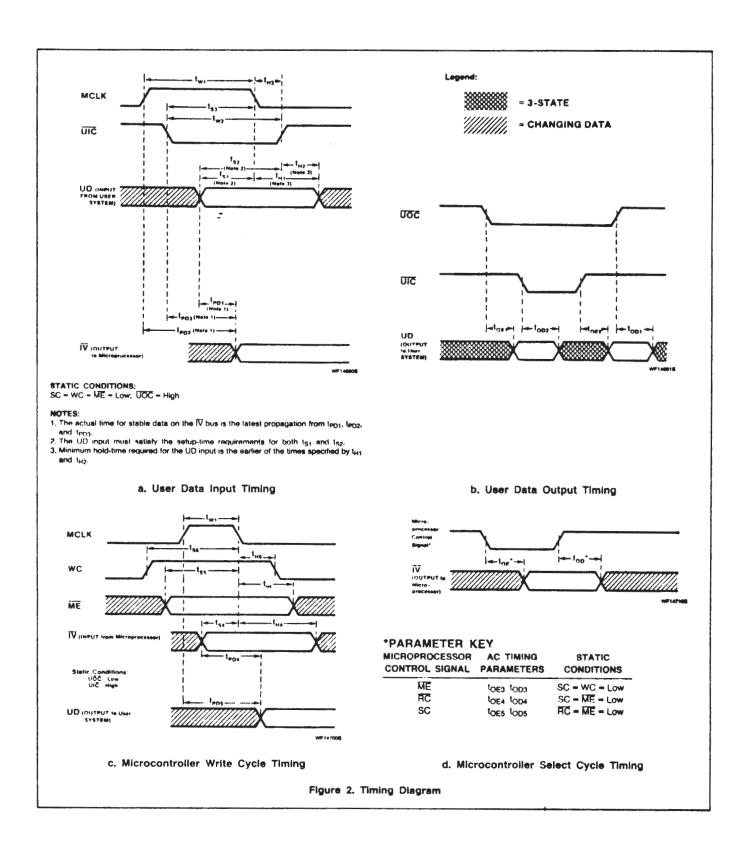

As shown in Table 1, the User Data (UD) bus interface is controlled by the  $\overline{UIC}$  and  $\overline{UOC}$  inputs. Data input to the UD bus is synchronous with MCLK, that is, with  $\overline{UIC}$  low, information is written into the data latches only when MCLK is high. Output drivers on the UD bus are enabled when  $\overline{UOC}$  is low and  $\overline{UIC}$  is high.

Table 1. Input/Output Control of UD Bus

| UIC | UOC | MCLK | FUNCTION<br>OF UD BUS |

|-----|-----|------|-----------------------|

| н   | L   | Х    | Output data           |

| L.  | Х   | н    | Input data            |

| L   | Х   | L    | Inactive              |

| н   | Н   | ×    | Inactive              |

### NOTE:

X = don't care

### **IV** Bus Control

Input/output control of the  $\overline{\text{IV}}$  bus is shown in Table 2; this bus is controlled by  $\overline{\text{RC}}$ , WC,  $\overline{\text{ME}}$ ,

Table 2. Input/Output Control of IV Bus

| ME  | AC | wc | MCLK | UIC | FUNCTION OF IV BUS |

|-----|----|----|------|-----|--------------------|

| L   | L  | L  | X    | х   | Output Data        |

| L   | Х  | н  | н    | Н   | Input Data         |

| L . | н  | L  | Х    | х   | Inactive           |

| L   | Х  | Н  | ×    | L   | Inactive           |

| L   | х  | н  | L    | Н   | Inactive           |

| н   | Х  | х  | Х    | х   | Inactive           |

and MCLK. The  $\overline{\text{IV}}$  bus is enabled for output (Microcontroller read operation) when ME,  $\overline{\text{RC}}$ , and WC are all low. Data is written into the data latches from the  $\overline{\text{IV}}$  bus when  $\overline{\text{ME}}$  is low and both WC and MCLK are high. To avoid data-input conflicts, inputs from the  $\overline{\text{IV}}$  bus are inhibited when  $\overline{\text{UIC}}$  is low; under all other conditions, the  $\overline{\text{IV}}$  and UD busses operate independently. The Microcontroller Left Bank  $\overline{\text{(LB)}}$  and Right Bank  $\overline{\text{(RB)}}$  outputs can control the  $\overline{\text{ME}}$  inputs for two banks of I/O devices, thus acting as a ninth address bit. If more than one I/O Port (including the addressable parts — 8X372, 8X376, 8X382, etc.) are to be connected to the same bank

(LB or RB) of the Microcontroller, selection of each 8X371 must be accomplished with external logic to avoid bus conflicts.

### **Bus Logic Levels**

Data written into the I/O port from either bus will appear inverted when read from the other bus. Data written into either bus will not be inverted when read from the same bus. (Note: A logic "1" in Microcontroller software corresponds to a high-level on the UD bus even though the  $\overline{V}$  bus is inverted.) The 8X371 wakes up in the unselected state with all data bits latched at the "logic 1" level (UD) bus outputs high if enabled).

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                 | RATING      | UNIT            |  |

|------------------|---------------------------|-------------|-----------------|--|

| V <sub>CC</sub>  | Power supply voltage      | +7          | V <sub>DC</sub> |  |

| V <sub>1</sub>   | Input voltage             | +5.5        | V <sub>DC</sub> |  |

| T <sub>STG</sub> | Storage temperature range | -65 to +150 | °C              |  |

# DC ELECTRICAL CHARACTERISTICS (Military) $4.75 \text{V} \le \text{V}_{\text{CC}} \le 5.25 \text{V}, -55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C}$

| SYMBOL          | PARAMETER                              | TEST CONDITIONS                                   |     | LIMITS |      | UNIT |

|-----------------|----------------------------------------|---------------------------------------------------|-----|--------|------|------|

|                 |                                        |                                                   | Min | Тур    | Max  |      |

| V <sub>cc</sub> | Supply voltage                         |                                                   | 4.5 | 5.0    | 5.5  | ٧    |

| V <sub>H</sub>  | High level input voltage               |                                                   | 2.0 |        |      | ٧    |

| ٧,              | Low level input voltage                |                                                   |     |        | 0.8  | V    |

| V <sub>IK</sub> | Input clamp voltage                    | V <sub>cc</sub> = MIN; I <sub>i</sub> = -10mA     |     |        | -1.5 | ٧    |

| I <sub>H</sub>  | High level input current 1             | $V_{cc} = MAX; V_{H} = 2.7V$                      |     |        | 100  | μΑ   |

| 1,              | Low level input current <sup>1</sup>   | V <sub>cc</sub> = MAX; V <sub>L</sub> = 0.5V      |     |        | -550 | μA   |

| Va              | Low level output voltage               | $V_{\infty} = MIN; I_{\infty} = 16mA$             |     |        | 0.55 | V    |

| <b>V</b> 2      | IV bus (IV0=IV7), User bus (UD4 - UD7) | $V_{cc} = MIN; I_{cl} = 24mA$                     |     |        | 0.55 | V    |

| V <sub>OH</sub> | High level output voltage              | $V_{cc} = MIN; I_{cH} = -3.2mA$                   | 2.4 |        |      | V    |

| l <sub>os</sub> | Short circuit output current2          | V <sub>cc</sub> = MAX                             | -20 |        |      | mA   |

|                 | IV bus (IV0=IV7), UD bus (UD4 - UD7)   | V <sub>cc</sub> = MAX                             | -10 |        |      | mA   |

| l <sub>cc</sub> | Supply current                         | V <sub>cc</sub> = MAX; ME = UOC = V <sub>cc</sub> |     |        | 150  | mA   |

### **MILITARY ONLY**

# DC ELECTRICAL CHARACTERISTICS (Commercial) $4.75 \text{V} \le \text{V}_{\text{CC}} \le 5.25 \text{V}, -0^{\text{Q}} \text{C} \le \text{T}_{\text{C}} \le +70^{\text{Q}} \text{C}$

| SYMBOL          | PARAMETER                              | TEST CONDITIONS                                   |      | LIMITS |      | UNIT |

|-----------------|----------------------------------------|---------------------------------------------------|------|--------|------|------|

|                 |                                        |                                                   | Min  | Тур    | Max  |      |

| V <sub>cc</sub> | Supply voltage                         |                                                   | 4.75 | 5.0    | 5.25 | ٧    |

| V <sub>H</sub>  | High level input voltage               |                                                   | 2.0  |        |      | ٧    |

| V,              | Low level input voltage                |                                                   |      |        | 0.8  | ٧    |

| V <sub>iK</sub> | Input clamp voltage                    | $V_{cc} = MIN; I_1 = -10mA$                       |      |        | -1.5 | ٧    |

| I <sub>IH</sub> | High level input current <sup>1</sup>  | $V_{cc} = MAX; V_{H} = 2.7V$                      |      | 5      | 100  | μΑ   |

| l,              | Low level input current 1 -            | V <sub>∞</sub> = MAX; V <sub>L</sub> = 0.5V       |      | -350   | -550 | μA   |

| Va              | Low level output voltage               | V <sub>∞</sub> = MIN; I <sub>∞</sub> = 16mA       |      |        | 0.55 | ٧    |

| ~~              | IV bus (IV0=IV7), User bus (UD4 - UD7) | $V_{cc} = MIN; l_{oL} = 24mA$                     |      |        | 0.55 | V    |

| V <sub>OH</sub> | High level output voltage              | $V_{cc} = MIN; I_{oH} = -3.2mA$                   | 2.4  |        |      | V    |

| los             | Short circuit output current2          | V <sub>cc</sub> = MAX                             | -20  |        |      | mA   |

|                 | IV bus (IV0=IV7), UD bus (UD4 - UD7)   | V <sub>cc</sub> = MAX                             | -10  |        |      | mA   |

| I <sub>cc</sub> | Supply current                         | V <sub>cc</sub> = MAX; ME = UOC = V <sub>cc</sub> |      | 90     | 150  | mA   |

### **COMMERCIAL ONLY**

### NOTES:

- 1. The input current includes the 3-State leakage current of the output driver on the data lines.

- 2. Only one output may be shorted at a time.

AC ELECTRICAL CHARACTERISTICS 4.5V ≤ Vcc ≤ 5.5V, -55°C ≤ Tc ≤ +125°C

| SYMBOL            | PARAMETER                     | REFERI       | ENCES         | TEST CONDITIONS                                     | L     | LIMITS  |            | UNIT |  |

|-------------------|-------------------------------|--------------|---------------|-----------------------------------------------------|-------|---------|------------|------|--|

|                   | From                          |              | То            |                                                     |       | Min Max |            | 1    |  |

| Pulse Widti       | 18:                           |              |               |                                                     |       |         |            |      |  |

| T <sub>W1</sub>   | Clock high                    | TMCLK        | ↓MCLK         |                                                     |       | 30      |            | ns   |  |

| lw2               | User input control            | ↓uic         | ੀਂਗਟ          | MCLK ≃ High                                         |       | 35      |            | ns   |  |

| Propagatio        | n Delays:                     |              |               |                                                     |       |         |            |      |  |

| t <sub>PD1</sub>  | UD propagation delay          | UD           | ΙV            | MCLK = High<br>RC = WC = ME = UCI = Low             |       |         | 45         | ns   |  |

| \$PD2             | UD clock delay                | TMCLK        | ſ∇            | UD = stable;<br>RC = WC = ME - UIC = Low            |       |         | 5 <b>5</b> | ns   |  |

| t <sub>PO3</sub>  | UD input delay                | ↑aic         | ΙV            | UD = Stable; MCLK = High<br>RC = WC = ME = Low      |       |         | 55         | ns   |  |

| t <sub>PO4</sub>  | IV data propagation delay     | ī∇           | αυ            | MCLK = WC = UIC = High;<br>ME = DOC = RC = Low      |       |         | 45         | ns   |  |

| t <sub>PO5</sub>  | Ⅳ data clock delay            | TMCLK        | UD            | WC = UIC = High; IV = Stable<br>ME = UOC = RC = Low | )     |         | 55         | ns   |  |

| Output Ena        | ble Timing:                   |              |               |                                                     |       |         |            |      |  |

| toe1              | UD output enable              | Juoc         | UD            | UIC = High                                          |       |         | 45         | ns   |  |

| IOE2              | UD input recovery             | Tuic         | QU            | UOC = Low                                           |       |         | 45         | ns   |  |

| to∈a              | IV data master enable         | JMF.         | ΙV            | WC = RC = Low                                       |       |         | 45         | ns   |  |

| <sup>t</sup> OE4  | IV data read enable           | ↓RC          | rv            | WC = ME = Low                                       |       |         | 45         | ns   |  |

| t <sub>OE5</sub>  | Ⅳ data write recovery         | Jwc          | IΔ            | RC = ME = Low                                       |       |         | 45         | ns   |  |

| Output Dis        | able Timing:                  |              | ·             |                                                     |       |         |            |      |  |

| <sup>t</sup> 001  | UD output disable             | Tuoc         | UD            | UIC = High                                          |       |         | 40         | ns   |  |

| t002              | UD input override             | ↓uic         | υD            | UOC = Low                                           |       |         | 45         | ns   |  |

| toos <sup>3</sup> | IV data master disable        | ↑ME          | IV            | WC = RC = Low                                       |       |         | 40         | ns   |  |

| 10043             | Ⅳ data read disable           | THC          | ΙV            | WC = ME = Low                                       |       |         | 40         | ns   |  |

| tous <sup>3</sup> | IV data write override        | ↑wc          | ΙV            | ΠC = ME - Low                                       |       |         | 40         | ns   |  |

| Setup Time        | ):                            |              | <del></del>   |                                                     |       |         |            |      |  |

| t <sub>S1</sub>   | UD clock setup time           | υD           | <b>JMCLK</b>  | UIC = Low                                           |       | 15      |            | ns   |  |

| 1 <sub>S2</sub>   | UD setup time                 | UD           | Tuic          | MCLK = High                                         |       | 25      |            | ns   |  |

| tsa               | User input control setup time | Joic         | <b>↓</b> MCLK |                                                     |       | 25      |            | ns   |  |

| t <sub>S4</sub>   | IV data setup time            | IV           | <b>↓</b> MCLK | WC = UTC = High; ME = Lov                           | v     | 15      |            | ns   |  |

| tss <sup>4</sup>  | Ⅳ master enable setup time    | <b>↓ME</b>   | JMLCK         | WC = UIC = High                                     |       | 20      |            | ns   |  |

| 1 <sub>S6</sub>   | IV write control setup time   | ↑wc          | JMCLK         | ME = Low; UIC = High                                |       | 40      |            | ns   |  |

| Hold Time         | <b>6</b> :                    |              |               | ·                                                   |       |         |            |      |  |

| t <sub>H1</sub>   | UD clock hold time            | <b>JMCLK</b> | UD            | UIC = Low                                           |       | 20      |            | ns   |  |

| tH2               | UD control hold time          | Tuic         | UD            | MCLK = High                                         |       | 10      |            | ns   |  |

| 1нз               | User input control hold time  | ↓ MCLK       | Tuic          |                                                     |       | 0       | 1          | ns   |  |

| l <sub>H6</sub>   | IV data hold time             | JMCLK        | IV            | WC = UTC = High; ME = Low (                         | 25°C  | 5       |            | ns   |  |

|                   |                               |              |               |                                                     | Temp. | 20      |            | ns   |  |

| t <sub>H5</sub> 4 | TV master enable hold time    | ↓ MCLK       | TWE           | WE = UIC - High                                     | - '   | 0       | 1          | ns   |  |

| t <sub>H6</sub>   | IV write control hold time    | ↓MCLK        | ↓wc           | ME = Low; UIC = High                                |       | 0       |            | ns   |  |

- 1. The input current includes the 3-State leakage current of the output driver on the data lines.

- 2. Only one output may be shorted at a time.

- These parameters are measured with a capacitive loading of 50pF and represent the output driver turn-off time.

If ME is to be high (inactive), it must be setup before the rising edge and held after the falling edge of MCLK to avoid unintended writing into or selection of the I/O port.

### AC ELECTRICAL CHARACTERISTICS 4.75 < $V_{CC}$ < 5.25V, 0°C < $T_A$ < 70°C

| OVMBOL                       | DADAMETER                      | REFER  | ENCES  | TEST CONDITIONS                                  | LIMITS |     |     | UNIT |

|------------------------------|--------------------------------|--------|--------|--------------------------------------------------|--------|-----|-----|------|

| SYMBOL                       | PARAMETER                      | From   | То     | TEST CONDITIONS                                  | Min    | Тур | Max | ORI  |

| Pulse Wid                    | ths                            |        |        |                                                  |        |     |     |      |

| twi                          | Clock high                     | 1 MCLK | ↓ MCLK |                                                  | 35     |     |     | กร   |

| tw2                          | User input control             | ↓ UIC  | 1 DIC  | MCLK = High                                      | 35     |     |     | ns   |

| Propagatio                   | on Delays                      |        |        |                                                  |        |     |     |      |

| t <sub>PD1</sub>             | UD propagation delay           | αU     | I∇     | MCLK = High<br>RC = WC = ME = UCI = Low          |        |     | 30  | กร   |

| t <sub>PD2</sub>             | UD clock delay                 | † MCLK | ĩ∇     | UD = Stable;<br>RC = WC = ME = UIC = Low         |        |     | 50  | ns   |

| <sup>t</sup> PO3             | UD input delay                 | ↓ ਹਾਟ  | ΙV     | UD = Stable; MCLK = High<br>RC = WC = ME = Low   |        |     | 50  | ns   |

| t <sub>PD4</sub>             | Ⅳ data propagation delay       | I∇     | UD     | MCLK = WC = ÜÎC = High;<br>ME = ÜOC = RC = Low   |        |     | 45  | ns   |

| t <sub>PD5</sub>             | lV data clock delay            | 1 MCLK | UD     | WC = UIC = High; IV = Stable ME = UOC = RC = Low |        |     | 55  | ns   |

| Output En                    | nable Timing                   |        |        |                                                  |        |     |     |      |

| t <sub>OE1</sub>             | UD output enable               | 1 uoc  | QU     | UIC = High                                       |        |     | 30  | ns   |

| I <sub>OE2</sub>             | UD input recovery              | 1 UIC  | UD     | UOC = Low                                        |        |     | 30  | กร   |

| <sup>t</sup> OE3             | IV data master enable          | ↓ ME   | ΙΫ     | WC = RC - Low                                    |        |     | 22  | ns   |

| <sup>t</sup> OE4             | IV data read enable            | ↓ RC   | I∇     | WC = ME = Low                                    |        |     | 25  | ns   |

| t <sub>OE5</sub>             | IV data write recovery         | ↓ wc   | īV     | RC = ME - Low                                    |        |     | 25  | ns   |

| Output Di                    | sable Timing                   |        |        |                                                  |        |     |     | -    |

| t <sub>OD1</sub>             | UD output disable              | 1 UOC  | UD     | UIC = High                                       |        |     | 25  | ns   |

| <sup>t</sup> OD2             | UD input override              | ↓ UIC  | QU     | UOC = Low                                        |        |     | 30  | ns   |

| t <sub>OD3</sub> 1           | i∇ data master disable         | 1 ME   | IV     | WC = RC = Low                                    |        |     | 20  | ns   |

| t <sub>OD4</sub> 1           | V data read disable            | 1 RC   | IV     | WC = ME = Low                                    |        |     | 20  | ns   |

| tops1                        | IV data write override         | 1 wc   | īV     | RC = ME = Low                                    |        |     | 20  | ns   |

| Setup Tim                    | ne .                           |        |        |                                                  |        |     |     |      |

| t <sub>S1</sub>              | UD clock setup time            | UD     | ↓ MCLK | UIC = Low                                        | 15     | 1   |     | ns   |

| ts2                          | UD setup time                  | UD     | 1 UIC  | MCLK = High                                      | 15     |     |     | กร   |

| t <sub>S3</sub>              | User input control setup       | ⊅ טוכ  | ↓ MCLK |                                                  | 25     |     |     | ns   |

| t <sub>S4</sub>              | V data setup time              | I∇     | ↓ MCLK | WC = UIC = High; ME = Low                        | 35     |     |     | ns   |

| tss <sup>2</sup>             | IV master enable setup<br>time | ↓ ME   | ↓ MCLK | WC = ŪĪC = High                                  | 30     |     |     | ns   |

| t <sub>S6</sub>              | IV write control setup time    | † wc   | ↓ MCLK | ME - Low; UIC - High                             | 30     |     |     | ns   |

| Hold Time                    |                                |        |        |                                                  |        | •   |     |      |

| L <sub>H1</sub>              | UD clock hold time             | ↓ MCLK | QU     | UIC = Low                                        | 15     | T   |     | กร   |

| t <sub>H2</sub>              | UD control hold time           | 1 UIC  | UD     | MCLK = High                                      | 15     |     |     | ns   |

| tнз                          | User input control hold time   | ↓ MCLK | TUIC   |                                                  | 0      |     |     | ns   |

| t <sub>H4</sub>              | IV data hold time              | ↓ MCLK | I∇     | WC = UIC = High; ME = Low                        | 5      |     |     | ns   |

| t <sub>H5</sub> <sup>2</sup> | IV master enable hold time     | ↓ MCLK | 1 ME   | WE = UIC = High                                  | 0      | 1   |     | ns   |

| 1.0                          | IV write control hold time     | ↓ MCLK | ↓ wc   | ME = Low; = UIC = High                           | 0      | +   | +   | ns   |

<sup>1.</sup> These parameters are measured with a capacitive loading of 50pf and represent the output driver turn-off time.

2. If ME is to be high (inactive), it must be setup before the rising edge and held after the falling edge of MCLK to avoid unintended writing into or selection of the I/O. port.

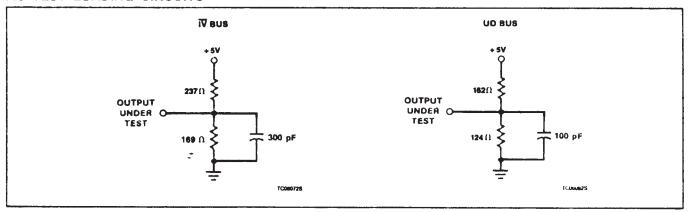

### AC TEST LOADING CIRCUITS

### **APPLICATIONS**

In some applications, performance of a Microcontroller system can be enhanced by using the 8X371 I/O Port instead of an addressable 8X372 port. Using a technique referred to as Extended Microcode or Fast TV Select, the address select cycles which normally precede a read or write operation when using an 8X372 can be eliminated by use of the 8X371.

This technique is often used in bit slice microprocessor designs and involves widening the program memory beyond the normal 16-bit requirement of the Microcontroller, the extra bits are used as enable signals for the 8X371 ports. Thus, the 8X371 is enabled during the instruction cycle in which it is required for input output operations. Since the software overhead of separate address select cycles is eliminated, the overall system performance is improved.

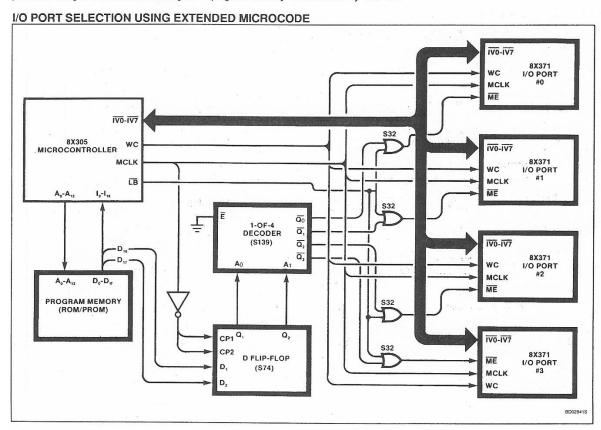

As shown in the accompanying diagram, the program memory is extended by two bit

positions (D $_{16}$  and D $_{17}$ ), permitting any one of four 8X371 ports to be enabled during those instructions. Because of timing considerations, latches must be used to hold the Extended Microcode through the end of the instruction cycle. A decoder is used to obtain four enable signals from the two extra bits. The decoder outputs are ORed with the LB output of the 8X305; thus, all four I/O ports are placed on the Left Bank of the IV bus.

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.