|      | REVISIONS                                         |                 |          |  |  |  |  |

|------|---------------------------------------------------|-----------------|----------|--|--|--|--|

| LTR  | DESCRIPTION                                       | DATE (YR-MO-DA) | APPROVED |  |  |  |  |

| INIT | INITIAL RELEASE                                   | 98-03-18        |          |  |  |  |  |

| Α    | CONVERSION OF WSD (SHORT FORM) TO WSD (FULL FORM) | 98-12-21        |          |  |  |  |  |

# **CAUTION**

THIS ITEM IS SENSITIVE TO ELECTROSTATIC DISCHARGE (ESD).

| WHITE SANDS<br>DRAWING                                                                  |                                                         |                  |                        |                                         |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|------------------------|-----------------------------------------|

| UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN INCHES TOLERANCES ON 2 PLACES 3 PLACES ± ± |                                                         | I .              |                        | ete Device, P-Channel<br>ect Transistor |

|                                                                                         | PREPARED BY DATE (YR-MO-DA) Lawrence S.N. Wang 98-12-21 |                  |                        |                                         |

|                                                                                         | CHECKED BY Roger Sloan 99/01/08 ENGINEER                |                  |                        |                                         |

|                                                                                         | M. Klein / Whin alls/19                                 |                  |                        | Y                                       |

|                                                                                         | DRAWING APPROVACI  John H. O'kuma  John H. O'kuma       | SIZE<br><b>A</b> | CAGE CODE <b>09WF0</b> | W98M9640                                |

|                                                                                         | DESIGN APPROXIMALS 99/01/19                             | SHEET            | 1 OF                   | 13                                      |

#### 1. SCOPE

- 1.1 Scope. This drawing describes a commercially available microcircuit with radiation tolerance.

- 1.1.1 \*\*RTA\*\* this drawing contains a radiation tolerance assured item and/or processes. All changes to items or processes and all proposed substitutions of items identified as RTA on the drawing, must be evaluated and approved by the Radiation Tolerance Assured Supply And Support Center (RTASSC), Directorate For Applied Technology, Test And Simulation (DATTS), White Sands Missile Range, (WSMR).

- 1.1.2 Only the item described on this drawing when procured from the vendor(s) listed hereon is approved for use in the application(s) specified hereon. A substitute item shall not be used without prior approval by the RTASSC.

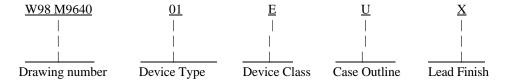

- 1.2 Part or Identification Number (PIN). The complete part number shall be as shown in the following example.

1.3 <u>Drawing Number</u>. The drawing number consists of three pieces of information as follows:

W98 = Indicates White Sands drawing, year 1998. M = Radiation Tolerance Designator (3000 rads(Si)).

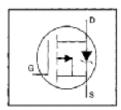

9640 = Semiconductor discrete device, P-channel power MOS field effect transistor

1.4 <u>Device Type</u>. The device type shall identify the circuit function as follows:

| Device Type | Generic # | Circuit Function       | Switchin on/off time(typ.); |

|-------------|-----------|------------------------|-----------------------------|

|             |           |                        | Frequency(Test Condition)   |

| 01          | 9640      | P-channel power MOSFET | 57 ns / 77 ns; 1.0 MHz      |

1.5 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

E Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix

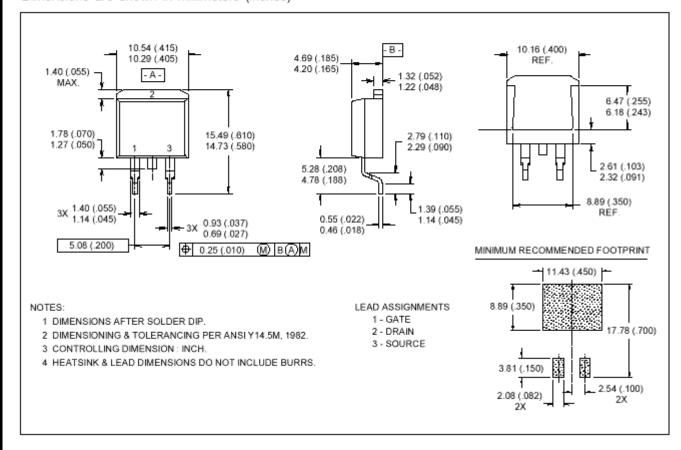

1.6 Case Outline. The case outline is as designated in MIL-STD-1835 as follows:

| Outline letter | <u>Terminals</u> | Package Style           |

|----------------|------------------|-------------------------|

| U              | 4                | TO-263AB, see Figure 1, |

|                |                  | Surface Mount           |

- 1.7 <u>Lead Finish</u>. The lead finish is as specified in the purchase order (X indicates acceptable lead finishes per manufacturers specification).

- 1.8 Operating Temperature. The operating temperature range of this device is -55°C to +150°C.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE              | CAGE CODE           | W98M9640 |

|--------------------------------------------|-------------------|---------------------|----------|

| Monolithic Silicon                         | <b>A</b>          | 09WF0               |          |

|                                            | DATE:<br>98-09-23 | REVISION LEVEL<br>A | SHEET 2  |

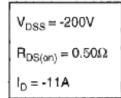

- 2.0 Salient characteristics.

- 2.1 <u>Maximum operating conditions</u>. The maximum operating conditions shall be as specified in Table I.

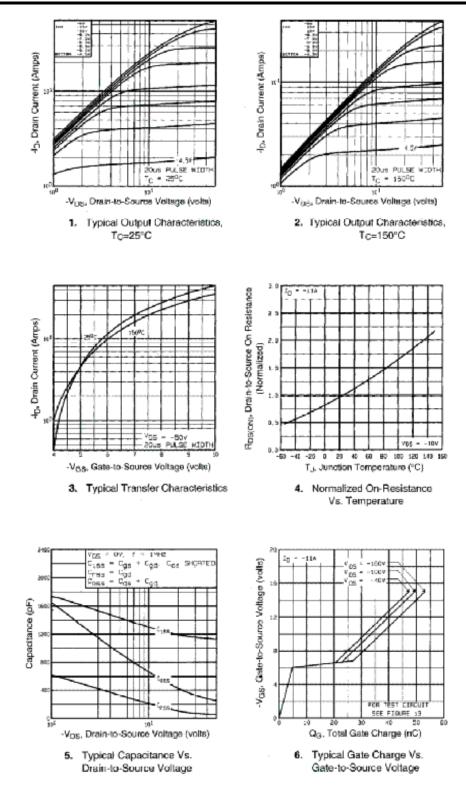

- 2..2 <u>Electrical performance characteristics</u>:

- 2.2.1 The electrical performance characteristics shall be as specified in Table II.

- 2.2.2 The Typical characteristics diagrams shall be as specified in diagrams in Figure 2.

- 2.2.3 Radiation Tolerance Assurance(RTA) data for electrical performance characteristics shall be as specified in Table III.

- 2.3 <u>Design and construction</u>. Microcircuits supplied to this WSD shall be as specified herein and on Figure 1.

- 2.4 Marking. Microcircuits supplied to this WSD shall be marked with the manufacturer's standard commercial PIN.

- 3.0 Regulatory requirements. This section is not utilized in this WSD.

TABLE I. Maximum operating conditions.

| -11 A                   |

|-------------------------|

| -6.8 A                  |

| -44 A                   |

| 125 W                   |

| 3.0 W                   |

| 1.0 W/°C                |

| 0.025 W/°C              |

| ±20 V                   |

| 700 mJ                  |

| -11 A                   |

| 13 mJ                   |

| 5.0 V/ns                |

| -55°C to +150°C         |

| -55°C to +150°C         |

| 300°C (1.6mm from case) |

|                         |

For notes  $\underline{1}$ /,  $\underline{3}$ / and  $\underline{2}$ /, see footnotes of TABLE II.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | 09WF0          |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 3        |

TABLE II. Electrical Performance Characteristics.

| Test                                      | Symbol                                                                | Conditions $T_J = +25^{\circ}C$                                       | Group A   |      | Limits |      | Units |

|-------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------|------|--------|------|-------|

|                                           |                                                                       | unless otherwise specified                                            | subgroups | Min  | Тур    | Max  |       |

| Drain-to-source<br>breakdown voltage      | V <sub>(BR)DSS</sub>                                                  | $V_{GS} = 0 \text{ V}, I_D = 250  \mu\text{A}$                        | Room      | -200 |        |      | V     |

| Breakdown voltage temperature coefficient | $\begin{array}{c} \Delta V_{(BR)DS} \\ _{S}/\Delta T_{J} \end{array}$ | $I_D = -1 \text{ mA}$                                                 |           |      | -0.20  |      | V/°C  |

| Static drain-to-source on resistance      | R <sub>(DS)ON</sub>                                                   | $V_{GS} = -10 \text{ V}, I_D = 6.6 \text{ A}$<br>$\underline{4}/$     |           |      |        | 0.50 | Ω     |

| Gate threshold voltage                    | $V_{\text{GS(th)}}$                                                   | $V_{DS}=V_{GS},I_D=250\;\mu A$                                        | ]         | -2.0 |        | -4.0 | V     |

| Forward transconductance                  | $g_{\mathrm{fs}}$                                                     | $V_{DS} = -50 \text{ V}, I_D = 6.6 \text{ A}$<br>$\underline{4}/$     |           | 4.1  |        |      | S     |

| Drain-to-source leakage                   | $I_{DSS}$                                                             | $V_{DS} = -200 \text{ V}, V_{GS} = 0 \text{ V}$                       |           |      |        | -100 | μА    |

| current                                   |                                                                       | $V_{DS} = -160 \text{ V}, V_{GS} = 0 \text{ V}$                       | Max.      |      |        | -500 |       |

| Gate-to-source forward leakage current    | $I_{GSS}$                                                             | $V_{GS} = -20 \text{ V}$                                              | Room      |      |        | -100 | nA    |

| Gate-to-source reverse leakage current    |                                                                       | $V_{GS} = 20 \text{ V}$                                               |           |      |        | 100  |       |

| Total gate charge                         | $Q_{g}$                                                               | $I_D = -11 \text{ A}$                                                 |           |      |        | 44   | nC    |

| Gate-to-source charge                     | $Q_{gs}$                                                              | $V_{DS} = -160 \text{ V}$                                             |           |      |        | 7.1  | ]     |

| Gate-to-drain (Miller) charge             | $Q_{\mathrm{gd}}$                                                     | $V_{GS} = -10 \text{ V}$ (see Figures 3.6 and 3.13) $\underline{4}$ / |           |      |        | 27   |       |

| Turn-on delay time                        | $t_{d(ON)}$                                                           | $V_{DD} = -100 \text{ V}$                                             |           |      | 14     |      | ns    |

| Rise time                                 | t <sub>r</sub>                                                        | $I_D = -11 A$                                                         |           |      | 43     |      |       |

| Turn-off delay time                       | $t_{d(off)}$                                                          | $R_G = 9.1 \Omega$                                                    |           |      | 39     |      |       |

| Fall time                                 | $t_{\rm f}$                                                           | $R_G = 8.6 \Omega$ (see Figure 2.10) $\underline{4}$                  |           |      | 38     |      |       |

| Internal drain inductance                 | $L_D$                                                                 | Between lead, 6 mm (0.25in) from                                      |           |      | 4.5    |      | nН    |

| Internal source inductance                | $L_{S}$                                                               | package and center of die contact <u>5A</u> /                         |           |      | 7.5    |      |       |

| Input capacitance                         | $C_{ISS}$                                                             | $V_{GS} = 0 V$                                                        |           |      | 1200   |      | pF    |

| Output capacitance                        | Coss                                                                  | $V_{DS} = -25 \text{ V}$                                              |           |      | 370    |      |       |

| Reverse transfer capacitance              | $C_{rSS}$                                                             | f = 1.0 MHz (see Figure 2.5)                                          |           |      | 81     |      |       |

See footnotes at end of table.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 4        |

TABLE II. Electrical performance characteristics- Continued.

| Test                                      | Symbol            | Conditions $T_J = +25$ °C                                                         | Group A   |           | Limits     |          | Units |

|-------------------------------------------|-------------------|-----------------------------------------------------------------------------------|-----------|-----------|------------|----------|-------|

|                                           |                   | unless otherwise specified                                                        | subgroups | Min       | Тур        | Max      |       |

| Source-Drain Ratings :                    |                   |                                                                                   |           |           |            |          | _     |

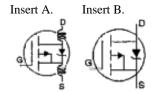

| Continuous source<br>current (body diode) | $I_{\mathrm{S}}$  | MOSFET symbol showing the integral reverse p-n junction diode 5B/                 | Room      |           |            | -11      | A     |

| Pulsed source current (body diode)        | $I_{SM}$          |                                                                                   |           |           |            | -44      |       |

| Diode forward voltage                     | $V_{\mathrm{SD}}$ | $I_{S} = -11 \text{ A}, V_{GS} = 0 \text{ V}$                                     |           |           |            | -5.0     | V     |

| Reverse recovery time                     | t <sub>rr</sub>   | $I_F = -11 \text{ A}, \text{ di/dt} = 100 \text{ A/}\mu\text{s}$ $\underline{4}/$ |           |           | 250        | 300      | ns    |

| Reverse recovery charge                   | Q <sub>rr</sub>   |                                                                                   |           |           | 2.9        | 3.6      | μС    |

| Forward turn-on time                      | t <sub>on</sub>   | turn-on is dominated by $L_S + L_D$                                               |           | intrinsic | turn-on is | neglible |       |

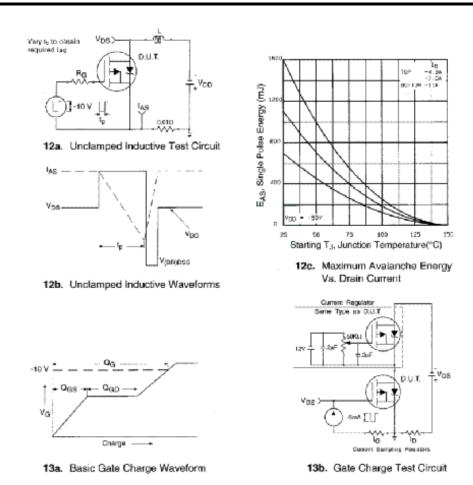

- $\begin{subarray}{ll} $\underline{1}/$ & Repetitive rating; pulse width limited by max. Junction temperature (see Figure 2.11) $\underline{2}/$ & VDD = -50 V, starting TJ = +25°C, L = 8.7 mH, RG = 25 $\Omega$, IAS = -11 A (see Figure 2.12). $\overline{3}/$ & I_{SD} \leq -11 A, di/dt \leq 150 A/\mus, V_{DD} \leq V_{(BR)DSS}, T_J \leq +150°C. $\overline{4}/$ & Pulse width \leq 300 $\mus;$ duty cycle \leq 2%.$

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | 09WF0          |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | <b>5</b> |

Terminal connections

## **HEXFET TO-263AB Outline**

Dimensions are shown in millimeters (inches)

Package Outline

Figure 1. Design and construction.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | 09WF0          |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 6        |

#### **HEXFET TO-263AB** Dimensions are shown in millimeters (inches) TRR 0000 1.60 (.063) 1.50 (.059) ტ<sup>1.60 (.063)</sup> 4.10 (.161) 3.90 (.153) 1.50 (.059) 0.368 (.0145) 0.342 (.0135) <del>+ + +</del> **+ + #** FEED DIRECTION 11.60 (.457) 1.85 (.073) 11.40 (.449) 24.30 (.957) 23.90 (.941) 1.65 (.065) 15.42 (.609) Φ 15.22 (.601) TRL 0000 Ø 1.75 (.069) 1.25 (.049) 10.90 (.429) 4.72 (.136) 10.70 (.421) 4.52 (.178) 16.10 (.634) 15.90 (.626) FEED DIRECTION 13.50 (.532) Ø 12.80 (.504) 27.40 (1.079) 23.90 (.941) 4 0 330.00 Ø 60.00 (2.362) (14.173)MIN. MAX. 30.40 (1.197) NOTES MAX. COMFORMS TO EIA-418. 26.40 (1.039) (4)CONTROLLING DIMENSION: MILLIMETER 24.40 (.961) DIMENSION MEASURED @ HUB. INCLUDES FLANGE DISTORTION @ OUTER EDGE.

Tape & Reel Information

3

Figure 1. Design and construction- Continued.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE              | CAGE CODE           | W98M9640       |

|--------------------------------------------|-------------------|---------------------|----------------|

| Monolithic Silicon                         | <b>A</b>          | 09WF0               |                |

|                                            | DATE:<br>98-09-23 | REVISION LEVEL<br>A | SHEET <b>7</b> |

Figure 2. Typical characteristics diagrams.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 8        |

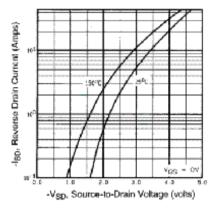

Typical Source-Drain Diode Forward Voltage

8. Maximum Safe Operating Area

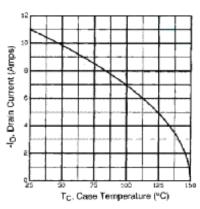

Maximum Drain Current Vs. Case Temperature

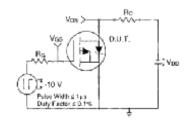

Fig 10a. Switching Time Test Circuit

10b. Switching Time Waveforms

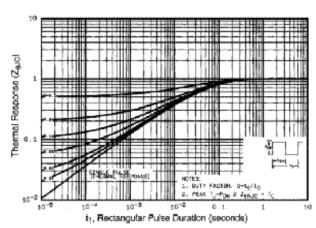

11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Figure 2. Typical characteristics diagrams - Continued.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 9        |

Figure 2. <u>Typical characteristics diagrams</u> - Continued.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 10       |

- 4.0 Quality assurance provisions.

- 4.1 <u>Responsibility for inspection</u>. Unless otherwise specified in the contract or purchase order, the contractor is responsible for the performance of all inspection, examination, and test requirements specified herein. Except as otherwise specified in the contract or purchase order, the contractor may use his own or any other facilities suitable for the inspection requirements specified herein, unless disapproved by the Government. The Government reserves the right to perform any of the inspections, examinations, or tests set forth in this description where such inspections, examinations, and tests are deemed necessary to assure supplies and services conform to prescribed requirements.

- 4.2 <u>Contractor certification statement</u>. The contractor shall certify and maintain objective quality evidence that the product offered meets the requirements of this WSD, and that the product conforms to the producer's own drawings, specifications, standards, quality assurances practices, and is the same as the product provided as a bid sample. The acquiring activity reserves the right to require proof of such conformance prior to the first delivery and thereafter as may be otherwise provided for under the provisions of the contract.

- 4.3 <u>Certificate of conformance</u>. A certificate of conformance shall accompany all microcircuits supplied to this WSD.

- 5.1 <u>Preservation, packaging, packing, labeling, and marking</u>. Preservation, packaging, labeling, and marking shall be as specified in the contract or purchase order.

- 6.0 <u>Notes</u>. This section contains relevant information which is useful to buyers, users, and suppliers in the process of acquiring the item, but is not mandatory.

- 6.1 <u>Radiation Tolerance Assured (RTA)</u>. RTA performance is not covered under the manufacturers warranty. RTA testing has been performed and is an integral part of this drawing. The RTA performance is certified by White Sands Missile Range, Directorate for Applied Technology, Test and Simulation (WSMR, DATTS) to the performance characteristics as specified in TABLE III herein.

- 6.2 <u>Electrical Performance over Temperature</u>. Electrical performance over temperature (  $-55^{\circ}C \le T_{A} \le +150^{\circ}C$ ) is covered under the manufacturers warranty. No further temperature testing is required for determining temperature related effects. There is no certification or warrantees by WSMR,DATTS to the performance characteristics specified in TABLE II herein.

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640 |

|--------------------------------------------|----------|----------------|----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |          |

|                                            | DATE:    | REVISION LEVEL | SHEET    |

|                                            | 98-09-23 | A              | 11       |

## TABLE III. RTA Electrical Performance Characteristics.

|                                        | Symbol               | Conditions $\underline{2}/$ $T_J = +25^{\circ}C$ | Limits |      | Units |

|----------------------------------------|----------------------|--------------------------------------------------|--------|------|-------|

|                                        |                      | unless otherwise specified                       | Min    | Max  |       |

| Drain-to-source breakdown voltage      | V <sub>(BR)DSS</sub> | $V_{GS} = 0 \text{ V}, I_D = 250 \ \mu\text{A}$  | -200   |      | V     |

| Static drain-to-source on resistance   | R <sub>(DS)ON</sub>  | $V_{GS} = -10 \text{ V}, I_D = 6.6 \text{ A}$    |        | 0.6  | Ω     |

| Gate threshold voltage                 | $V_{\text{GS(th)}}$  | $V_{DS}=V_{GS},I_D=250\;\mu A$                   | -2.0   | -4.4 | V     |

| Forward transconductance               | $g_{\mathrm{fs}}$    | $V_{DS} = -9 \text{ V}, I_{D} = 6.6 \text{ A}$   | 3.9    |      | S     |

| Drain-to-source leakage current        | $I_{DSS}$            | $V_{DS} = -200 \text{ V}, V_{GS} = 0 \text{ V}$  |        | -133 | μΑ    |

| Gate-to-source forward leakage current | $I_{GSS}$            | $V_{GS} = -20 \text{ V}$                         |        | -110 | nA    |

| Gate-to-source reverse leakage current |                      | $V_{GS} = 20 \text{ V}$                          |        | 110  |       |

| Diode forward voltage                  | $V_{SD}$             | $I_S = -11 \text{ A}, V_{GS} = 0 \text{ V}$      |        | -5.2 | V     |

| 1/ Devices supplied to this drawing will meet and only be tested at the level M of irradiation. | When performing post irradiation |

|-------------------------------------------------------------------------------------------------|----------------------------------|

| electrical measurements for any radiation level, $T_A = +25$ °C.                                |                                  |

|                                                                                                 |                                  |

| Microcircuit, Linear, Dual MOSFET Drivers, | SIZE     | CAGE CODE      | W98M9640  |

|--------------------------------------------|----------|----------------|-----------|

| Monolithic Silicon                         | <b>A</b> | <b>09WF0</b>   |           |

|                                            | DATE:    | REVISION LEVEL | SHEET     |

|                                            | 98-09-23 | A              | <b>12</b> |

| 6.3 Ordering data. The contract or purchase order shall specify the following:                                         |                                         |                          |                                                                              |                                     |  |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|------------------------------------------------------------------------------|-------------------------------------|--|

| <ul><li>a. WSD document number and</li><li>b. Quality assurance provision</li><li>c. Packaging requirements.</li></ul> |                                         | SD PIN.                  |                                                                              |                                     |  |

| 6.4 <u>Identification of the approved source of supply for the item desc</u>                                           | source(s) of suppl<br>ribed on the draw | y hereon is not to bing. | e construed as a guarantee of pre                                            | sent or continued availability as a |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

| PART ID NUMBER<br>W98M964001EUX                                                                                        | CAGE CODE<br>09WF0                      |                          | MANUFACTURER International Rectifier                                         | ITEM IDENTIFICATION IRF9640S        |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

| 09WF0                                                                                                                  |                                         |                          | Commander, USAWSMR ATTN: STEWS-DT-A Building 90121 White Sands NM 88002-5158 |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |

|                                                                                                                        | ,                                       |                          |                                                                              |                                     |  |

| Semiconductor Discrete D<br>Channel Power MOS Fiel                                                                     |                                         | SIZE<br><b>A</b>         | CAGE CODE<br>09WF0                                                           | W98M9640                            |  |

| Transistor                                                                                                             |                                         | DATE: 98-09-25           | REVISION LEVEL<br>A                                                          | SHEET 13                            |  |

|                                                                                                                        |                                         |                          |                                                                              |                                     |  |