# NEC

# AGC/UP-CONVERTER WITH IQ MODULATOR

**UPC8158K**

#### **FEATURES**

- SUPPLY VOLTAGE: Vcc = 2.7 to 4.0 V, lcc = 28 mA @ Vcc = 3.0 V

- BUILT-IN LPF: Suppresses spurious multipled by TX local (LO1)

- AGC AMPLIFIER INSTALLED IN LOCAL PORT OF UPCONVERTER:

- GCR = 35 dB MIN. @ fout = 1.5 GHz

- EXCELLENT PERFORMANCE: Padj = -65dBc TYP. @  $\Delta f = \pm 50$  KHz, EVM = 1.2 %rms TYP.

- EXTERNAL IF FILTER: Can be applied between modulator output and up converter input terminal

#### APLICATIONS

- Digital cellular phones (PDC800M, PDC1.5G, TDMA1900 and so on)

- Wireless Communiaction Systems (MMDS, Broadband wireless access)

#### DESCRIPTION

The UPC8158K is a silicon microwave monolithic integrated circuit designed as a quadrature modulator for digital mobile communication systems. This MMIC consist of a 0.8 GHz to 1.5 GHz up-converter and 100 MHz to 300 MHz quadrature modulator which are equipped with AGC and power save functions. This configuration suits IF modulation systems and is packaged in a 28-pin QFN suitable for high density mounting. The chip is manufactured using NEC's 20 GHz fr silicon bipolar process NESAT<sup>™</sup>III to realize low power consumption. Consequently the UPC8158K can contribute to make RF blocks smaller size, higher performance and lower power consumption.

#### **ELECTRICAL CHARACTERISTICS** (TA = 25°C, VCc1 = VCc2 = VCc3 = 3.0 V, VPS/VAGC = 2.5 V)

|               | PART NUMBER<br>PACKAGE OUTLINE                                                   | UPC8158K |       |        |       |  |  |

|---------------|----------------------------------------------------------------------------------|----------|-------|--------|-------|--|--|

| SYMBOLS       | PARAMETERS AND CONDITIONS                                                        | MIN      | TYP   | MAX    |       |  |  |

|               | UP-CONVERTER + QUADRATURE MODULATOR TOTAL                                        |          |       |        |       |  |  |

| ICC (TOTAL)   | Total Circuit Current, No input signal                                           | mA       | 23.7  | 28     | 37.6  |  |  |

| ICC(PS) TOTAL | Total Circuit Current at Power Save Mode, VPs $\leq$ 0.5 V(low), No input signal | μΑ       |       | 0.3    | 10    |  |  |

| PRFout1       | Total Output Power 1, VAGC = 2.5 V                                               | dBm      | -15   | -11.5  | -8    |  |  |

| PRFout2       | Total Output Power 2, VAGC = 1.0 V                                               | dBm      | -56.5 | -52    | -46.5 |  |  |

| LOL           | LO Carrier Leak, fLOL = fLO1 + fLO2                                              | dBc      |       | -40    | -30   |  |  |

| ImR           | Image Rejection (Side Band Leak)                                                 | dBc      |       | -40    | -30   |  |  |

| IM3(I/Q)      | I/Q 3rd Order Distortion                                                         | dBc      |       | -50    | -30   |  |  |

| GCR           | AGC Gain Control Range, VAGC = 2 V →1 V                                          | dB       | 35    | 40     |       |  |  |

| EVM           | Error Vector Magnitude, MOD Pattern PN9                                          | %rms     |       | 1.2    | 3.0   |  |  |

| Padj          | Adjacent Channel Interference, $\Delta f = \pm 50 \text{KHz}$ , MOD Pattern: PN9 | dBc      |       | -65    | -60   |  |  |

| Pout(8fLO1)   | Spurious Suppression, fLO1 $\times$ 8, fLO1 $\times$ 8 (image) <sup>Note</sup>   | dBc      |       | -70    | -65   |  |  |

| TPS(Rise)     | Power Save Rise Time, VPs(Low) $\rightarrow$ VPs(High)                           | μs       |       | 2      | 5     |  |  |

| TPS(Fall)     | Power Save Fall Time, VPs(High) $\rightarrow$ VPs(Low)                           | μs       |       | 2      | 5     |  |  |

| Zı/Q          | I/Q Input Impedance, Between pin I/lb, Q/Qb                                      | kΩ       | 80    | 200    |       |  |  |

| lı/q          | I/Q Input Bias Current, Between pin I/lb, Q/Qb                                   | μA       |       | 5      | 13    |  |  |

| ZLO1          | LO1 Input VSWR, fLo1 = 100 M to 300 MHz                                          | -        |       | 1.5 :1 |       |  |  |

Note:

1. Without external LC between Fil1 and Fil2 pin on this frequency conditions. Spectrum analyzer conditions: VBW = 300 Hz, RBW = 300 Hz.

#### **UPC8158K**

### **ABSOLUTE MAXIMUM RATINGS1** (TA = 25°C)

| SYMBOLS  | PARAMETERS                     | UNITS | RATINGS     |

|----------|--------------------------------|-------|-------------|

| Vcc      | Supply Voltage                 | V     | 5.0         |

| Vps/Vagc | Power Save & AGC Control       | V     | 5.0         |

| PD       | Power Dissipation <sup>2</sup> | mW    | 430         |

| TA       | Operating Ambient Temp.        | °C    | -40 to +85  |

| Tstg     | Storage Temperature            | °C    | -55 to +150 |

Note:

Operation in excess of any one of these conditions may result in permanent damage.

TA = +85° C

#### RECOMMENDED **OPERATING CONDITIONS**

| PART NUMBER UPC81        |                         |       |     |     |      |  |

|--------------------------|-------------------------|-------|-----|-----|------|--|

| SYMBOLS PARAMETERS UNITS |                         |       |     | TYP | MAX  |  |

| Vcc                      | Supply Voltage          | V     | 2.7 | 3.0 | 4.0  |  |

| Vps                      | Power Save Voltage      | V     | 0   |     | 0.3  |  |

| VAGCPS                   | AGC Control Voltage     | V     | 1.0 |     | 2.5  |  |

| TA                       | Operating Ambient Temp. | °C    | -30 | +25 | +80  |  |

| fRFout                   | Upconv. RF Output Freq. | MHz   | 800 |     | 1500 |  |

| fLO2in                   | LO2 Input Frequency     | MHz   | 600 |     | 1750 |  |

| fl/Qin                   | I/Q Input Frequency     | MHz   | DC  |     | 10   |  |

| PLO1in                   | LO1 Input Level         | dBm   | -18 | -15 | -12  |  |

| PLO2in                   | LO2 Input Level         | dBm   | -18 | -15 | -12  |  |

| VI/Qin                   | I/Q Input Amplitude     | mVp-p |     | 420 | 500  |  |

| fUPCONin                 | Upconverter Input Freq. |       |     |     |      |  |

| fMODout                  | Modulator Output Freq.  | MHz   | 100 |     | 300  |  |

| fLO1in                   | LO1 Input Frequency     |       |     |     |      |  |

#### **PIN EXPLANATIONS**

| PIN<br>NO. | SYMBOL | SUPPLY<br>VOLTAGE (V) | PIN<br>VOLTAGE (V) | FUNCTION AND APPLICATION                                                                                                                                                                                                                                                        | EQUIVALENT CIRCUIT                      |

|------------|--------|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1          | lin    | Vcc/2                 | _                  | Input for I signal. This input impedance<br>is 200 k $\Omega$ . In the case of that I/Q input<br>signals are single ended, amplitude of<br>the signal 500 m VP-P max.                                                                                                           | ╷╶┼┕┯╱╫╲┯╱┤╴╷                           |

| 2          | linb   | Vcc/2                 | -                  | Input for I signal. This input impedance<br>is 200 k $\Omega$ . In the case of that I/Q input<br>signals are single ended,Vcc/2 biased<br>DC signal should be input. In the case of<br>the I/Q input signals are differential,<br>amplitude of the signal is 500 m VP-P<br>max. |                                         |

| 3          | N.C.   | -                     | _                  | This pin is not connected to internal circuit. This pin should be opened or grounded.                                                                                                                                                                                           |                                         |

| 4          | Qinb   | Vcc/2                 | _                  | Input for Q signal. This input impedance<br>is 200 K $\Omega$ . In the case of that I/Q input<br>signals are single ended, amplitude of<br>the signal is 500 m VP-P max.                                                                                                        | ╷╶┥┷ <sub>┱</sub> ╱╫┥ <sub>┱</sub> ╱╢╶╷ |

| 5          | Qin    | Vcc/2                 | _                  | Input for I signal. This input impedance<br>is 200 k $\Omega$ . In the case of that I/Q input<br>signals are single ended,Vcc/2 biased<br>DC signal should be input. In the case of<br>the I/Q input signals are differential,<br>amplitude of the signal is 500 m VP-P<br>max. |                                         |

| 6          | N.C.   | -                     | _                  | These pins is not connected to internal                                                                                                                                                                                                                                         |                                         |

| 7          | N.C.   | -                     | -                  | circuit. These pins should be opened or<br>grounded.                                                                                                                                                                                                                            |                                         |

| 8          | N.C.   | -                     | _                  |                                                                                                                                                                                                                                                                                 |                                         |

| 9          | LO1inb | _                     | 2.98               | Bypass pin of modulator's local input.<br>This pin should be decoupled with 330<br>pF capacitor.                                                                                                                                                                                |                                         |

| 10         | LO1in  | _                     | 2.98               | Local signal for modulator. This pin must be coupled with DC cut capacitor 330 pF and should be terminated with 51 $\Omega$ resistor                                                                                                                                            |                                         |

| 11         | Vcc    | 2.7 to 4.0            | -                  | Supply Voltage pin modulator, up-<br>converter and AGC circuits.                                                                                                                                                                                                                |                                         |

#### UPC8158K

## PIN EXPLANATIONS (CONT.)

| PIN<br>NO. | SYMBOL   | SUPPLY<br>VOLTAGE (V) | PIN<br>VOLTAGE (V) | FUNCTION AND APPLICATION                                                                                                                                                                                                                                                                 | EQUIVALENT CIRCUIT  |

|------------|----------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 12         | GND      | 0                     | -                  | Ground pin for modulator, up-converter<br>and AGC circuits. This pin should be<br>grounded with minimum inductance.<br>Form the ground pattern as widely as<br>possible to minimize ground impedance.                                                                                    |                     |

| 13         | LO2in    | _                     | 1.8                | Local signal input for modulator. This pin must be coupled with DC cut capacitor 33 pF and should be terminated with 51 $\Omega$ resistor.                                                                                                                                               |                     |

| 14         | LO2inb   | -                     | 1.8                | Bypass pin of up-converter's local signal<br>input. This pin should be decoupled with<br>33 pF capacitor.                                                                                                                                                                                |                     |

| 15         | N.C.     | -                     | _                  | This pin is not connected to internal circuit. This pin should be opened or grounded.                                                                                                                                                                                                    |                     |

| 16         | GND      | 0                     | _                  | Ground pin for modulator, up-converter<br>and AGC circuits. This pin should be<br>grounded with minimum inductance.                                                                                                                                                                      |                     |

| 17         | Vps/Vagc | Vps/Vagc              | _                  | Power save control pin for modulator,<br>upconverter and AGC circuits. This pin<br>also assigned as gain control pin<br>forAGC circuits. Operation status with<br>applied voltages are as follows.     VPs/VAGC (V)   STATE     0 to 0.4   OFF (Sleep Mode)     1 to 2.5   On (AGC Mode) | REG<br>TTT AGC Cont |

| 18         | N.C.     | -                     | _                  | These pins is not connected to internal circuit. These pins should be opened or grounded.                                                                                                                                                                                                |                     |

| 19         | GND      | 0                     | _                  | Ground pin for modulator, up-converter<br>and AGC circuits. This pin should be<br>grounded with minimum inductance.                                                                                                                                                                      |                     |

| 20         | Vcc      | 2.7 to 4.0            | -                  | Supply Voltage pin for modulator, up-<br>converter and AGC circuits.                                                                                                                                                                                                                     |                     |

| 21         | GND      | 0                     | _                  | Ground pin for RF output buffer. This pin should be grounded with minimum inductance.                                                                                                                                                                                                    |                     |

| 22         | N.C.     | -                     | _                  | This pin is not connected to internal<br>circuit. This pin should be opened or<br>grounded.                                                                                                                                                                                              |                     |

| 23         | RFout    | _                     | 1.75               | RF output pin. This pin is emitter follower which is low impedance output port. This pin can be easily matched to 50 $\Omega$ impedance using external coupling and decoupling capacitors.                                                                                               | 23 External         |

| 24         | N.C.     | _                     | _                  | These pins are not connected to internal circuit. These pins should be opened or grounded.                                                                                                                                                                                               |                     |

| 25         | Vcc      | 2.7 to 4.0            | _                  | Supply Voltage pin for RF output buffer.                                                                                                                                                                                                                                                 |                     |

#### PIN EXPLANATIONS (CONT.)

| PIN<br>NO. | SYMBOL | SUPPLY<br>VOLTAGE (V) | PIN<br>VOLTAGE (V) | FUNCTION AND APPLICATION                                                                                                                                                                                 | EQUIVALENT CIRCUIT |

|------------|--------|-----------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 26         | FIL1   | _                     | 2.76               | External inductor and capacitor can<br>supress harmonics spurious of LO1<br>frequency.<br>LC value should be determined                                                                                  | External 27        |

| 27         | FIL2   | _                     | 2.76               | according to LO1 input frequency and suppression level.                                                                                                                                                  |                    |

| 28         | GND    | 0                     | _                  | Ground pin for modulator, up-converter<br>and AGC circuits. This pin should be<br>grounded with minimum inductance.<br>Form the ground pattern as widely as<br>possible to minimize ground<br>impedance. |                    |

#### Note:

1. Pin Votages are measured on Vcc = 3.0 V.

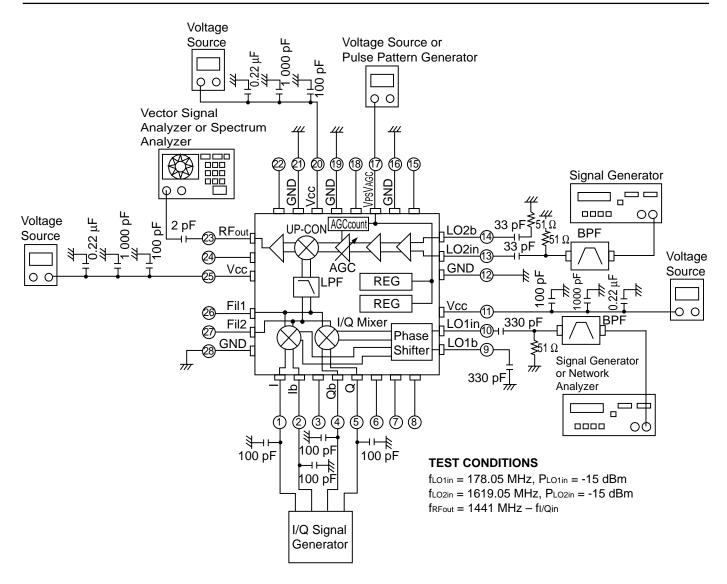

#### **TEST CIRCUIT**

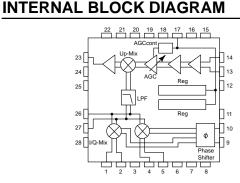

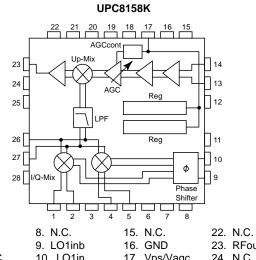

#### INTERNAL BLOCK DIAGRAM AND PIN CONNECTIONS (Top View)

| 1. lin  | 8. N.C.    | 15. N.C.     | 22. N.C.  |

|---------|------------|--------------|-----------|

| 2. linb | 9. LO1inb  | 16. GND      | 23. RFout |

| 3. N.C. | 10. LO1in  | 17. Vps/Vagc | 24. N.C.  |

| 4. Qinb | 11. Vcc    | 18. N.C.     | 25. Vcc   |

| 5. Qin  | 12. GND    | 19. GND      | 26. Fil1  |

| 6. N.C. | 13. LO2in  | 20. Vcc      | 27. Fil2  |

| 7. N.C. | 14. LO2inb | 21. GND      | 28. GND   |

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE                            | QUANTITY          |

|-------------|------------------------------------|-------------------|

| UPC8158K-E1 | 28-pin plastic QFN<br>(5.1x0.95mm) | QTY. 2.5 kp/Reel. |

Notes:

1. Embossed tape 12 mm wide. Pin 1 is in pull-out direction.

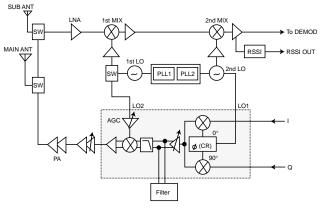

#### SYSTEM APPLICATION

#### PCS/TDMA PHONE

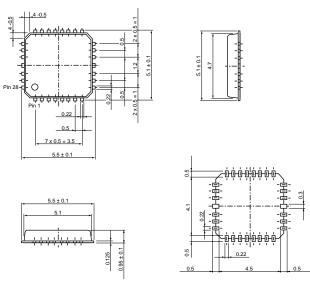

#### PACKAGE OUTLINE (Units in mm)

UPC8158K 28 PIN PLASTIC QFN

(Bottom View)