- 512 × 1 Sensor-Element Organization

- 200 Dots-Per-Inch (DPI) Sensor Pitch

- High Linearity and Uniformity

- Wide Dynamic Range . . . 2000:1 (66 dB)

- Output Referenced to Ground

- Low Image Lag . . . 0.5% Typ

- Operation to 5 MHz

- Single 5-V Supply

- Replacement for TSL208

# **Description**

The TSL208R linear sensor array consists of a  $512 \times 1$  array of photodiodes and associated charge amplifier circuitry. The pixels measure 120  $\mu$ m (H) by 70  $\mu$ m (W) with 125- $\mu$ m center-to-center spacing and 55- $\mu$ m spacing between pixels. Operation is simplified by internal control logic that requires only a serial-input (SI) signal and a clock.

The TSL208R is intended for use in a wide variety of applications including mark detection and code reading, optical character recognition (OCR) and contact imaging, edge detection and positioning as well as optical linear and rotary encoding.

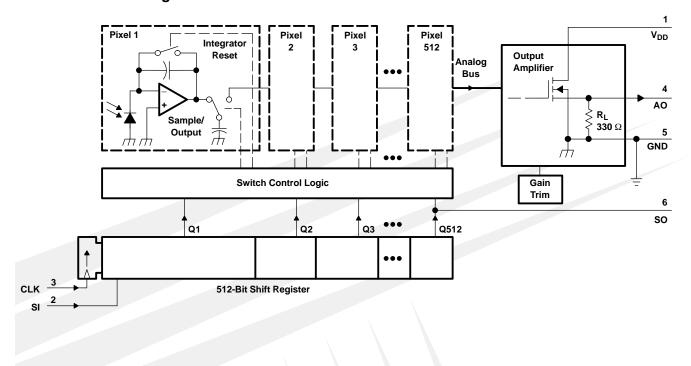

#### **Functional Block Diagram**

The *LUMENOLOGY*® Company

Copyright © 2002, TAOS Inc.

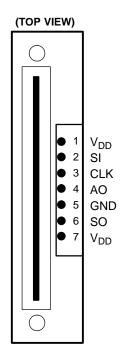

#### **Terminal Functions**

| TERMII | NAL  |     | DECORPTION                                                           |  |

|--------|------|-----|----------------------------------------------------------------------|--|

| NAME   | NO.  | 1/0 | DESCRIPTION                                                          |  |

| AO     | 4    | 0   | Analog output.                                                       |  |

| CLK    | 3    | ı   | ock. The clock controls the charge transfer, pixel output and reset. |  |

| GND    | 5    | I   | round (substrate). All voltages are referenced to the substrate.     |  |

| SI     | 2    | ı   | erial input. SI defines the start of the data out sequence.          |  |

| SO     | 6    | 0   | erial output. SO signals the end of the data out sequence.           |  |

| VDD    | 1, 7 | ı   | upply voltage for both analog and digital circuits.                  |  |

#### **Detailed Description**

The sensor consists of 512 photodiodes arranged in a linear array. Light energy impinging on a photodiode generates photocurrent, which is integrated by the active integration circuitry associated with that pixel. During the integration period, a sampling capacitor connects to the output of the integrator through an analog switch. The amount of charge accumulated at each pixel is directly proportional to the light intensity and the integration time. The integration time is the interval between two consecutive output periods.

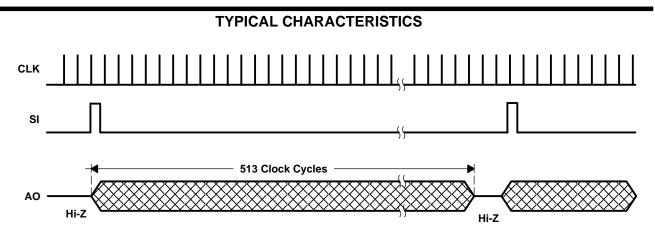

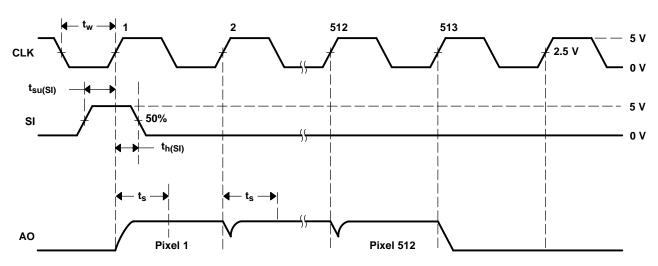

The output and reset of the integrators is controlled by a 512-bit shift register and reset logic. An output cycle is initiated by clocking in a logic 1 on SI for one positive going clock edge (see Figures1 and 2)<sup>†</sup>. As the SI pulse is clocked through the 512-bit shift register, the charge on the sampling capacitor of each pixel is sequentially connected to a charge-coupled output amplifier that generates a voltage output, AO. When the bit position goes low, the pixel integrator is reset. On the 513th clock rising edge, the SI pulse is clocked out of the shift register and the output assumes a high-impedance state. Note that this 513th clock pulse is required to terminate the output of the 512th pixel and return the internal logic to a known state. A subsequent SI pulse can be presented as early as the 514th clock pulse, thereby initiating another pixel output cycle.

The voltage developed at analog output (AO) is given by:

$$V_{out} = V_{drk} + (R_e) (E_e) (t_{int})$$

where:

$V_{out}$  is the analog output voltage for white condition  $V_{drk}$  is the analog output voltage for dark condition

R<sub>e</sub> is the device responsivity for a given wavelength of light given in V/(μJ/cm<sup>2</sup>)

$\begin{array}{ll} E_e & \text{is the incident irradiance in $\mu$W/cm$}^2 \\ t_{int} & \text{is integration time in seconds} \end{array}$

AO is driven by a source follower with an internal  $330-\Omega$  pulldown resistor (no external resistor is required). The output is nominally 0 V for no light input, 2 V for normal white-level, and 3.4 V for saturation light level. When the device is not in the output phase, AO is in a high impedance state.

A 0.1  $\mu$ F bypass capacitor should be connected between  $V_{DD}$  and ground as close as possible to the device.

† For proper operation, after meeting the minimum hold time condition, SI must go low before the next rising edge of the clock.

# Absolute Maximum Ratings<sup>†</sup>

| Supply voltage range, V <sub>DD</sub>                          |                                           |

|----------------------------------------------------------------|-------------------------------------------|

| Input voltage range, V <sub>I</sub>                            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{V}$ |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{DD}$ )  | –20 mA to 20 mA                           |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{DD}$ ) | –25 mA to 25 mA                           |

| Voltage range applied to any output in the high impedance or   |                                           |

| power-off state, V <sub>O</sub>                                | $-0.3 \text{ V to V}_{DD} + 0.3 \text{V}$ |

| Continuous output current, $I_O(V_O = 0 \text{ to } V_{DD})$   | –25 mA to 25 mA                           |

| Continuous current through V <sub>DD</sub> or GND              | –100 mA to 100 mA                         |

| Analog output current range, I <sub>O</sub>                    | –25 mA to 25 mA                           |

| Operating free-air temperature range, T <sub>A</sub>           | –25°C to 85°C                             |

| Storage temperature range, T <sub>stq</sub>                    | –25°C to 85°C                             |

| Lead temperature on connection pad for 10 seconds              | 260°C                                     |

| ESD tolerance, human body model                                | 2000 V                                    |

|                                                                |                                           |

<sup>&</sup>lt;sup>†</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions (see Figure 1 and Figure 2)**

|                                                | MIN    | NOM | MAX      | UNIT |

|------------------------------------------------|--------|-----|----------|------|

| Supply voltage, V <sub>DD</sub>                | 4.5    | 5   | 5.5      | V    |

| Input voltage, V <sub>I</sub>                  | 0      |     | $V_{DD}$ | V    |

| High-level input voltage, V <sub>IH</sub>      | 2      |     | $V_{DD}$ | V    |

| Low-level input voltage, V <sub>IL</sub>       | 0      |     | 0.8      | V    |

| Wavelength of light source, $\lambda$          | 400    |     | 1000     | nm   |

| Clock frequency, f <sub>clock</sub>            | 5      |     | 5000     | kHz  |

| Sensor integration time, t <sub>int</sub>      | 0.1026 |     | 100      | ms   |

| Operating free-air temperature, T <sub>A</sub> | 0      |     | 70       | °C   |

| Load resistance, R <sub>L</sub>                | 300    |     | 4700     | Ω    |

| Load capacitance, C <sub>L</sub>               |        |     | 330      | pF   |

# Electrical Characteristics at $f_{clock}$ = 1 MHz, $V_{DD}$ = 5 V, $T_A$ = 25°C, $\lambda_p$ = 640 nm, $t_{int}$ = 5 ms, $R_L = 330 \Omega$ , $E_e = 18 \mu W/cm^2$ (unless otherwise noted)

|                     | PARAMETER                                              | TEST CONDITIONS        | MIN | TYP   | MAX  | UNIT                        |  |

|---------------------|--------------------------------------------------------|------------------------|-----|-------|------|-----------------------------|--|

| V <sub>out</sub>    | Analog output voltage (white, average over 512 pixels) | See Note 1             | 1.6 | 2     | 2.4  | V                           |  |

| $V_{drk}$           | Analog output voltage (dark, average over 512 pixels)  |                        | 0   | 50    | 150  | mV                          |  |

| PRNU                | Pixel response nonuniformity                           | See Notes 2 & 3        |     | ±7%   | ±20% |                             |  |

|                     | Nonlinearity of analog output voltage                  | See Note 3             |     | ±0.4% |      | FS                          |  |

|                     | Output noise voltage                                   | See Note 4             |     | 1     |      | mVrms                       |  |

| R <sub>e</sub>      | Responsivity                                           |                        | 16  | 22    | 28   | V/<br>(μJ/cm <sup>2</sup> ) |  |

| SE                  | Saturation exposure                                    | See Note 5             |     | 155   |      | nJ/cm <sup>2</sup>          |  |

| $V_{\text{sat}}$    | Analog output saturation voltage                       |                        | 2.5 | 3.4   |      | V                           |  |

| DSNU                | Dark signal nonuniformity                              | All pixels See Note 6  |     | 25    | 120  | mV                          |  |

| IL                  | Image lag                                              | See Note 7             |     | 0.5%  |      |                             |  |

| $I_{DD}$            | Supply current, output idle                            |                        |     | 28    | 45   | mA                          |  |

| I <sub>IH</sub>     | High-level input current                               | $V_I = V_{DD}$         |     |       | 10   | μΑ                          |  |

| I <sub>IL</sub>     | Low-level input current                                | V <sub>I</sub> = 0     |     |       | 10   | μΑ                          |  |

| .,                  | High level autout valteurs CO                          | I <sub>O</sub> = 50 μA | 4.5 | 4.95  |      |                             |  |

| V <sub>OH</sub>     | High-level output voltage, SO                          | I <sub>O</sub> = 4 mA  |     | 4.6   |      | · V                         |  |

| V                   | Landard advisor 20                                     | I <sub>O</sub> = 50 μA |     | 0.01  | 0.1  | V                           |  |

| $V_{OL}$            | Low-level output voltage, SO                           | I <sub>O</sub> = 4 mA  |     | 0.4   |      | 1 '                         |  |

| C <sub>i(SI)</sub>  | Input capacitance, SI                                  |                        |     | 40    |      | pF                          |  |

| C <sub>i(CLK)</sub> | Input capacitance, CLK                                 |                        |     | 40    |      | pF                          |  |

- NOTES: 1. The array is uniformly illuminated with a diffused LED source having a peak wavelength of 640 nm.

- 2. PRNU is the maximum difference between the voltage from any single pixel and the average output voltage from all pixels of the device under test when the array is uniformly illuminated at the white irradiance level. PRNU includes DSNU.

- 3. Nonlinearity is defined as the maximum deviation from a best-fit straight line over the dark-to-white irradiance levels, as a percent of analog output voltage (white).

- 4. RMS noise is the standard deviation of a single-pixel output under constant illumination as observed over a 5-second period.

- 5. Minimum saturation exposure is calculated using the minimum V<sub>sat</sub>, the maximum V<sub>drk</sub>, and the maximum R<sub>e</sub>.

- 6. DSNU is the difference between the maximum and minimum output voltage in the absence of illumination.

- 7. Image lag is a residual signal left in a pixel from a previous exposure. It is defined as a percent of white-level signal remaining after a pixel is exposed to a white condition followed by a dark condition:

$$IL = \frac{V_{out (IL)} - V_{drk}}{V_{out (white)} - V_{drk}} \times 100$$

# Timing Requirements (see Figure 1 and Figure 2)

|                                 |                                                 | MIN | NOM | MAX | UNIT |

|---------------------------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>su(SI)</sub>             | Setup time, serial input (see Note 8)           | 20  |     |     | ns   |

| t <sub>h(SI)</sub>              | Hold time, serial input (see Note 8 and Note 9) | 0   |     |     | ns   |

| t <sub>w</sub>                  | Pulse duration, clock high or low               | 50  |     |     | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Input transition (rise and fall) time           | 0   |     | 500 | ns   |

NOTES: 8. Input pulses have the following characteristics:  $t_f = 6$  ns,  $t_f = 6$  ns.

9. SI must go low before the rising edge of the next clock pulse.

# Dynamic Characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 2)

|                     | PARAMETER                          | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|---------------------|------------------------------------|------------------------|-----|-----|-----|------|

| ts                  | Analog output settling time to ±1% | C <sub>L</sub> = 10 pF |     | 185 |     | ns   |

| t <sub>pd(SO)</sub> | Propagation delay time, SO         |                        |     | 50  |     | ns   |

Figure 1. Timing Waveforms (each section)

Figure 2. Operational Waveforms (each section)

### **TYPICAL CHARACTERISTICS**

#

Figure 3

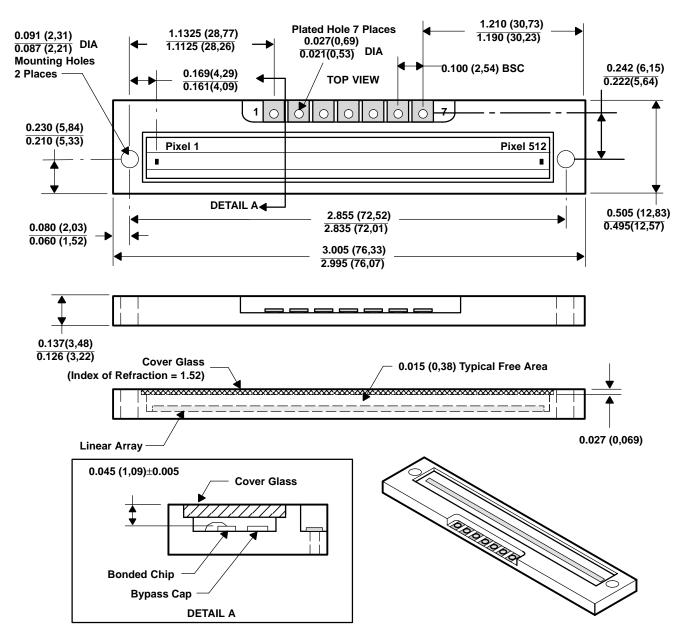

#### **MECHANICAL INFORMATION**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Pixel centers are located along the center line of the mounting holes.

Figure 4. TSL208R Mechanical Specifications

TAOS031C - OCTOBER 2002

**PRODUCTION DATA** — information in this document is current at publication date. Products conform to specifications in accordance with the terms of Texas Advanced Optoelectronic Solutions, Inc. standard warranty. Production processing does not necessarily include testing of all parameters.

#### NOTICE

Texas Advanced Optoelectronic Solutions, Inc. (TAOS) reserves the right to make changes to the products contained in this document to improve performance or for any other purpose, or to discontinue them without notice. Customers are advised to contact TAOS to obtain the latest product information before placing orders or designing TAOS products into systems.

TAOS assumes no responsibility for the use of any products or circuits described in this document or customer product design, conveys no license, either expressed or implied, under any patent or other right, and makes no representation that the circuits are free of patent infringement. TAOS further makes no claim as to the suitability of its products for any particular purpose, nor does TAOS assume any liability arising out of the use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

TEXAS ADVANCED OPTOELECTRONIC SOLUTIONS, INC. PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN CRITICAL APPLICATIONS IN WHICH THE FAILURE OR MALFUNCTION OF THE TAOS PRODUCT MAY RESULT IN PERSONAL INJURY OR DEATH. USE OF TAOS PRODUCTS IN LIFE SUPPORT SYSTEMS IS EXPRESSLY UNAUTHORIZED AND ANY SUCH USE BY A CUSTOMER IS COMPLETELY AT THE CUSTOMER'S RISK.

LUMENOLOGY is a registered trademark, and TAOS, the TAOS logo, and Texas Advanced Optoelectronic Solutions are trademarks of Texas Advanced Optoelectronic Solutions Incorporated.