## FEATURES

- Generates 12-output buffers from one input.

- Supports VIA Pro266 DDR chipset.

- Supports up to 2 DDR DIMMS.

- Supports up to 400MHz DDR, SDRAMS.

- One additional output for feedback.

- 6 differential clock distribution.

- Less than 5ns delay.

- Skew between any outputs is less than 100 ps.

- 2.5V Supply range.

- Available in 28-pin SSOP.

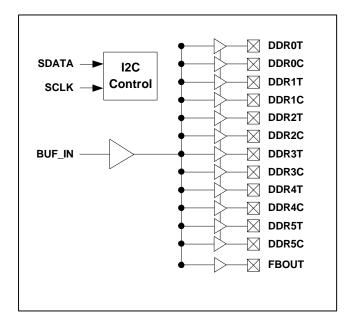

## **BLOCK DIAGRAM**

#### **PIN CONFIGURATION**

| FBOUT  | 1  | 0         | 28 | GND     |

|--------|----|-----------|----|---------|

| GND    | 2  |           | 27 | DDRT5   |

| DDRT0  | 3  |           | 26 | DDRC5   |

| DDRC0  | 4  |           | 25 | VDD2.5  |

| VDD2.5 | 5  | -         | 24 | GND     |

| GND    | 6  | Ĕ         | 23 | DDRT4   |

| DDRT1  | 7  | 7         | 22 | DDRC4   |

| DDRC1  | 8  | Ģ         | 21 | VDD2.5  |

| VDD2.5 | 9  | PLL103-07 | 20 | GND     |

| BUF_IN | 10 |           | 19 | DDRT3   |

| GND    | 11 |           | 18 | DDRC3   |

| DDRT2  | 12 |           | 17 | VDD2.5  |

| DDRC2  | 13 |           | 16 | SCLK    |

| VDD2.5 | 14 |           | 15 | ] SDATA |

|        |    |           |    |         |

Note: #: Active Low

#### DESCRIPTIONS

The PLL103-07 is designed as a 2.5V buffer to distribute high-speed clocks in PC applications. The device has 12 outputs. These outputs can be configured to support 2 DDR DIMMs. The PLL103-07 can be used in conjunction with the PLL202-04 or similar clock synthesizer for the VIA Pro 266 chipset.

#### **PIN DESCRIPTIONS**

| Name      | Number              | Туре | Description                                        |

|-----------|---------------------|------|----------------------------------------------------|

| FBOUT     | 1                   | 0    | Feedback clock for chipset.                        |

| BUF_IN    | 10                  | I    | Reference input from chipset.                      |

| DDRT[0:5] | 3,7,12,19,<br>23,27 | 0    | True clocks of differential pair outputs.          |

| DDRC[0:5] | 4,8,13,18,<br>22,26 | 0    | Complementary clocks of differential pair outputs. |

| VDD2.5    | 5,9,14,<br>17,21,25 | Ρ    | 2.5V power supply.                                 |

| GND       | 6,11,20,24          | Р    | Ground.                                            |

## **I2C BUS CONFIGURATION SETTING**

| Address Assignment                                                                                                                                                                                                                                                                  | A6                                  | A5                                                     | A4                                                   | A3                                                   | A2                                                       | A1                                                     | A0                                                    | R/W                          |                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|------------------------------|----------------------------------------------|--|--|

| , laar ooo , loorginnon                                                                                                                                                                                                                                                             | 1                                   | 1                                                      | 0                                                    | 1                                                    | 0                                                        | 0                                                      | 1                                                     | _                            |                                              |  |  |

| Slave<br>Receiver/Transmitter                                                                                                                                                                                                                                                       | Provid                              | Provides both slave write and readback functionality   |                                                      |                                                      |                                                          |                                                        |                                                       |                              |                                              |  |  |

| Data Transfer Rate                                                                                                                                                                                                                                                                  | Stand                               | ard mode                                               | at 100kbi                                            | ts/s                                                 |                                                          |                                                        |                                                       |                              |                                              |  |  |

|                                                                                                                                                                                                                                                                                     |                                     |                                                        |                                                      |                                                      |                                                          |                                                        |                                                       |                              |                                              |  |  |

| Data Protocol                                                                                                                                                                                                                                                                       | bytes<br>must t<br>termin<br>addres | must be a<br>be followe<br>ate the trans<br>ss and a v | iccessed i<br>d by 1 acl<br>ansfer. Th<br>vrite cond | n sequenti<br>knowledge<br>e write or<br>ition (0xD2 | al order fr<br>bit. A byte<br>read block<br>?) or a read | om lowest<br>e transferr<br>c both begi<br>d conditior | to highest<br>ed without<br>ins with the<br>n (0xD3). | acknowledge<br>e master send | yte transferred<br>d bit will<br>ing a slave |  |  |

| Following the acknowledge of this address byte, in Write Mode: the Command Byte<br>Count Byte must be sent by the master but ignored by the slave, in Read Mode: the<br>Count Byte will be read by the master then all other Data Byte. Byte Count Byte of<br>power-up is = (0x09). |                                     |                                                        |                                                      |                                                      |                                                          | de: the Byte                                           |                                                       |                              |                                              |  |  |

## **I2C CONTROL REGISTERS**

#### 1. BYTE 6: Outputs Register (1=Enable, 0=Disable)

| Bit   | Pin#   | Default | Description  |

|-------|--------|---------|--------------|

| Bit 7 | -      | 1       | Reserved     |

| Bit 6 | -      | 0       | Reserved     |

| Bit 5 | -      | 0       | Reserved     |

| Bit 4 | -      | 0       | Reserved     |

| Bit 3 | -      | 1       | Reserved     |

| Bit 2 | 27, 26 | 1       | DDRT5, DDRC5 |

| Bit 1 | 23, 22 | 1       | DDRT4, DDRC4 |

| Bit 0 | 19, 18 | 1       | DDRT3, DDRC3 |

## 2. BYTE 7: Outputs Register (1=Enable, 0=Disable)

| Bit   | Pin#   | Default | Description  |

|-------|--------|---------|--------------|

| Bit 7 | -      | 1       | Reserved     |

| Bit 6 | -      | 1       | Reserved     |

| Bit 5 | -      | 1       | Reserved     |

| Bit 4 | 12, 13 | 1       | DDRT2, DDRC2 |

| Bit 3 | -      | 1       | Reserved     |

| Bit 2 | 7, 8   | 1       | DDRT1, DDRC1 |

| Bit 1 | -      | 1       | Reserved     |

| Bit 0 | 3, 4   | 1       | DDRT0, DDRC0 |

## **ELECTRICAL SPECIFICATIONS**

#### 1. Absolute Maximum Ratings

| PARAMETERS                    | SYMBOL          | MIN.                 | MAX.                 | UNITS |

|-------------------------------|-----------------|----------------------|----------------------|-------|

| Supply Voltage                | V <sub>DD</sub> | V <sub>SS</sub> -0.5 | 7.0                  | V     |

| Input Voltage, dc             | VI              | Vss-0.5              | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc            | Vo              | Vss-0.5              | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature           | Τ <sub>S</sub>  | -65                  | 150                  | °C    |

| Ambient Operating Temperature | TA              | 0                    | 70                   | °C    |

| ESD Voltage                   |                 |                      | 2                    | KV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

#### 2. Operating Conditions

| PARAMETERS         | SYMBOL | MIN.  | MAX.  | UNITS |

|--------------------|--------|-------|-------|-------|

| Supply Voltage     | Vdd2.5 | 2.375 | 2.625 | V     |

| Input Capacitance  | CIN    |       | 5     | pF    |

| Output Capacitance | Соит   |       | 6     | pF    |

#### **3. Electrical Specifications**

| PARAMETERS             | SYMBOL           | CONDITIONS                        | MIN.    | TYP. | MAX.                 | UNITS |

|------------------------|------------------|-----------------------------------|---------|------|----------------------|-------|

| Input High Voltage     | VIH              | All Inputs except I2C             | 2.0     |      | V <sub>DD</sub> +0.3 | V     |

| Input Low Voltage      | VIL              | All inputs except I2C             | Vss-0.3 |      | 0.8                  | V     |

| Input High Current     | Іін              | V <sub>IN</sub> = V <sub>DD</sub> |         |      | ТВМ                  | uA    |

| Input Low Current      | ١ <sub>١</sub> ٢ | V <sub>IN</sub> = 0               |         |      | ТВМ                  | uA    |

| Output High<br>Voltage | V <sub>OH</sub>  | IOL = -12mA, VDD = 2.375V         | 1.7     |      |                      | V     |

| Output Low<br>Voltage  | Vol              | IOL = 12mA, VDD = 2.375V          |         |      | 0.6                  | V     |

| Output High<br>Current | I <sub>ОН</sub>  | VDD = 2.375V, VOUT=1V             | -18     | -32  |                      | mA    |

| Output Low<br>Current  | I <sub>OL</sub>  | VDD = 2.375V, VOUT=1.2V           | 26      | 35   |                      | mA    |

Note: TBM: To be measured

## 3. Electrical Specifications (Continued)

| PARAMETERS                        | SYMBOL          | CONDITIONS                            | MIN.            | TYP.  | MAX.            | UNITS |

|-----------------------------------|-----------------|---------------------------------------|-----------------|-------|-----------------|-------|

| Supply Current<br>(DDR-only mode) | I <sub>DD</sub> | Unloaded outputs, 133MHz              |                 |       | TBM             | mA    |

| Supply Current<br>(SDRAM mode)    | I <sub>DD</sub> | Unloaded outputs, 133MHz              |                 |       | TBM             | mA    |

| Supply Current                    | Idds            | PD = 0                                |                 |       | TBM             | mA    |

| Output Crossing<br>Voltage        | Voc             |                                       | (VDD/2)<br>-0.1 | VDD/2 | (VDD/2)+<br>0.1 | V     |

| Output Voltage Swing              | Vout            |                                       | 0.7             |       | VDD-0.4         | V     |

| Duty Cycle                        | DT              | Measured @ 1.5V                       | 45              | 50    | 55              | %     |

| Max. Operating<br>Frequency       |                 |                                       | 66              |       | 170             | MHz   |

| Rising Edge Rate                  | T <sub>OR</sub> | Measured @ 0.4V ~ 2.4V                | 1.0             | 1.5   | 2.0             | V/ns  |

| Falling Edge Rate                 | Tof             | Measured @ 2.4V ~ 0.4V                | 1.0             | 1.5   | 2.0             | V/ns  |

| DDR Rising Edge Rate              | Tor             | Measured between 20% to 80% of output | 0.25            | 0.6   | 1.0             | V/ns  |

| DDR Falling Edge Rate             | Tof             | Measured between 20% to 80% of output | 0.25            | 0.6   | 1.0             | V/ns  |

| Clock Skew(pin to pin)            | Тѕкеw           | All outputs equally loaded            |                 |       | 100             | ps    |

| Stabilization Time                | T <sub>ST</sub> |                                       |                 |       | 0.1             | ms    |

**Note:** TBM: To be measured

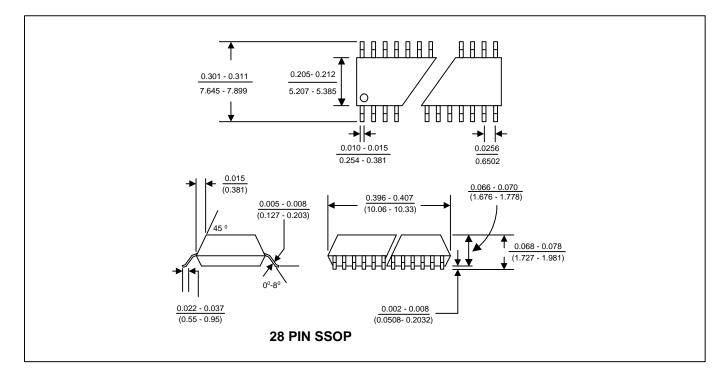

### PACKAGE INFORMATION

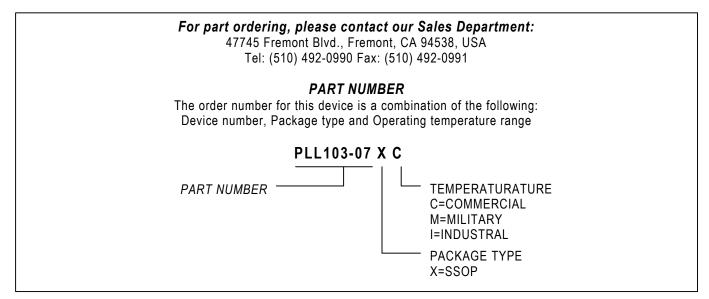

#### **ORDERING INFORMATION**

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by PhaseLink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

**LIFE SUPPORT POLICY**: PhaseLink s products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.