# **Product Specification PE3341**

# 2700 MHz Integer-N PLL with Field-Programmable EEPROM

# **Features**

- Field-programmable EEPROM for selfstarting applications

- Standard 2700 MHz operation, 3000 MHz speed-grade option

- ÷10/11 dual modulus prescaler

- Internal charge pump

- Serial programmable

- Low power 20 mA at 3 V

- Ultra-low phase noise

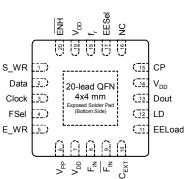

- Available in 24-lead TSSOP or 20-lead 4x4 mm QFN package

# **Product Description**

The PE3341 is a high performance integer-N PLL with embedded EEPROM capable of frequency synthesis up to 2700 MHz with a speed-grade option to 3000 MHz. The EEPROM allows designers to permanently store control bits. allowing easy configuration of self-starting synthesizers. The superior phase noise performance of the PE3341 is ideal for applications such as sonet, wireless base stations, fixed wireless, and RF instrumentation systems.

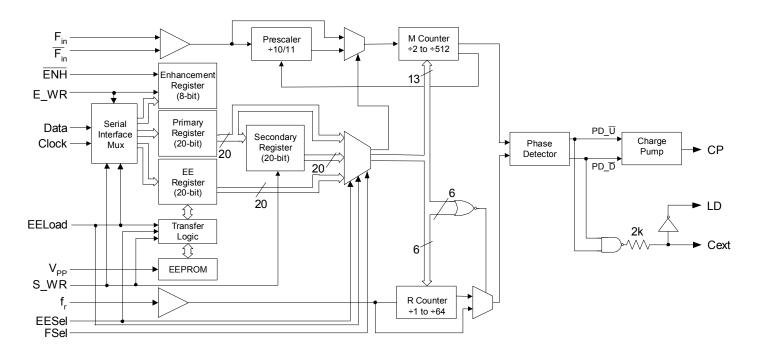

The PE3341 features a ÷10/11 dual modulus prescaler, counters, a phase comparator, and a charge pump as shown in Figure 1. Counter values are programmable through a threewire serial interface.

The PE3341 UltraCMOS™ Phase Locked-Loop is manufactured in Peregrine's patented Ultra Thin Silicon (UTSi®) CMOS process, offering excellent RF performance with the economy and integration of conventional CMOS.

Figure 1. Block Diagram

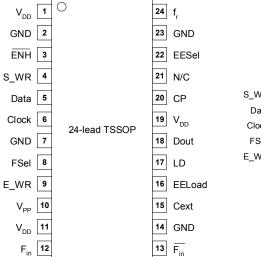

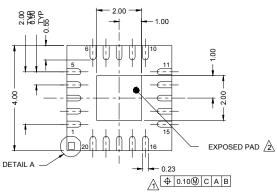

Figure 2. Pin Configurations (Top View)

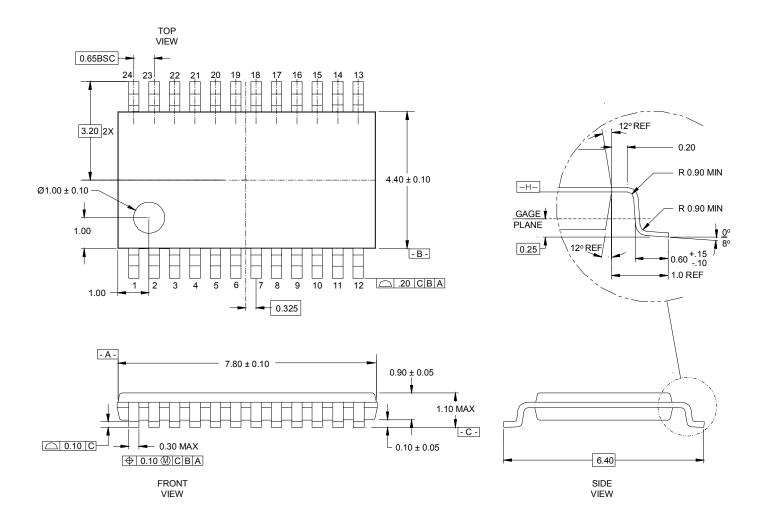

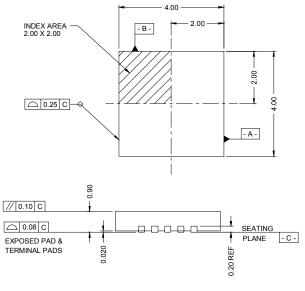

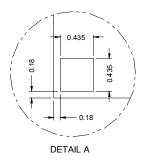

Figure 3. Package Types 24-lead TSSOP, 20-lead QFN

**Table 2. Pin Descriptions**

| Pin No.<br>TSSOP | Pin No.<br>QFN | Pin Name         | Туре       | Description                                                                                                                                                                                                                      |

|------------------|----------------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | 19             | $V_{DD}$         | (Note 1)   | Power supply input. Input may range from 2.85 V to 3.15 V. Bypassing required.                                                                                                                                                   |

| 2                |                | GND              | (Note 2)   | Ground.                                                                                                                                                                                                                          |

| 3                | 20             | ENH              | Input      | Enhancement mode control line. When asserted LOW, enhancement register bits are functional. Internal 70 k $\Omega$ pull-up resistor.                                                                                             |

| 4                | 1              | S_WR             | Input      | Secondary Register WRITE input. Primary Register contents are copied to the Secondary Register on S_WR rising edge. Also used to control Serial Port operation and EEPROM programming.                                           |

| 5                | 2              | Data             | Input      | Binary serial data input. Input data entered LSB (B <sub>0</sub> ) first.                                                                                                                                                        |

| 6                | 3              | Clock            | Input      | Serial clock input. Data is clocked serially into the 20-bit Primary Register, the 20-bit EE Register, or the 8-bit Enhancement Register on the rising edge of Clock. Also used to clock EE Register data out Dout port.         |

| 7                |                | GND              | (Note 2)   | Ground.                                                                                                                                                                                                                          |

| 8                | 4              | FSel             | Input      | Frequency Register selection control line. Internal 70 k $\Omega$ pull-down resistor.                                                                                                                                            |

| 9                | 5              | E_WR             | Input      | Enhancement Register write enable. Also functions as a Serial Port control line. Internal 70 k $\Omega$ pull-down resistor.                                                                                                      |

| 10               | 6              | V <sub>PP</sub>  | Input      | EEPROM erase/write programming voltage supply pin. Requires a 100pF bypass capacitor connected to GND.                                                                                                                           |

| 11               | 7              | $V_{DD}$         | (Note 1)   | Same as pin 1.                                                                                                                                                                                                                   |

| 12               | 8              | F <sub>in</sub>  | Input      | Prescaler input from the VCO.                                                                                                                                                                                                    |

| 13               | 9              | F <sub>in</sub>  | Input      | Prescaler complementary input. A series 50 $\Omega$ resistor and DC blocking capacitor should be placed as close as possible to this pin and connected to the ground plane.                                                      |

| 14               |                | GND              | (Note 2)   | Ground.                                                                                                                                                                                                                          |

| 15               | 10             | C <sub>EXT</sub> | Output     | Logical "NAND" of PD_U and PD_D terminated through an on-chip, 2 k $\Omega$ series resistor. Connecting C <sub>EXT</sub> to an external capacitor will low pass filter the input to the inverting amplifier used for driving LD. |

| 16               | 11             | EELoad           | Input      | Control line for Serial Data Port, Frequency Register selection, EE Register parallel loading, and EEPROM programming. Internal 70 k $\Omega$ pull-down resistor.                                                                |

| 17               | 12             | LD               | Output, OD | Lock detect output, an open-drain logical inversion of $C_{\text{EXT}}$ . When the loop is in lock, LD is high impedance; otherwise, LD is a logic LOW.                                                                          |

| Pin No.<br>TSSOP | Pin No.<br>QFN | Pin Name       | Туре     | Description                                                                                                                                   |

|------------------|----------------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 18               | 13             | Dout           | Output   | Data out function. Dout is defined with the Enhancement Register and enabled with $\overline{\mathrm{ENH}}$ .                                 |

| 19               | 14             | $V_{DD}$       | (Note 1) | Same as pin 1.                                                                                                                                |

| 20               | 15             | СР             | Output   | Charge pump output. Sources current is when $f_c$ leads $f_p$ and sinks current when $f_c$ lags $f_p$ .                                       |

| 21               | 16             | N/C            |          | No connection.                                                                                                                                |

| 22               | 17             | EESel          | Input    | Control line for Frequency Register selection, EE Register parallel loading, and EEPROM programming. Internal 70 k $\Omega$ pull-up resistor. |

| 23               |                | GND            | (Note 2) | Ground.                                                                                                                                       |

| 24               | 18             | f <sub>r</sub> | Input    | Reference frequency input.                                                                                                                    |

Notes 1: VDD pins 1, 11, and 19 (TSSOP) or pins 6, 14 and 19 (QFN), are connected by diodes and must be supplied with the same positive voltage level

**Table 2. Absolute Maximum Ratings**

| Symbol           | Parameter/Conditions         | Min  | Max                  | Units |

|------------------|------------------------------|------|----------------------|-------|

| $V_{DD}$         | Supply voltage               | -0.3 | +4.0                 | V     |

| Vı               | Voltage on any digital input | -0.3 | V <sub>DD</sub> +0.3 | V     |

| T <sub>Stg</sub> | Storage temperature range    | -65  | +85                  | °C    |

Absolute Maximum Ratings are those values listed in the above table. Exceeding these values may cause permanent device damage. Functional operation should be restricted to the limits in the DC and AC Characteristics table. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Table 3. DC Electrical Specifications

| Symbol         | Parameter/Conditions                | Min  | Max  | Units |

|----------------|-------------------------------------|------|------|-------|

| $V_{DD}$       | Supply voltage                      | 2.85 | 3.15 | V     |

| T <sub>A</sub> | Operating ambient temperature range | -40  | 85   | °C    |

**Table 4. ESD Ratings**

| Symbol                              | Parameter/Conditions                  | Min | Max  | Units |

|-------------------------------------|---------------------------------------|-----|------|-------|

| $V_{ESD}$                           | ESD voltage human body model (Note 1) |     | 1000 | V     |

| V <sub>ESD</sub> (V <sub>PP</sub> ) | ESD voltage human body model (Note 1) |     | 200  | V     |

Note 1: Periodically sampled, not 100% tested. Tested per MIL-STD-883, M3015 C2

# **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating in Table 4.

## **Latch-Up Avoidance**

Unlike conventional CMOS devices, UltraCMOS™ devices are immune to latch-up.

<sup>2:</sup> Ground connections are made through the exposed solder pad. The solder pad must be soldered to the ground plane for proper operation.

# **Table 5. DC Characteristics**

# $V_{\text{DD}}$ = 3.0 V, -40° C < $T_{\text{A}}$ < 85° C, unless otherwise specified

| Symbol                                                 | Parameter                                                         | Conditions                                                                                   | Min                   | Тур  | Max                   | Units |

|--------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>DD</sub>                                        | Operational supply current; Prescaler enabled                     | V <sub>DD</sub> = 2.85 to 3.15 V                                                             |                       | 20   | 30                    | mA    |

| Digital Inputs:                                        | S_WR, Data, Clock                                                 | - 1                                                                                          | •                     |      | •                     |       |

| V <sub>IH</sub>                                        | High-level input voltage                                          | $V_{DD} = 2.85 \text{ to } 3.15 \text{ V}$                                                   | 0.7 x V <sub>DD</sub> |      |                       | V     |

| V <sub>IL</sub>                                        | Low-level input voltage                                           | V <sub>DD</sub> = 2.85 to 3.15 V                                                             |                       |      | 0.3 x V <sub>DD</sub> | V     |

| I <sub>IH</sub>                                        | High-level input current                                          | $V_{IH} = V_{DD} = 3.15 \text{ V}$                                                           |                       |      | +1                    | μA    |

| I <sub>IL</sub>                                        | Low-level input current                                           | $V_{IL} = 0, V_{DD} = 3.15 \text{ V}$                                                        | -1                    |      |                       | μA    |

| Digital inputs:                                        | ENH, EESel (contains a 70 kΩ pull-up resistor)                    | -                                                                                            | l                     |      | _ L                   |       |

| V <sub>IH</sub>                                        | High-level input voltage                                          | $V_{DD} = 2.85 \text{ to } 3.15 \text{ V}$                                                   | 0.7 x V <sub>DD</sub> |      |                       | V     |

| V <sub>IL</sub>                                        | Low-level input voltage                                           | $V_{DD} = 2.85 \text{ to } 3.15 \text{ V}$                                                   |                       |      | 0.3 x V <sub>DD</sub> | V     |

| I <sub>IH</sub>                                        | High-level input current                                          | $V_{IH} = V_{DD} = 3.15 \text{ V}$                                                           |                       |      | +1                    | μA    |

| I <sub>IL</sub>                                        | Low-level input current                                           | $V_{IL} = 0, V_{DD} = 3.15 \text{ V}$                                                        | -100                  |      |                       | μA    |

| Digital inputs:                                        | FSel, EELoad, E_WR (contains a 70 kΩ pull-down                    | resistor)                                                                                    |                       |      | · ·                   |       |

| V <sub>IH</sub>                                        | High-level input voltage                                          | $V_{DD} = 2.85 \text{ to } 3.15 \text{ V}$                                                   | 0.7 x V <sub>DD</sub> |      |                       | V     |

| V <sub>IL</sub>                                        | Low-level input voltage                                           | $V_{DD} = 2.85 \text{ to } 3.15 \text{ V}$                                                   |                       |      | 0.3 x V <sub>DD</sub> | V     |

| I <sub>IH</sub>                                        | High-level input current                                          | $V_{IH} = V_{DD} = 3.15 \text{ V}$                                                           |                       |      | +100                  | μA    |

| I <sub>IL</sub>                                        | Low-level input current                                           | $V_{IL} = 0, V_{DD} = 3.15 \text{ V}$                                                        | -1                    |      |                       | μA    |

| EE Memory P                                            | rogramming Voltage and Current: V <sub>PP</sub> , I <sub>PP</sub> | -                                                                                            | l                     |      | _ L                   |       |

| V <sub>PP</sub> _WRITE                                 | EEPROM write voltage                                              |                                                                                              |                       | 12.5 |                       | V     |

| V <sub>PP</sub> _ERASE                                 | EEPROM erase voltage                                              |                                                                                              |                       | -8.5 |                       | V     |

| I <sub>PP</sub> _WRITE                                 | EEPROM write cycle current                                        |                                                                                              |                       |      | 30                    | mA    |

| I <sub>PP</sub> _ERASE                                 | EEPROM erase cycle current                                        |                                                                                              | -10                   |      |                       | mA    |

| Reference Div                                          | rider input: f <sub>r</sub>                                       | -                                                                                            | l                     |      | _ L                   |       |

| I <sub>IHR</sub>                                       | High-level input current                                          | $V_{IH} = V_{DD} = 3.15 \text{ V}$                                                           |                       |      | +100                  | μA    |

| I <sub>ILR</sub>                                       | Low-level input current                                           | $V_{IL} = 0, V_{DD} = 3.15 \text{ V}$                                                        | -100                  |      |                       | μA    |

| Counter outpu                                          | it: Dout                                                          | -1                                                                                           |                       |      |                       |       |

| V <sub>OLD</sub>                                       | Output voltage LOW                                                | I <sub>out</sub> = 6 mA                                                                      |                       |      | 0.4                   | V     |

| V <sub>OHD</sub>                                       | Output voltage HIGH                                               | I <sub>out</sub> = -3 mA                                                                     | V <sub>DD</sub> - 0.4 |      |                       | V     |

| Lock detect or                                         | utputs: (C <sub>EXT</sub> , LD)                                   |                                                                                              |                       |      |                       |       |

| V <sub>OLC</sub>                                       | Output voltage LOW, C <sub>EXT</sub>                              | I <sub>out</sub> = 0.1 mA                                                                    |                       |      | 0.4                   | V     |

| V <sub>OHC</sub>                                       | Output voltage HIGH, C <sub>EXT</sub>                             | I <sub>out</sub> = -0.1 mA                                                                   | V <sub>DD</sub> - 0.4 |      |                       | V     |

| V <sub>OLLD</sub>                                      | Output voltage LOW, LD                                            | I <sub>out</sub> = 1 mA                                                                      |                       |      | 0.4                   | V     |

| Charge Pump                                            | output: CP                                                        | -                                                                                            | l                     |      | _ L                   |       |

| I <sub>CP</sub> – Source                               | Drive current                                                     | $V_{CP} = V_{DD} / 2$                                                                        | -2.6                  | -2   | -1.4                  | mA    |

| I <sub>CP</sub> – Sink                                 | Drive current                                                     | $V_{CP} = V_{DD} / 2$                                                                        | 1.4                   | 2    | 2.6                   | mA    |

| I <sub>CPL</sub>                                       | Leakage current                                                   | 1.0 V < V <sub>CP</sub> < V <sub>DD</sub> - 1.0 V                                            | -1                    |      | 1                     | μA    |

| I <sub>CP</sub> - Source<br>vs. I <sub>CP</sub> – Sink | Sink vs. source mismatch                                          | $V_{CP} = V_{DD} / 2$ , $T_A = 25^{\circ} C$                                                 |                       |      | 15                    | %     |

| $I_{\text{CP}}$ vs. $V_{\text{CP}}$                    | Output current magnitude variation vs. voltage                    | $1.0 \text{ V} < \text{V}_{CP} < \text{V}_{DD} - 1.0 \text{ V}$ $T_A = 25^{\circ} \text{ C}$ |                       |      | 15                    | %     |

# **Table 6. AC Characteristics**

# $V_{DD}$ = 3.0 V, -40° C < $T_A$ < 85° C, unless otherwise specified

| Symbol            | Parameter                                                               | Conditions                                  | Min | Max  | Units  |

|-------------------|-------------------------------------------------------------------------|---------------------------------------------|-----|------|--------|

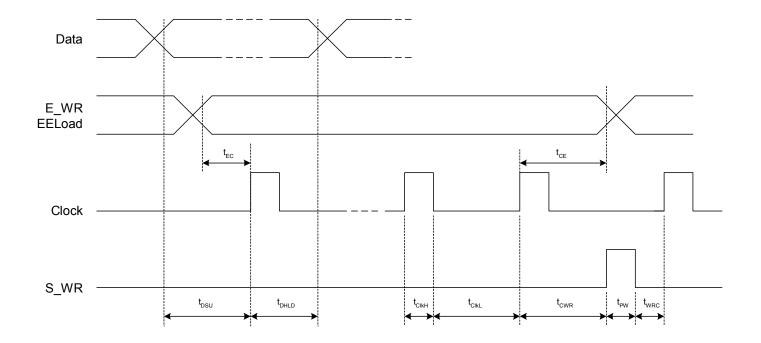

| Control Interface | e and Registers (see Figure 4)                                          |                                             |     |      |        |

| f <sub>Clk</sub>  | Serial data clock frequency                                             | (Note 1)                                    |     | 10   | MHz    |

| t <sub>ClkH</sub> | Serial clock HIGH time                                                  |                                             | 30  |      | ns     |

| t <sub>ClkL</sub> | Serial clock LOW time                                                   |                                             | 30  |      | ns     |

| t <sub>DSU</sub>  | Data set-up time to Clock rising edge                                   |                                             | 10  |      | ns     |

| t <sub>DHLD</sub> | Data hold time after Clock rising edge                                  |                                             | 10  |      | ns     |

| t <sub>PW</sub>   | S_WR pulse width                                                        |                                             | 30  |      | ns     |

| t <sub>CWR</sub>  | Clock rising edge to S_WR rising edge                                   |                                             | 30  |      | ns     |

| t <sub>CE</sub>   | Clock falling edge to E_WR transition                                   |                                             | 30  |      | ns     |

| t <sub>WRC</sub>  | S_WR falling edge to Clock rising edge                                  |                                             | 30  |      | ns     |

| t <sub>EC</sub>   | E_WR transition to Clock rising edge                                    |                                             | 30  |      | ns     |

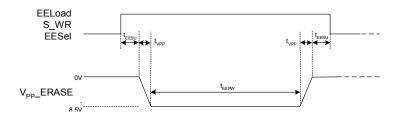

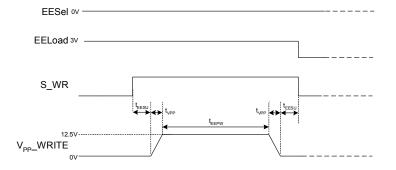

| EEPROM Erase      | e/Write Programming (see Figures 5 & 6)                                 |                                             |     |      |        |

| t <sub>EESU</sub> | EELoad rising edge to V <sub>PP</sub> rising edge                       |                                             | 500 |      | ns     |

| t <sub>EEPW</sub> | V <sub>PP</sub> pulse width                                             |                                             | 25  | 30   | ms     |

| $t_{VPP}$         | V <sub>PP</sub> pulse rise and fall times                               | (Note 2)                                    | 1   |      | μs     |

| Main Divider (In  | cluding Prescaler)                                                      |                                             |     |      |        |

| F <sub>In</sub>   | Operating frequency                                                     |                                             | 300 | 2700 | MHz    |

| F <sub>In</sub>   | Operating frequency                                                     | Speed-grade option (Note 3)                 | 300 | 3000 | MHz    |

| P <sub>FIn</sub>  | Input level range                                                       | External AC coupling                        | -5  | 5    | dBm    |

| Main Divider (Pi  | rescaler Bypassed)                                                      |                                             |     |      |        |

| F <sub>In</sub>   | Operating frequency                                                     | (Note 4)                                    | 50  | 270  | MHz    |

| P <sub>FIn</sub>  | Input level range                                                       | External AC coupling (Note 4)               | -5  | 5    | dBm    |

| Reference Divid   | ler                                                                     |                                             |     |      |        |

| f <sub>r</sub>    | Operating frequency                                                     | (Note 5)                                    |     | 100  | MHz    |

| P <sub>fr</sub>   | Reference input power (Note 4)                                          | Single ended input                          | -2  |      | dBm    |

| Phase Detector    |                                                                         |                                             |     | •    | •      |

| f <sub>c</sub>    | Comparison frequency                                                    | (Note 6)                                    |     | 20   | MHz    |

| SSB Phase Noi     | se ( $F_{in}$ = 1.3 GHz, $f_r$ = 10 MHz, $f_c$ = 1.25 MHz, LBW = 70 kHz | Hz, V <sub>DD</sub> = 3.0 V, Temp = -40° C) |     | •    | •      |

|                   | 100 Hz Offset                                                           |                                             |     | -75  | dBc/Hz |

|                   | 1 kHz Offset                                                            |                                             |     | -85  | dBc/Hz |

- Note 1: f<sub>Cik</sub> is verified during the functional pattern test. Serial programming sections of the functional pattern are clocked at 10 MHz to verify f<sub>Cik</sub> specification.

- Note 2: Rise and fall times of the V<sub>PP</sub> programming voltage pulse must be greater than 1 µs.

- Note 3: The maximum frequency of operation can be extended to 3.0 GHz by ordering a special speed-grade option. Please refer to Table 14, Ordering Information, for ordering details.

- Note 4: CMOS logic levels can be used to drive F<sub>In</sub> input if DC coupled and used in Prescaler Bypass mode. Voltage input needs to be a minimum of 0.5 Vp-p. For optimum phase noise performance, the reference input falling edge rate should be faster than 80 mV/ns. No minimum frequency limit exists when operated in this mode.

- CMOS logic levels can be used to drive reference input if DC coupled. Voltage input needs to be a minimum of 0.5 Vp-p. For optimum Note 5: phase noise performance, the reference input falling edge rate should be faster than 80 mV/ns.

- Note 6: Parameter is guaranteed through characterization only and is not tested.

# **Functional Description**

The PE3341 consists of a dual modulus prescaler, three programmable counters, a phase detector with charge pump and control logic with EEPROM memory (see Figure 1).

The dual modulus prescaler divides the VCO frequency by either 10 or 11, depending on the state of the internal modulus select logic. The R and M counters divide the reference and prescaler outputs by integer values stored in one of three selectable registers. The modulus select logic uses the 4-bit A counter.

The phase-frequency detector generates up and down frequency control signals that direct the charge pump operation, and are also used to enable a lock detect circuit.

Frequency control data is loaded into the device via the Serial Data Port, and can be placed in three separate frequency registers. One of these registers (EE register) is used to load from and write to the non-volatile 20-bit EEPROM.

Various operational and test modes are available through the enhancement register, which is only accessible through the Serial Data Port (it cannot be loaded from the EEPROM).

#### Main Counter Chain

The main counter chain divides the RF input frequency, F<sub>in</sub>, by an integer derived from the user-defined values in the M and A counters. It operates in two modes:

# High Frequency Mode

Setting PB (prescaler bypass) LOW enables the ÷10/11 prescaler, providing operation to 2.7 GHz. In this mode, the output from the main counter chain, f<sub>p</sub>, is related to the VCO frequency, F<sub>in</sub>, by the following equation:

$$f_p = F_{in} / [10 \text{ x } (M+1) + A]$$

(1)

where  $0 \le A \le 15$  and  $A \le M+1$ ;  $1 \le M \le 511$

When the loop is locked, F<sub>in</sub> is related to the reference frequency, f<sub>r</sub>, by the following equation:

$$F_{in} = [10 \text{ x } (M+1) + A] \text{ x } (f_r/(R+1))$$

(2)

where  $0 \le A \le 15$  and  $A \le M+1$ ;  $1 \le M \le 511$

A consequence of the upper limit on A is that F<sub>in</sub> must be greater than or equal to 90 x ( $f_r$  / (R+1)) to obtain contiguous channels. Programming the M counter with the minimum value of 1 will result in a minimum M counter divide ratio of 2.

Programming the M and A counters with their maximum values provides a divide ratio of 5135.

## Prescaler Bypass Mode

Setting the PB bit of a frequency register HIGH allows  $F_{in}$  to bypass the  $\div 10/11$  prescaler. In this mode, the prescaler and A counter are powered down, and the input VCO frequency is divided by the M counter directly. The following equation relates F<sub>in</sub> to the reference frequency f<sub>r</sub>:

$$F_{in} = (M + 1) \times (f_r / (R+1))$$

(3)

where  $1 \le M \le 511$

#### **Reference Counter**

The reference counter chain divides the reference frequency, f<sub>r</sub>, down to the phase detector comparison frequency, f<sub>c</sub>.

The output frequency of the 6-bit R Counter is related to the reference frequency by the following equation:

$$f_c = f_r / (R + 1)$$

(4) where  $0 \le R \le 63$

Note that programming R with 0 will pass the reference frequency, f<sub>r</sub>, directly to the phase detector.

### Phase Detector and Charge Pump

The phase detector is triggered by rising edges from the main counter (f<sub>p</sub>) and the reference counter (f<sub>c</sub>). It has two outputs, PD\_U, and PD\_D. If the divided VCO leads the divided reference in phase or frequency (f<sub>p</sub> leads f<sub>c</sub>), PD\_D pulses LOW. If the divided reference leads the divided VCO in phase or frequency (f<sub>c</sub> leads f<sub>p</sub>), PD\_U pulses LOW. The width of either pulse is directly proportional to the phase offset between the fo and f<sub>c</sub> signals.

The signals from the phase detector are also routed to an internal charge pump. PD\_U controls a current source at pin CP, and PD\_D controls a current sink at pin CP. When using a positive Kv VCO, PD U pulses (current source) will increase the VCO frequency, and PD D pulses (current sink) will decrease VCO frequency.

# **Lock Detect Output**

A lock detect signal is provided at pin LD, via the pin C<sub>EXT</sub> (see Figure 1). C<sub>EXT</sub> is the logical "NAND" of PD\_U and PD\_D waveforms, driven through a series 2k ohm resistor. When the loop is locked, this output will be HIGH with narrow pulses LOW. Connecting C<sub>EXT</sub> to an external shunt capacitor provides integration of this signal.

The  $C_{EXT}$  signal is sent to the LD pin through an internal inverting comparator with an open drain output. Thus LD is an "AND" function of PD\_U and PD D.

Table 7. Serial Interface

| S_WR | E_WR | EELoad | Register Loaded      |

|------|------|--------|----------------------|

| 0    | 0    | 0      | Primary Register     |

| 0    | 1    | 0      | Enhancement Register |

| 0    | Х    | 1      | EE Register          |

## **Serial Data Port**

The Serial Data Port allows control data to be entered into the device. This data can be directed into one of three registers: the Enhancement register, the Primary register, and the EE register. Table 7 defines the control line settings required to select one of these destinations.

Input data presented on pin 5 (Data) is clocked serially into the designated register on the rising edge of Clock. Data is always loaded LSB (B<sub>0</sub>) first into the receiving register. Figure 4 defines the timing requirements for this process.

Figure 4. Serial Interface Timing Diagram

# **Frequency Registers**

There are three independent frequency registers, any one of which can be selected to control the operation of the device. Each register is 20 bits in length, and provides data to the three counters and the prescaler bypass control. Table 8 defines these bit assignments.

# Primary Register

The Primary Register is a serial shift register, loaded through the Serial Data Port. It can be selected to control the PLL as shown in Table 9. It is not buffered, thus when this register is selected to control the PLL, its data is continuously presented to the counters during a load operation.

This register is also used to perform a parallel load of data into the Secondary Register.

# Secondary Register

The Secondary Register is a parallel-load register. Data is copied into this register from the Primary Register on the rising edge of S\_WR, according to the timing diagrams shown in Figure 3. It can be selected to control the PLL as shown in Table 9.

# EE Register

The EE Register is a serial/parallel-in, serial/ parallel-out register, and provides the interface to the EEPROM. It is loaded from the Serial Data Port to provide the parallel data source when writing to the EEPROM. It also accepts stored data from the EEPROM for controlling the PLL.

Serial loading of the EE Register is done as shown in Table 7 and Figure 4. Parallel loading of the register from EEPROM is accomplished as shown in Table 10.

The EE register can be selected to control the PLL as shown in Table 9. Note that it cannot be selected to control the PLL using data that has been loaded serially. This is because it must first go through one of the two conditions in Table 10 that causes the EEPROM data to be copied into the EE Register. The effect of this is that only EEPROM data is used when the EE Register is selected.

The contents of the EE register can also be shifted out serially through the Dout pin. This mode is enabled by appropriately programming the Enhancement Register. In this mode, data exits the register on the rising edge of Clock, LSB (B<sub>0</sub>) first, and is replaced with the data present on the Data input pin. Tables 7 and 12 define the settings required to enable this mode.

Table 8. Primary / Secondary / EE Register Bit Assignments

| R <sub>5</sub> | R <sub>4</sub> | M <sub>8</sub> | M <sub>7</sub> | РВ    | M <sub>6</sub> | <b>M</b> <sub>5</sub> | M <sub>4</sub> | M <sub>3</sub> | M <sub>2</sub> | M <sub>1</sub>  | Mo              | R <sub>3</sub>  | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | $A_3$           | A <sub>2</sub>  | <b>A</b> <sub>1</sub> | A <sub>0</sub>  |

|----------------|----------------|----------------|----------------|-------|----------------|-----------------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------|-----------------|

| B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | $B_4$ | B <sub>5</sub> | B <sub>6</sub>        | B <sub>7</sub> | B <sub>8</sub> | $B_9$          | B <sub>10</sub> | B <sub>11</sub> | B <sub>12</sub> | B <sub>13</sub> | B <sub>14</sub> | B <sub>15</sub> | B <sub>16</sub> | B <sub>17</sub> | B <sub>18</sub>       | B <sub>19</sub> |

Table 9. Frequency Register Selection

| EESel | FSel | EELoad | Register Selected  |

|-------|------|--------|--------------------|

| 0     | 1    | 0      | Primary Register   |

| 0     | 0    | 0      | Secondary Register |

| 1     | Х    | 0      | EE Register        |

Table 10. EE Register Load from EEPROM

| EESel | EELoad | Function             |

|-------|--------|----------------------|

| _/ -  | 0      | EEPROM → EE Register |

| 1     | ~_     | EEPROM → EE Register |

# **Enhancement Register**

The Enhancement Register is a buffered serial shift register, loaded from the Serial Data Port. It activates special test and operating modes in the PLL. The bit assignments for these modes are shown in Table 11.

The functions of these Enhancement Register bits are shown in Table 12. A function becomes active when its corresponding bit is set HIGH. Note that bits 1, 2, 5, and 6 direct various data to the Dout pin, and for valid operation no more than one should be set HIGH simultaneously.

The Enhancement Register is buffered to prevent inadvertent control changes during serial loading. Data that has been loaded into the register is captured in the buffer and made available to the PLL on the falling edge of E WR.

A separate control line is provided to enable and disable the Enhancement mode. Functions are enabled by taking the ENH control line LOW. Note: The enhancement register bit values are unknown during power up. To avoid enabling the enhancement mode during power up, set the Enh pin high ("1") until the enhancement register bit values are programmed to a known state.

Table 11. Enhancement Register Bit Assignments

| Reserved       | EE Register<br>Output | f <sub>p</sub> output | Power<br>down | Counter<br>load | MSEL<br>output | f <sub>c</sub> output | Reserved       |

|----------------|-----------------------|-----------------------|---------------|-----------------|----------------|-----------------------|----------------|

| B <sub>0</sub> | B <sub>1</sub>        | $B_2$                 | $B_3$         | $B_4$           | $B_{5}$        | $B_6$                 | B <sub>7</sub> |

Table 12. Enhancement Register Functions

| Bit Function |                       | Description                                                                                                                                   |  |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit 0        | Reserved              | Program to 0                                                                                                                                  |  |

| Bit 1        | EE Register Output    | Allows the contents of the EE Register to be serially shifted out Dout, LSB (B <sub>0</sub> ) first. Data is shifted on rising edge of Clock. |  |

| Bit 2        | f <sub>p</sub> output | Provides the M counter output at Dout.                                                                                                        |  |

| Bit 3        | Power down            | Powers down all functions except programming interface.                                                                                       |  |

| Bit 4        | Counter load          | Immediate and continuous load of counter programming.                                                                                         |  |

| Bit 5        | MSEL output           | Provides the internal dual modulus prescaler modulus select (MSEL) at Dout.                                                                   |  |

| Bit 6        | f <sub>c</sub> output | Provides the R counter output at Dout.                                                                                                        |  |

| Bit 7        | Reserved              | Program to 0                                                                                                                                  |  |

# **EEPROM Programming**

Frequency control data that is present in the EE Register can be written to the non-volatile EEPROM. All 20 bits are written simultaneously in a parallel operation. The EEPROM is guaranteed for at least 100 erase/write cycles.

## Erase Cycle

The EEPROM should be taken through an erase cycle before writing data, since the write operation performs a logical AND of the EEPROM's current contents with the data in the EE Register. Erasing the EEPROM is accomplished by holding the S\_WR, EESel, and EELoad inputs HIGH, then applying one ERASE programming voltage pulse to the  $V_{PP}$  input (see Table 13). The voltage source for this operation must be capable of supplying the EEPROM erase cycle current ( $I_{PP}$ \_ERASE, Table 5). The timing diagram is shown in Figure 5.

**Table 13. EEPROM Programming**

| S_WR | EESel | EELoad | $V_{PP}$      | Function    |

|------|-------|--------|---------------|-------------|

| 1    | 1     | 1      | 25ms @ -8.5V  | Erase cycle |

| 1    | 0     | 1      | 25ms @ +12.5V | Write cycle |

Figure 5. EEPROM Erase Timing Diagram

Figure 6. EEPROM Write Timing Diagram

# Write Cycle

Using the Serial Data Port, the EE Register is first loaded with the desired data. The EEPROM is then programmed with this data by taking the S\_WR input HIGH and EESel input LOW, then applying one WRITE programming voltage pulse to the V<sub>PP</sub> input. The voltage source for this operation must be capable of supplying the EEPROM write cycle current (I<sub>PP</sub>\_WRITE, Table 5). The timing diagram of this operation is shown in Figure 6. Programming is completed by taking the EELoad input LOW.

Note that it is possible to erroneously overwrite the EE Register with the EEPROM contents before the write cycle begins by unneeded manipulation of the EELoad bit (see Table 10).

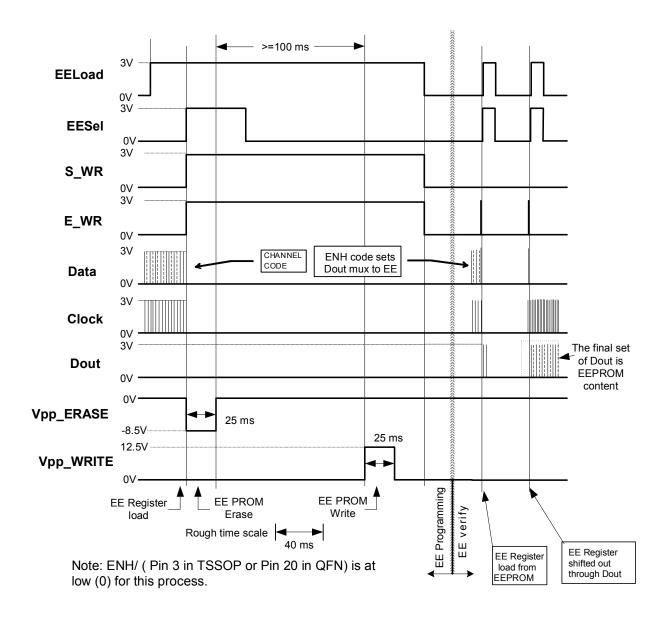

# **Gross EEPROM Programming Timing Grid**

Figure 7 shows a gross PE3341 EEPROM programming timing grid although each individual step has been described thoroughly in previous sections. It starts with EE Register load, and then together with other parameters a Vpp\_ERASE negative pulse is applied to Vpp pin to erase the EEPROM contents and followed by a Vpp\_WRITE pulse for EEPROM write cycle. The separation

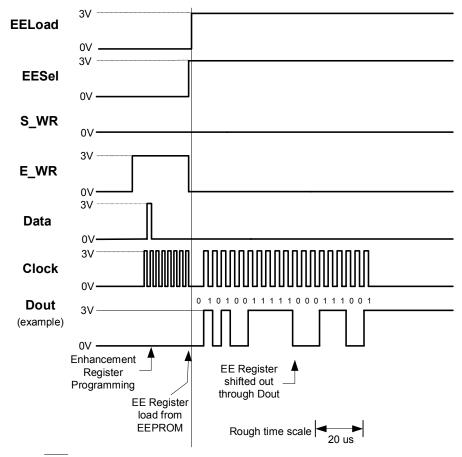

between the Vpp\_ERASE and Vpp\_WRITE pulse has to be at least 100 ms if mechanical relays are used to avoid both being on at the same time. After EE programming, the contents of the EEPROM cells can be verified by setting Enhancement Register Bit 1. A procedure shown in Figure 8 is applied twice. The first time is to load the EE Register from EEPROM and the second time is to shift out the EE Register contents through Dout pin.

Figure 7. Gross PE3341 EEPROM Programming Timing Grid

Figure 8. Details of EE register contents loaded from EEPROM and then shifted out Serially through Dout pin - The procedure is performed twice.

Note: ENH/ (Pin 3 in TSSOP or Pin 20 in QFN) is at low (0) for this process.

In Figure 8, the first step is to program Enhancement Register to set Bit 1 high ("1") to access EE Register Output Bit Function. Subsequent action, which includes pulses, allows the existing EE Register contents to be shifted out the Dout pin and the EEPROM contents are loaded to the EE Register. Since the initial data existing in the EE Register could be anything, the data must be flushed out before clocking the

contents of the EEPROM register out. After the same procedures are duplicated, the Dout output is the EEPROM content. Note that only 19 Clock pulses are enough for the 20-bit EE Register because the first bit data is already present at Dout pin. Also ENH/ (Pin 3 in TSSOP or Pin 20 in QFN) is set to low ("0") to access the Enhancement mode.

# **Application Information**

The PE3341 has been designed to allow a selfstarting PLL synthesizer to be built, removing the need to have a micro-controller or other programming source load data into the device on power-up. It can be used as a remotely controllable PLL as well, since the EEPROM circuitry has been added to a complete PLL core (PE3339).

The PE3341's EEPROM can be programmed incircuit, or prior to assembly using a socketed fixture.

It can be reprogrammed a minimum of 100 times, but is not designed to support constant reprogramming of the EEPROM by an application.

## Self-Starting Mode

In self-starting applications, the EE Register is used to control the device and must be selected per Table 9. Additionally, the contents of the EEPROM must be copied to the EE Register per Table 10, and device power must be stable for this transfer to be reliably accomplished. These requirements can be met by connecting a capacitor of 50pF-10uF (evaluation design uses 3.3uF) from the EESel pin to ground. The delay of the rising edge on EESel, created by the RC time constant of its 70k ohm internal pull-up resistor and the external capacitor, will allow device power to stabilize first, ensuring proper data transfer. This edge is adaptable by capacitor value selection. The Vcc applied to the IC must be settled first.

# **Evaluation and Programming Kit Support**

To provide easy evaluation of the PE3341 and to also enable programming of small evaluation quantities, Peregrine has developed complete evaluation kits and programming kits for the PE3341 EEPROM PLLs.

### Evaluation Kits

The evaluation kits consist of an evaluation board and support software enabling the user to evaluate the full functionality of the part. The EEPROM can be loaded with user specified values and then placed in a self start-up mode. Please refer to Table 14, Ordering Information, for the specific order codes.

# Programming Kits

The programming kits consist of a programming board and support software that enables the user to program small quantities of devices for prototype evaluation and for small pre-production runs. Please refer to Table 14, Ordering Information, for the specific order codes

Large production quantities can be special programmed at Peregrine for an additional charge. Please contact Peregrine Sales for pricing and leadtime at sales@psemi.com.

# Figure 9. Package Drawing

24-lead TSSOP

# Figure 10. Package Drawing

20-lead QFN

- 1. DIMENSION APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 FROM TERMINAL TIP.

- 2. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

# **Table 14. Ordering Information**

| Order Code | Part Marking | Description                        | Package           | Shipping Method  |

|------------|--------------|------------------------------------|-------------------|------------------|

| 3341-01    | PE3341       | PE3341-24TSSOP-62A                 | 24-lead TSSOP     | 62 units / Tube  |

| 3341-02    | PE3341       | PE3341-24TSSOP-2000C               | 24-lead TSSOP     | 2000 units / T&R |

| 3341-03    | PE3341       | PE3341-20QFN4x4-92A                | 20-lead QFN       | 92 units / Tube  |

| 3341-04    | PE3341       | PE3341-20QFN4x4-3000C              | 20-lead QFN       | 3000 units / T&R |

| 3341-53    | PE3341       | PE3341G-20QFN4x4-92A               | Green 20-lead QFN | 92 units / Tube  |

| 3341-54    | PE3341       | PE3341G-20QFN4x4-3000C             | Green 20-lead QFN | 3000 units / T&R |

| 3341-31    | PE3341       | PE3341-24TSSOP-62A (3GHz grade)    | 24-lead TSSOP     | 62 units / Tube  |

| 3341-32    | PE3341       | PE3341-24TSSOP-2000C (3GHz grade)  | 24-lead TSSOP     | 2000 units / T&R |

| 3341-33    | PE3341       | PE3341-20QFN4x4-92A (3GHz grade)   | 20-lead QFN       | 92 units / Tube  |

| 3341-34    | PE3341       | PE3341-20QFN4x4-3000C (3GHz grade) | 20-lead QFN       | 3000 units / T&R |

| 3341-00    | PE3341-EK    | PE3341-24TSSOP-EK (TSSOP)          | Evaluation Kit    | 1 / Box          |

| 3341-05    | PE3341-EK    | PE3341-20QFN4x4-EK (QFN)           | Evaluation Kit    | 1 / Box          |

| 3341-06    | PE3341-PK    | PE3341-24TSSOP-PK (TSSOP)          | Programming Kit   | 1 / Box          |

| 3341-07    | PE3341-PK    | PE3341-20MLP4x4-PK (QFN)           | Programming Kit   | 1 / Box          |

# Sales Offices

#### The Americas

## **Peregrine Semiconductor Corporation**

9450 Carroll Park Drive San Diego, CA 92121 Tel 858-731-9400 Fax 858-731-9499

## Europe

# **Peregrine Semiconductor Europe**

Bâtiment Maine 13-15 rue des Quatre Vents F- 92380 Garches, France Tel: +33-1-47-41-91-73 Fax: +33-1-47-41-91-73

# **Space and Defense Products**

#### Americas:

Tel: 505-881-0438 Fax: 505-881-0443 Europe, Asia Pacific:

180 Rue Jean de Guiramand 13852 Aix-En-Provence cedex 3, France

Tel: +33(0) 4 4239 3361 Fax: +33(0) 4 4239 7227

#### North Asia Pacific

## Peregrine Semiconductor K.K.

5A-5, 5F Imperial Tower 1-1-1 Uchisaiwaicho, Chiyoda-ku Tokyo 100-0011 Japan Tel: +81-3-3502-5211

Fax: +81-3-3502-5213

## Peregrine Semiconductor, Korea

#B-2402, Kolon Tripolis, #210 Geumgok-dong, Bundang-gu, Seongnam-si Gyeonggi-do, 463-480 S. Korea

Tel: +82-31-728-4300 Fax: +82-31-728-4305

## South Asia Pacific

## Peregrine Semiconductor, China

Shanghai, 200040, P.R. China Tel: +86-21-5836-8276

Fax: +86-21-5836-7652

For a list of representatives in your area, please refer to our Web site at: www.psemi.com

# Data Sheet Identification

## Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

# **Preliminary Specification**

The data sheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

### Product Specification

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a DCN (Document Change Notice).

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, and UTSi are registered trademarks and UltraCMOS and HaRP are trademarks of Peregrine Semiconductor Corp.