# NTE7132 Integrated Circuit Horizontal and Vertical Deflection Controller for VGA/XGA and Multi–Frequency Monitors

#### **Description:**

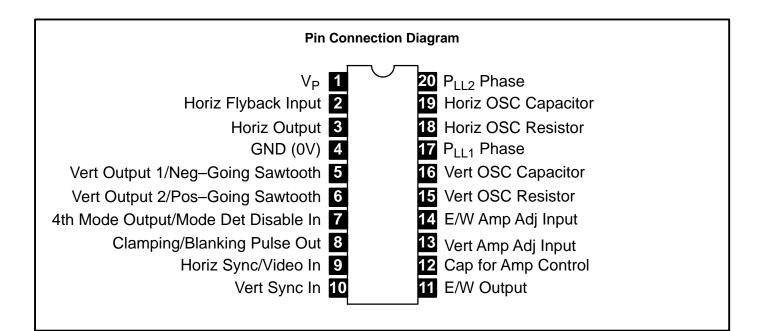

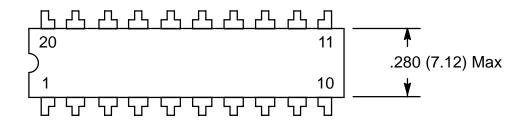

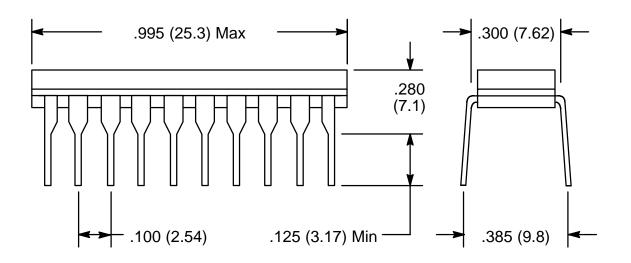

The NTE7132 is an integrated circuit in a 20–Lead DIP type package. This device is designed to provide an economical solution in VGA/XGA and multifrequency monitors by incorporating complete horizontal and vertical small signal processing. VGA–dependent mode detection and setting are performed on–chip.

#### Features:

- VGA Operation Fully Implemented Including Alignment

—Free Vertical and E/W Amplitude Pre—Settings

- 4th VGA Mode Easy Applicable (XGA, Super VGA)

- Mulit-Frequency Operation Externally Selectable

- All Adjustments DC–Controllable

- Alignment–Free Oscillators

- Sync Separators for Video or Horizontal and Vertical TTL Sync Levels Regardless or Polarity

- Horizontal Oscillator with P<sub>LL1</sub> for Sync and P<sub>LL2</sub> for Flyback

- Constant Vertical and E/W Amplitude in Multi–Frequency Operation

- Internal Supply Voltage Stabilization with Excellent Ripple Rejection to Ensure Stable Geometrical Adjustments

#### **Absolute Maximum Ratings:**

| Supply Voltage (Pin1), V <sub>P</sub>                                    | 0.5 to +16V    |

|--------------------------------------------------------------------------|----------------|

| Voltage (Pin3, Pin7), V <sub>3</sub> , V <sub>7</sub>                    | 0.5 to +16V    |

| Voltage (Pin8), V <sub>8</sub>                                           | 0.5 to +7V     |

| Voltage (Pin5, Pin6, Pin9, Pin10, Pin13, Pin14, Pin18), V <sub>n</sub>   | 0.5 to +6.5V   |

| Current (Pin2), I <sub>2</sub>                                           | ±10mA          |

| Current (Pin3), I <sub>3</sub>                                           | 100mA          |

| Current (Pin7), I <sub>7</sub>                                           | 20mA           |

| Current (Pin8), I <sub>8</sub>                                           | –10mA          |

| Electrostatic Handling for All Pins (Note 1), V <sub>esd</sub>           | ±300V          |

| Operating Junction Temperature, T <sub>J</sub>                           | +150°C         |

| Operating Ambient Temperatrure Range, T <sub>A</sub>                     | 0° to +70°C    |

| Storage Temperature Range, T <sub>stq</sub>                              | –55° to +150°C |

| Thermal Resistance, Junction-to-Ambient (In Free Air), R <sub>thJA</sub> |                |

|                                                                          |                |

Note 1. Equivalent to discharging a 200pF capacitor through a  $0\Omega$  series resistor.

## Electrical Characteristics: $(V_P = 12V, T_A = +25^{\circ}C)$ unless otherwise specified)

| Parameter                                                                                            | Symbol                           | Test Conditions                                      | Min | Тур   | Max            | Unit                |  |

|------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------|-----|-------|----------------|---------------------|--|

| Supply                                                                                               |                                  |                                                      |     |       |                |                     |  |

| Supply Voltage (Pin1)                                                                                | $V_{P}$                          |                                                      | 9.2 | 12.0  | 16.0           | V                   |  |

| Supply Current                                                                                       | l <sub>P</sub>                   |                                                      | -   | 40    | -              | mA                  |  |

| Internal Reference Voltage                                                                           | •                                |                                                      |     |       |                |                     |  |

| Internal Reference Voltage                                                                           | V <sub>ref</sub>                 |                                                      | 6.0 | 6.25  | 6.5            | V                   |  |

| Temperature Coefficient                                                                              | TC                               | $T_A = +20^{\circ} \text{ to } +100^{\circ}\text{C}$ | _   | -     | ±90            | 10 <sup>-6</sup> /K |  |

| Power Supply Ripple Rejection                                                                        | PSRR                             | f = 1kHz Sine Wave                                   | 60  | 75    | _              | dB                  |  |

|                                                                                                      |                                  | f = 1MHz Sine Wave                                   | 25  | 35    | _              | dB                  |  |

| Supply Voltage (Pin1) to Ensure All Internal<br>Reference Voltages                                   | V <sub>P</sub>                   |                                                      | 9.2 | _     | 16.0           | V                   |  |

| Composite Sync Input (AC-Coupled, V <sub>10</sub> = 5\                                               | <b>V</b> )                       |                                                      |     |       |                |                     |  |

| Sync Amplitude of Video Input Signal (Pin9)                                                          | V <sub>i sync</sub>              | Sync on Green, $R_S = 50\Omega$                      | _   | 300   | _              | mV                  |  |

| Top Sync Clamping Level                                                                              | 1                                |                                                      | 1.1 | 1.32  | 1.5            | V                   |  |

| Slicing Level Above Top Sync Level                                                                   | 1                                |                                                      | 90  | 120   | 150            | mV                  |  |

| Allowed Source Resistance for 7% Duty Cycle                                                          | R <sub>S</sub>                   | V <sub>i sync</sub> > 200mV                          | _   | _     | 1.5            | kΩ                  |  |

| Differential Input Resistance                                                                        | r <sub>9</sub>                   | During Sync                                          | _   | 80    | _              | Ω                   |  |

| Charging Current of Coupling Capacitor                                                               | l <sub>9</sub>                   | V <sub>9</sub> > 1.5V                                | 1.7 | 2.6   | 3.4            | μΑ                  |  |

| Vertical Sync Integration Time to Generate Sync Pulse                                                | t <sub>int</sub>                 |                                                      | 7   | 10    | 13             | μs                  |  |

| Horizontal Sync Input (DC-Coupled, TTL-Cor                                                           | mpatible)                        |                                                      |     |       |                |                     |  |

| Sync Input Signal (Peak Value, Pin9)                                                                 | V <sub>u sync</sub>              |                                                      | 1.7 | _     | _              | V                   |  |

| Slicing Level                                                                                        | 1                                |                                                      | 1.2 | 1.4   | 1.6            | V                   |  |

| Minimum Pulse Width                                                                                  | t <sub>p</sub>                   |                                                      | 700 | _     | _              | ns                  |  |

| Rise Time and Fall Time                                                                              | t <sub>r</sub> , t <sub>f</sub>  |                                                      | 10  | _     | 500            | ns                  |  |

| Input Current                                                                                        | lg                               | V <sub>9</sub> = 0.8V                                | _   | _     | -200           | μΑ                  |  |

|                                                                                                      |                                  | V <sub>9</sub> 5.5V                                  | _   | _     | 10             | μΑ                  |  |

| Automatic Horizontal Polarity Switch (H–Syn                                                          | nc on Pin9)                      |                                                      |     |       |                | <u> </u>            |  |

| Horizontal Sync Pulse Width Related to t <sub>H</sub> (Duty Cycle for Automatic Polarity Correction) | t <sub>p H</sub> /t <sub>H</sub> |                                                      | _   | _     | 30             | %                   |  |

| Delay Time for Changing Sync Polarity                                                                | t <sub>p</sub>                   |                                                      | 0.3 | _     | 1.8            | ms                  |  |

| Vertical Sync Input (DC-Coupled, TTL-Compa                                                           |                                  | Sync on Pin10)                                       |     | I     |                |                     |  |

| Sync Input Signal (Peak Value, Pin10)                                                                | V <sub>i sync</sub>              |                                                      | 1.7 | _     | _              | V                   |  |

| Slicing Level                                                                                        |                                  |                                                      | 1.2 | 1.4   | 1.6            | V                   |  |

| Input Current                                                                                        | I <sub>10</sub>                  | 0 < V <sub>10</sub> < 5.5V                           | _   | _     | ±10            | μΑ                  |  |

| Maximum Vertical Sync Pulse Width for<br>Automatic Vertical Polarity Switch                          | t <sub>p V</sub>                 |                                                      | _   | _     | 300            | μs                  |  |

| Horizontal Mode Detector Output (VGA Mode)                                                           |                                  |                                                      |     |       |                |                     |  |

| Output Saturation Voltage LOW<br>(For Modes 1, 2, and 3)                                             | V <sub>7</sub>                   | I <sub>7</sub> = 6mA                                 | _   | 0.275 | 0.33           | V                   |  |

| Output Voltage HIGH                                                                                  | 1                                | Mode 4                                               | _   | _     | V <sub>P</sub> | V                   |  |

| Load Current to Force VGA Mode–Dependent Vertical and Parabola Amplitudes                            | I <sub>7</sub>                   | Modes 1, 2, and 3                                    | 2   | _     | 6              | mA                  |  |

| 4                                                                                                    |                                  |                                                      |     |       | ı              |                     |  |

## **<u>Electrical Characteristics (Cont'd):</u>** $(V_P = 12V, T_A = +25^{\circ}C \text{ unless otherwise specified})$

| Parameter                                                                      | Symbol                         | Test Conditions                                                            | Min          | Тур     | Max   | Unit                |  |

|--------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------|--------------|---------|-------|---------------------|--|

| VGA/Multi-Frequency Mode Switch                                                |                                |                                                                            |              |         |       |                     |  |

| Input Voltage LOW to Force Multi–Frequency Mode                                | V <sub>7</sub>                 |                                                                            | 0            | -       | 50    | mV                  |  |

| Horizontal Comparator P <sub>LL1</sub>                                         | <u>.</u>                       |                                                                            |              |         |       |                     |  |

| Upper Control Voltage Limitation                                               | V <sub>17</sub>                |                                                                            | _            | 5.0     | _     | V                   |  |

| Lower Control Voltage Limitation                                               | 1                              |                                                                            | -            | 1.2     | _     | V                   |  |

| Control Current                                                                | I <sub>17</sub>                |                                                                            | -            | ±300    | _     | μА                  |  |

| Horizontal Oscillator                                                          | •                              |                                                                            | •            |         |       | •                   |  |

| Center Frequency                                                               | fosc                           | $R_{18} = 12k\Omega \text{ (Pin18)},$<br>$C_{19} = 2.2nF \text{ (Pin19)}$  | -            | 31.45   | _     | kHz                 |  |

| Deviation of Center Frequency                                                  | $\Delta f_{OSC}$               |                                                                            | _            | -       | ±3.0  | %                   |  |

| Temperature Coefficient                                                        | TC                             |                                                                            | _            | _       | ±150  | 10 <sup>-6</sup> /K |  |

| Relative Holding/Catching Range                                                | φ <sub>H</sub> /t <sub>H</sub> |                                                                            | ±6.0         | ±6.5    | ±7.3  | %                   |  |

| External Oscillator Resistor                                                   | R <sub>18</sub>                |                                                                            | 9            | _       | 18    | kΩ                  |  |

| Voltage at Reference Current Input (Pin18)                                     | V <sub>18</sub>                | P <sub>LL1</sub> and P <sub>LL2</sub> Locked,<br>V <sub>ref</sub> m= 6.25V | _            | 3.125   | _     | V                   |  |

| Control Voltage                                                                | ΔV <sub>18</sub>               |                                                                            | <b>—</b>     | ±205    | _     | mV                  |  |

| Horizontal P <sub>LL2</sub>                                                    |                                |                                                                            |              |         |       |                     |  |

| Upper Clamping Level of Flyback Input                                          | V <sub>2</sub>                 | $I_2 = 6mA$                                                                | _            | 5.5     | _     | V                   |  |

| Lower Clamping Level of Flyback Input                                          | 1                              | $I_2 = -1 \text{mA}$                                                       | <b>—</b>     | -0.75   | _     | V                   |  |

| H–Flyback Slicing Level                                                        | 7                              |                                                                            | _            | 3.0     | _     | V                   |  |

| Input Current                                                                  | l <sub>2</sub>                 | H-Scan; V <sub>8</sub> < 0.9V                                              | -0.5         | _       | _     | mA                  |  |

|                                                                                |                                | H–Flyback; V <sub>8</sub> > 1.8V                                           | _            | _       | -0.2  | mA                  |  |

| Delay Between Middle of Sync and Middle of H–Flyback Related to t <sub>H</sub> | t <sub>d</sub> /t <sub>H</sub> |                                                                            | _            | 3.2     | _     | %                   |  |

| Upper Control Voltage Limitation                                               | V <sub>20</sub>                |                                                                            | -            | 4.6     | _     | V                   |  |

| Lower Control Voltage Limitation                                               | 7                              |                                                                            | -            | 1.6     | _     | V                   |  |

| Control Current                                                                | I <sub>20</sub>                |                                                                            | -            | ±200    | _     | μА                  |  |

| P <sub>LL2</sub> Control range Related to t <sub>H</sub>                       | ∆t/t <sub>H</sub>              |                                                                            | 30           | _       | _     | %                   |  |

| Horizontal Output (Open–Collector)                                             |                                |                                                                            |              |         |       |                     |  |

| Output Voltage LOW                                                             | V <sub>3</sub>                 | I <sub>3</sub> = 20mA                                                      |              | _       | 0.3   | V                   |  |

|                                                                                |                                | $I_3 = 60 \text{mA}$                                                       | <b>—</b>     | _       | 0.8   | V                   |  |

| t <sub>H</sub> Duty Cycle                                                      | t <sub>p</sub> /t <sub>H</sub> |                                                                            | 42           | 45      | 48    | %                   |  |

| Threshold to Activate Too Low Supply Voltage                                   | V <sub>P</sub>                 | Horizontal Output OFF                                                      | <b>—</b>     | 5.3     | _     | V                   |  |

| Protection                                                                     |                                | Horizontal Output ON                                                       | _            | 5.6     | _     | V                   |  |

| Horizontal Clamping/Blanking Generator Ou                                      | tput                           |                                                                            |              |         |       | 1                   |  |

| Output Voltage LOW                                                             | V <sub>8</sub>                 | H and V Scanning                                                           | _            | _       | 0.9   | V                   |  |

| Blanking Output Voltage                                                        | 1                              | Internal V Blanking                                                        | 1.8          | 2.1     | 2.4   | V                   |  |

|                                                                                |                                | External H Blanking                                                        | 1.8          | 2.1     | 2.4   | V                   |  |

| Clamping Output Voltage                                                        | 1                              | H–Sync on Pin9                                                             | 3.5          | 3.9     | 4.3   | V                   |  |

| Internal Sink Current for All Output Levels                                    | I <sub>8</sub>                 | H and V Scanning                                                           | 2.3          | 2.9     | 3.5   | mA                  |  |

| Clamping Pulse Start                                                           | t <sub>8</sub>                 |                                                                            | With E       | nd of H | -Sync |                     |  |

| Clamping Pulse Width                                                           | t <sub>clp</sub>               |                                                                            | 0.8          | 1.0     | 1.2   | μs                  |  |

| Steepness of Rise and Fall Times                                               | S                              |                                                                            | <del> </del> | 40      | _     | ns/V                |  |

### <u>Electrical Characteristics (Cont'd)</u>: $(V_P = 12V, T_A = +25^{\circ}C \text{ unless otherwise specified})$

| Parameter                                                                              | Symbol                                              | Test Conditions                                                   | Min   | Тур   | Max   | Unit                |

|----------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|---------------------|

| Vertical Oscillator ( $V_{ref} = 6.25V$ )                                              |                                                     |                                                                   |       |       |       |                     |

| Vertical Free–Running Frequency                                                        | f <sub>o</sub>                                      | $R_{15} = 22k\Omega$ , $C_{16} = 0.1\mu F$                        | 40.0  | 42.0  | 43.3  | Hz                  |

| Nominal Vertical Sync Range                                                            | f <sub>V</sub>                                      | No f <sub>o</sub> Adjustment                                      | 50    | _     | 110   | Hz                  |

| Voltage on Pin15                                                                       |                                                     | $R_{15} = 22k\Omega$                                              | 2.8   | 3.0   | 3.2   | V                   |

| Delay Between Sync Pulse and Start of Vertical Scan in VGA/XGA Mode                    |                                                     | Measured on Pin8,<br>Activated by an External<br>Resistor on Pin7 | 500   | 575   | 650   | μs                  |

| Delay Between Sync Pulse and Start of Vertical Scan in Multi-Frequency Mode            |                                                     | Measured on Pin8,<br>V <sub>7</sub> < 50mV                        | 240   | 300   | 360   | μs                  |

| Control Current for Amplitude Control                                                  | ntrol Current for Amplitude Control I <sub>12</sub> |                                                                   | _     | ±200  | _     | μΑ                  |

| Capacitor for Amplitude Control                                                        | C <sub>12</sub>                                     |                                                                   | _     | _     | 0.33  | μF                  |

| Vertical Differential Output                                                           | •                                                   |                                                                   |       |       | •     | -                   |

| Differential Output Current Between Pin5 and Pin6 (Peak-to-Peak Value)                 | I <sub>o</sub>                                      | Mode 3, $I_{13} > -135\mu A$ , $R_{15} = 22kΩ$                    | 0.9   | 1.0   | 1.1   | mA                  |

| Maximum Offset Current Error                                                           | 1                                                   | $I_0 = 1mA$                                                       | _     | _     | ±2.5  | %                   |

| Maximum Linearity Error                                                                |                                                     |                                                                   | _     | _     | ±1.5  | %                   |

| Vertical Amplitude Adjustment (In Percent of 0                                         | Output Sig                                          | nal)                                                              |       |       |       |                     |

| Input Voltage                                                                          | V <sub>13</sub>                                     |                                                                   | _     | 5.0   | _     | V                   |

| Adjustment Current                                                                     | I <sub>13</sub>                                     | I <sub>o</sub> max (100%)                                         | -110  | -120  | -135  | μΑ                  |

|                                                                                        |                                                     | I <sub>o</sub> min (Typically 58%)                                | _     | 0     | _     | μΑ                  |

| VGA Mode–Dependent Pre–Settings Activated<br>by an External Resistor on Pin7<br>Mode 1 | Δl <sub>o</sub> /Δt                                 | Note 2                                                            | 116.1 | 116.8 | 117.5 | %                   |

| Mode 2                                                                                 | 1                                                   |                                                                   | 102.0 | 102.2 | 102.5 | %                   |

| Mode 3                                                                                 |                                                     |                                                                   | _     | 100   | _     | %                   |

| Mode 4                                                                                 | _                                                   |                                                                   | _     | 100   | _     | %                   |

| Multi–Frequency Operation (VGA Operation Disabled)                                     |                                                     | Note 2, V <sub>7</sub> < 50mV                                     | _     | 100   | -     | %                   |

| E/W Output (Note 2)                                                                    | 1                                                   |                                                                   | 1     |       |       |                     |

| Bottom Output Signal During Mid-Scan (Pin11)                                           | V <sub>11</sub>                                     | Internally Stabilized                                             | 1.05  | 1.2   | 1.35  | V                   |

| Top Output Signal During Flyback                                                       |                                                     |                                                                   | 4.1   | 4.35  | 4.6   | V                   |

| Temperature Coefficient of Output Signal                                               | TC                                                  |                                                                   | _     | _     | 250   | 10 <sup>-6</sup> /K |

| E/W Amplitude Adjustment (Parabola)                                                    |                                                     |                                                                   |       |       |       |                     |

| Input Voltage (Pin14)                                                                  | V <sub>14</sub>                                     |                                                                   | _     | 5.0   | _     | V                   |

| Adjustment Current                                                                     | I <sub>14</sub>                                     | 100% Parabola                                                     | -110  | -120  | -135  | μΑ                  |

|                                                                                        |                                                     | Typicall 28% Parabola                                             | _     | 0     | _     | μΑ                  |

|                                                                                        | _                                                   | -                                                                 |       |       |       |                     |

Note 2.  $\Delta I_0/\Delta t$  relative to value of Mode 3.

Note 3. Parabola amplitude tracks with mode—dependent vertical amplitude but not with vertical amplitude adjustment. Tracking can be achieved by a resistor from vertical amplitude potentiometer to Pin14.

#### **Functional Description:**

#### **Horizontal Sync Separator and Polarity Correction**

An AC–coupled video signal or a DC–coupled TTL sync signal (H only or composite sync) is input on Pin9. Video signals are clamped with top sync on 12.8V, and are sliced at 1.4V. This results in a fixed absolute slicing level of 120mV relative to top sync.

DC-coupled TTL sync signals are also sliced at 1.4V, however with the clamping circuit in current limitation. The polarity of the separated sync is detected by internal integration of the signal, then the polarity is corrected.

The polarity information is fed to the VGA mode detector. The corrected sync is the input signal for the vertical sync integrator and the P<sub>1.1.1</sub> stage.

#### Vertical Sync Separator, Polarity Correction and Vertical Sync Integrator

DC-coupled vertical TTL sync signals may be applied to Pin10. They are sliced at 1.4V. The polarity of the separated sync is detected by internal integration, then polarity is corrected. The polarity information is fed to the VGA mode detector. If Pin10 is not used, it must be connected to GND.

The separated V<sub>i sync</sub> signal from Pin10, or the integrated composite sync signal from Pin9 (TTL or video) directly triggers the vertical oscillator.

#### **VGA Mode Detector and Mode Output**

The three standard VGA modes and a 4th not fixed mode are decoded by the polarities of the horizontal and the vertical sync input signals. An external resistor (from V<sub>P</sub> to Pin7) is necessary to match this function. In all three VGA modes the correxct amplitudes are activated. The presence of the 4th mode is indicated by HIGH on Pin7. This signal can be used externally to switch any horizontal or vertical parameters.

#### **VGA Mode Detector Input**

For multi–frequency operation the voltage on Pin7 must be externally forced to a level of < 50mV. Vertical amplitude pre–settings for VGA are then inhibited. The delay time between vertical trigger pulse and the start of vertical deflection changes from 575 to  $300\mu s$  (575 $\mu s$  is needed for VGA). The vertical amplitude then remains constant in a frequency range from 50 to 110Hz.

#### **Clamping and Blanking Generator**

A combined clamping and blanking pulse is available on Pin8. The lower level of 2.1V can be the blanking signal derived from line flyback, or the vertical blanking pulse from the internal vertical oscillator.

Vertical blanking equals the delay between vertical sync and the start of vertical scan. By this, an optimum blanking is acheived for VGA/XGA as well as for multi–frequency operation (selectable via Pin7).

The upper level of 3.9V is the horizontal clamping pulse with internally fixed pulse width of 1µs. A mono flop, which is triggered by the trailing edge of the horizontal sync pulse, generates this pulse.

#### P<sub>111</sub> Phase Detector

The phase detector is a standard one using switched current sources. The middle of the sync is compared with a fixed point of the oscillator sawtooth voltage. The PLL filter is connected to Pin17.

#### **Horizontal Oscillator**

This oscillator is a relaxation type oscillator. Its frequency is determined mainly by the capacitor on Pin19.

A frequency range of one octave is acheived by the current on Pin18. The  $\phi$ 1 control voltage from Pin17 is fed via a buffer amplifier and an attenuator to the current reference Pin18 to acheive a high DC loop gain. Therefore, changes in frequency will not affect the phase relationship between horizontal sync pulses and line flyback pulses.

#### Functional Description (Cont'd):

#### P<sub>LL2</sub> Phase Detector

This phase detector is similar to the P<sub>LL1</sub> phase detector. Line flyback signals (Pin2) are compared with a fixed point of the oscillator sawtooth voltage. Delays in the horizontal deflection circuit are compensated by adjusting the phase relationship between horizontal sync and horizontal output pulses.

A certain amount of phase adjustment is possible by injecting a DC current from an external source into the P<sub>LL2</sub> filter capacitor on Pin20.

#### **Horizontal Driver**

This open–collector output stage (Pin3) can directly drive an external driver transistor. The saturation voltage is 300mV at 20mA. To protect the line deflection transistor, the horizontal output stage does not conduct at  $V_P < 6.4\text{V}$  (Pin1).

#### **Vertical Oscillator and Amplitude Control**

This stage is designed for fast stabilization of the vertical amplitude after changes in sync conditions.

The free–running frequency  $f_o$  is determined by the values of  $R_{VOS}$  and  $C_{VOS}$ . The recommended values should be altered marginally only to preserve the excellent linearity and noise performance. The vertical drive currents  $I_5$  and  $I_6$  are in relation to the value of  $R_{VOS}$ . Therefore, the oscillator frequency must be determined only by  $C_{VOS}$  on Pin16.

$$f_0 = \frac{1}{10.8 \times R_{VOS} \times C_{VOS}}$$

To acheive a stabilized amplitude the free–running frequency f<sub>o</sub> (without adjustment) must be lower than the lowest occurring sync frequency. The contributions shown in Table 1 can be assumed.

Table 1. Calculation of fo Total Spread

| Contributing Elements                                                |    |  |

|----------------------------------------------------------------------|----|--|

| Minimum Frequency Offset Between fo and the Lowest Trigger Frequency | 10 |  |

| Spread of IC                                                         | ±3 |  |

| Spread of R (22kΩ)                                                   | ±1 |  |

| Spread of C (0.1μF)                                                  | ±5 |  |

| Total                                                                | 19 |  |

Results for 50 to 110Hz application:  $f_0 = \frac{50Hz}{1.19} = 42Hz$

Table 2. VGA Modes

| Mode | Horizontal/Vertical<br>Sync Polarity | Horizontal<br>Frequency<br>(kHz) | Vertical<br>Frequency<br>(Hz) | Number of<br>Active Lines | Output<br>Mode Pin7 |

|------|--------------------------------------|----------------------------------|-------------------------------|---------------------------|---------------------|

| 1    | +/-                                  | 31.45                            | 70                            | 350                       | LOW                 |

| 2    | <b>-/+</b>                           | 31.45                            | 70                            | 400                       | LOW                 |

| 3    | -/-                                  | 31.45                            | 60                            | 480                       | LOW                 |

| 4    | +/+                                  | Fixed by External Circuitry      | _                             | _                         | HIGH                |