MT92210

## Features

1023 full-duplex PCM or ADPCM voice channels over IP/UDP/RTP connections

ZARLI

- RTP packaging optional in IP/UDP connection

- Supports IP version 4 and version 6

- Supports IP over Ethernet, ATM (AAL5) or POS

- Support Ethernet II, IEEE 802.3, LLC/SNAP and PPP frames

- Supports Classical IP over ATM and LAN Emulation (LANE) v1/v2

- Supports MPLS, MPOA and IEEE 802.1p/Q ELAN-ID

- H.110 compliant TDM bus carrying PCM, ADPCM or HDLC channels

- HDLC channels can be used to carry UDP payload generated by external agent

- Support trunking in RTP; up to 255 PCM/ADPCM channels per RTP connection

- Support maximum 1500 bytes packet size

- Up to 4096 bytes of jitter buffer, absorbing +/-256 ms of PDV

- Less than 250 usec of latency

Ordering Information

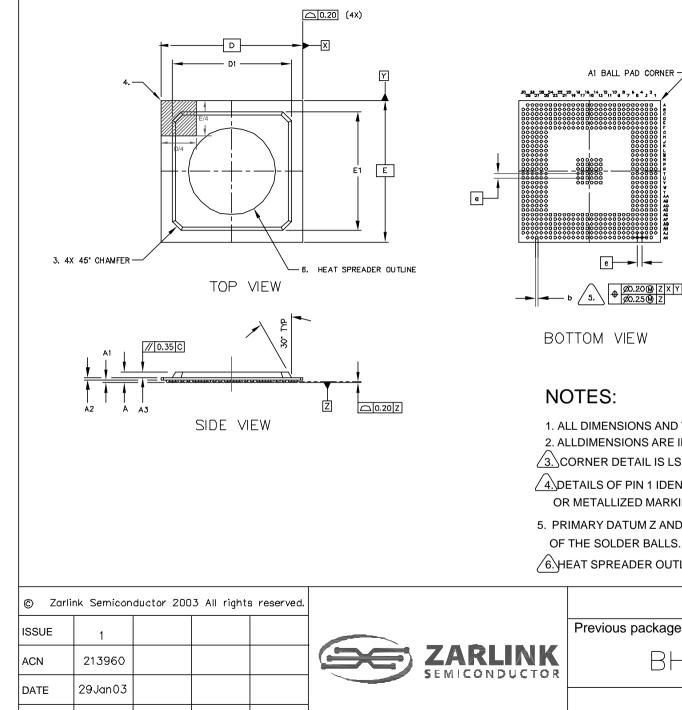

MT92210

608 Pin EPBGA

-40°C to +85°C

- Injection of CPU-generated RTP packets or AAL0 cells

- Reception of CPU-destinated RTP packets or AAL0 cells

- Primary and secondary network interfaces

- Primary network interface supports 10/100 MII, POS-PHY or Utopia level 1/2

- Secondary network interface supports Utopia level 1

- Proprietary Adaptive Silence Suppression

- Less than 2.5 watts of power

- 608 pin PBGA package

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2002-2004, Zarlink Semiconductor Inc. All Rights Reserved. December 2004

## Applications

- High density voice gateway

- Voice over IP

- 3G and UMTS

- Network processor

- IP switching

- Voice over DSL/cable

## Description

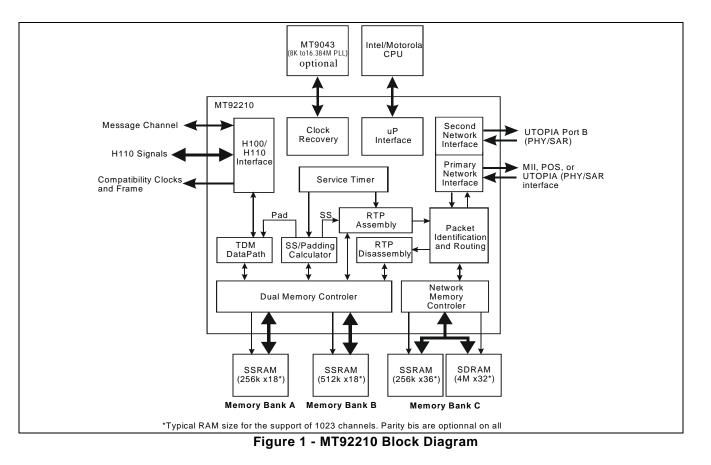

The MT92210 device is a voice over IP/RTP assembly and disassembly engine that can convert up to 1023 fullduplex PCM voice channels or 4096 HDLC channels to IP packets and back, conforming to IETF RFC791 (IPv4), RFC2460 (IPv6), RFC768 (UDP) and RFC1889 (RTP). On one side, the device communicates with an H.110 TDM bus carrying voice in either PCM format, ADPCM or HDLC-encapsulated mini-packets; on the other side, it carries its packet data over Ethernet, ATM (using AAL5 cells) or Packet over SONET. A 16-bit Intel/Motorola CPU interface is used to access and configure the device. Finally, three external SSRAM banks and one external SDRAM bank are used for configuration and storage space.

## Conventions

In this document, the following conventions are used:

- The transmission direction and the abbreviation TX always refer to the direction in which voice is converted into IP packets.

- The reception direction and the abbreviation RX refer to the direction in which packets or cells are converted into PCM bytes or HDLC packets.

- All numbers in this document are decimal unless otherwise specified.

- Hexadecimal number can be identified by the 'h' suffix (ex: A5h).

- Binary numbers are either in double quotes for multiple bits or in single quotes for individual bits (ex: "1001", '0').

- The term "byte" means 8 bits.

- The term "word" means 16 bits.

- The term "dword" means 32 bits.

- The word "high" means a binary value of '1'.

- The word "low" means a binary value of '0'.

- The verb "to clear" means to reset one or multiple bits to '0'

- The verb "to set" means to put one or multiple bits to '1'.

- All addresses are specified in hexadecimal and point to bytes. Addresses are converted from bytes to words to double words using the little endian format, unless otherwise specified.

## Colour Code

In this document, the following color code is used:

- Fields in red are initialized by software when the structure is created, and are written back by the hardware.

- Fields in black are initialized by software when the structure is created, and are never written back by the hardware.

- Fields in dark yellow are initialized by software when the structure is created and are written back at the same value by the hardware.

This shade denotes a Reserved Field.

This shade denotes an Unimplemented Field.

The field outlined in red is only written back by the chip when one of the bits, contained within the field and in red, was set and will then be cleared by the chip when it is done acting upon the set request bit.

## **Document Organization**

This data sheet is divided into the following sections:

- CPU Interface (Chapter 2.0) describes the main external interface of the MT92210 chip.

- **Network Interface** (Chapter 3.0) describes the interface to the 3 different types of link interfaces, Ethernet, UTOPIA, and Packet over SONET, that are supported.

- Link Layers (Chapter 4.0) describes the 3 different types of link layers, Ethernet, ATM AAL5, and Packet over SONET, that are supported.

- **RX/TX Data Flows** (Chapter 5.0) describes the data flows for all packets received and transmitted.

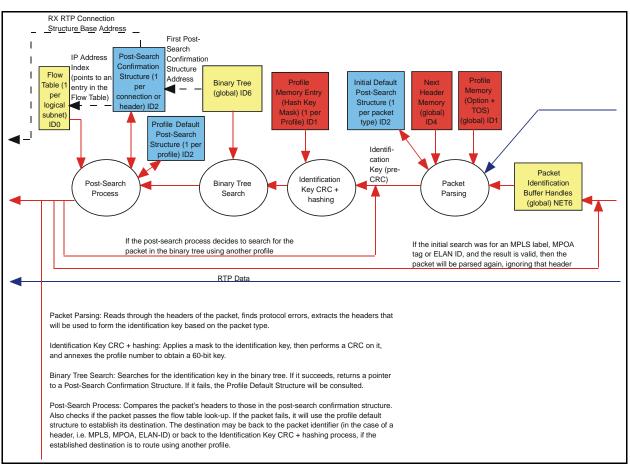

- Packet Identification (Chapter 6.0) describes the process by which packets are identified.

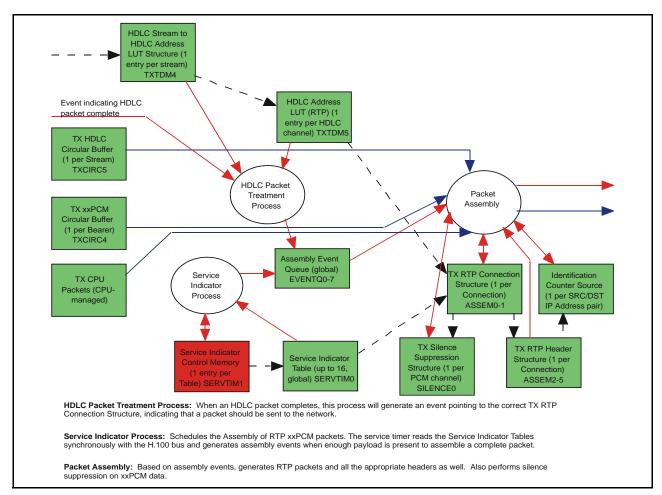

- **Packet Assembly** (Chapter 7.0) describes the collected bytes written in the circular buffers by the TX TDM, and how they are assembled into RTP packets.

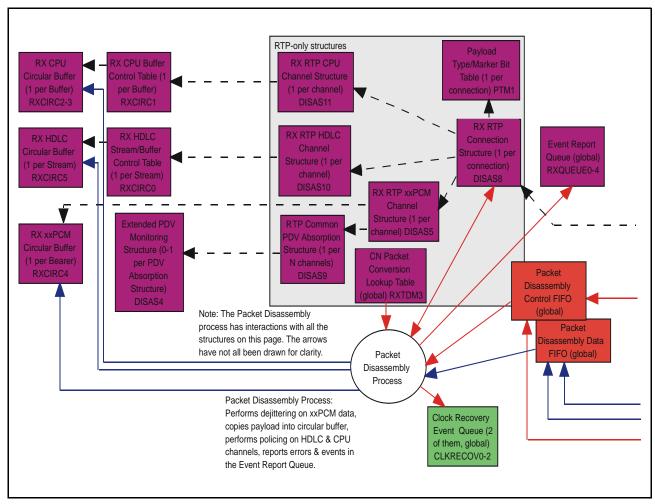

- **Packet Disassembly** (Chapter 8.0) describes how RTP packets are transformed into PCM bytes, ADPCM samples, or HDLC/CPU-destined mini-packets.

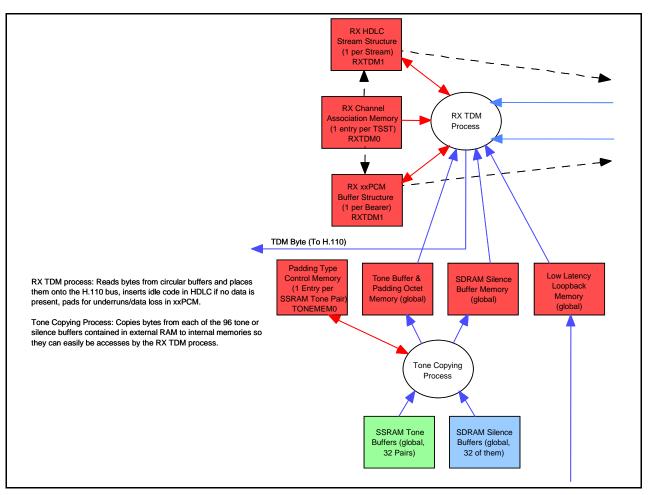

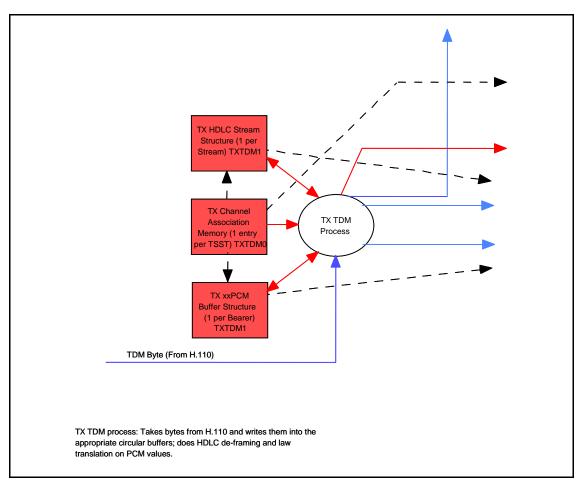

- **TX/RX TDM Data Paths** (Chapter 9.0) describes the data paths for all bytes transmitted and received with the H.110 interface.

- H.110 Interface (Chapter 10.0) describes the compatibility of the TDM interface with the H.110 bus.

- **Clocking** (Chapter 11.0) describes the clocks used for the Network Interface and the SAR portion of the device.

- **Pin-out** is in Chapter 12.0.

- Electrical Characteristics (Chapter 13.0) describes the electrical characteristics of all the interfaces.

- **Register List** and **Memory Map** are contained in the MT92210 Design Manual.

## **Table of Contents**

| Features                                  |       |

|-------------------------------------------|-------|

| Applications                              | ii    |

| Description                               | ii    |

| Conventions                               | ii    |

| Colour Code                               | . iii |

| Document Organization                     | . iii |

| 1.0 Features.                             |       |

| 1.1 General Features                      |       |

| 1.2 Data Formats                          |       |

| 1.3 Voice Treatment Functions             |       |

| 1.4 Network Functions                     |       |

| 1.5 Silence Suppression and Padding       |       |

| 1.6 H.110 Interface                       |       |

| 1.7 TDM data formats.                     |       |

| 1.8 Link Interface                        |       |

| 2.0 CPU interface                         | 17    |

| 2.1 CPU Interface Description             |       |

| 2.2 CPU Interrupts                        |       |

| 2.2.1 Example Interrupt Flow.             |       |

| 2.2.1.1 Interrupt Initialization          |       |

| 2.2.1.2 Interrupt Servicing               |       |

| 2.3 Intel/Motorola Interface.             |       |

| 2.3.1 Extended Indirect Access Procedures |       |

| 2.3.1.1 Extended Indirect Writes          |       |

| 2.3.1.2 Extended Indirect Reads.          |       |

| 2.3.2 Extended Direct Access Procedures   |       |

| 2.3.2.1 Extended Direct Writes            |       |

| 2.3.2.2 Extended direct reads             |       |

| 2.4 MT92210 Reset Procedure               |       |

| 3.0 Network Interface                     |       |

| 4.0 Link Layers                           |       |

| 4.1 Interfaces                            |       |

| 4.2 Ethernet Interface.                   |       |

| 4.3 Packet over SONET Interface           |       |

| 4.4 UTOPIA Interface                      |       |

| 4.5 Packet Reassembly                     |       |

| 5.0 RX/TX Data Flows                      |       |

| 5.1 RX Data Flow                          |       |

| 5.2 TX Data Flow                          |       |

|                                           |       |

| 6.0 Packet Identification                 |       |

| 6.1 Packet Types                          |       |

| 6.2 Packet Parsing                        |       |

| 6.3 Look-up                               |       |

| 6.4 Masking                               |       |

|                                           |       |

| 7.0 Packet Assembly                       |       |

| 7.1 Service Timer                         |       |

| 7.2 Event Queue                           |       |

| 7.3 RTP Packets                           |       |

| 7.3.1 TX RTP Header Structure.            |       |

| 7.3.2 Header Length                       |       |

| 7.3.3 Packet Type                         | 70    |

## **Table of Contents**

| 7.3.4 Identification Counter Source Address          |     |

|------------------------------------------------------|-----|

| 7.3.5 UDP Header Start.                              |     |

| 7.3.6 Timestamp Offset                               |     |

| 7.3.7 Sequence Number                                |     |

| 7.3.8 Transmitted Packet Count                       |     |

| 7.3.9 RTD.                                           |     |

| 7.4 PCM Packets                                      |     |

| 7.4.1 Next TDM Write Pointer                         |     |

| 7.4.2 Valid Bit                                      |     |

| 7.4.3 Buffer Size                                    |     |

| 7.4.4 TX Silence Suppression Structure Base.         |     |

| 7.4.5 Extra Delay Frames                             |     |

| 7.4.6 RTP Timestamp                                  |     |

| 7.4.7 Circular Buffer Base Addresses                 |     |

| 7.5 HDLC Packets                                     |     |

| 7.6 Silence Suppression.                             |     |

| 8.0 Packet Disassembly                               |     |

| 8.1 RTP Treatment.                                   |     |

| 8.2 xxPCM Treatment                                  |     |

| 8.3 Packet Delay Variation (PDV) Monitoring          |     |

| 8.4 HDLC Treatment                                   |     |

| 8.5 CPU Treatment                                    | 106 |

| 9.0 TX/RX TDM Data Paths                             | 111 |

| 9.1 TX TDM Data Path                                 | 111 |

| 9.2 TX TDM Data Formats                              | 117 |

| 9.3 RX TDM Data Path.                                | 119 |

| 9.3.1 RX TDM Data Formats                            | 126 |

| 10.0 H.110 Interface                                 | 131 |

| 10.1 Slave Mode                                      |     |

| 10.2 Bus Master Mode                                 |     |

| 10.3 Polarities.                                     |     |

| 11.0 Clocking                                        |     |

| 11.1 Programming the mem_clk_xxx PLL                 |     |

| 11.2 Clock Recovery                                  |     |

| 11.3 Memory Controllers                              |     |

| 12.0 Pin-out                                         |     |

|                                                      |     |

| 13.0 Electrical Characteristics                      |     |

|                                                      | 163 |

| 13.2 Recommended Operating Conditions                |     |

|                                                      | 163 |

| ······································               | 165 |

| 13.5 AC Characteristics                              | 166 |

|                                                      |     |

| 13.5.2 UTOPIA / POS-PHY / Ethernet Interface         |     |

|                                                      | 174 |

|                                                      | 177 |

| Appendix A                                           |     |

| Notes                                                |     |

| Appendix B                                           |     |

| HDLC Format, Including Zero-Insertion and Extraction |     |

| Appendix C                                           |     |

| Standards & Specifications                           | 183 |

## **Table of Contents**

| Appendix D        | <br> |

|-------------------|------|

| Glossary of Terms | <br> |

# List of Figures

| Figure 1 - MT92210 Block Diagram                                                           | i    |

|--------------------------------------------------------------------------------------------|------|

| Figure 2 - Internal Interrupt Network                                                      | . 18 |

| Figure 3 - Network Interface Buffering                                                     | . 23 |

| Figure 4 - Packet Block Memory and Format.                                                 | . 24 |

| Figure 5 - Packet Block Format                                                             | . 24 |

| Figure 6 - Packet Handler Memory                                                           | . 26 |

| Figure 7 - Handle Queue and Handle Format                                                  | . 27 |

| Figure 8 - Basic Handle Format.                                                            |      |

| Figure 9 - Raw Cell Format (used cell)                                                     |      |

| Figure 10 - Raw Cell Format (free cell)                                                    |      |

| Figure 11 - Cell Handler Memory                                                            |      |

| Figure 12 - UTOPIA Look Up Table                                                           |      |

| Figure 13 - UTOPIA LUT Entry Format                                                        |      |

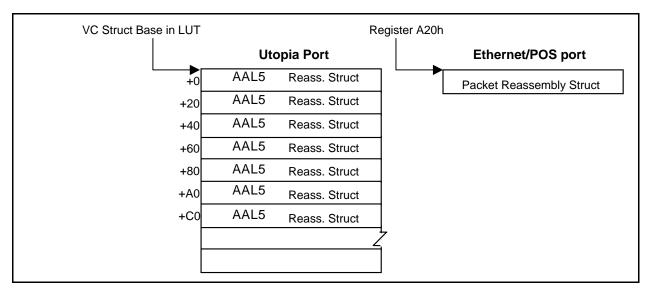

| Figure 14 - Location of Reassembly Structures                                              |      |

| Figure 15 - Packet Reassembly Structure                                                    |      |

| Figure 16 - Rx Flow 1                                                                      |      |

| Figure 17 - Rx Flow 2                                                                      |      |

| Figure 18 - Rx Flow 3                                                                      |      |

| Figure 19 - Rx Flow 4.                                                                     |      |

| Figure 20 - Tx Flow 1                                                                      |      |

| Figure 21 - Tx Flow 2                                                                      |      |

| Figure 22 - Tx Flow 3                                                                      |      |

| Figure 23 - Tx Flow 4                                                                      |      |

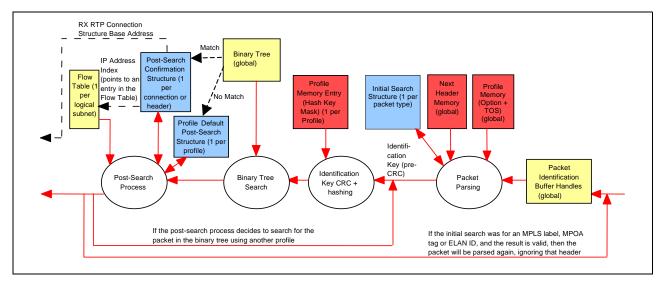

| Figure 24 - Packet Identification                                                          |      |

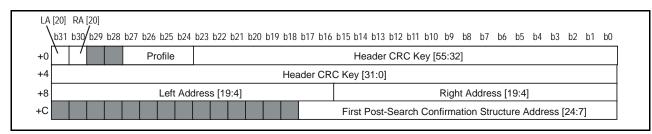

| Figure 25 - Format of Initial Search Structure (Refer to Figure 19 for field descriptions) |      |

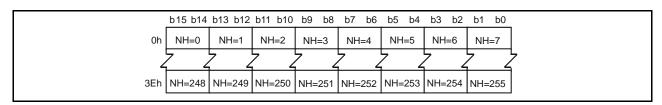

| Figure 26 - Next Header Memory                                                             |      |

| Figure 27 - Identification Key Formats (before CRC).                                       |      |

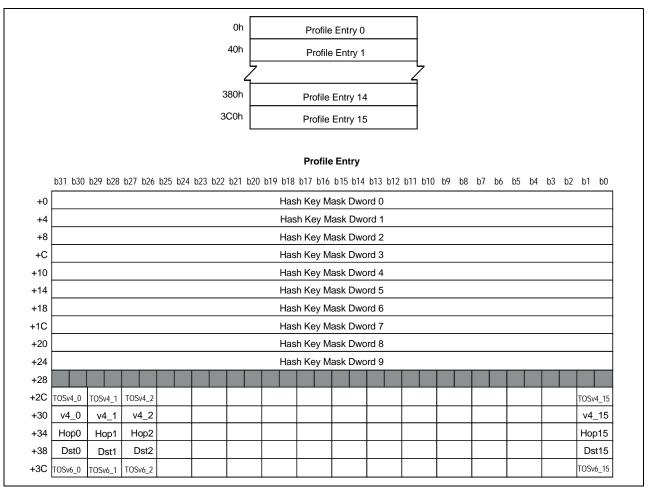

| Figure 28 - Profile Memory                                                                 |      |

| Figure 29 - Flow Table                                                                     |      |

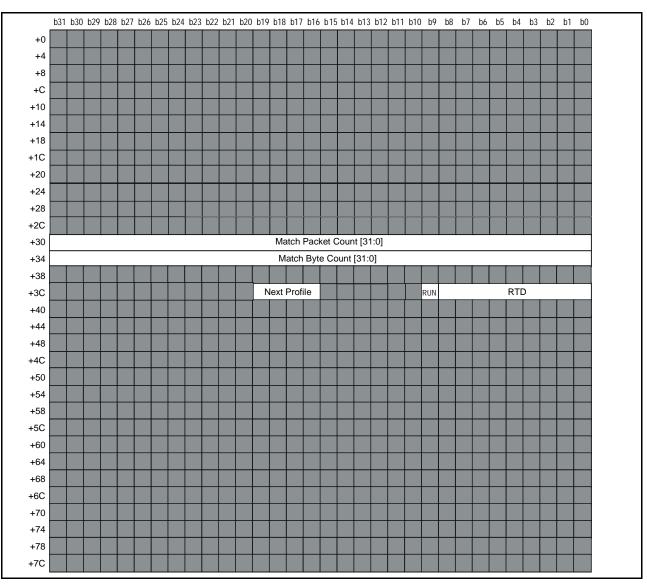

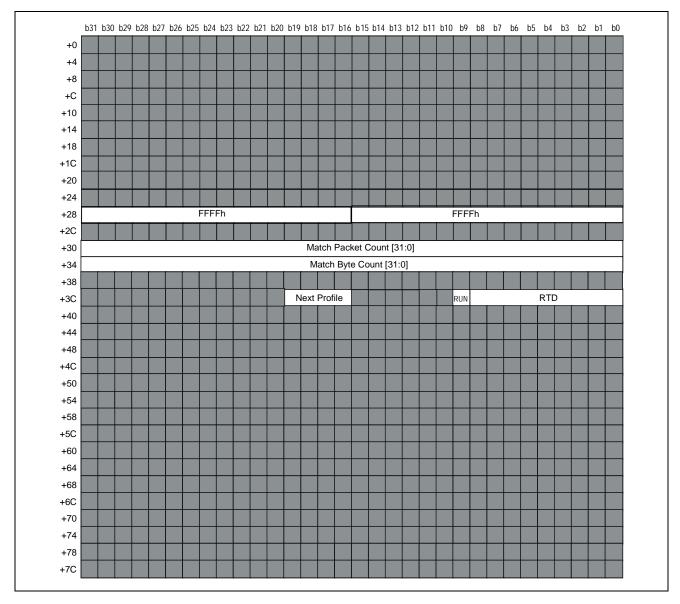

| Figure 30 - Format of Profile Default Post-Search Structure                                | . 55 |

| (Refer to Table 19 for field descriptions)                                                 | 57   |

| Figure 31 - Binary Tree Node.                                                              | . 57 |

| Figure 32 - Post-Search Conformation Structure.                                            |      |

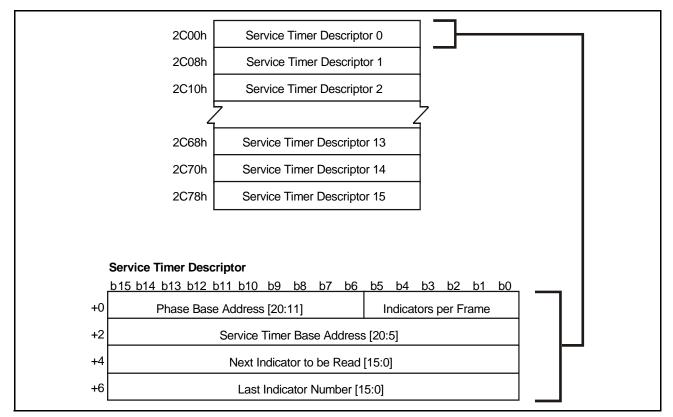

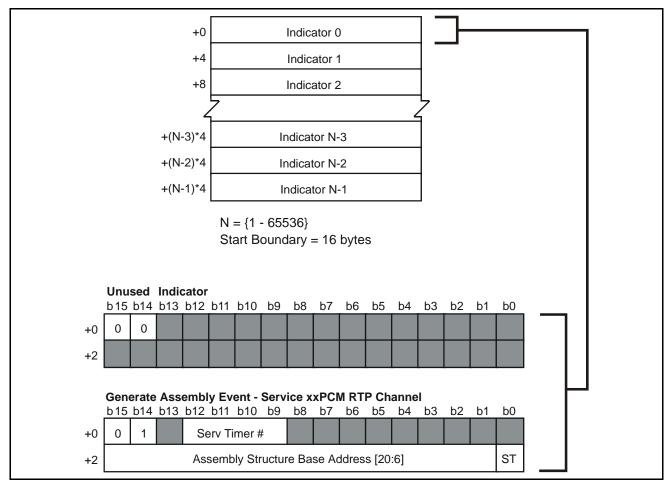

| Figure 33 - Service Timer Control Memory                                                   |      |

|                                                                                            |      |

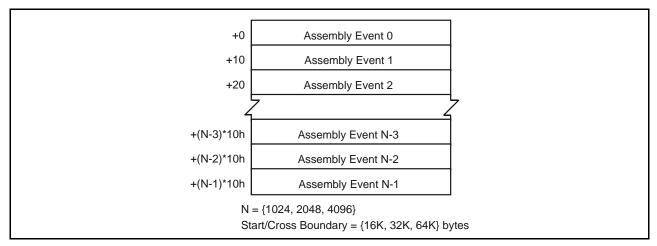

| Figure 34 - Assembly Event Queue                                                           |      |

|                                                                                            |      |

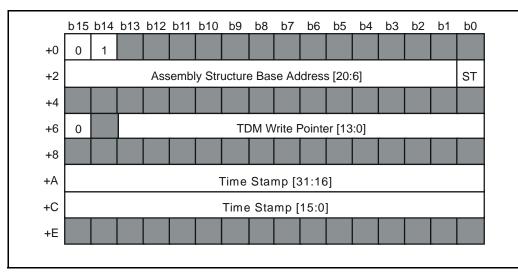

| Figure 36 - Assembly Event - Service xxPCM RTP Channel.                                    |      |

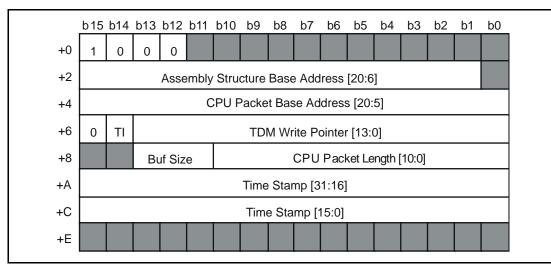

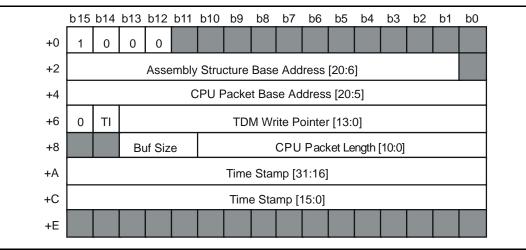

| Figure 37 - Assembly Event - Send CPU RTP Packet.                                          |      |

| Figure 38 - TX RTP Connection Structure                                                    |      |

| Figure 39 - xxPCM Channel Addition to TX RTP Connection Structure                          |      |

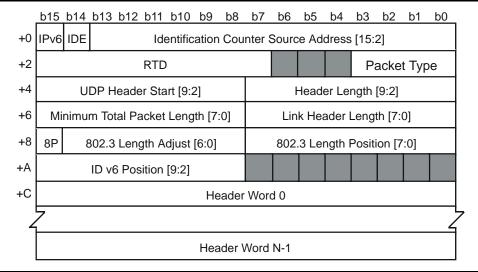

| Figure 40 - TX RTP Header Structure                                                        |      |

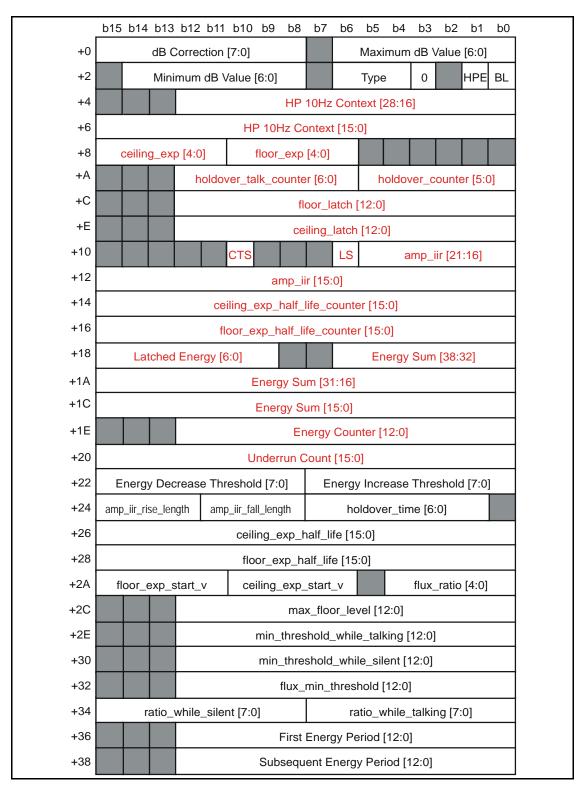

| Figure 41 - TX Silence Suppression Structure: Internal VAD & White Energy Estimation       |      |

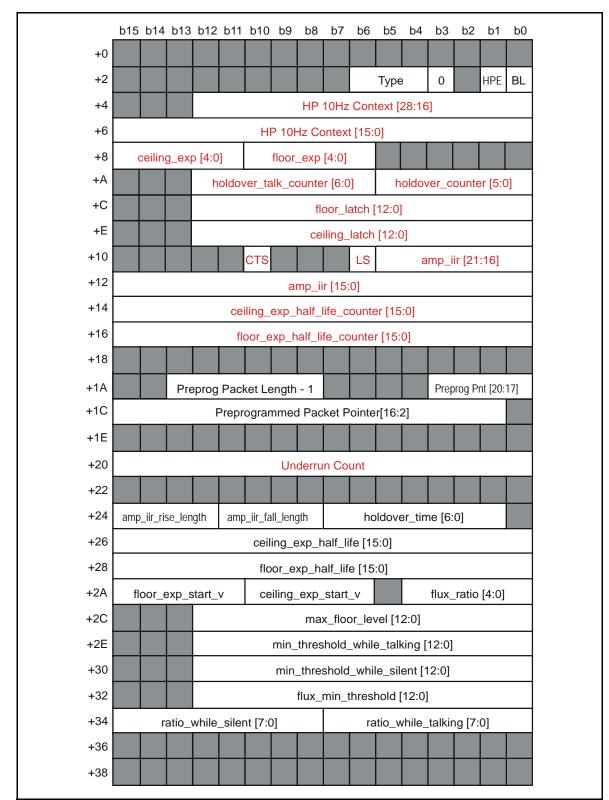

| Figure 42 - TX Silence Suppression Structure: Internal VAD & Spectral Energy Forwarding    |      |

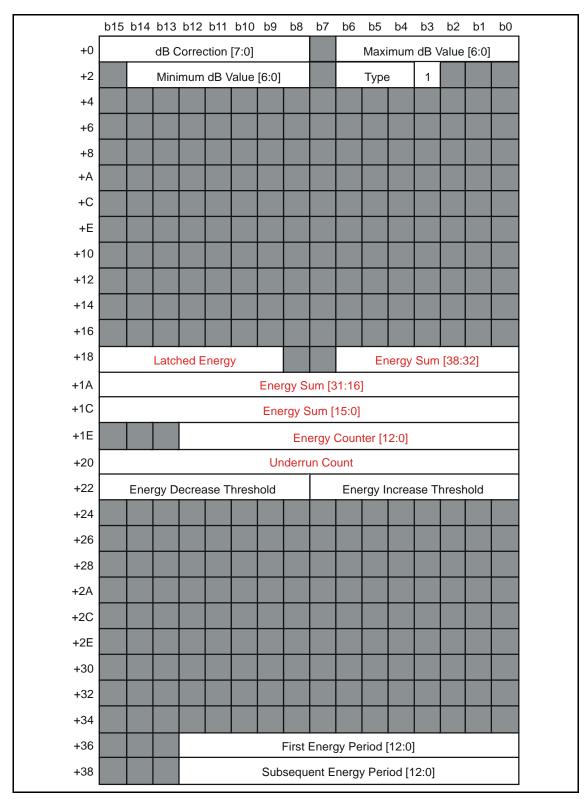

| Figure 43 - TX Silence Suppression Structure: External VAD & White Energy Estimation       |      |

| Figure 44 - TX Silence Suppression Structure: External VAD & Spectral Energy Forwarding    |      |

| Figure 45 - RX Disassembly Event Report Queue.                                             |      |

| Figure 46 - RX RTP Connection Structure                                                    |      |

| Figure 47 - Payload Type/Marker Bit Table                                                  |      |

| Figure 48 - RX Disassembly Event Report Queue - RTP Connection Report                      |      |

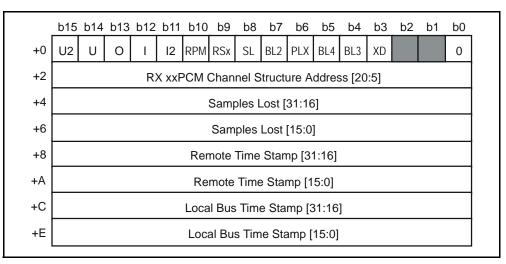

| Figure 49 - RX RTP xxPCM Channel Structure                                                 | . 94 |

## List of Figures

| Figure 50 - RX Disassembly Event Report Queue - xxPCM Channel Report                  |     |

|---------------------------------------------------------------------------------------|-----|

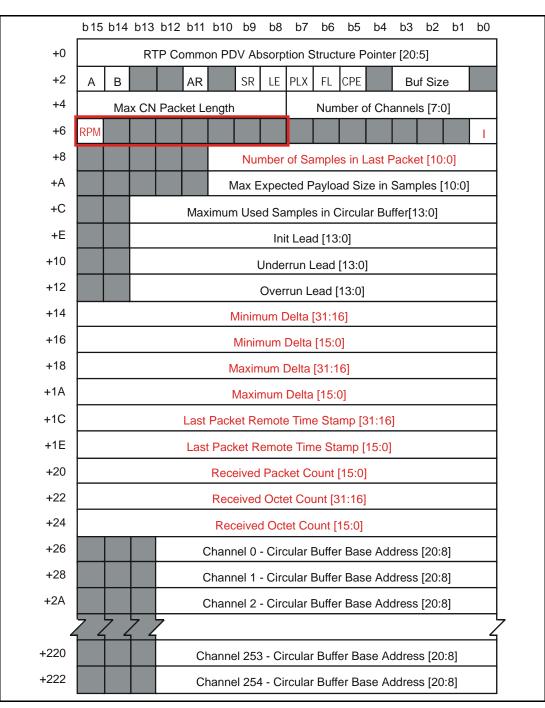

| Figure 51 - RTP Common PDV Absorption Structure                                       |     |

| Figure 52 - RX RTP HDLC Channel Structure                                             |     |

| Figure 53 - RX Disassembly Event Report Queue - HDLC / CPU Channel Report.            |     |

| Figure 54 - Rx CPU Buffer Control Table.                                              |     |

| Figure 55 - RX Circular Buffer Base and Size                                          |     |

| Figure 56 - RX RTP CPU Channel Structure                                              |     |

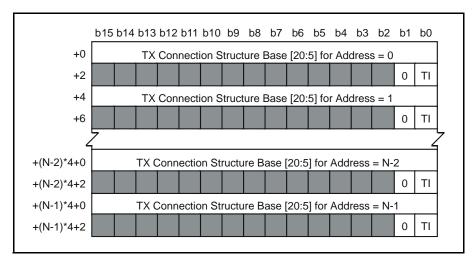

| Figure 57 - TX Channel Association Memory                                             |     |

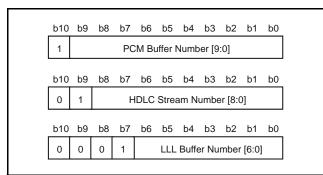

| Figure 58 - Buffer Tag Format                                                         |     |

| Figure 59 - TX TDM Control Memory.                                                    |     |

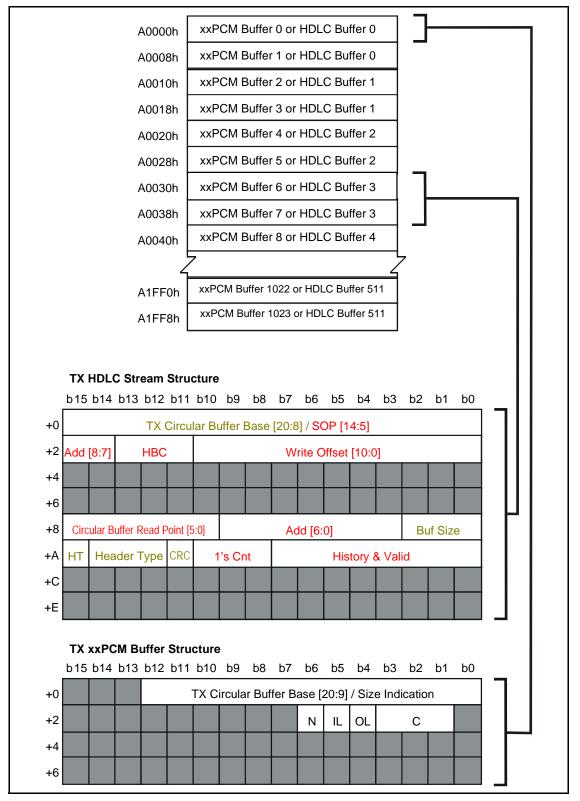

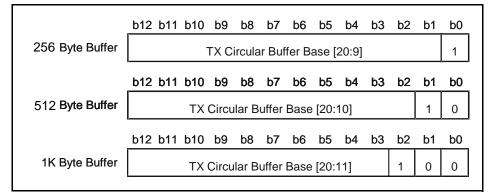

| Figure 60 - TX Circular Buffer Base/Size Indication.                                  |     |

| Figure 61 - TX Circular Buffer Base/SOP                                               |     |

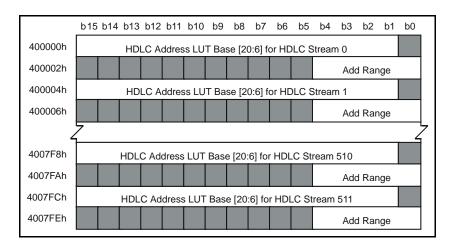

| Figure 62 - HDLC Stream to HDLC Address LUT Structure                                 |     |

| Figure 63 - HDLC Address LUT (RTP)                                                    |     |

| Figure 64 - Format of TX xxPCM TSSTs                                                  |     |

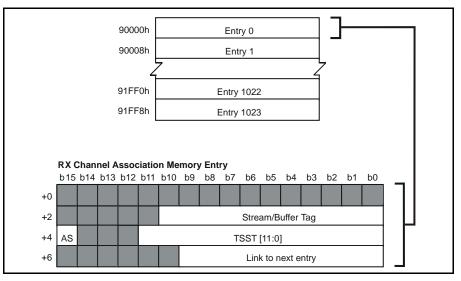

| Figure 65 - RX Channel Association Memory                                             |     |

| Figure 66 - Stream/Buffer Tag Format                                                  |     |

| Figure 67 - RX TDM Control Memory                                                     |     |

| Figure 68 - RX Circular Buffer Base/Size Indication                                   |     |

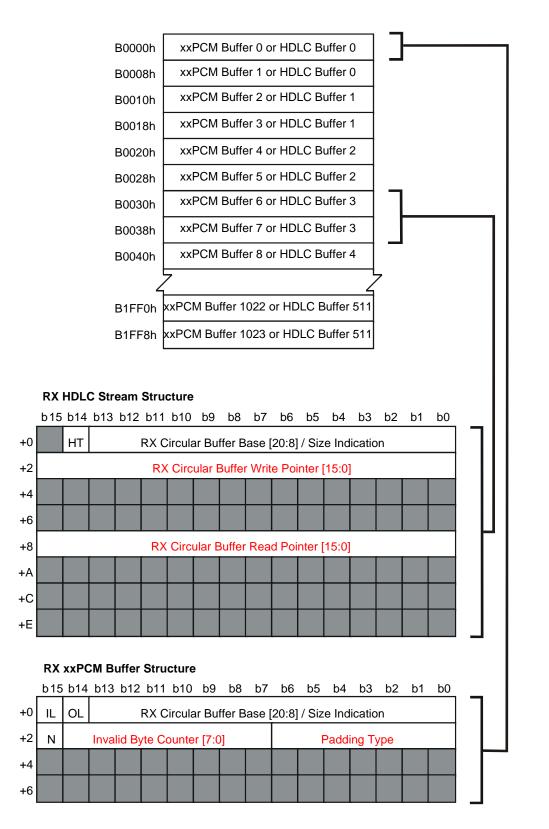

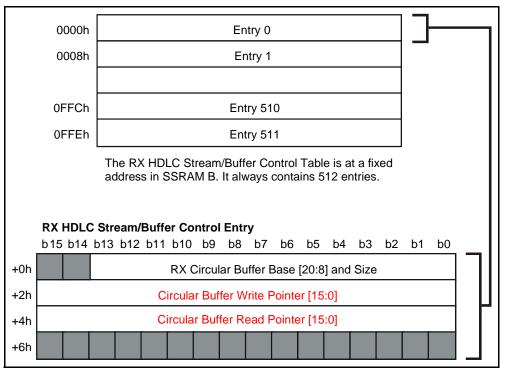

| Figure 69 - RX HDLC Stream/Buffer Control Table                                       |     |

| Figure 70 - RX Circular Buffer Base and Size                                          |     |

| Figure 71 - Format of RX xxPCM TSSTs - 1 of 2                                         |     |

| Figure 72 - Format of RX xxPCM TSSTs - 2 of 2                                         |     |

| Figure 73 - CN Packet Conversion Lookup Table                                         |     |

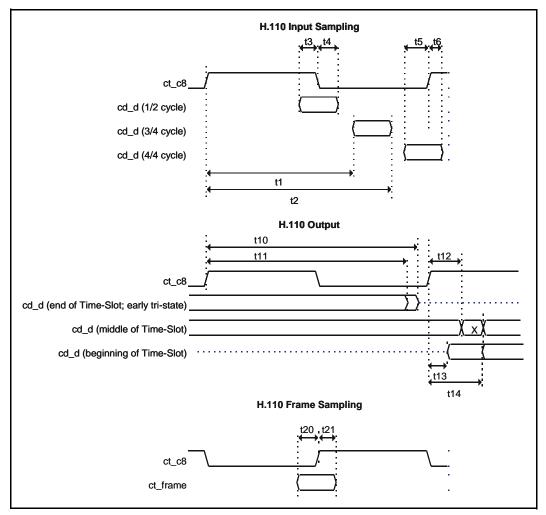

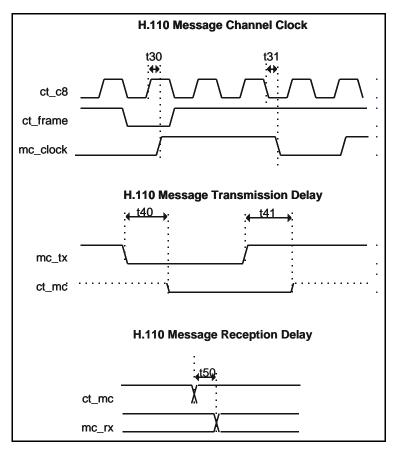

| Figure 74 - TDM Bus Timing - ct_d                                                     |     |

| Figure 75 - TDM Bus Timing - fr_comp Generation                                       |     |

| Figure 76 - TDM Bus Timing - sclkx2 Generation                                        |     |

| Figure 77 - TDM Bus Timing - Compatibility Clock Generation (other than sclk, sclkx2) |     |

| Figure 78 - Clock Synthesis                                                           |     |

| Figure 79 - Adaptive Clock Recovery Event Queue                                       | 137 |

| Figure 80 - Adaptive Clock Recovery RTP Event Structure                               | 137 |

| Figure 81 - Adaptive Clock Recovery Modules                                           | 139 |

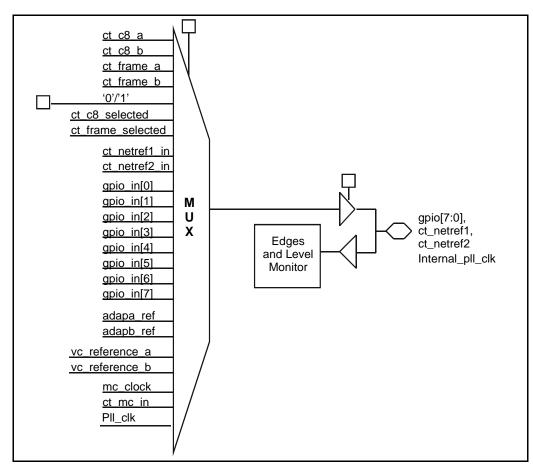

| Figure 82 - GPIO Functionality                                                        | 140 |

| Figure 83 - Message Channel Circuit                                                   | 141 |

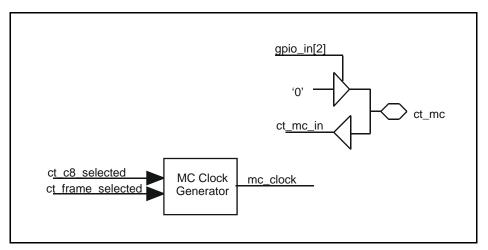

| Figure 84 - PLL Noise Reduction Circuits                                              | 161 |

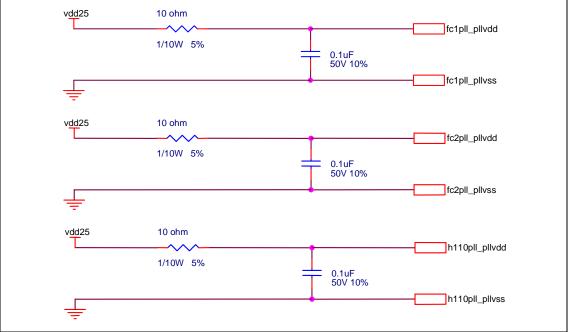

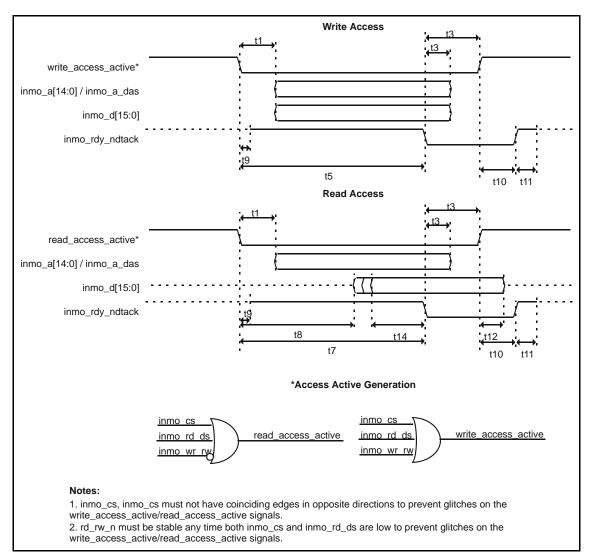

| Figure 85 - Non-multiplexed CPU Interface - Intel Mode                                | 166 |

| Figure 86 - Non-multiplexed CPU Interface - Motorola Mode                             | 167 |

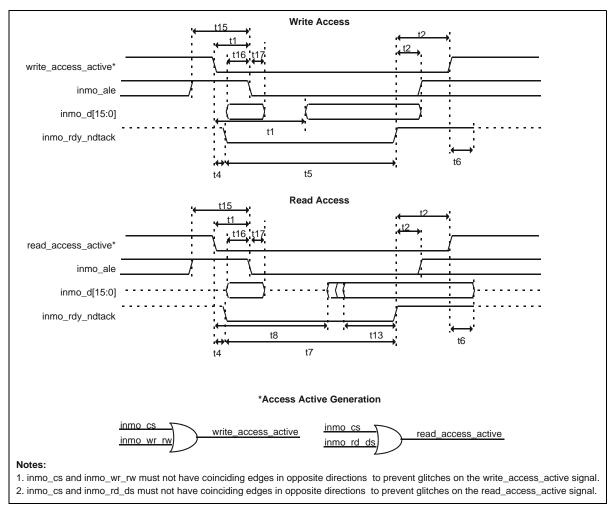

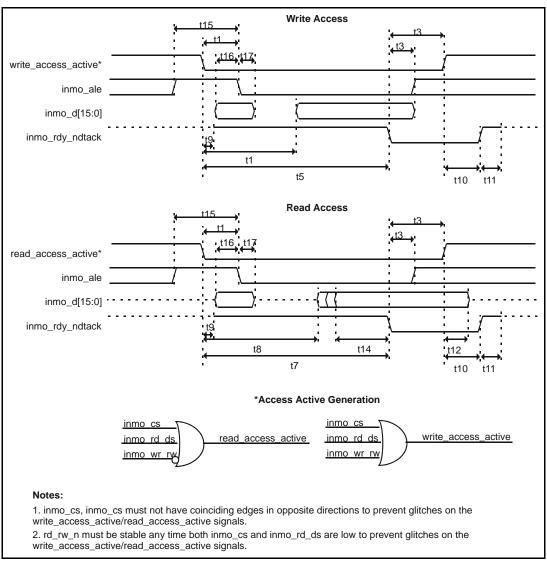

| Figure 87 - Multiplexed CPU Interface - Intel Mode                                    | 168 |

| Figure 88 - Multiplexed CPU Interface - Motorola Mode                                 | 169 |

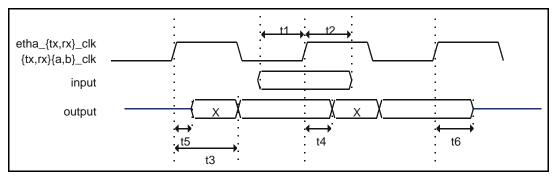

| Figure 89 - UTOPIA / POS-PHY / Ethernet Timing                                        | 173 |

| Figure 90 - H.110 Input Output.                                                       | 174 |

| Figure 91 - H.110 Message Handling.                                                   |     |

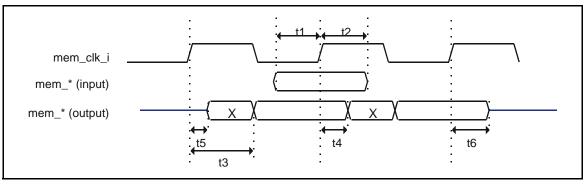

| Figure 92 - External Memory Timing (both SSRAM and SDRAM)                             | 177 |

| Figure 93 - Supported RTP HDLC Packet Format (after zero extraction)                  | 181 |

|                                                                                       |     |

# List of Tables

| Table 1 - Indirect Access Register                     | 19  |

|--------------------------------------------------------|-----|

| Table 2 - CPU Interface Mode Selection                 | 19  |

| Table 3 - Control Register (000h).                     |     |

| Table 4 - Read/Write Data Register (004h)              | 20  |

| Table 5 - Address High Register (008h).                | 20  |

| Table 6 - Address Low Register (00Ah)                  |     |

| Table 7 - Packet Block Format Table                    |     |

| Table 8 - Handle Queue Descriptor                      |     |

| Table 9 - Fields and Description.                      |     |

| Table 10 - Fields and Description.                     |     |

| Table 11 - Fields and Description                      |     |

| Table 12 - Fields and Description.                     |     |

| Table 13 - Packet Types and Initial Search Structures. |     |

| Table 14 - Fields and Description.                     | 52  |

| Table 15 - Fields and Description.                     | 54  |

| Table 16 - Fields and Description.                     | 56  |

| Table 17 - Profile Default Post-Search Structure       | 56  |

| Table 18 - Fields and Description.                     | 58  |

| Table 19 - Fields and Description.                     |     |

| Table 20 - Fields and Description.                     | 64  |

| Table 21 - Service Timer                               | 65  |

| Table 22 - Fields and Description.                     | 67  |

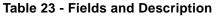

| Table 23 - Fields and Description.                     | 68  |

| Table 24 - Fields and Description.                     | 69  |

| Table 25 - Fields and Description.                     | 72  |

| Table 26 - Fields and Description.                     | 74  |

| Table 27 - Fields and Description.                     |     |

| Table 28 - Fields and Description.                     | 85  |

| Table 29 - Fields and Description.                     | 89  |

| Table 30 - Fields and Description.                     |     |

| Table 31 - Fields and Description.                     |     |

| Table 32 - Fields and Description.                     | 95  |

| Table 33 - Fields and Description.                     |     |

| Table 34 - Fields and Description.                     | 100 |

| Table 35 - Fields and Description.                     | 104 |

| Table 36 - Fields and Description.                     | 105 |

| Table 37 - Fields and Description.                     | 106 |

| Table 38 - Fields and Description.                     | 108 |

| Table 39 - Fields and Description.                     | 111 |

| Table 40 - Fields and Description.                     | 114 |

| Table 42 - Fields and Description.                     | 117 |

| Table 41 - Fields and Description.                     | 117 |

| Table 43 - Fields and Description.                     | 120 |

| Table 44 - Fields and Description.                     | 121 |

| Table 45 - Fields and Description.                     | 123 |

| Table 46 - Fields and Description.                     | 125 |

| Table 47 - Fields and Description.                     | 129 |

| Table 48 - Clock Divisor X and Y                       | 135 |

| Table 49 - Clock Divisor Z                             | 136 |

## List of Tables

| Table 50 - Fields and Description | 138 |

|-----------------------------------|-----|

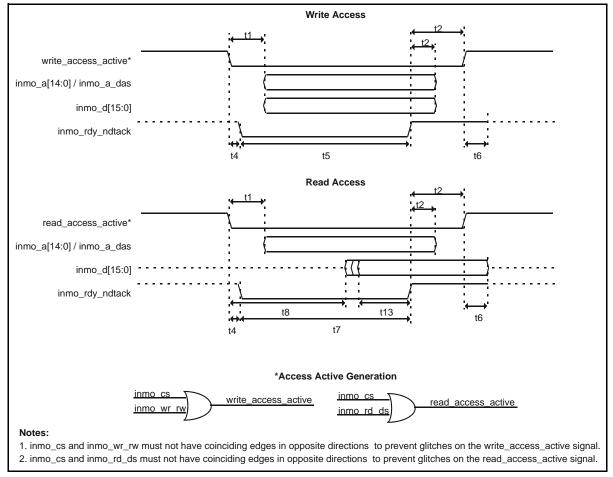

| Table 51 - t5 Write Access Time   |     |

| Table 52 - t7 Read Access Time    |     |

| Table 53 - Fields and Description |     |

| Table 54 - Fields and Description |     |

| Table 55 - Fields and Description |     |

## 1.0 Changes Summary

Changes from December 2002 Issue to December 2004 Issue. Page, section, figure and table numbers refer to this issue.

| Page | Item                    | Change                                         |  |

|------|-------------------------|------------------------------------------------|--|

| 133  | "Pin Description Table" | Pin names for "PLL_CLK" and "Vss_0" corrected. |  |

## 2.0 Features

The MT92210 device supports the following features:

### 2.1 General Features

- Up to 1023 full-duplex PCM or ADPCM voice channels over IP/UDP/RTP connections

- Up to 4096 HDLC channels carrying application data (UDP payload) converted to IP/UDP connections

- Simultaneous support of PCM, ADPCM and HDLC connections

- 16-bit Intel/Motorola CPU Interface

- Fully H.110 compliant TDM interface

- Network Interface A: UTOPIA Level 1/2, POS-PHY Level 2 or MII

- Network Interface B: UTOPIA Level 1

- Full chip capacity can be achieved with two 18 bit data bus ZBT SSRAM, each ranging in size from 128 K to 1 M bytes; one 36 bit data bus ZBT SSRAM, ranging in size from 128 K to 1 M bytes; and two 16 bit data bus SDRAM, each ranging in size from 8 M to 16 M bytes

### 2.2 Data Formats

- Simultaneous support of IP version 4 and 6

- Chip packages voice in RTP, UDP, and IP to support RFC791, RFC2460, RFC768, and RFC1889

- IP packets can be sent over 3 different types of physical links (Ethernet, ATM, Packet over SONET)

- RTP packaging is optional per connection

- HDLC mini-packets are encapsulated in IP and UDP (RTP packaging performed by external agent)

- IP/UDP layers are optional and can be eliminated to reduce overhead (i.e., null encapsulation) in either ATM AAL5 or Ethernet (using custom EtherType)

- IP over AAL5 can be performed using Classical IP over ATM with SNAP/LLC headers or Ethernet LAN Emulation (LANE) v1 or v2

- Support of MPLS. On reception, MPLS label can be used to establish data format following it, as well as logical subnet number and quality of service. MPLS multicast can be treated as unicast or routed to software

- Support of MPOA. On reception, MPOA tag can be used to establish data format following it, as well as logical subnet number and quality of service

- Logical subnet number can be established using ATM header, MPLS flow header, MPOA tag or ELAN-ID in LANE v2 header

- Quality of service can be determined using ATM header, Ethernet user priority or IP Type Of Service (TOS)

## 2.3 Voice Treatment Functions

- Up to 1023 PCM/ADPCM channels

- Support for up to 4096 HDLC channels distributed over 512 streams and 2046 time slots

- Up to 255 PCM/ADPCM channels per connection

- HDLC packets contain application data (UDP payload) converted to IP/UDP datagram

- Packets sizes up to 1500 bytes for IP/UDP

- Support of up to 1500 TDM samples of data per packet

- Jitter Absorption Buffer size up to 4096 bytes allowing absorption of up to ±256 ms of PDV

- Injection of CPU-generated RTP packets

- Reception of CPU-destined RTP packets in buffers of up to 64 K bytes

- Packet Delay Variation monitoring to diagnose and reduce delay

- Packet loss & misinsertion compensation for PCM and ADPCM packets

- Network jitter monitoring allows support of RTCP for PCM, ADPCM, HDLC and CPU connections

- Policing on HDLC channels and CPU channels protects against misbehaving connections

- PCM, ADPCM, HDLC and CPU mini-packets can all be transported on the same connection with chip's RTP engine to guarantee consistency among the packets

- In the disassembly module, synchronization deltas allow multiple independent connections to be synchronized end-to-end, allowing, for example, transparent transport of a DS3 over many IP connections

### 2.4 Network Functions

- IP packet identification can be performed using any combination of IP source address, IP destination address, UDP source port, UDP destination port and RTP Synchronization Source Identifier and are programmable on a per-connection basis

- Non-voice packets can be injected and received via the CPU Interface

- · Non-voice packets can be injected and received via the secondary UTOPIA port

- The MT92210 can be daisy-chained to other UTOPIA devices to increase capacity

- Off-the-shelf AAL5 SAR can be used to terminate data connections on a PCI bus

- Support of 16 different look-up profiles, each one of which can use different fields from the packet headers

- Look-up can be performed on a priority basis: for example, a packet can be looked-up using IP, UDP and RTP headers, then the look-up result can request a second lookup using only IP and UDP headers

- Binary tree of up to 128 K nodes is used to route packets using packet identification key

- · Dynamically balanced tree system ensures optimal performance

- IP, UDP and RTP header verification is performed

- Multihoming is supported with any number of local IP addresses

- Payload Type & Marker bit routing allows different compression formats as well as signaling packets to be transported on the same connection

- MPLS labels, MPOA tags and ELAN ID can be looked-up in binary tree to establish data format that will follow them, logical subnet number and quality of service

## 2.5 Silence Suppression and Padding

- Proprietary Adaptive Silence Suppression

- Supported in both PCM and ADPCM formats

- Built-in detection of energy level

- · Padding with matched-energy comfort noise

- 64 tone buffers used to generate tones (1 byte to 64 Kb each)

- 32 large comfort noise buffers (16 Kb to 64 Kb)

- Suppression indication can be generated by chip or fed externally to synchronize with off-chip compression CODEC

## 2.6 H.110 Interface

- Fully H.110 compatible

- H.110 Master and Slave capability

- Support of message channel

- Low Latency Loop-back (H.110 to H.110) of 128 channels (delay <= 375 us)</li>

- Redundant Adaptive Clock Recovery Circuit

- Support of 2/4/8 MHz bus speed in groups of 4 streams (8 separate groups)

- Generation of H.110 compatibility signals

- Dual ct\_netref signals

- Programmable fsync and TDM clocks for compatibility with other TDM buses

## 2.7 TDM data formats

- Support of plain PCM in u-law and A-law

- Translation between u-law and A-law on a per connection basis

- Support of ADPCM at 40, 32, 24 or 16 kbps

- Dual time-slot mode allows dynamic, error-free switching between PCM and ADPCM formats with silence suppression

- · Support of HDLC encapsulated mini-packets with asynchronous timing

- Support of HDLC streams ranging from 1 to 2046 time slots

- Support of HDLC packets with optional Address byte or word, optional Control byte and optional 16-bit CCITT-CRC

- · Routing of HDLC streams according to HDLC address byte, with up to 512 channels per stream

- Support of HDLC packets up to 1500 bytes in length

### 2.8 Link Interface

- Ethernet support for MII interface

- Support for Ethernet MIB

- ATM using twin UTOPIA interfaces allow secondary data SAR to be daisy-chained with device for data connections

- Packet over SONET support for 16-bit POS-PHY bus allowing interoperation with PHY at speeds up to 155 Mbps

- Support for packets of up to 1500 bytes (plus MAC header) in Ethernet and up to 65535 bytes in ATM and Packet Over SONET

- Secondary UTOPIA port can be used in all modes allowing the same data support architecture to be used independently of the link layer with minimal changes

- Transmission of voice to secondary port allows H.110/PCM bridging when coupled with AAL5 SAR

- Pin-out allows designs that support Ethernet, ATM and Packet over SONET with only software configuration deciding on the link layer used

## 3.0 CPU interface

The CPU module serves as the main external interface of the MT92210 device. Through the CPU interface, external agents can program the MT92210 registers, and read or write to the internal or external memories. The interface is programmable to allow interaction with various types of external agents.

#### 3.1 CPU Interface Description

The CPU interface is comprised of:

- Direct Access Select (DAS) as the MSB bit concatenated with a 15-bit address bus

- 16-bit data bus

- 2 interrupt signals

- associated control signals.

The CPU interface can be configured to operate in either Intel or Motorola mode, The MT92210 supports both 8-bit or 16-bit data bus and multiplexed or non-multiplexed address/data pins.

Internally, a subset of registers -- CPU Interface Registers (000h to 00Ah), can be accessed with very low latency. These registers contain address indirection and data indirection bits. The controlling CPU can choose to launch an indirect access through these registers. Indirect reads will complete in due time when the data is available, while indirect writes are performed almost instantaneously.

Direct accesses to the device can also be made. In these cases, accesses may take longer to complete. Any time a direct access is done, the CPU interface will delay the access using the **cpu\_rdy\_ndtack** pin until the access has completed internally. Note that direct writes are likely to complete very quickly as long as the write cache is not full.

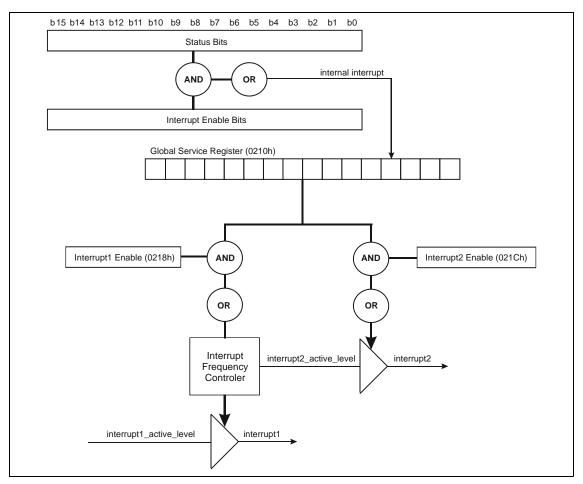

#### 3.2 CPU Interrupts

The CPU interface provides a programmable global interrupt capability. The interrupt signal are 'interrupt1' and 'interrupt2', pins Y5 and W4 respectively. Both interrupts have programmability to select their active polarity (open-collector drive) via registers 'interrupt1\_conf' and 'interrupt2\_conf', addresses 214h and 216h respectively. Interrupt1 provides the capability to program a minimum acceptable period between interrupts. The period is programmed in us units via the 'interrupt1\_conf' register. This provides a 'frequency interrupt controller' facility and mask the assertion of further interrupts until the specified period of time has elapsed. The mask period will start when the interrupt1\_treated[15] bit in the register 'interrupt\_treated' (address 212h) is set. When Interrupt2 is enabled it is always activated when an interrupt condition occurs.

The operation of the CPU interrupt network is common for all modules. When an interrupt is asserted, an interrupt flag is set to identify the module where the interrupt was generated. On completion of the ISR the interrupt must be cleared as the interrupt will remain asserted until it is de-asserted by the user. All Interrupt Enable Registers have a mirror Status Register. Hence, the bit positioning of the interrupt enables and the corresponding status bits are identical.

Interrupt pins are always tri-stated when inactive.

#### 3.2.1 Example Interrupt Flow

Upon the initialization of the Globe Interrupt pins the following methodology is adopted to identify the source of the interrupt. For this example Interrupt2 is employed and the CPU module will be the source of the interruption.

#### 3.2.1.1 Interrupt Initialization

Set interrupt polarity, register interrupt2\_conf[15:14], address 216h.

Enable Inetrrupt2 for the CPU module by setting bit 0 in inetrrupt2\_enble register (21Ch). The MT92210 will generate an interrupt on interrupt2 pin according to the modules enabled in inetrrupt2\_enable.

## 3.2.1.2 Interrupt Servicing

When interrupt2 is asserted ('inetrrupt2' pin):

- 1. Read the interrupt flags to ascertain the module raising the interrupt. The CPU module interrupt flag is located in register inetrrupt\_flags(210h), this bit is named cpureg\_interrupt\_active.

- 2. If the cpureg\_interrupt\_active bit is set, check the source of the CPU interrupt by reading the 'status0' register at 102h, either internal\_read\_timeout\_sar, and/or inmo\_read\_done, and/or interrnal\_read\_timeout\_net

- 3. To de-assert the interrupt the user must write 1 to corresponding bit in register 102h, ether internal\_read\_timeout\_sar, and/or inmo\_read\_done, and/or internal\_read\_timeout\_net. Only then will the interrupt be de-asserted.

Figure 2 - Internal Interrupt Network

#### 3.3 Intel/Motorola Interface

The MT92210 CPU interface supports both Intel and Motorola modes, in both 8-bit or 16-bit data bus and multiplexed or non-multiplexed address/data pins. The MT92210 supports 128 Megabytes of addressable space, therefore extended addressing is necessary. The CPU interface directly addresses four control words, delegated for indirection accessing. All of the register spaces in this section provide extremely fast CPU access times.

| 000h | Control Register         |  |  |

|------|--------------------------|--|--|

| 004h | Read/Write Data Register |  |  |

| 008h | Address High Register    |  |  |

| 00Ah | Address Low Register     |  |  |

| CPU_MODE<br>[3:0] | INTERFACE TYPE                                | ALE <sup>a</sup> | ADDRESS PIN <sup>b</sup>                      | DATA PIN    | DIRECT_<br>ACCESS |

|-------------------|-----------------------------------------------|------------------|-----------------------------------------------|-------------|-------------------|

| 0000              | Intel, 16 bit data bus,<br>non-multiplexed    | cpu_ale          | cpu_a[14:0]<br>(word address)                 | cpu_d[15:0] | cpu_a_das         |

| 0001              | Intel, 16 bit data bus,<br>multiplexed.       | cpu_ale          | cpu_d[15:1]<br>(word address)                 | cpu_d[15:0] | cpu_a_das         |

| 0010              | Intel, 8 data bus,<br>non-multiplexed         | cpu_ale          | cpu_a[14:0]<br>(byte address)                 | cpu_d[7:0]  | cpu_a_das         |

| 0011              | Intel, 8 data bus,<br>multiplexed             | cpu_ale          | cpu_a[14:8] &<br>cpu_d[7:0]<br>(byte address) | cpu_d[7:0]  | cpu_a_das         |

| 0100              | Motorola, 16 bit data bus,<br>non-multiplexed | cpu_ale          | cpu_d[14:0]<br>(word address)                 | cpu_d[15:0] | cpu_a_das         |

| 0101              | Motorola, 16 bit data bus,<br>multiplexed     | cpu_ale          | cpu_a[15:1]<br>(word address)                 | cpu_d[15:0] | cpu_a_das         |

| 0110              | Motorola, 8 bit data bus, non-multiplexed     |                  | cpu_a[14:0]<br>(byte address)                 | cpu_d[7:0]  | cpu_a_das         |

| 0111              | Motorola, 8 bit data bus,<br>multiplexed      | cpu_ale          | cpu_a[14:8] &<br>cpu_d[7:0]<br>(byte address) | cpu_d[7:0]  | cpu_a_das         |

| 1xxx              | Reserved                                      |                  |                                               |             |                   |

#### Table 2 - CPU Interface Mode Selection

a. The cpu\_ale pin is interpreted in all modes. However, it is not necessary in the non-multiplexed modes and can be tied to VCC.

b. The address placed on the cpu\_a[14:0] pin is a word address in 16-bit mode and a byte address in 8-bit mode. The address, when placed on the cpu\_d pins, is always a byte address.

| Field             | Bit   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| read_burst_length | 6:0   | RW   | 01h   | Number of words to prefetch when any read is executed. $00h = 128$ ; $01h= 1$ ; $02h = 2$ , etc. The higher this number, the longer the first read in a sequential series of reads will take; all successive accesses will be very quick and the overall read performance will be much better. This field should be set to 1 for individual (non-sequential) reads. Any read burst that crosses a 256 byte boundary will be broken up into two bursts. |

| Reserved          | 7     | RO   | 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| access_req        | 8     | PC   | 0     | Set by software when an extended access to the device must be<br>started. Cleared by hardware when the access is completed.<br>Used for extended indirect accesses only.                                                                                                                                                                                                                                                                               |

| extended_a[3:1]   | 11:9  | RW   | 000   | Extended address bits 3:1. <b>extended_a</b> [32:0] points to bytes. Used for extended indirect accesses only.                                                                                                                                                                                                                                                                                                                                         |

| write_enable      | 13:12 | RW   | 00    | Active high write enables. "00" = read access (indirect only);<br>"01" = write to lower byte; "10"=write to upper byte; "11"=write to<br>entire word. Used both in extended indirect and extended direct<br>write accesses. For all extended direct read accesses, this field<br>has no effect. For all byte wide extended direct accesses, this<br>field has no effect.                                                                               |

| extended_parity   | 15:14 | RW   | 00    | Parity bits used for both reads and writes. Used both in extended indirect and extended direct accesses.                                                                                                                                                                                                                                                                                                                                               |

## Table 3 - Control Register (000h)

| Field         | Bit  | Туре | Reset | Description                                                                                                                                                                                                                                                                 |

|---------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| extended_data | 15:0 | RW   |       | The 16 bits of data used in an extended indirect access to the chip. For<br>all extended direct accesses, this field is not used. During write<br>accesses, the write data is written here by the external CPU. During read<br>accesses, read data returns here to be read. |

#### Table 4 - Read/Write Data Register (004h)

| Field             | Bit   | Туре | Reset | Description                                                                                                                          |

|-------------------|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| extended_a[32:20] | 12:0  | RW   | 0000h | Extended address bits 32:20. <b>extended_a</b> [32:0] points to bytes. Used both for extended indirect and extended direct accesses. |

| Reserved          | 15:13 | RO   | 000   |                                                                                                                                      |

## Table 5 - Address High Register (008h)

| Field            | Bit  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                         |

|------------------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| extended_a[19:4] | 15:0 | RW   | 0000h | Extended address bits 19:4. <b>extended_a</b> [32:0] points to bytes.<br>Some bits in this register are not used in direct accesses. When<br>operating the CPU interface with a 16 bit data bus, only bits 19:16<br>are used. When operating the CPU interface with an 8-bit data<br>bus, only bits 19:15 are used. |

| Table 6 - | Address  | Low | Register | (00Ah) |

|-----------|----------|-----|----------|--------|

|           | Augu 633 |     | Register |        |

#### 3.3.1 Extended Indirect Access Procedures

Extended Indirect Accessing solely employees the registers 000h to 00Ah to access the 128 Megabytes of addressable memory space. The access address is written to registers 000h, 008h, and 00Ah. The MT92210 will read/write to that address and fetch /place the data value from/to register 004h. For all extended indirect accesses the cpu\_a\_das pin will be held low.

#### 3.3.1.1 Extended Indirect Writes

- 1. Write the upper address, **extended\_a**[32:20], to register 008h. This may not be required if previous value holds true.

- 2. Write the lower address, **extended\_a** [19:4], to register 00Ah. This may not be required if previous value holds true.

- 3. Write the write data, **extended\_data**[15,0], to register 004h.This may not be required if previous value holds true.

- 4. Write write\_enable, extended\_parity, access\_req='1' and extended\_a [3:1] in a single access to register 000h.

- 5. Read the **access\_req** bit located in the Control Register[8] to determine when the write cycle has completed.

The software will set access\_req[8] in register 000h. The hardware will reset the bit when the data write cycle has completed. Therefore, this bit can be polled to determine when the data write cycle has completed.

#### 3.3.1.2 Extended Indirect Reads

- 1. Write the upper address, **extended\_a**[32:20], to register 008h. This may not be required if previous value holds true.

- 2. Write the lower address, **extended\_a** [19:4], to register 00Ah. This may not be required if previous value holds true.

- 3. Write write\_enable="00", access\_req='1' and extended\_a [3:1] in a single access to register 000h.

- 4. Wait until access\_req is cleared, then read data from the data field **extended\_data[15,0]**, register 004h.

Optional parity check may be ascertained by performing a read on the extended\_parity[15,14], register 000h. The software will set access\_req[8] in register 000h and then the hardware will reset it when the data is ready to be read from register 004h.

#### 3.3.2 Extended Direct Access Procedures

Extended Direct Accessing employs the high and low address registers to perform page addressing. The address within the page is provided directly by the CPU address bus. Similarly, the data is fetched/placed directly on the CPU data bus.

The access address is written to registers 008h and 00Ah. This will perform only the page addressing. Upon assertion of the address within the page, the MT92210 will read/write the data with respect to that address. The

cpu\_a\_das pin is set when the data read/write occurs. When operating the CPU interface in direct mode with a 16-bit data bus, **extended\_a[19:16]**, are employed for the lower address word register 00Ah. However, when operating the CPU interface in direct mode with an 8-bit data bus, bits **[19:15]** are used for the lower address word.

### 3.3.2.1 Extended Direct Writes

- 1. Write the upper address, **extended\_a**[32:20], to register 008h. This may not be required if previous value holds true.

- 2. Write the lower address, **extended\_a** [19:16] or [19:15] to register 00Ah. The remaining bits [15:4] or [14:4] are ignored. This may not be required if previous value holds true.

- 3. Write **write\_enable**[13:12] (This may not be required if previous value holds true) and **extended\_parity**[15:14]. The extended parity write is optional.

- 4. Write data value to the address within the corresponding memory page with the cpu\_a\_das pin set.

#### 3.3.2.2 Extended direct reads

- 1. Write the upper address, **extended\_a**[32:20], to register 008h. This may not be required if previous value holds true.

- 2. Write the lower address, **extended\_a** [19:16] or [19:15] to register 00Ah. The remaining bits [15:4] or [14:4] are ignored. This may not be required if previous value holds true.

- 3. Assert the lower address within the memory page and fetch the read data with cpu\_a\_das set.

- 4. Read the **extended\_parity** field (optional), extended\_parity[15:14], register 000h.

## 3.4 MT92210 Reset Procedure

The reset procedure for the MT92210 requires several steps, mostly due to the fact that there are several levels of hardware and software resets in the chip. All register accesses in the reset procedure maybe performed in either Direct or Indirect mode. The procedure to configure the chip is as follows:

- 1. Assert the nreset pin for at least one 1 ms.

- 2. De-assert the nreset pin.

- 3. Clear nreset bit in Register 100h, set Bit 9 (mem\_oe), Bit 10 (ethernet\_enable, if necessary), Bit 13 (low\_latency\_cpu\_accesses) in Register 100h.

- 4. Configure upclk frequency in Register 10Ah.

- 5. Configure the fast\_clock PLLs in Register 110h, 170h, 172h.

- 6. Configure H.110 PLL in Register 174h.

- 7. Set proper divisors in Register 164h, 166h.

- 8. Reset Bit 9 (mem\_oe) in Register 100h.

- 9. Set Bit 0 (nreset\_registers) in CPU Register 100h.

- 10. Set active levels for interrupt pins in the Main Registers (214h, 216h).

- 11. Configure external memories in the Main Registers (230h, 232h, 234h, 236h, 240h).

- 12. Set Bit 1 (nreset\_chip) in CPU Register 100h.

- 13. Configure all the other registers.

- 14. Set Bit 2 (nreset\_network) in CPU Register 100h.

## 4.0 Network Interface

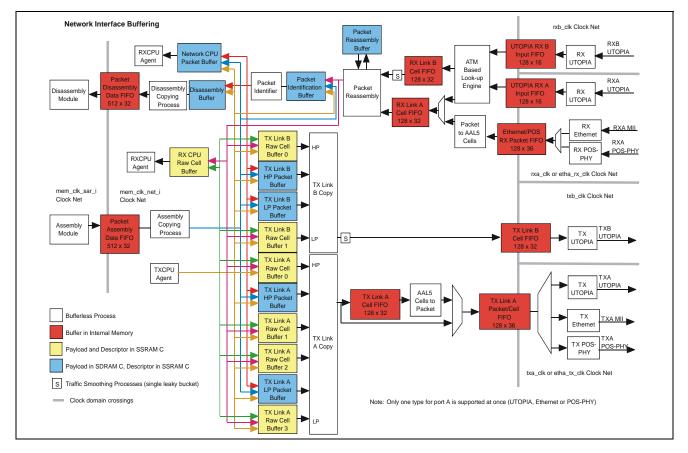

The objective of the MT92210 device is to transport voice information encapsulated in IP packets over network connections. Therefore, to allow maximum flexibility, it can support 3 different types of link interfaces: Ethernet, UTOPIA and Packet over SONET.

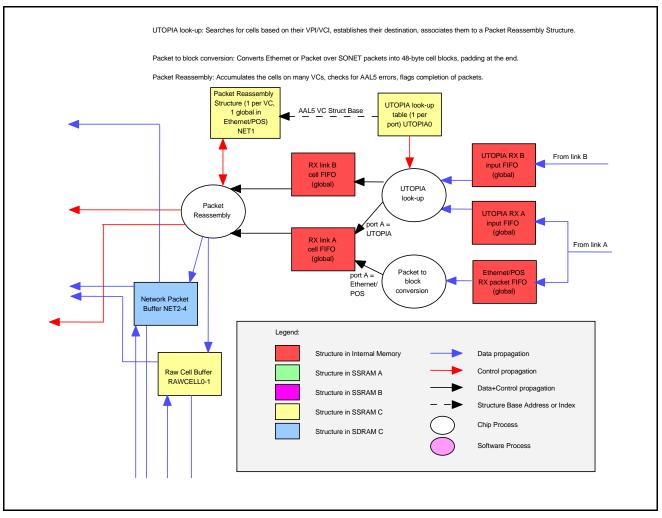

The network module of the chip is responsible for the identification and routing of packets, deciding which packets should be kept and treated as voice, which should be routed to the data packet buffer and which should be discarded.

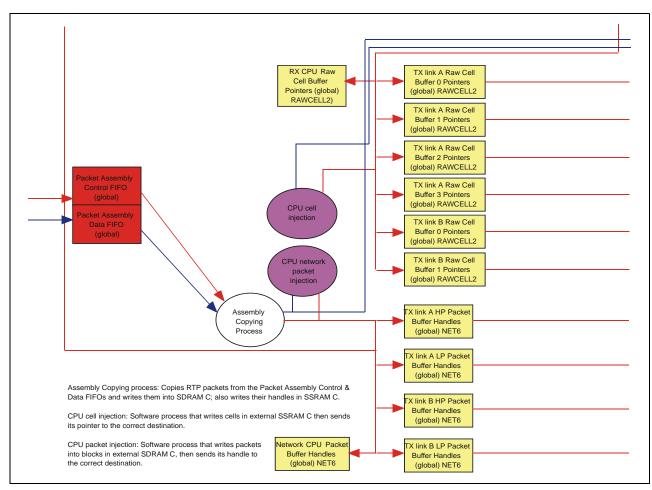

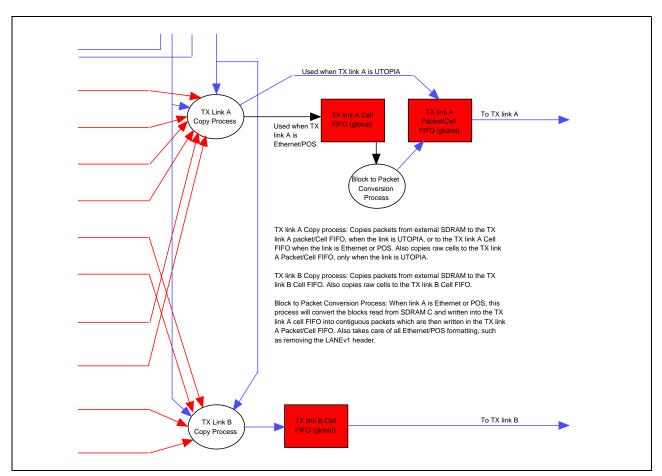

The network module accepts packets that are generated by the Packet Assembly module, as well as packets received from either of the two RX link ports. In the TX direction, it can send packets to the Packet Disassembly module, as well as to any of 4 TX link buffers: TX link A High-Priority, TX link A Low-Priority, TX link B High-Priority and TX link B Low-Priority.

It can also receive cells from its twin UTOPIA ports or from the TX CPU cell queue and can route them to the RX CPU cell buffer, or one of 4 TX link A cell queues (in priority) or one of 2 cell queues going to TX link B.

The following figure gives an overview of the data path in the network module, including all the queues that are used to buffer the data along the way:

Figure 3 - Network Interface Buffering

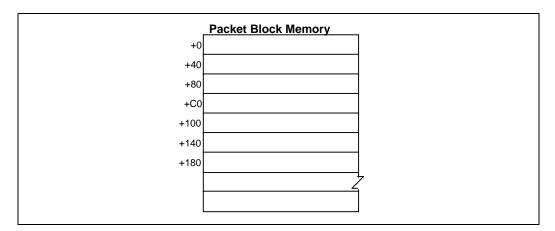

The module uses an external 32-bit SDRAM to buffer all the packets in transit and applies a linked list technique to allocate the blocks of memory in the SDRAM. Each packet, as it enters the module, is broken down into 48-byte payload blocks. These blocks are stored one at a time in SDRAM. A 19-bit link pointer links together the blocks that make up the packet. A link value of 00000h indicates that this block is the last one in the packet. Each block

occupies 64 bytes of SDRAM. The following figure 4 illustrates the format of blocks as they are kept in external SDRAM.

Figure 4 - Packet Block Memory and Format

|     | b31 b30 b29 b28 b27 b26 b25 b24 | b23 b22 b21 b20 b19 b18 b17 b16 | b15 b14 b13 b12 b11 b10 b9 b8 | b7 b6 b5 b4 b3 b2 b1 b0 |  |  |  |

|-----|---------------------------------|---------------------------------|-------------------------------|-------------------------|--|--|--|

| +0  | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +4  | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +8  | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +C  | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +10 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +14 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +18 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +1C | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +20 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +24 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +28 | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +2C | Payload                         | Payload                         | Payload                       | Payload                 |  |  |  |

| +30 |                                 | Multicast Sum                   | Forward Link Han              | ndle [24:6]             |  |  |  |

| +34 |                                 |                                 |                               |                         |  |  |  |

| +38 |                                 |                                 |                               |                         |  |  |  |

| +3C |                                 |                                 |                               |                         |  |  |  |

Figure 5 - Packet Block Format

| Field                  | Description                                                                                                                                                              |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Payload                | Packet payload. 48 bytes per block.                                                                                                                                      |

| Forward Link<br>Handle | Link to next block of packet. All zeros is invalid link (indicating end of packet).                                                                                      |

| Multicast Sum          | Used in TX. When packet is queued in multiple TX queues this is decremented each time the packet is sent and the TX queue that decrements it to 0 frees the cell memory. |

#### Table 7 - Packet Block Format Table

Packets are managed in 7 queues. Each queue corresponds to a possible destination of a packet within the module. In addition to the 4 queues containing packets for the 2 TX link outputs, there are also queues for packets going to the Disassembly module, the RX CPU FIFO in external memory and the Packet Identifier module. Each of these queues can be configured independently as to a maximum number of blocks it may contain This prevents a single overflowing port to grab the entire SDRAM and rob properly functioning ports of the memory they need to operate. The CPU agent can also seize blocks from the linked list to write its packets destined to the CPU. The CPU must free those blocks once it has read them.

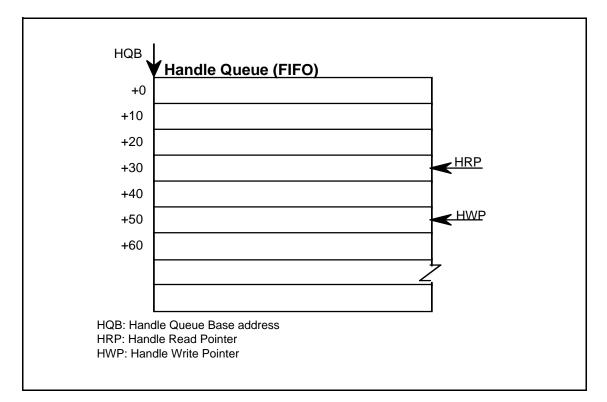

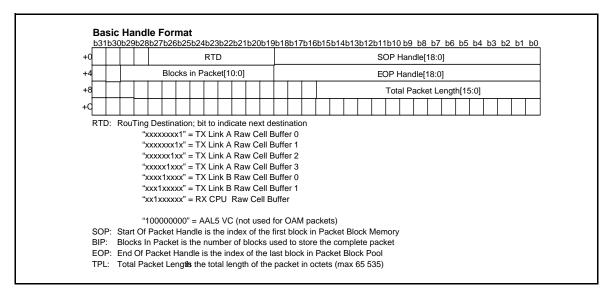

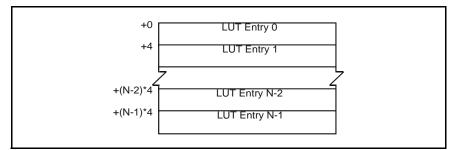

In addition to the block queues, there are also 7 handle queues, each handle queue being associated to the block queues. The handle queues contain the handles identifying the packets contained within the block queue. These handles detail all the characteristics of the packets and are passed between agents until they reach their final destination. Each handle queue can be programmed to a 2<sup>n</sup> size. Note that while handles may be copied to a new handle queues (especially after passing through the packet identification section), the blocks that contain the packet itself are never moved.

Each time a packet handle is added to a handle queue, the number of blocks it occupies is added to the block fill of the queue. Should the packet cause either the block fill or the handle fill to exceed their maximum values, the packet will be discarded and a per-queue status bit will be set in registers, indicating the error that has occurred. Note that the chip performs its own garbage collection, so no blocks in the linked list are ever left floating because the packet to which they were associated was lost.

The network interface also supports multicast functionality: a single packet can be sent to multiple destinations simultaneously. A notable exception is that if a packet is being sent to the packet identifier, it cannot be sent anywhere else.

A module called the packet handler manages all of these queues using a small internal memory shown in the next figure.

| ir         | 4000E00h in<br>internal memory |                 |                   |                                 |                             |        |     |         |        |        |        |        |

|------------|--------------------------------|-----------------|-------------------|---------------------------------|-----------------------------|--------|-----|---------|--------|--------|--------|--------|

|            | ,                              | +0              | Identific         | ation Buffer                    |                             | _      |     |         |        |        |        |        |

|            |                                | +10             | Network CP        | J Packet B                      | uffer                       |        |     |         |        |        |        |        |

|            |                                | +20             | Disasse           | mbly Buffer                     |                             |        |     |         |        |        |        |        |

|            |                                | +30             | TX L              | ink B HP                        |                             |        |     |         |        |        |        |        |

|            |                                | +40             | TX L              | ink A HP                        |                             |        |     |         |        |        |        |        |

|            |                                | +50             | TX L              | ink A LP                        |                             |        |     |         |        |        |        |        |

|            |                                | +60             | TX L              | ink B LP                        |                             |        |     |         |        |        |        |        |

|            |                                | +70             | Re                | served                          |                             |        |     |         |        |        |        |        |

|            |                                |                 | Handle Que        | le Descript                     | or                          |        |     |         |        |        |        |        |

| b31 b30 b2 | 29 b28 b27 b26 b25 b24         | b23 b22 b21 b20 | b19 b18 b17 b16 b | 15 b14 b13                      | b12 b11                     | b10 b9 | b8  | b7 b6   | b5     | b4 b3  | b2     | b1 b0  |

| +0         |                                | Blocks in Qu    | eue [18:0]        |                                 |                             | Handle | Que | ue Base | e Add  | ress & | Size [ | 20:11] |

| +4         | Handle Read Pointer [14:0]     |                 |                   |                                 | Handle Write Pointer [14:0] |        |     |         |        |        |        |        |

| +8         | Service Block Fill [18:2]      |                 |                   |                                 |                             |        | М   | ax Bloc | k Fill | [18:6] |        |        |

| -c         | Service Handle Fill [13:0]     |                 |                   | Max Monitored Block Fill [18:3] |                             |        |     |         |        |        |        |        |

## Figure 6 - Packet Handler Memory

| Field                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blocks in Queue                        | Total number of blocks currently contained in queue.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Handle Queue<br>Base Address &<br>Size | Indicates the base address of the handle queue as well as its size. The minimum queue size is 2K bytes, which is 128 handles. The maximum size is 256K bytes, which is 16K handles. The size is indicated by the lowest '1' in the field: for instance, if the field were xxxxxxxx1, this would represent a 2K byte buffer with a base address whose high bits are xxxxxxxxx. If the field were xxxxxx10000, this would represent a 32K byte buffer with a base address whose high bits are xxxxxxx. |

| Handle Read<br>Pointer                 | Pointer within the handle queue indicating the most recently read handle.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Handle Write<br>Pointer                | Pointer within the handle queue indicating the most recently written handle.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Service Block Fill                     | If the Blocks in Queue is less than or equal to this value, a service bit in registers can be set, indicating that the queue has gone below a certain fill. Both this and the handle fill must be valid for the service bit to be set.                                                                                                                                                                                                                                                               |

| Service Handle Fill                    | If the difference between Handle Write Pointer and Handle Read Pointer is less than or equal to this value, a service bit in registers can be set. Both this and the block fill must be valid for the service bit to be set.                                                                                                                                                                                                                                                                         |

| Max Block Fill                         | Indicates how many blocks, at most, the cache may contain before it overflows. This excludes the packet at the head of the queue, because it has been cached and will be treated shortly.                                                                                                                                                                                                                                                                                                            |

## Table 8 - Handle Queue Descriptor

Handle queues are stored in SSRAM C. Each handle occupies a block of 16 bytes. Handle format is shown in Figure 7.

Figure 7 - Handle Queue and Handle Format

RX packets received from the packet assembly module are contained in a 2 K byte internal memory. Once the full packet has been received, it is transferred to the SDRAM in block form. This internal buffer is large enough to contain an entire packet of up to 1500 bytes in length (+ link overhead). In addition to the packet memory, a small (128 bytes) handle memory contains the handles to these packets, indicating their length, base address and

г

destination. Packets from the packet assembly module can be routed to any one of the TX link buffers or to the packet identifier for internal loopback functionality.

Packets going to the disassembly module use a similar scheme: a 2 K-byte memory is used for the packets and a 128-byte memory for the handles.

Near the TX link layer interface, the network module uses 512-byte buffers to transfer packets between the SDRAM and the link layer interfaces. There are 4 buffers used for this purpose: 1 destined to TX link A, 1 to TX link B, 1 from RX link A and 1 from RX link B. These buffers can be smaller because the system operates flawlessly even if the entire packet is not contained in the buffer at any one time.

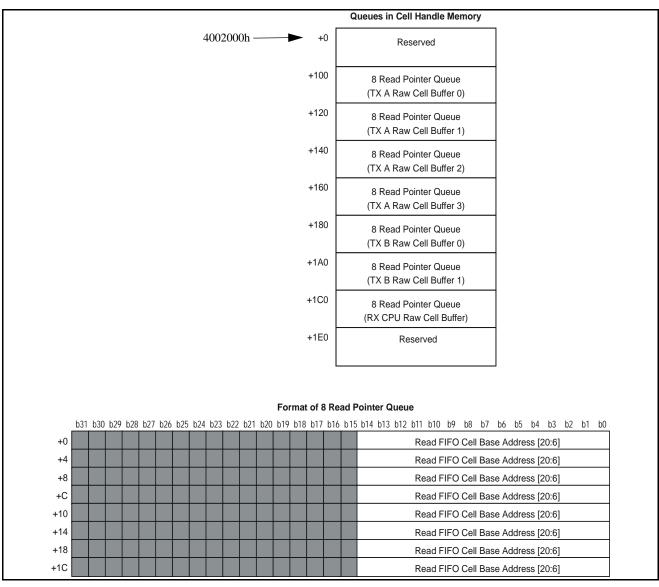

Cells contained in external memory are stored in the SSRAM and free cells are allocated as the various modules within the chip request them. The cells are also managed in a linked list, in the same way as the packet are. However, since each cell is individual (i.e. not part of a packet comprised of many blocks) they are only linked when they are free: when a cell is allocated and contains valid data, its link is not used. Whenever cells are allocated, the pointer to the cell is added to a cell queue, which contains all cells going to a given destination. The following figures indicate the format of raw cells in queues, depending on whether the cell is allocated or free:

|     | b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16 b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0 |  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| +0  | Cell Header[31:0]                                                                                                     |  |  |  |  |  |  |  |

| +4  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +8  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +C  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +10 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +14 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +18 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +1C | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +20 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +24 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +28 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +2C | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +30 |                                                                                                                       |  |  |  |  |  |  |  |

| +34 | Multicast Sum     PN     AAL5 VC Number [15:0]                                                                        |  |  |  |  |  |  |  |

| +38 |                                                                                                                       |  |  |  |  |  |  |  |

| +3C |                                                                                                                       |  |  |  |  |  |  |  |

| 1   |                                                                                                                       |  |  |  |  |  |  |  |

#### Figure 9 - Raw Cell Format (used cell)

| Field          | Description                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multicast Sum  | Used in TX. When Cell is queued in multiple TX queues this is decremented each time the cell is sent and the TX queue that decrements it to 0 frees the cell memory. |

| AAL5 VC Number | This points to a Packet Reassembly structure.                                                                                                                        |

| PN             | Port Number. Used in RX. Source port of this cell. Used to indicate, in the RX AAL0 FIFO, where cells originated. "00" = RX port A, "01" = RX port B; "11" = TX CPU. |

#### Table 9 - Fields and Description

| -   |                                                                                                                       |  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|     | b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16 b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0 |  |  |  |  |  |  |  |

| +0  | Cell Header[31:0]                                                                                                     |  |  |  |  |  |  |  |

| +4  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +8  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +C  | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +10 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +14 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +18 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

| +1C | Cell Payload                                                                                                          |  |  |  |  |  |  |  |

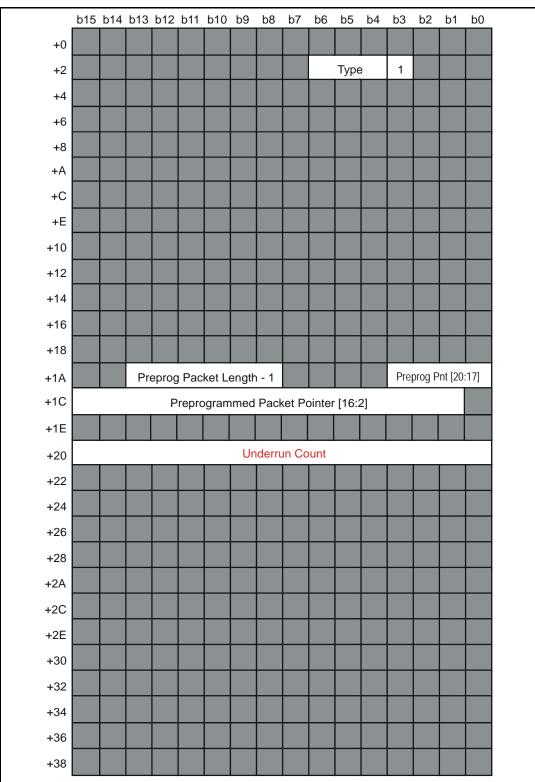

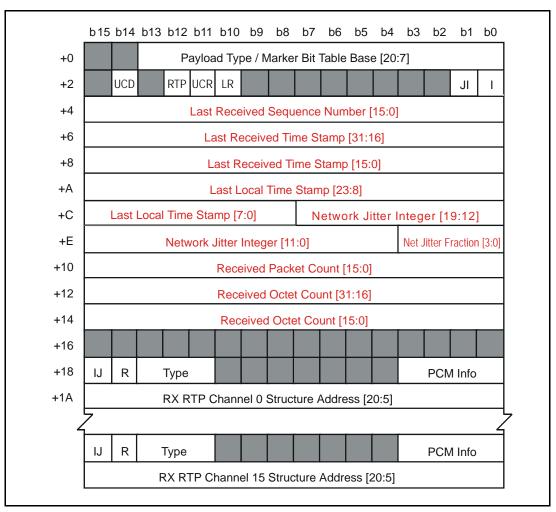

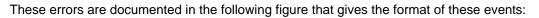

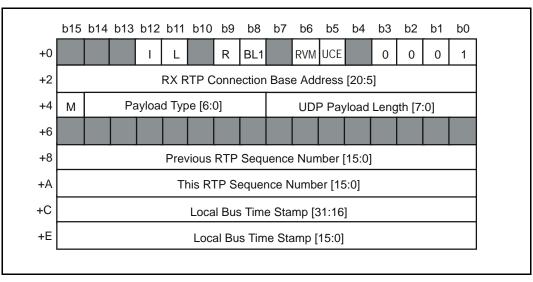

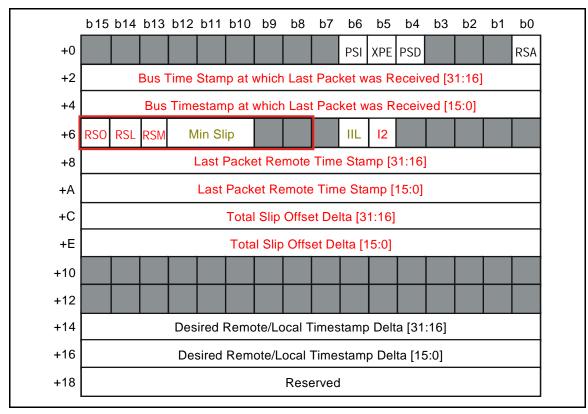

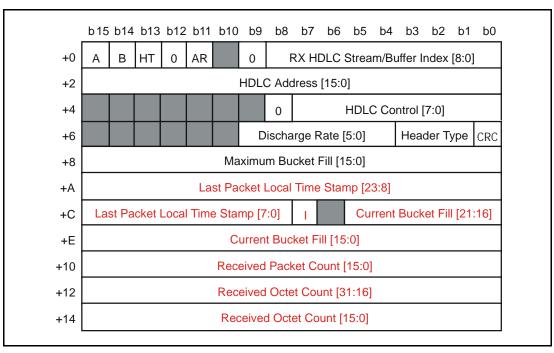

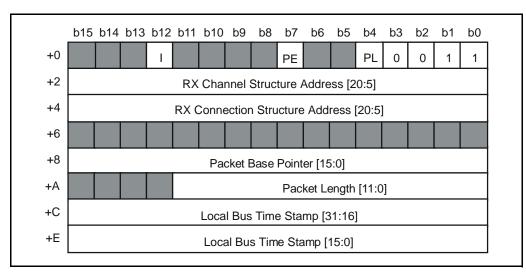

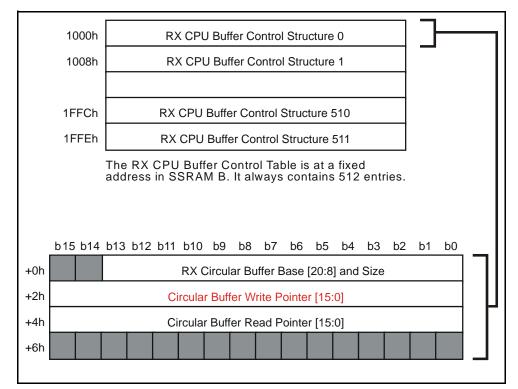

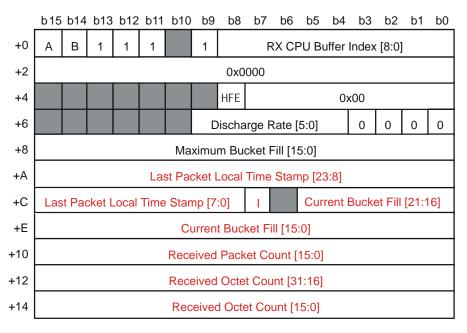

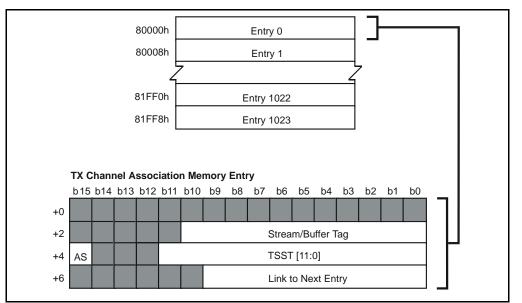

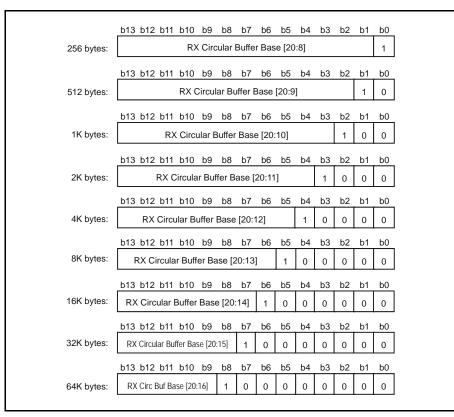

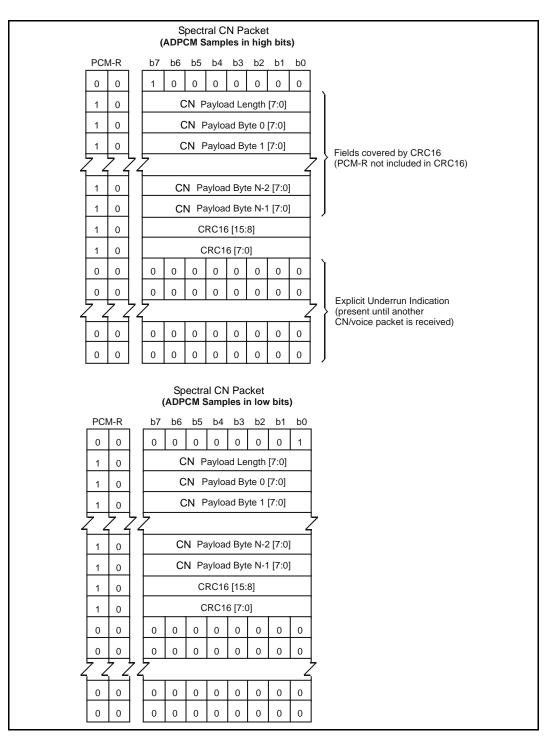

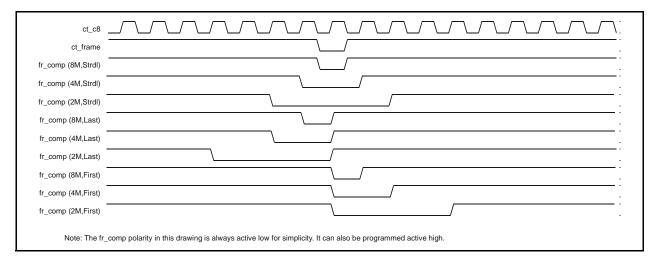

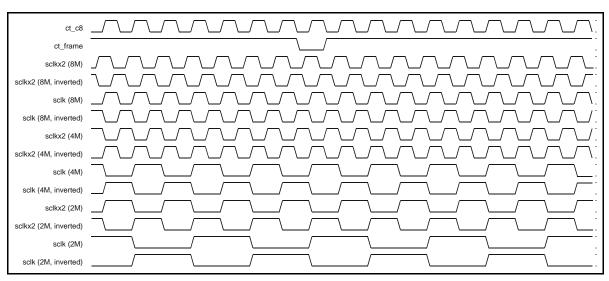

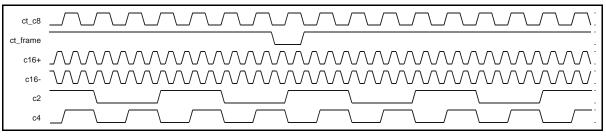

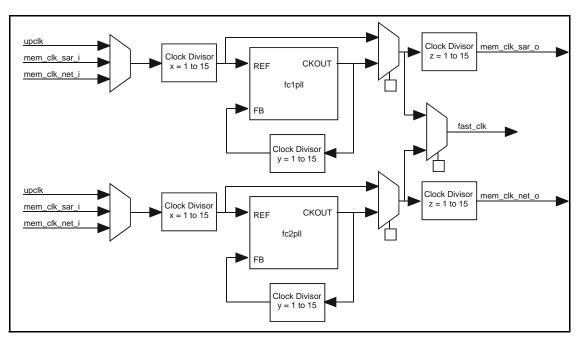

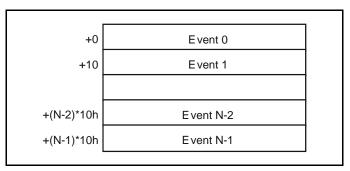

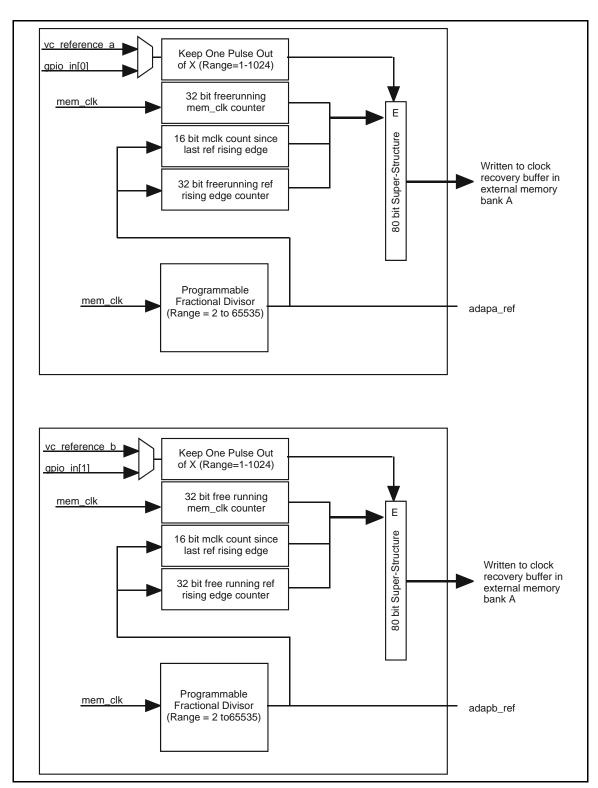

| +20 | Cell Payload                                                                                                          |  |  |  |  |  |  |  |