# MH88634CV-K Central Office Interface Circuit

Data Sheet

September 2003

#### Features

- Loop Start Trunk Interface

- 600Ω

- 2-4 Wire Conversion

- Line state Detection Outputs:

- Forward Loop

- Reverse Loop

- Ringing Voltage

- Switch Hook

- One Relay Driver

- On-Hook Reception

- · Small footprint area

- Meets FCC Part 68 Leakage Current Requirements

# Applications

Interface to Central Office for:

- PABX

- Key Telephone Systems

- Channel Bank

- Voice Mail

- Terminal Equipment

## Ordering Information

MH88634CV-K 21 Pin SIL Package

0°C to 70°C

- Digital Loop Carrier

- Optical Multiplexer

#### Description

The Zarlink MH88634CV-K Central Office Interface Circuit trunk provides a complete analog and signalling link between audio switching equipment and a telephone line.

The device is fabricated as a thick film hybrid incorporating various technologies for optimum circuit design and very high reliability.

The component design has been changed to improve the general performance of the part. It is also now capable of operating at a 24V battery and on hook reception.

The main difference between the MH88634BV-2 and MH88634CV-K is that SHK is active high on the CV-K.

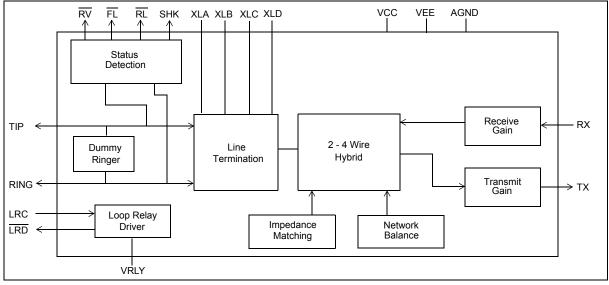

#### Figure 1 - Functional Block Diagram

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003, 2001 Zarlink Semiconductor Inc. All Rights Reserved.

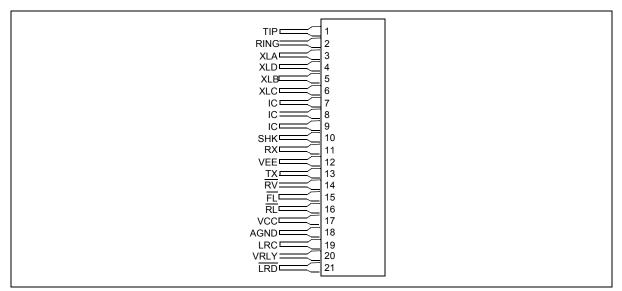

Figure 2 - Pin Connections

# Pin Description

| Pin # | Name | Description                                                                                                                                                                                                  |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | TIP  | Tip Lead. Connects to the "Tip" lead of a Telephone Line.                                                                                                                                                    |

| 2     | RING | Ring Lead. Connects to the "Ring" lead of a Telephone Line.                                                                                                                                                  |

| 3     | XLA  | <b>Loop Relay Contact A.</b> Connects to XLB through the Loop relay (K1) contacts when the relay is activated.                                                                                               |

| 4     | XLD  | <b>Loop Relay Contact D.</b> Connects to XLC through the loop relay (K1) contacts, when the relay is activated.                                                                                              |

| 5     | XLB  | <b>Loop Relay Contact B.</b> Connects to XLA through the loop relay (K1) contacts, when the relay is activated.                                                                                              |

| 6     | XLC  | <b>Loop Relay Contact C.</b> Connects to XLD through the loop relay (K1) contacts, when the relay is activated.                                                                                              |

| 7-9   | IC   | Internal Connection. No connection should be made to this pin.                                                                                                                                               |

| 10    | SHK  | <b>Switch Hook (Output).</b> A logic 0 indicates the presence of forward or reverse battery voltage when LRC is logic 0 and the presence of forward or reverse loop current when LRC is logic 1.             |

| 11    | RX   | Receive (Input). 4-Wire ground (AGND) referenced analog input.                                                                                                                                               |

| 12    | VEE  | Negative Supply Voltage5V DC                                                                                                                                                                                 |

| 13    | ТΧ   | Transmit (Output). 4-Wire ground (AGND) referenced analog output.                                                                                                                                            |

| 14    | RV   | <b>Ringing Voltage Detect (Output).</b> A logic low indicates that ringing voltage is across the Tip and Ring leads.                                                                                         |

| 15    | FL   | <b>Forward Loop Detect (Output).</b> In the on-hook state, a logic 0 output indicates that forward loop battery is present. In the off-hook state, a logic 0 indicates that forward loop current is present. |

| Pin # | Name | Description                                                                                                                                                                                                         |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16    | RL   | <b>Reverse Loop Detect (Output).</b> In the on-hook state, a logic 0 output indicates that reverse loop battery is present. In the off-hook state, a logic 0 output indicates that reverse loop current is present. |

| 17    | VCC  | Positive Supply Voltage. +5V DC                                                                                                                                                                                     |

| 18    | AGND | Analog Ground. 4-wire ground (AGND). Normally connected to system ground.                                                                                                                                           |

| 19    | LRC  | Loop Relay Control (Input). A logic 1 activates the Loop Relay Driver output (IRD).                                                                                                                                 |

| 20    | VRLY | Relay Positive Supply Voltage. Typically +5V. Connects to the relay supply voltage.                                                                                                                                 |

| 21    | LRD  | <b>Loop Relay Drive (Output).</b> Connects to the Loop Relay Coil. When LRC is at a logic 1 an open collector output at LRD sinks current and energizes the relay.                                                  |

## Pin Description (continued)

## Functional Description

The MH88634CV-K is a Central Office Interface Circuit (COIC). It is used to correctly terminate a Central Office 2wire telephone line. The device provides a signalling link and a 2-4 Wire line interface between the Telephone Line and subscriber equipment. The subscriber equipment can include Private Branch Exchanges (PBXs), Key Telephone Systems, Terminal Equipment, Digital Loop Carriers and Wireless Local Loops.

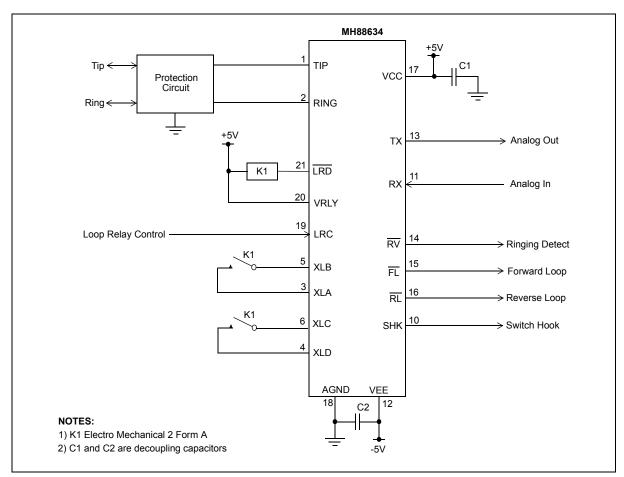

All descriptions assume that the device is connected as in the application circuit shown in Figure 3.

#### **Isolation Barrier**

The MH88634CV-K provides an isolation barrier which is designed to meet FCC Part 68 (November 1987) Leakage Current Requirements.

#### **External Protection Circuit**

An external Protection Circuit Device assists in preventing damage to the device and the subscriber's equipment, due to over-voltage conditions. The type of protection required is dependant upon the application and regulatory standards. Further details should be obtained from the specific country's regulatory body. Typically you will need lightening protection supplied by resettable fuses or PTC<sup>™</sup> and mains crossover protection via a foldover diode.

#### Suitable Markets

The MH88634CV-K has fixed  $600\Omega$  line and network balance impedance for use in North America and Asia.

#### Line Termination

When LRC is at a logic 1, LRD will sink current which energizes the Loop Relay (K1), connecting XLA to XLB and XLC to XLD. This places a line termination across Tip and Ring. The device can be considered to be in an off-hook state and DC loop current will flow. The line termination consists of a DC resistance and an AC impedance. When LRC is at a logic 0, the line termination is removed from across Tip and Ring.

An internal Dummy Ringer is permanently connected across Tip and Ring which is a series AC load of  $(17k\Omega+330nF)$ . This represents a mechanical telephone ringer and allows ringing voltages to be sensed. This load can be considered negligible when the line has been terminated.

Depending on the Network Protocol being used the Line Termination can terminate an incoming call, seize the line for an outgoing call, or if applied and disconnected at the correct rate can be used to generate dial pulse signals.

The DC line termination circuitry provides the line with an active DC load termination which is equivalent to a DC resistance of  $280\Omega$  at 20mA.

## Ringing Equivalent Number

The Ringing Equivalent Number (REN) is application specific. See the governing regulatory body specification for details.

#### Input Impedance

The input impedance (Zin) is the AC impedance that the MH88634CV-K places across Tip and Ring to terminate the Telephone line. This is fixed at  $600\Omega$ .

#### Network Balance Impedance

The MH88634CV-K Network Balance Impedance is fixed at  $600\Omega$ .

#### 2-4 Wire Conversion

The device converts the balanced 2-Wire input, presented by the line at Tip and Ring, to a ground referenced signal at TX. This circuit operates with or without loop current; signal reception with no loop current is required for on-hook reception enabling the detection of Caller Line Identification (CLI) signals.

Conversely, the device converts the ground referenced signal input at RX, to a balanced 2-Wire signal across Tip and Ring.

The 4-Wire side (TX and RX) can be interfaced to a filter/codec, such as the Zarlink MT896X, for use in digital voice switched systems.

During full duplex transmission, the signal at Tip and Ring consists of both the signal from the device to the line and the signal from the line to the device. The signal input at RX, being sent to the line, must not appear at the output TX. In order to prevent this, the device has an internal cancellation circuit. The measure of attenuation is Transhybrid Loss (THL).

#### Transmit and Receive Gain

The Transmit Gain of the device is the gain from the balanced signal across Tip and Ring to the ground referenced signal at TX. It is set at 0dB.

The Receive Gain of the device is the gain from the ground referenced signal at RX to the balanced signal across Tip and Ring. It is set at -2dB.

#### Supervision Features

#### Line Status Detection Outputs

The MH88634CV-K supervisory circuitry provides the signalling status outputs which are monitored by the system controller. The supervisory circuitry is capable of detecting: Ringing Voltage; Forward and Reverse loop battery; Forward and Reverse loop current; and Switch Hook.

#### Ringing Voltage Detect Output (RV)

The  $\overline{\text{RV}}$  output provides a logic 0 when ringing voltage is detected across Tip and Ring. This detector includes a filter which ensures that the output toggles at the ringing cadence and not at the ringing frequency. Typically this

output switches to a logic 0 after 50ms of applied ringing voltage and remains at a logic 0 for 50ms after ringing voltage is removed.

RV shall not toggle during ringing.

#### Forward Loop and Reverse Loop Detect Outputs (FL & RL)

The FL output provides a logic 0 when either forward loop battery or forward loop current is detected, that is the Ring pin voltage is more negative than the Tip pin voltage.

The RL output provides a logic 0 when either reverse loop battery or reverse loop current is detected, that is the Tip pin voltage is more negative than the Ring pin voltage.

#### Switch Hook (SHK)

The SHK output is active if either forward loop or reverse loop current is detected, or if forward or reverse battery voltage is detected.

#### **Control Input**

The MH88634CV-K accepts a control signal from the system controller at the Loop Relay Control input (LRC). This energizes the relay drive output Loop Relay Drive (LRD). The output is active low and has an internal clamp diode to VRLY.

The intended use of this relay driver is to add and remove the Line Termination from across Tip and Ring, as shown in Figure 3.

If this Control input and the Supervisory Features are used as indicated in Figure 3, Loop-Start Signalling can be implemented.

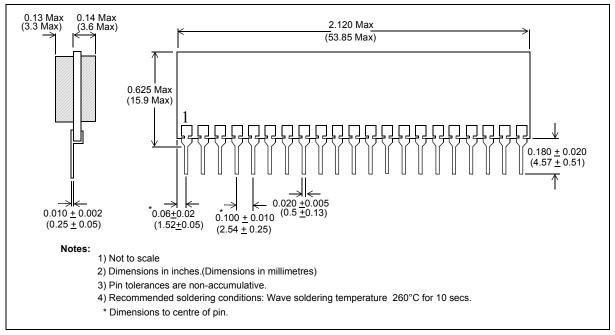

#### Mechanical Data

See Figure 9 for details of the mechanical specification.

Figure 3 - Typical LS Application Circuit

#### Absolute Maximum Ratings\*

|   | Parameters            | Sym               | Min  | Мах  | Units | Comments                                  |

|---|-----------------------|-------------------|------|------|-------|-------------------------------------------|

| 1 | DC Supply Voltages    | V <sub>CC</sub>   | -0.3 | 7    | V     |                                           |

|   |                       | V <sub>EE</sub>   | 0.3  | -7   | V     |                                           |

| 2 | DC Ring Relay Voltage | V <sub>RLY</sub>  | -0.3 | 18   | V     |                                           |

| 3 | Storage Temperature   | т <sub>S</sub>    | -55  | +125 | °C    |                                           |

| 4 | Ring Trip Current     | I <sub>TRIP</sub> |      | 180  | mArms | 250ms 10% duty cycle or 500ms single shot |

\*Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### **Recommended Operating Conditions**

|   | Parameters            | Sym                                | Min           | Тур <sup>‡</sup> | Max           | Units  |

|---|-----------------------|------------------------------------|---------------|------------------|---------------|--------|

| 1 | DC Supply Voltages    | V <sub>CC</sub><br>V <sub>EE</sub> | 4.75<br>-4.75 | 5.0<br>-5.0      | 5.25<br>-5.25 | V<br>V |

| 2 | DC Ring Relay Voltage | V <sub>RLY</sub>                   |               | 5.0              | 15            | V      |

| 3 | Operating Temperature | T <sub>OP</sub>                    | 0             | 25               | 70            | °C     |

$\ddagger$  Typical figures are at 25°C with nominal  $\pm5V$  supplies and are for design aid only.

s

#### **DC Electrical Characteristics<sup>†</sup>**

|   |           | Characteristics                                               | Sym                                | Min        | Тур <sup>‡</sup> | Max      | Units    | Test Conditions                                  |

|---|-----------|---------------------------------------------------------------|------------------------------------|------------|------------------|----------|----------|--------------------------------------------------|

| 1 |           | Supply Current                                                | I <sub>CC</sub><br>I <sub>EE</sub> |            | 5<br>2.5         | 13<br>13 | mA<br>mA |                                                  |

| 2 |           | Power Consumption                                             | PC                                 |            | 37.5             | 137      | mW       | V <sub>BAT</sub> not connected                   |

| 3 | FLIR KIRV | Low Level Output Voltage<br>High Level Output Voltage         | V <sub>OL</sub><br>V <sub>OH</sub> | 2.4        |                  | 0.5      | V<br>V   | I <sub>OL</sub> = 4mA<br>I <sub>OH</sub> = 0.4mA |

| 4 | LRD       | Sink Current, Relay to V <sub>CC</sub><br>Clamp Diode Current | I <sub>OL</sub><br>I <sub>CD</sub> | 100<br>150 |                  |          | mA<br>mA | V <sub>OL</sub> = 0.5V not<br>continuous, LRC=5V |

| 5 | LRC       | Low Level Input Voltage<br>High Level Input Voltage           | V <sub>IL</sub><br>V <sub>IH</sub> | 3.20       |                  | 0.8      | V<br>V   |                                                  |

| 6 | LRC       | High Level Input Current<br>Low Level Input Current           | 빌                                  |            |                  | 40<br>40 | μA<br>μA | V <sub>IH</sub> = 5.0V                           |

† Electrical Characteristics are over recommended operating conditions unless otherwise stated.

‡ Typical figures are at 25°C with nominal ±5V supplies and are for design aid only.

#### Loop Electrical Characteristics<sup>†</sup>

|   | Characteristics                                                         | Sym | Min        | Тур‡ | Мах       | Units            | Test Conditions                                         |

|---|-------------------------------------------------------------------------|-----|------------|------|-----------|------------------|---------------------------------------------------------|

| 1 | Ringing Voltage                                                         | VR  | 40         | 90   | 150       | V <sub>rms</sub> | 17 to 68Hz                                              |

| 2 | Operating Loop Current                                                  |     | 16         |      | 85        | mA               |                                                         |

| 3 | Off-Hook DC Resistance                                                  |     |            | 270  | 280       | Ω                | @ 20mA Note 1                                           |

| 4 | Leakage Current (Tip-Ring to AGND)                                      |     |            |      | 7         | mArms            | @ 1000VAC                                               |

| 5 | SHK & FL Threshold<br>Tip-Ring (On-hook)<br>Tip-Ring Current (Off-Hook) |     | 12<br>10.5 |      | 21<br>15  | Vdc<br>mA        | $\frac{\overline{LRC}}{LRC} = 0V$ $\overline{LRC} = 5V$ |

| 6 | SHK & RL Threshold<br>Tip-Ring (On-Hook)<br>Tip-Ring Current (Off-Hook) |     | 12<br>10.5 |      | 21<br>-15 | Vdc<br>mA        | $\frac{\overline{LRC}}{LRC} = 0V$ $\overline{LRC} = 5V$ |

+ Electrical Characteristics are over recommended operating conditions unless otherwise stated. + Typical figures are at 25°C with nominal  $\pm$ 5V supplies and are for design aid only. Note 1: Maximum figure of 282Ω at 0°C

# **AC Electrical Characteristics<sup>†</sup>**

|    | Characteristics                                         | Symbol | Min            | Тур‡           | Мах          | Units          | Test Conditions                                                                |

|----|---------------------------------------------------------|--------|----------------|----------------|--------------|----------------|--------------------------------------------------------------------------------|

| 1  | 2-wire Input Impedance                                  | Zin    |                | 600            |              | Ω              | -2 Variant                                                                     |

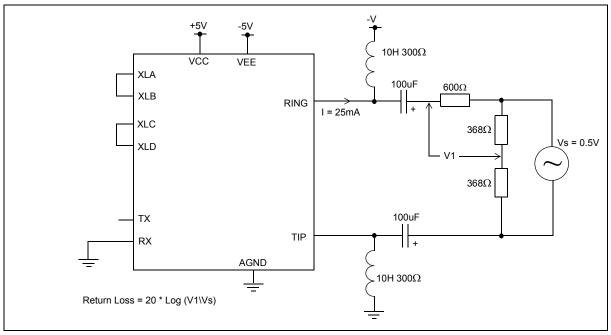

| 2  | Return Loss at 2-wire                                   | RL     | 20             | 29             |              | dB             | Test Circuit as Fig 6<br>200-3400 Hz                                           |

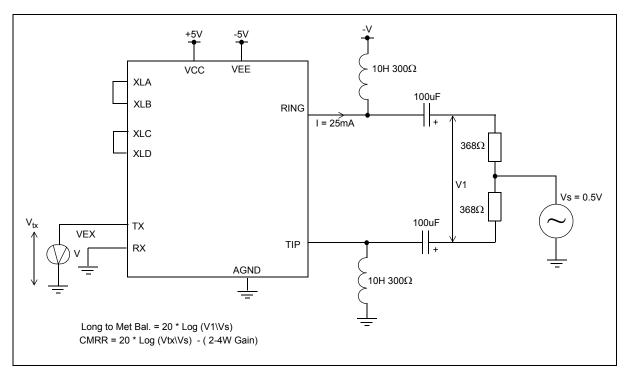

| 3  | Longitudinal to Metallic<br>Balance                     |        | 58<br>55<br>53 | 60<br>60<br>58 |              | dB<br>dB<br>dB | Test Circuit as Fig 7<br>200Hz<br>1000Hz<br>3400Hz                             |

| 4  | Transhybrid Loss                                        | THL    | 20             | 27             |              | dB             | 200-3400Hz                                                                     |

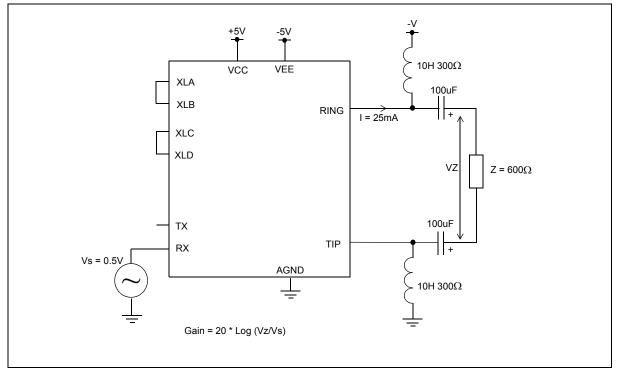

| 5  | Gain, 2 wire to TX<br>Relative Gain                     |        | -0.25<br>-0.3  | 0<br>0         | 0.25<br>0.3  | dB<br>dB       | Test Circuit as Fig 4<br>1000Hz<br>200-3400Hz                                  |

| 6  | Gain, Rx to 2 wire<br>Relative Gain                     |        | -2.25<br>-0.3  | -2<br>0        | -1.75<br>0.3 | dB<br>dB       | Test Circuit as Fig 5<br>1000Hz<br>200-3400Hz                                  |

| 7  | Input impedance at RX                                   |        |                | 10             |              | kΩ             |                                                                                |

| 8  | Output impedance at TX                                  |        |                | 5              |              | Ω              |                                                                                |

| 9  | Signal Overload Level<br>at 2-wire<br>at TX             |        | 4.0<br>1.7     |                |              | dBm<br>dBm     | % THD <u>&lt;</u> 5% @ 20mA                                                    |

| 10 | Total Harmonic Distortion<br>at 2-wire                  | THD    |                |                | 1.0          | %              | Input 0.5V, 1kHz @<br>RX                                                       |

|    | at TX                                                   |        |                |                | 1.0          | %              | Input 0.5V, 1kHz @<br>Tip-Ring                                                 |

| 11 | Idle Channel Noise<br>at 2-Wire<br>at TX                | NC     |                | 15<br>15       | 16.5<br>16.5 | dBrnC<br>dBrnC |                                                                                |

| 12 | Power Supply Rejection Ratio at 2-wire and TX           | PSRR   |                |                |              |                | Ripple 0.1V, 1kHz                                                              |

|    | V <sub>CC</sub><br>V <sub>EE</sub>                      |        | 25<br>25       | 48<br>47       |              | dB<br>dB       |                                                                                |

| 13 | On-Hook Gain, 2-Wire to TX<br>Relative to Off-Hook Gain |        | -1             | 0              | 1            | dB             | Input 1000Hz @ 0.5V                                                            |

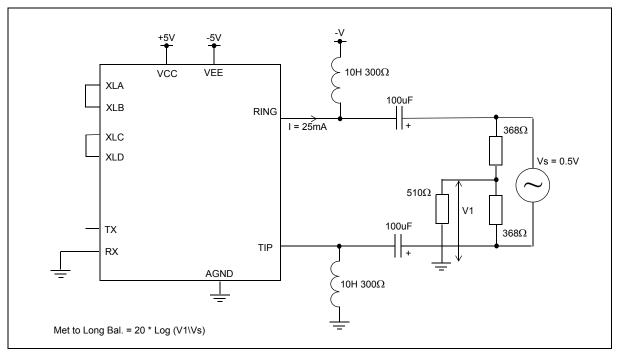

| 14 | Met. to Long. Balance                                   |        |                |                |              |                | Test Circuit as Fig. 8                                                         |

|    | -2 Variant                                              |        | 60<br>40       | 62<br>48       |              |                | 200-1000Hz<br>1000-3400Hz                                                      |

|    | -4 Variant                                              |        | 55<br>40       | 62<br>48       |              |                | 200-1000Hz<br>1000-3400Hz                                                      |

| 15 | Common Mode Rejection<br>Ratio                          | CMRR   | 48             | 55             |              | dB             | Test Circ <u>uit</u> as Fig. 7<br>1000Hz, FL = 0V,<br>I <sub>Loop</sub> = 25mA |

† Electrical Characteristics are over recommended operating conditions unless otherwise stated.

‡ Typical figures are at 25°C with nominal ±5V supplies and are for design aid only.

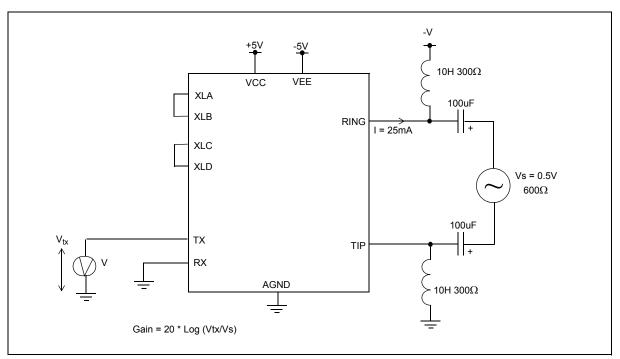

Figure 4 - 2-4 Wire Gain Test Circuit

Figure 5 - 4-2 Wire Gain Test Circuit

Figure 6 - Return Loss Test Circuit

Figure 7 - Longitudinal to Metallic Balance and CMRR Test Circuit

Figure 8 - Metallic to Longitudinal Balance Test Circuit

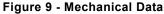

Figure 10 - MH88634CV-KT-2 Mechanical Information

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE