### **General Description**

The MAX8710/MAX8711/MAX8712/MAX8761 offer complete linear-regulator power-supply solutions for thin-film transistor (TFT) liquid-crystal-display (LCD) panels used in LCD monitors and LCD TVs. All four devices include a high-performance AVDD linear regulator, a positive charge-pump regulator, a negative charge-pump regulator, and built-in power-up sequence control. The MAX8710/MAX8711/MAX8761 also include a high-current operational amplifier. Additionally, the MAX8710/MAX8761 provide logic-controlled high-voltage switches to control the positive charge-pump output.

The linear regulator directly steps down the input voltage to generate the supply voltage for the source-driver ICs (AVDD). The two built-in charge-pump regulators are used to generate the TFT gate-on and gate-off supplies. The high-current operational amplifier is typically used to drive the LCD backplane (VCOM) and features high output current (150mA), fast slew rate (12V/µs), and wide bandwidth (12MHz). Its rail-to-rail inputs and output maximize flexibility.

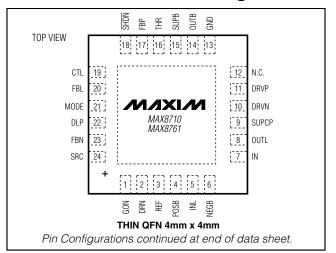

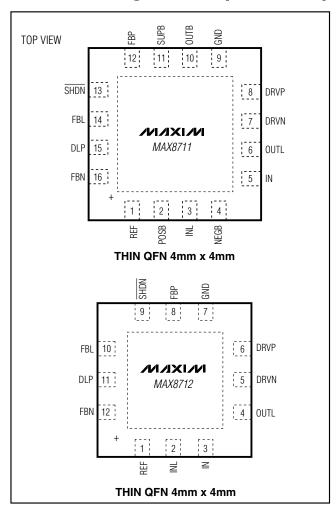

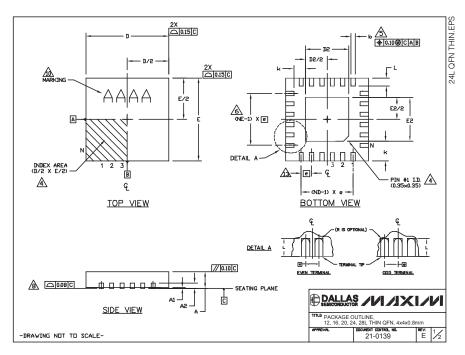

The MAX8710/MAX8761 are available in a 24-pin thin QFN package, the MAX8711 is available in a 16-pin thin QFN package, and the MAX8712 is available in a 12-pin thin QFN package. All three packages are 4mm x 4mm with a maximum thickness of 0.8mm for ultra-thin LCD panel design. The MAX8710/MAX8711/MAX8712 operate over the -40°C to +100°C temperature range and the MAX8761 operates over the -40°C to +85°C range.

### **Applications**

LCD Monitor Panel Modules LCD TV Panel Modules

### Pin Configurations

Dual Mode is a trademark of Maxim Integrated Products, Inc.

### **Features**

- High-Performance Linear Regulator 1.6% Output Accuracy Works with Small Ceramic Output Capacitors Fast Transient Response Foldback Current Limit

- ♦ 50mA Negative Regulated Charge Pump

- ♦ 20mA Positive Regulated Charge Pump with Adjustable Delay

- ♦ Built-In Power-Up Sequence

- ♦ High-Current Operational Amplifier (MAX8710/MAX8711/MAX8761) ±150mA Output Short-Circuit Current 12V/µs Slew Rate 12MHz, -3dB Bandwidth Rail-to-Rail Inputs/Output

- ◆ Dual-Mode™ High-Voltage Switches (MAX8710/MAX8761)

- **♦ Thermal Protection**

- **♦ Latched Fault Protection with Timer**

### Ordering Information

| PART                | TEMP RANGE      | PIN-PACKAGE              | PKG<br>CODE |

|---------------------|-----------------|--------------------------|-------------|

| <b>MAX8710</b> ETG+ | -40°C to +100°C | 24 Thin QFN<br>4mm x 4mm | T2444-4     |

| MAX8711ETE+         | -40°C to +100°C | 16 Thin QFN<br>4mm x 4mm | T2444-4     |

| <b>MAX8712</b> ETC+ | -40°C to +100°C | 12 Thin QFN<br>4mm x 4mm | T2444-4     |

| <b>MAX8761</b> ETG+ | -40°C to +85°C  | 24 Thin QFN<br>4mm x 4mm | T2444-4     |

+Denotes lead-free package.

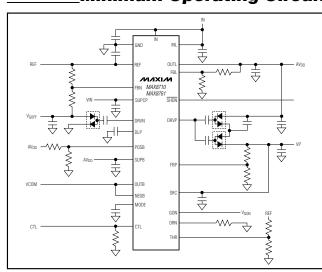

### Minimum Operating Circuit

**Maxim Integrated Products**

### **ABSOLUTE MAXIMUM RATINGS**

| CTL, FBL, FBP, FBN, SHDN, REF |                                     |

|-------------------------------|-------------------------------------|

| MODE, DLP to GND              | 0.3V to V <sub>REF</sub> + 0.3V     |

| IN, INL to GND                | 0.3V to +28V                        |

| SUPCP, SUPB to GND            | 0.3V to +14V                        |

| OUTL (MAX8710/MAX8761)        | 0.3V to +28V                        |

| OUTL (MAX8711/MAX8712)        |                                     |

| POSB, OUTB, NEGB to GND       |                                     |

| DRVN, DRVP (MAX8710/MAX87     |                                     |

| DRVN, DRVP (MAX8711/MAX87     | 12)0.3V to (V <sub>IN</sub> - 0.3V) |

| SRC to GND                    | 0.3V to +30V                        |

| GON, DRN to GND               | 0.3V to V <sub>SRC</sub> + 0.3V     |

| DRN to GON                    | 30V to +30V                         |

|                               |                                     |

| OUTB Maximum Continuous Output Current DRVP RMS Output Current |                |

|----------------------------------------------------------------|----------------|

| DRVN RMS Output Current                                        |                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )          |                |

| 24-, 16-, and 12-Pin Thin QFN 4mm x 4mm                        |                |

| (derate 16.9mW/°C above +70°C)                                 | 1349mW         |

| Operating Temperature Range                                    |                |

| MAX8710/MAX8711/MAX8712                                        | 40°C to +100°C |

| MAX8761                                                        | 40°C to +85°C  |

| Junction Temperature                                           | +150°C         |

| Storage Temperature Range                                      |                |

| Lead Temperature (soldering, 10s)                              | +300°C         |

|                                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                  | CONDITIONS                                                                                             | MIN  | TYP     | MAX  | UNITS |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------|------|---------|------|-------|--|

| IN Operating Supply Range                  |                                                                                                        | 8    |         | 28   | V     |  |

| INI Ovigen and Overgent                    | SHDN = GND                                                                                             |      | 0.2     | 0.4  |       |  |

| IN Quiescent Current                       | <u>SHDN</u> = 3.3V                                                                                     |      |         | 2.5  | - mA  |  |

| Duration to Trigger Fault Condition        | 2 <sup>16</sup> oscillator clock cycles                                                                |      | 44      |      | ms    |  |

| REF Output Voltage                         | -10μA < I <sub>REF</sub> < 1mA (excluding internal load)                                               | 4.9  | 5.0     | 5.1  | V     |  |

| SUPCP Input Supply Range                   |                                                                                                        | 2.7  |         | 13.2 | V     |  |

| Charge-Pump Regulators Operating Frequency |                                                                                                        | 1275 | 1500    | 1725 | kHz   |  |

| Thermal Shutdown                           | Rising temperature, 15°C hysteresis                                                                    |      | +160    |      | °C    |  |

| LINEAR REGULATOR                           |                                                                                                        |      |         |      | •     |  |

| INL Operation Supply Range                 | V <sub>OUTL</sub> < V <sub>INL</sub>                                                                   | 7    |         | 28   | V     |  |

| Draw out Valtage                           | I <sub>OUTL</sub> = 50mA (MAX8710/MAX8711/MAX8712)                                                     | 150  |         | 300  | mV    |  |

| Dropout Voltage                            | I <sub>OUTL</sub> = 200mA (MAX8761)                                                                    | 200  | 200 400 |      |       |  |

| FBL Regulation Voltage                     | I <sub>OUTL</sub> = 50mA                                                                               | 2.46 | 2.50    | 2.54 | V     |  |

| FBL Input Bias Current                     | V <sub>FBL</sub> = 2.5V                                                                                |      |         | 50   | nA    |  |

| FBL Fault Trip Level                       | Falling edge                                                                                           | 1.92 | 2.00    | 2.08 | V     |  |

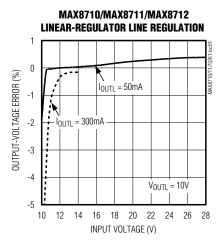

| FBL Line-Regulation Error                  | V <sub>INL</sub> = V <sub>IN</sub> = 10.8V~13.2V, V <sub>OUTL</sub> = 10V,<br>I <sub>OUTL</sub> = 50mA |      |         | 15   | mV    |  |

|                                            | V <sub>INL</sub> = V <sub>IN</sub> = 10V~28V, V <sub>OUTL</sub> = 9V, I <sub>OUTL</sub> = 50mA         |      | 10      |      | 1     |  |

| Bandwidth                                  | Guaranteed by design                                                                                   | 1000 |         |      | kHz   |  |

| Maximum OUTL Current                       | V <sub>FBL</sub> = 2.4V (MAX8710/MAX8711/MAX8712)                                                      | 300  |         |      | Λ     |  |

| Maximum OOTL Current                       | V <sub>FBL</sub> = 2.4V (MAX8761)                                                                      | 500  |         |      | mA    |  |

| OUTL Soft-Start Period                     | 2 <sup>12</sup> oscillator clock cycles in a 7-bit DAC                                                 |      | 2.73    |      | ms    |  |

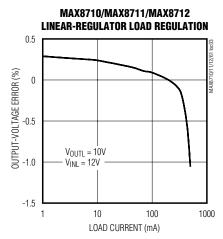

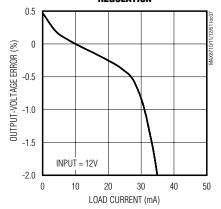

| OUTL Load Regulation                       | V <sub>IN</sub> = 12V, 5mA < I <sub>OUT</sub> < 300mA<br>(MAX8710/MAX8711/MAX8712)                     |      | _       | 2    | %     |  |

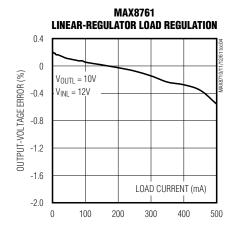

|                                            | V <sub>IN</sub> = 12V, 5mA < I <sub>OUT</sub> < 500mA (MAX8761)                                        |      | 2       |      |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                 | CONDITIONS                                                                                                                 | MIN                     | TYP                           | MAX   | UNITS |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|-------|-------|

| OPERATIONAL AMPLIFIER (MAX                | 8710/MAX8711/MAX8761)                                                                                                      | 1                       |                               |       |       |

| SUPB Supply Operating Range               |                                                                                                                            | 4.5                     |                               | 13.2  | V     |

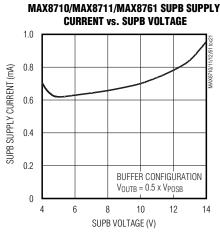

| SUPB Supply Current                       | Buffer configuration, V <sub>POSB</sub> = 4V, no load                                                                      |                         | 0.7                           | 1.0   | mA    |

| Input Offset Voltage                      | (VNEGB, VPOSB) = VSUPB / 2, TA = +25°C                                                                                     |                         | 0                             | 12    | mV    |

| Input Bias Current                        | (VNEGB, VPOSB) = VSUPB / 2                                                                                                 | -50                     | +1                            | +50   | nA    |

| Common-Mode Input Range                   | VNEGB, VPOSB                                                                                                               | 0                       |                               | VSUPB | V     |

| Common-Mode Rejection Ratio               | 0≤(V <sub>NEGB</sub> , V <sub>POSB</sub> )< V <sub>SUPB</sub>                                                              | 50                      | 90                            |       | dB    |

| Open-Loop Gain                            |                                                                                                                            |                         | 125                           |       | dB    |

| Output Valtage Swing High                 | I <sub>OUTB</sub> = 100μA                                                                                                  | V <sub>SUPB</sub> -     | V <sub>SUPB</sub> -           |       | m)/   |

| Output Voltage Swing High                 | I <sub>OUTB</sub> = 5mA                                                                                                    | V <sub>SUPB</sub> - 150 | V <sub>SUPB</sub> -<br>80     |       | mV    |

| Output Voltage Swing Low                  | $I_{OUTB} = -100\mu A$                                                                                                     |                         | 2                             | 15    | m\/   |

| Output Voltage Swing Low                  | IOUTB = -5mA                                                                                                               |                         | 80                            | 150   | IIIV  |

| Chart Circuit Current                     | Short to V <sub>SUPB</sub> / 2, sourcing                                                                                   | 50                      | 150                           |       | m ^   |

| Short-Circuit Current                     | Short to V <sub>SUPB</sub> / 2, sinking                                                                                    | 50                      | 80 150 mV<br>150 mA<br>±40 mA |       |       |

| Output Current                            | Buffer configuration, V <sub>POSB</sub> = 4V,<br>V <sub>OUTB</sub> error < ±10mV                                           |                         | ±40                           |       | mA    |

| Power-Supply Rejection Ratio              | 6V ≤ V <sub>SUPB</sub> ≤ 13.2V, DC (V <sub>NEGB</sub> , V <sub>POSB</sub> ) = V <sub>SUPB</sub> / 2                        | 60                      | 100                           |       | dB    |

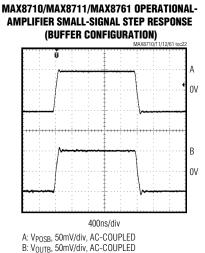

| Slew Rate                                 |                                                                                                                            |                         | 12                            |       | V/µs  |

| -3dB Bandwidth                            | Buffer configuration, $R_L = 10k\Omega$ , $C_L = 10pF$                                                                     |                         | 12                            |       | MHz   |

| Gain-Bandwidth Product                    | Buffer configuration, $R_L = 10k\Omega$ , $C_L = 10pF$                                                                     |                         | 8                             |       | MHz   |

| POSITIVE CHARGE-PUMP REGUI                | LATOR                                                                                                                      |                         |                               |       |       |

| FBP Regulation Voltage                    | I <sub>GON</sub> = 10mA                                                                                                    | 2.425                   | 2.500                         | 2.575 | V     |

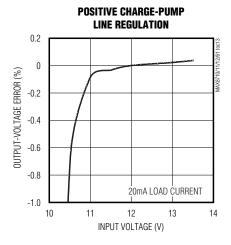

| FBP Line-Regulation Error                 | V <sub>OUTL</sub> (V <sub>SUPCP</sub> , MAX8710/MAX8761)<br>= 10.8V~13.2V, V <sub>GON</sub> = 27V, I <sub>GON</sub> = 20mA |                         |                               | 25    | mV    |

| FBP Input Bias Current                    | V <sub>FBP</sub> = 2.5V                                                                                                    | -50                     |                               | +50   | nA    |

| DRVP p-Channel On-Resistance              |                                                                                                                            |                         | 15                            | 30    | Ω     |

| DD//D = Observed On Desistance            | V <sub>FBP</sub> = 2.4V                                                                                                    |                         | 6                             | 12    | Ω     |

| DRVP n-Channel On-Resistance              | V <sub>FBP</sub> = 2.6V                                                                                                    | 20                      |                               |       | kΩ    |

| FBP Fault Trip Level                      | Falling edge                                                                                                               | 1.92                    | 2.00                          | 2.08  | V     |

| Positive Charge-Pump Soft-Start<br>Period | 2 <sup>12</sup> oscillator clock cycles in a 7-bit DAC                                                                     |                         | 2.73                          |       | ms    |

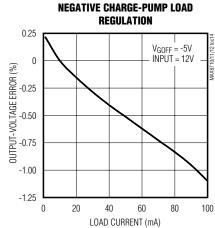

| NEGATIVE CHARGE-PUMP REGU                 | JLATOR                                                                                                                     |                         |                               |       |       |

| FBN Regulation Voltage                    | IGOFF = 10mA                                                                                                               | 200                     | 250                           | 300   | mV    |

| FBN Input Bias Current                    | V <sub>FBN</sub> = 250mV                                                                                                   | -50                     |                               | +50   | nA    |

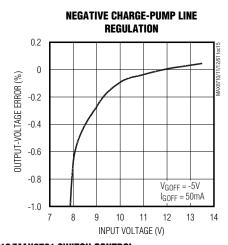

| FBN Line Regulation                       | VOUTL (VSUPCP, MAX8710/MAX8761)<br>= 10.8V~13.2V, VVGOFF = -6V, IGOFF = -50mA                                              |                         |                               | 25    | mV    |

| DRVN p-Channel On-Resistance              |                                                                                                                            |                         | 7.5                           | 15    | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                              | CONDITIONS                                                                                                                                                                             | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

|                                                                        | V <sub>FBN</sub> = 350mV                                                                                                                                                               |       | 3    | 6     | Ω     |

| DRVN n-Channel On-Resistance                                           | V <sub>FBN</sub> = 150mV                                                                                                                                                               | 20    |      |       | kΩ    |

| FBN Fault Trip Level                                                   | Rising edge                                                                                                                                                                            |       | 700  |       | mV    |

| Negative Charge-Pump Soft-Start<br>Period                              | 2 <sup>12</sup> oscillator clock cycles in a 7-bit DAC                                                                                                                                 |       | 2.73 |       | ms    |

| SEQUENCE CONTROL                                                       |                                                                                                                                                                                        | •     |      |       | •     |

| SHDN Input Low Voltage                                                 |                                                                                                                                                                                        |       |      | 0.6   | V     |

| SHDN Input High Voltage                                                |                                                                                                                                                                                        | 2.0   |      |       | V     |

| SHDN Input Current                                                     |                                                                                                                                                                                        |       |      | 1     | μΑ    |

| DLP Capacitor Charge Current                                           | During startup, V <sub>DLP</sub> = 1.0V                                                                                                                                                | 4     | 5    | 6     | μΑ    |

| DLP Turn-On Threshold                                                  |                                                                                                                                                                                        | 2.375 | 2.5  | 2.625 | V     |

|                                                                        | SHDN = low or fault tripped; DLP, FBP, FBN to GND                                                                                                                                      |       | 10   |       | Ω     |

| Pin Discharge Switch On-Resistance                                     | SHDN = low or fault tripped;<br>MODE, OUTL, OUTB to GND<br>MAX8710, SHDN = low or fault trip; GON to GND                                                                               |       | 1    |       | kΩ    |

| POSITIVE GATE-DRIVER TIMING A                                          | ND CONTROL SWITCHES (MAX8710/MAX8761)                                                                                                                                                  | I.    |      |       | Į.    |

| CTL Input Low Voltage                                                  |                                                                                                                                                                                        |       |      | 0.6   | V     |

| CTL Input High Voltage                                                 |                                                                                                                                                                                        | 2.0   |      |       | V     |

| CTL Input Leakage Current                                              |                                                                                                                                                                                        | -1    |      | +1    | μΑ    |

| CTL to GON Rising Propagation<br>Delay                                 | $V_{MODE} = V_{REF}$ , 1.5nF from GON to GND, $V_{CTL} = 0$ to 3V step, no load on GON, measured from $V_{CTL} = 1.5V$ to GON = 20%                                                    |       | 100  |       | ns    |

| CTL to GON Falling Propagation<br>Delay                                | V <sub>MODE</sub> = V <sub>REF</sub> , 1.5nF from GON to GND, V <sub>CTL</sub> = 3V to 0 step, DRN falling, no load on DRN and GON, measured from V <sub>CTL</sub> = 1.5V to GON = 80% |       | 100  |       | ns    |

| SRC Input Voltage Range                                                |                                                                                                                                                                                        |       |      | 28    | V     |

| SRC Input Current                                                      | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DLP</sub> = 3V, CTL = high                                                                                                               |       | 150  | 250   | μΑ    |

| DRN Input Current                                                      | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DRN</sub> = 8V, V <sub>DLP</sub> = 3V, V <sub>CTL</sub> = 0V                                                                             |       | 26   | 40    | μΑ    |

| SRC Switch On-Resistance                                               | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DLP</sub> = 3V, CTL = high                                                                                                               |       | 20   | 40    | Ω     |

| DRN Switch On-Resistance                                               | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DLP</sub> = 3V, V <sub>CTL</sub> = 0V                                                                                                    |       | 60   |       | Ω     |

| MODE Switch On-Resistance                                              |                                                                                                                                                                                        |       | 1    |       | kΩ    |

| Mode 2 MODE Capacitor Charge<br>Current                                | V <sub>MODE</sub> < MODE current-source stop voltage threshold                                                                                                                         | 42    | 50   | 64    | μΑ    |

| MODE Voltage Threshold for<br>Enabling DRN Switch Control in<br>Mode 2 |                                                                                                                                                                                        | 2.3   | 2.5  | 2.7   | V     |

| MODE Current-Source Stop Voltage Threshold                             | V <sub>MODE</sub> rising, CMODE = 150pF                                                                                                                                                | 3.3   | 3.5  | 3.7   | V     |

| THR to GON Voltage Gain                                                |                                                                                                                                                                                        | 9.4   | 10   | 10.6  | V/V   |

| GON Falling Slew Rate                                                  |                                                                                                                                                                                        |       | 13.5 |       | V/µs  |

4 \_\_\_\_\_\_ NIXI/N

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = -40^{\circ}C$  to  $+100^{\circ}C$  (-40°C to  $85^{\circ}C$  for MAX8761), unless otherwise noted.) (Note 1)

| PARAMETER                                  |                                            |                                               | MIN   | TYP | MAX   | UNITS |

|--------------------------------------------|--------------------------------------------|-----------------------------------------------|-------|-----|-------|-------|

| REF Output Voltage                         | -10μA < I <sub>REF</sub> < 1n              | nA (excluding internal load)                  | 4.9   |     | 5.1   | V     |

| SUPCP Input Supply Range                   |                                            |                                               | 2.7   |     | 13.2  | V     |

| Charge-Pump Regulators Operating Frequency | -10µA <                                    |                                               | 1850  | kHz |       |       |

| LINEAR REGULATOR                           | 1                                          |                                               |       |     |       | u .   |

| D 11/1                                     | I <sub>OUTL</sub> = 50mA (MA               | AX8710/MAX8711/MAX8712)                       |       |     | 300   | .,,   |

| Dropout Voltage                            | I <sub>OUTL</sub> = 200mA (N               | /IAX8761)                                     |       |     | 400   | mV    |

| FBL Regulation Voltage                     | I <sub>OUTL</sub> = 50mA                   |                                               | 2.455 |     | 2.545 | V     |

| FBL Fault Trip Level                       | Falling edge                               |                                               | 1.96  |     | 2.04  | V     |

| FBL Line-Regulation Error                  |                                            | V~13.2V, V <sub>OUTL</sub> = 10V,             |       |     | 15    | mV    |

| Marriago de Older Company                  | V <sub>FBL</sub> = 2.4V (MAX               | (8710/MAX8711/MAX8712)                        | 300   |     |       | A     |

| Maximum OUTL Current                       | V <sub>FBL</sub> = 2.4V (MAX               | (8761)                                        | 500   |     |       | mA    |

| OUTL Load Regulation                       |                                            |                                               |       |     | 2     | %     |

| G                                          | V <sub>IN</sub> = 12V, 5mA <               | I <sub>OUT</sub> < 500mA (MAX8761)            |       | 2   |       | 1     |

| OPERATIONAL AMPLIFIER (MAX                 |                                            |                                               |       |     |       |       |

| SUPB Supply Current                        | Buffer configuration                       | on, V <sub>POSB</sub> = 4V, no load           |       |     | 1.0   | mA    |

| Input Offset Voltage                       | (V <sub>NEGB</sub> , V <sub>POSB</sub> ) = | · V <sub>SUPB</sub> / 2                       |       |     | 14    | mV    |

|                                            | IOUTB = 100μA                              |                                               |       |     |       | .,,   |

| Output-Voltage-Swing High                  | I <sub>OUTB</sub> = 5mA                    |                                               |       |     |       | mV    |

| Outrot Valle are Outro I are               | I <sub>OUTB</sub> = -100μA                 |                                               |       |     | 15    | \/    |

| Output-Voltage-Swing Low                   | I <sub>OUTB</sub> = -5mA                   |                                               |       |     | 150   | mV    |

| Classit Circuit Comment                    | Short to V <sub>SUPB</sub> / 2             | , sourcing                                    | 50    |     |       | A     |

| Short-Circuit Current                      | Short to V <sub>SUPB</sub> / 2             | , sinking                                     | 50    |     |       | mA    |

| POSITIVE CHARGE-PUMP REGUL                 | ATOR                                       |                                               |       |     |       |       |

| FBP Regulation Voltage                     | loov 10mA                                  | MAX8710/MAX8711/MAX8712                       | 2.425 |     | 2.575 | V     |

| i Br negulation voltage                    | IGON = TOTTA                               | MAX8761                                       | 2.40  |     | 2.65  | V     |

| EDD Line Description Force                 |                                            |                                               |       |     | 25    |       |

| FBP Line-Regulation Error                  |                                            |                                               |       |     | 50    | mV    |

| DRVP p-Channel On-Resistance               |                                            |                                               |       |     | 30    | Ω     |

| DDVD n Channel On Desigtant                | V <sub>FBP</sub> = 2.4V                    |                                               |       |     | 12    | Ω     |

| DRVP n-Channel On-Resistance               | V <sub>FBP</sub> = 2.6V                    |                                               | 20    |     |       | kΩ    |

| NEGATIVE CHARGE-PUMP REGU                  | LATOR                                      |                                               |       |     |       |       |

| FBN Regulation Voltage                     | I <sub>GOFF</sub> = 10mA                   |                                               | 200   |     | 300   | mV    |

| FBN Line Regulation                        |                                            | MAX8710/MAX8761)<br>GOFF = -6V, IGOFF = -50mA |       |     | 25    | mV    |

| DRVN p-Channel On-Resistance               |                                            |                                               |       |     | 15    | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_{A} = -40^{\circ}C$  to  $+100^{\circ}C$ ,  $(-40^{\circ}C \text{ to } +85^{\circ}C \text{ for MAX8761})$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                              | CONDITIONS                                                                                                 | MIN   | TYP | MAX   | UNITS |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| DDVN a Channel On Desistance                                           | V <sub>FBN</sub> = 350mV                                                                                   |       |     | 6     | Ω     |

| DRVN n-Channel On-Resistance                                           | V <sub>FBN</sub> = 150mV                                                                                   | 20    |     |       | kΩ    |

| SEQUENCE CONTROL                                                       |                                                                                                            |       |     |       |       |

| SHDN Input Low Voltage                                                 |                                                                                                            |       |     | 0.6   | V     |

| CLIDN Input High Voltage                                               | MAX8710/MAX8711/MAX8712                                                                                    | 2.0   |     |       | V     |

| SHDN Input High Voltage                                                | MAX8761                                                                                                    | 2.05  |     |       |       |

| DLP Capacitor Charge Current                                           | During startup, V <sub>DLP</sub> = 1.0V                                                                    | 4     |     | 6     | μΑ    |

| DLP Turn-On Threshold                                                  |                                                                                                            | 2.375 |     | 2.625 | V     |

| POSITIVE GATE-DRIVER TIMING A                                          | ND CONTROL SWITCHES (MAX8710/MAX8761)                                                                      |       |     |       |       |

| SRC Input Current                                                      | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DLP</sub> = 3V, CTL = high                                   |       |     | 250   | μΑ    |

| DRN Input Current                                                      | V <sub>MODE</sub> = V <sub>REF</sub> , V <sub>DRN</sub> = 8V, V <sub>DLP</sub> = 3V, V <sub>CTL</sub> = 0V |       |     | 40    | μΑ    |

| SRC Switch On-Resistance                                               | V <sub>MODE</sub> =V <sub>REF</sub> , V <sub>DLP</sub> = 3V, CTL = high                                    |       |     | 40    | Ω     |

| Mode 2 MODE Capacitor Charge<br>Current                                | V <sub>MODE</sub> < MODE current-source stop voltage threshold                                             | 42    |     | 64    | μA    |

| MODE Voltage Threshold for<br>Enabling DRN Switch Control in<br>Mode 2 |                                                                                                            | 2.3   |     | 2.7   | V     |

Note 1: Specifications to -40°C and +85°C are guaranteed by design, not production tested.

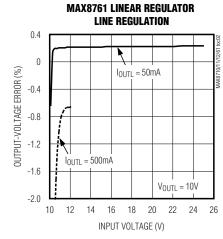

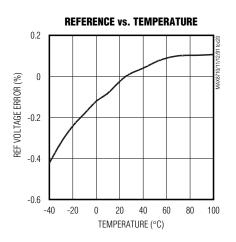

### **Typical Operating Characteristics**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

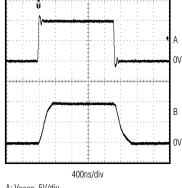

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN} = V_{IDL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

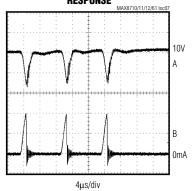

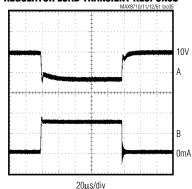

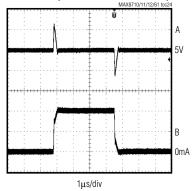

### MAX8710/MAX8711/MAX8712 LINEAR-REGULATOR PULSED LOAD-TRANSIENT RESPONSE

A: V<sub>OUTL</sub>, 100mV/div, AC-COUPLED B: I<sub>OUTL</sub>, 500mA/div

MAX8710/MAX8711/MAX8712 LINEAR-REGULATOR LOAD TRANSIENT RESPONSE

A: V<sub>OUTL</sub>, 50mV/div, AC-COUPLED B: I<sub>OUTL</sub>, 200mA/div

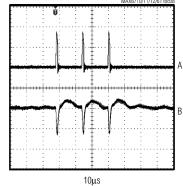

### MAX8761 LINEAR-REGULATOR PULSED LOAD TRANSIENT RESPONSE

A: I<sub>OUTL</sub>, 500mA/div B: V<sub>OUTL</sub>, AC-COUPLED, 100mV/div

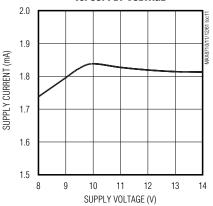

### CHARGE-PUMP NO-LOAD SUPPLY CURRENT vs. Supply Voltage

MAX8761 LINEAR-REGULATOR LOAD TRANSIENT RESPONSE

A: I<sub>OUTL</sub>, 200mA/div B: V<sub>OUTL</sub>, AC-COUPLED, 20mV/div

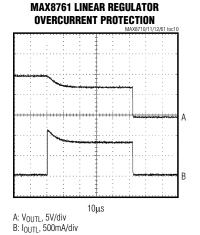

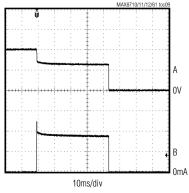

#### MAX8710/MAX8711/MAX8712 LINEAR-REGULATOR OVERCURRENT PROTECTION

A: V<sub>OUTL</sub>, 5V/div B: I<sub>OUTL</sub>, 500mA/div

### POSITIVE CHARGE-PUMP LOAD REGULATION

### Typical Operating Characteristics (continued)

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

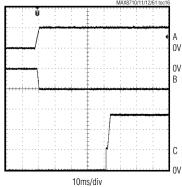

### POWER-UP SEQUENCE

A: V<sub>OUTL</sub>, 10V/div B: V<sub>GOFF</sub>, 5V/div C: V<sub>GON</sub>, 10V/div

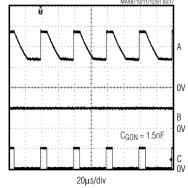

### MAX8710/MAX8761 SWITCH CONTROL FUNCTION (MODE 1) MAX8710/11/12/61 toc17

A: V<sub>GON</sub>, 10V/div B: V<sub>MODE</sub>, 5V/div C: V<sub>CTL</sub>, 5V/div

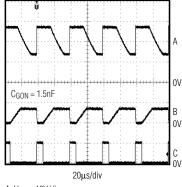

#### MAX8710/MAX8761 SWITCH CONTROL FUNCTION (MODE 2)

A: V<sub>GON</sub>, 10V/div B: V<sub>MODE</sub>, 5V/div C: V<sub>CTL</sub>, 5V/div

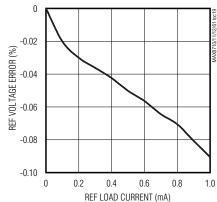

#### REFERENCE LOAD REGULATION

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN} = V_{INL} = V_{SUPCP} = 12V$ ,  $V_{OUTL} = V_{SUPB} = 10V$ ,  $V_{SRC} = 27V$ ,  $T_A = 0$ °C to +85°C. Typical values are at  $T_A = +25$ °C, unless otherwise noted.)

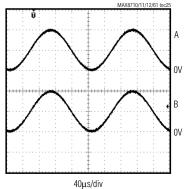

### MAX8710/MAX8711/MAX8761 OPERATIONAL-AMPLIFIER LARGE-SIGNAL STEP RESPONSE (BUFFER CONFIGURATION)

A: V<sub>POSB</sub>, 5V/div B: V<sub>OUTB</sub>, 5V/div

### MAX8710/MAX8711/MAX8761 OPERATIONAL-AMPLIFIER LOAD TRANSIENT RESPONSE (BUFFER CONFIGURATION)

A: V<sub>OUTB</sub>, 2V/div B: I<sub>OUTB</sub>, 50mA/div

#### MAX8710/MAX8711/MAX8761 OPERATIONAL-AMPLIFIER RAIL-TO-RAIL I/O

A: V<sub>POSB</sub>, 5V/div B: V<sub>OUTB</sub>, 5V/div

### **Pin Description**

|                     | MAX8711   MAX8712 |   | PIN   |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------|-------------------|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX8710/<br>MAX8761 |                   |   | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 1                   | _                 |   | GON   | Internal High-Voltage MOSFET Switch Common Terminal. GON is the output of the high-voltage switch-control block. GON is internally pulled to GND by a $1k\Omega$ resistor in shutdown for the MAX8710. GON is not pulled to GND for the MAX8761.                                                        |  |  |  |  |

| 2                   | _                 | _ | DRN   | Switch Input. Drain of the internal high-voltage back-to-back p-channel MOSFETs connected to GON.                                                                                                                                                                                                       |  |  |  |  |

| 3                   | 1                 | 1 | REF   | Reference Output. Connect a 0.22µF capacitor from REF to GND. REF remains on in shutdown.                                                                                                                                                                                                               |  |  |  |  |

| 4                   | 2                 | _ | POSB  | Operational-Amplifier Noninverting Input                                                                                                                                                                                                                                                                |  |  |  |  |

| 5                   | 3                 | 2 | INL   | Linear-Regulator Supply Input                                                                                                                                                                                                                                                                           |  |  |  |  |

| 6                   | 4                 | _ | NEGB  | Operational-Amplifier Inverting Input                                                                                                                                                                                                                                                                   |  |  |  |  |

| 7                   | 5                 | 3 | IN    | IC Supply Input. Bypass IN to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                               |  |  |  |  |

| 8                   | 6                 | 4 | OUTL  | Linear-Regulator Output. OUTL is internally pulled to GND by a $1k\Omega$ resistor in shutdown. For the MAX8711/MAX8712, OUTL is also the supply input for the charge-pump regulators.                                                                                                                  |  |  |  |  |

| 9                   | _                 | _ | SUPCP | Supply Input for the Charge-Pump Regulators. Connect a 0.1µF capacitor from SUPCP to GND.                                                                                                                                                                                                               |  |  |  |  |

| 10                  | 7                 | 5 | DRVN  | Negative Charge-Pump Driver Output. Output high level is V <sub>SUPCP</sub> , and output low level is GND. DRVN is internally pulled high to SUPCP when the negative charge pump is disabled.                                                                                                           |  |  |  |  |

| 11                  | 8                 | 6 | DRVP  | Positive Charge-Pump Driver Output. Output high level is V <sub>SUPCP</sub> , and output low level is GND. DRVP is internally pulled low in shutdown.                                                                                                                                                   |  |  |  |  |

| 12                  | _                 | _ | N.C.  | No Connection. Not internally connected.                                                                                                                                                                                                                                                                |  |  |  |  |

| 13                  | 9                 | 7 | GND   | Ground                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 14                  | 10                | _ | OUTB  | Operational-Amplifier Output. OUTB is internally pulled to GND by a $1 \text{k}\Omega$ resistor in shutdown.                                                                                                                                                                                            |  |  |  |  |

| 15                  | 11                | _ | SUPB  | Operational-Amplifier Supply Input. Bypass SUPB to GND with a 0.1µF capacitor.                                                                                                                                                                                                                          |  |  |  |  |

| 16                  | _                 | _ | THR   | GON Low-Level Regulation Set-Point Input. Connect THR to the center of a resistive voltage-divider between REF and GND to set the $V_{\rm GON}$ regulation level. The actual level is $10 \times V_{\rm THR}$ . See the <i>Switch Control (MAX8710/MAX8761)</i> section for details.                    |  |  |  |  |

| 17                  | 12                | 8 | FBP   | Positive Charge-Pump Feedback Input. Connect FBP to the center of a resistive voltage-divider between the positive charge-pump regulator output and GND to set the regulator output voltage. Place the divider within 5mm of FBP. FBP is internally pulled to GND by a $10\Omega$ resistor in shutdown. |  |  |  |  |

### Pin Description (continued)

|                     | PIN     |         |      |                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|---------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX8710/<br>MAX8761 | MAX8711 | MAX8712 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                               |

| 18                  | 13      | 9       | SHDN | Active-Low Shutdown Control Input. Pull SHDN low to turn off all sections of the device except REF. Pull SHDN high to enable the device. Cycle SHDN to reset the device after a fault.                                                                                                                                                                 |

| 19                  | _       | _       | CTL  | High-Voltage Switch-Control Block Timing Control Input. See the <i>Switch Control</i> (MAX8710/MAX8761) section for details.                                                                                                                                                                                                                           |

| 20                  | 14      | 10      | FBL  | Linear-Regulator Feedback Input. Connect FBL to the center of a resistive voltage-divider between the linear-regulator output and GND to set the linear-regulator output voltage. Place the divider within 5mm of FBL.                                                                                                                                 |

| 21                  | _       | _       | MODE | High-Voltage Switch-Control Block-Mode Selection Input and Timing-Adjustment Input. See the <i>Switch Control (MAX8710/MAX8761)</i> section for details. MODE is high impedance when it is connected to REF. MODE is internally pulled to GND by a $1 \text{k}\Omega$ resistor during REF UVLO, when $V_{\text{DLP}} < 2.5 \text{V}$ , or in shutdown. |

| 22                  | 15      | 11      | DLP  | Positive Charge-Pump Startup Delay and High-Voltage Switch Delay Input. Connect a capacitor from DLP to GND to set the delay time. A $5\mu$ A current source charges $C_{DLP}$ . DLP is internally pulled to GND by a $10\Omega$ resistor in shutdown.                                                                                                 |

| 23                  | 16      | 12      | FBN  | Negative Charge-Pump Feedback Input. Connect FBN to the center of a resistive voltage-divider between the negative output and REF to set the output voltage. Place the divider within 5mm of FBN. FBN is internally pulled to GND through a $10\Omega$ resistor in shutdown.                                                                           |

| 24                  | _       | _       | SRC  | Switch Input. Source of the internal high-voltage p-channel MOSFET connected to GON.                                                                                                                                                                                                                                                                   |

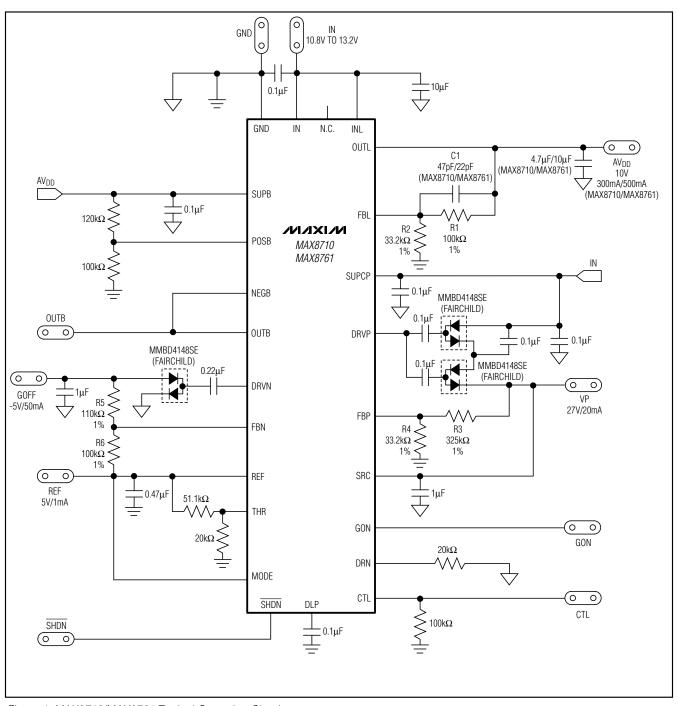

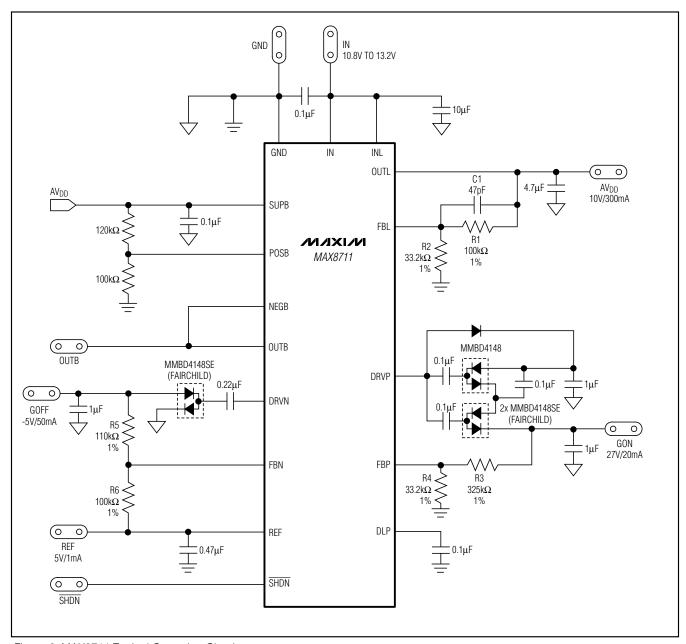

### **Typical Operating Circuit**

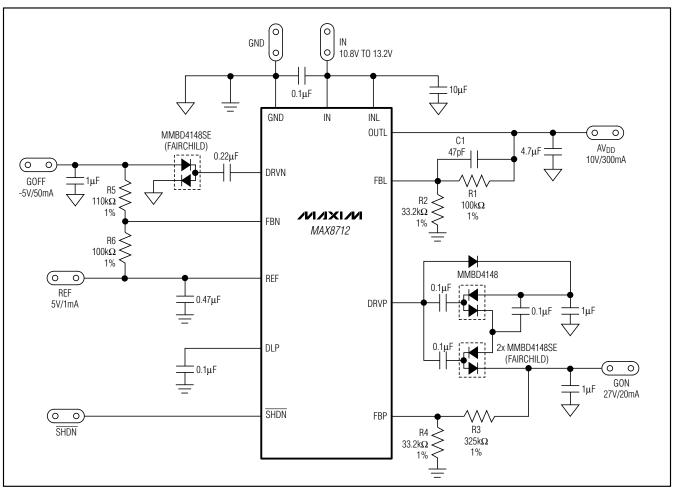

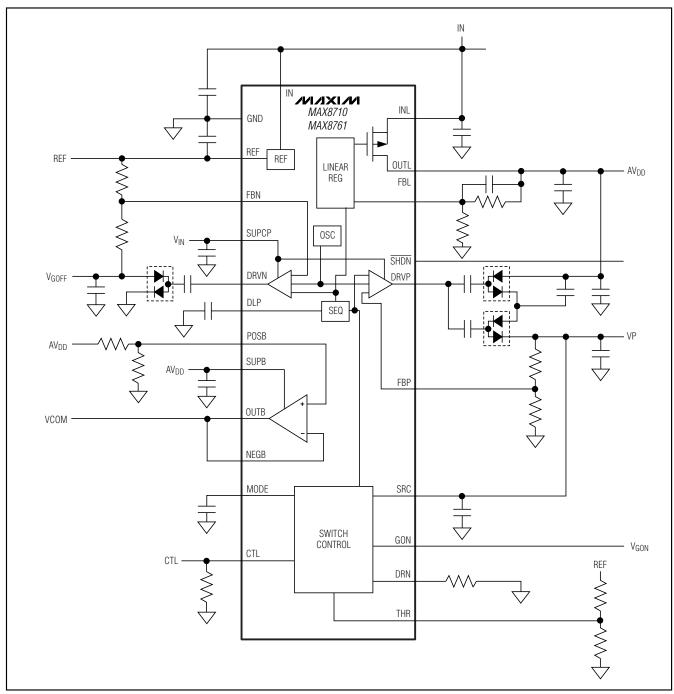

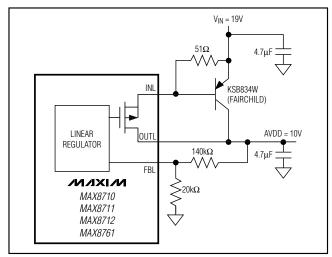

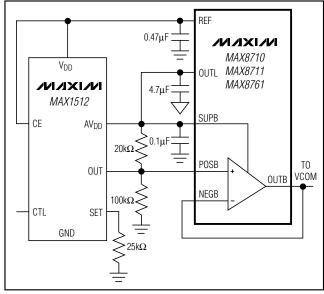

Figures 1, 2, and 3 are the *Typical Operating Circuits* of the MAX8710/MAX8761, MAX8711, and MAX8712 for generating power rails in TFT LCD panels. The input voltage range is from 10.8V to 13.2V. The AVDD output is 10V at 300mA, the V $_{\rm GON}$  output is 27V at 20mA, and the V $_{\rm GOFF}$  output is -5V at 50mA.

### Detailed Description

The MAX8710/MAX8711/MAX8712/MAX8761 include a high-performance linear regulator, a positive charge-pump regulator, a negative charge-pump regulator, and built-in power-up sequence control. The MAX8710/MAX8711/MAX8761 also include a high-current operational amplifier. Additionally, the MAX8710/MAX8761 provide logic-controlled high-voltage switches to control the positive charge-pump output. The linear regulator directly steps down the input voltage to generate the source-dri-

ver ICs' supply voltage. The two built-in charge-pump regulators are used to generate the TFT gate-on and gate-off supplies. The high-current operational amplifier is typically used to drive the LCD backplane (VCOM) and features high output current (150mA), fast slew rate (12V/ $\mu$ s), and wide bandwidth (12MHz). Its rail-to-rail inputs and output maximize flexibility.

#### **Linear Regulator**

The MAX8710/MAX8711/MAX8712/MAX8761 contain a linear regulator including a PMOS pass transistor. The MAX8710/MAX8711/MAX8712 can supply an output current of at least 300mA and the MAX8761 can supply at least 500mA. Connect an external resistive voltage-divider between the regulator output and GND with the midpoint connected to FBL to adjust the linear-regulator output. An error amplifier compares the FBL voltage with the 2.5V internal reference voltage and amplifies the difference. If the feedback voltage is higher than the

Figure 1. MAX8710/MAX8761 Typical Operating Circuit

Figure 2. MAX8711 Typical Operating Circuit

Figure 3. MAX8712 Typical Operating Circuit

reference voltage, the controller lowers the base current of the pnp transistor, which reduces the amount of current delivered to the output. If the feedback voltage is too low, the device increases the pnp transistor's base current, which allows more current to pass to the output and raises the output voltage. The linear regulator also includes an output current limit that protects the internal pass transistor against short circuits.

The input voltage range of the linear regulator is from 8V to 28V. The *Typical Operating Circuits* shown use a 12V input. The output voltage range of the linear regulator (OUTL) is up to 28V (MAX8710/MAX8761) or up to 13.2V (MAX8711/MAX8712). The linear-regulator output is used to generate the AVDD voltage, which is the analog supply rail for source-driver ICs in TFT LCD panels. The typical load of the AVDD supply is a periodic pulsed load, with a peak current of approximately 1A and pulse width of

approximately 2µs. The typical period of the pulse load is between 8.9µs and 31.7µs. The excellent transient performance of the linear regulator can easily meet this transient-response requirement.

The linear regulator can deliver at least 300mA (500mA for the MAX8761) output current continuously with a 4.7µF (10µF for the MAX8761) output capacitor. Do not allow the device power dissipation to exceed the package-dissipation limit listed in the *Absolute Maximum Ratings* section. The power dissipation can be estimated by multiplying the voltage difference between the input and the output with the required maximum continuous output current. For applications where the power dissipation exceeds the package limit, see the *External Transistor for Higher Current or Power Dissipation* section for more information.

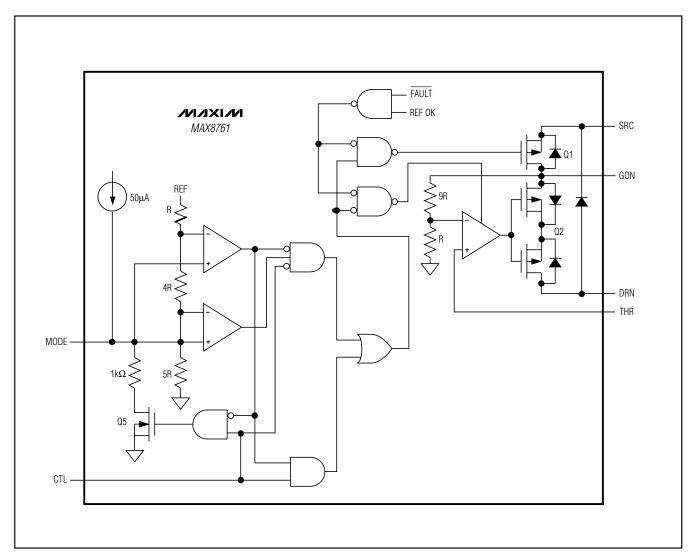

Figure 4. MAX8710/MAX8761 Functional Diagram

The linear regulator is enabled whenever REF is in regulation and SHDN is logic high. Each time it is enabled, the linear regulator goes through a soft-start routine by ramping up its internal reference voltage from 0 to 2.5V in 128 steps. The soft-start period is 2.73ms (typ), and FBL fault detection is disabled during this period. This soft-start feature effectively limits the inrush current during startup.

The linear-regulator current-limit circuitry monitors the current flowing through the internal pass transistor. The internal current limit is approximately 800mA (1.1A for the MAX8761). The linear-regulator output declines when it is not able to supply the load current. If the FBL voltage drops below 0.75V, the current limit folds back to approximately 180mA (250mA for the MAX8761).

The MAX8710/MAX8711/MAX8712/MAX8761 monitor the FBL voltage for undervoltage conditions. If V<sub>FBL</sub> is continuously below 2V (typ) for approximately 44ms, the device latches off. The foldback current-limit circuit, in conjunction with the output undervoltage fault latch and thermal-overload protection, protects the output load and the internal pass transistor against short circuits or overloads.

### **Positive Charge-Pump Regulator**

The positive charge-pump regulator is typically used to generate the positive supply rail for the TFT LCD gate-dri-

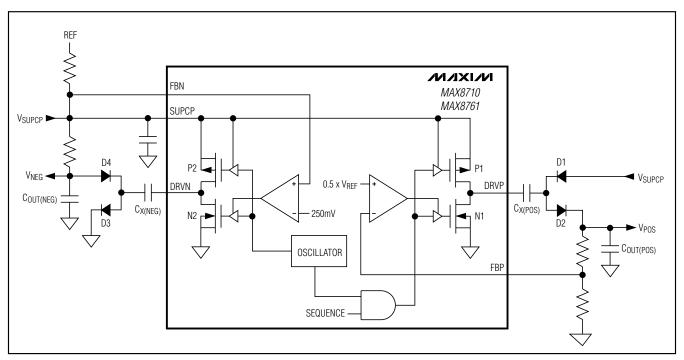

ver ICs. The output voltage is set with an external resistive voltage-divider from its output to GND with the midpoint connected to FBP. The number of charge-pump stages and the setting of the feedback divider determine the output voltage of the positive charge-pump regulator. The charge-pump driver includes a high-side p-channel MOSFET (P1) and a low-side n-channel MOSFET (N1) to control the power transfer as shown in Figure 5. The MOSFETs switch at a constant frequency of 1.5MHz.

During the first half-cycle, N1 turns on and allows VINPUT (VSUPCP, MAX8710/MAX8761 or VOUTL, MAX8711/ MAX8712) to charge up the flying capacitor Cx(POS) through diode D1. The amount of charge transferred from VINPUT to CX(POS) is determined by the on-resistance of N1, which varies according to the output of the feedback error amplifier. The error amplifier compares the feedback signal (FBP) with a 2.5V internal reference and amplifies the difference. If the feedback signal is below the reference, the error-amplifier output increases the supply voltage of N1's gate driver, lowering the onresistance. Similarly, if the feedback signal is above the reference, the error-amplifier output reduces the driver supply voltage, increasing the on-resistance. During the second half-cycle, N1 turns off and P1 turns on, level shifting Cx(POS) by VINPUT volts. This connects Cx(POS)

Figure 5. Charge-Pump Regulator Functional Diagram

in parallel with the reservoir capacitor  $C_{OUT(POS)}$ . If the voltage across  $C_{OUT(POS)}$  plus a diode drop (VPOS + VDIODE) is smaller than the level-shifted flying-capacitor voltage (VCX(POS) + VINPUT), charge flows from CX(POS) to  $C_{OUT(POS)}$  until diode D2 turns off.

The positive charge-pump regulator's startup can be delayed by connecting an external capacitor from DLP to GND. An internal constant current source begins charging the DLP capacitor when SHDN is logic high and REF reaches regulation. When the DLP voltage exceeds VREF / 2, the positive charge-pump regulator is enabled. Each time it is enabled, the positive chargepump regulator goes through a soft-start routine by ramping up its internal reference voltage from 0 to 2.5V in 128 steps. The soft-start period is 2.73ms (typ), and FBP fault detection is disabled during this period. The soft-start feature effectively limits the inrush current during startup. The MAX8710/MAX8711/MAX8712/ MAX8761 also monitor the FBP voltage for undervoltage conditions. If VFBP is continuously below 2V (typ) for approximately 44ms, the device latches off.

### **Negative Charge-Pump Regulator**

The negative charge-pump regulator is typically used to generate the negative supply rail for the TFT LCD gate-driver ICs. The output voltage is set with an external resistive voltage-divider from its output to REF with the midpoint connected to FBN. The number of charge-pump stages and the setting of the feedback divider determine the output of the negative charge-pump regulator. The charge-pump driver includes a high-side p-channel MOSFET (P2) and a low-side n-channel MOSFET (N2) to control the power transfer as shown in Figure 5. The MOSFETs switch a constant frequency of 1.5MHz.

During the first half-cycle, P2 turns on and allows VINPUT to charge up the flying capacitor CX(NEG) through diode D3. During the second half-cycle, P2 turns off and N2 turns on, level shifting CX(NEG) by VINPUT volts. This connects  $C_{X(NEG)}$  in parallel with reservoir capacitor Cout(NEG). If the voltage across Cout(NEG) minus a diode drop is greater than the voltage across CX(NEG), charge flows from COUT(NEG) to CX(NEG) until diode D4 turns off. The amount of charge transferred to the output is controlled by the on-resistance of N2, which varies according to the output of the feedback error amplifier. The error amplifier compares the feedback signal (FBN) with a 250mV internal reference and amplifies the difference. If the feedback signal is above the reference, the error-amplifier output increases the supply voltage of N2's gate driver, lowering the on-resistance. Similarly, if the feedback signal is below the reference, the error-amplifier output reduces the driver supply voltage, increasing the on-resistance.

The negative charge-pump regulator is enabled when \$\overline{SHDN}\$ is logic high and REF reaches regulation. Each time it is enabled, the negative charge-pump regulator goes through a soft-start routine by ramping down its internal reference voltage from 5V to 250mV in 128 steps. The soft-start period is 2.73ms (typ), and FBN fault detection is disabled during this period. The soft-start feature effectively limits the inrush current during startup. The MAX8710/MAX8711/MAX8712/MAX8761 also monitor the FBN voltage for undervoltage conditions. If VFBN is continuously above 700mV (typ) for approximately 44ms, the device latches off.

### Operational Amplifier (MAX8710/MAX8711/MAX8761)

The MAX8710/MAX8711/MAX8761s' operational amplifier features high output current (150mA), fast slew rate (7.5V/ $\mu$ s), and wide bandwidth (12MHz). The operational amplifier is enabled when REF is in regulation and  $\overline{SHDN}$  is logic high. The output of the amplifier (OUTB) is internally pulled to ground through a 1k $\Omega$  resistor in shutdown.

The amplifier is typically used to drive the backplane (VCOM) of TFT LCD panels. The LCD backplane consists of a distributed series capacitance and resistance, a load that can be easily driven by this operational amplifier. However, if the operational amplifier is used in an application with a pure capacitive load, steps must be taken to ensure stable operation. As the operational amplifier's capacitive load increases, the amplifier's bandwidth decreases, and its gain peaking increases. To ensure stable operation, a  $5\Omega$  to  $50\Omega$  resistor can be placed between OUTB and the capacitive load to reduce gain peaking.

The operational amplifier limits short-circuit current to approximately  $\pm 150$ mA if the output is directly shorted to SUPB or to GND. If the short-circuit condition persists, the junction temperature of the IC rises until it trips the IC's thermal-overload protection.

### Reference Voltage (REF)

The reference output is nominally 5V and can source up to 1mA (see the *Typical Operating Characteristics*). Bypass REF with a 0.22µF ceramic capacitor connected between REF and GND. The reference remains enabled in shutdown.

### **Power-Up Sequence and Shutdown Control**

When the MAX8710/MAX8711/MAX8761 are powered up, REF rises with the voltage on IN. After REF reaches regulation and if SHDN is logic high, the linear regulator, operational amplifier, and negative charge-pump regulator are enabled and begin their respective soft-start routines. After the soft-start routines are completed, the fault-protection circuits for the linear regulator and the negative charge-pump regulator are activated.

When the linear regulator is enabled, the positive charge-pump-regulator delay block is enabled. An internal current source starts charging the DLP capacitor. The voltage on DLP linearly rises because of the constant charging current. When  $V_{DLP}$  goes above  $V_{REF}$  / 2, the switch control block is enabled, and the positive charge-pump regulator begins its soft-start. After the positive charge-pump regulator's soft-start is completed, the fault protection of the positive charge-pump regulator is also enabled.

The MAX8710/MAX8711/MAX8712/MAX8761 enter into shutdown when  $\overline{SHDN}$  is pulled low or REF falls below 4.5V. In shutdown, OUTL and OUTB are internally pulled to ground with 1k $\Omega$  resistors, FBN and FBP are internally pulled to ground with 10 $\Omega$  resistors, and DLP is pulled to GND through a 10 $\Omega$  resistor, discharging CDLP. In the MAX8710 only, GON is pulled to GND through a 1k $\Omega$  resistor. REF remains on in shutdown. Pulling SHDN high when REF is above 4.5V reactivates the IC. Output fault protection and thermal-overload protection can also turn off the IC's outputs. See the respective sections for details.

### **Output Fault Protection**

During steady-state operation, if the output of the linear regulator or any of the charge-pump regulator outputs does not exceed its respective fault-detection threshold, the MAX8710/MAX8711/MAX8712/MAX8761 activate an internal fault timer. If any condition or the combination of conditions indicates a continuous fault for the fault-timer duration (44ms typ), the MAX8710/MAX8711/MAX8712/MAX8761 set the fault latch, shutting down all the outputs except the reference. Once the fault condition is removed, cycle the input voltage or toggle SHDN to clear the fault latch and reactivate the device. Each regulator's fault-detection circuit is disabled during the regulator's soft-start time.

#### **Thermal-Overload Protection**

The thermal-overload protection prevents excessive power dissipation from overheating the IC. When the junction temperature exceeds +160°C, a thermal sensor immediately activates the fault protection, which shuts down all the outputs except the reference, allowing the device to cool down. Once the device cools down by approximately 15°C, the IC restarts automatically.

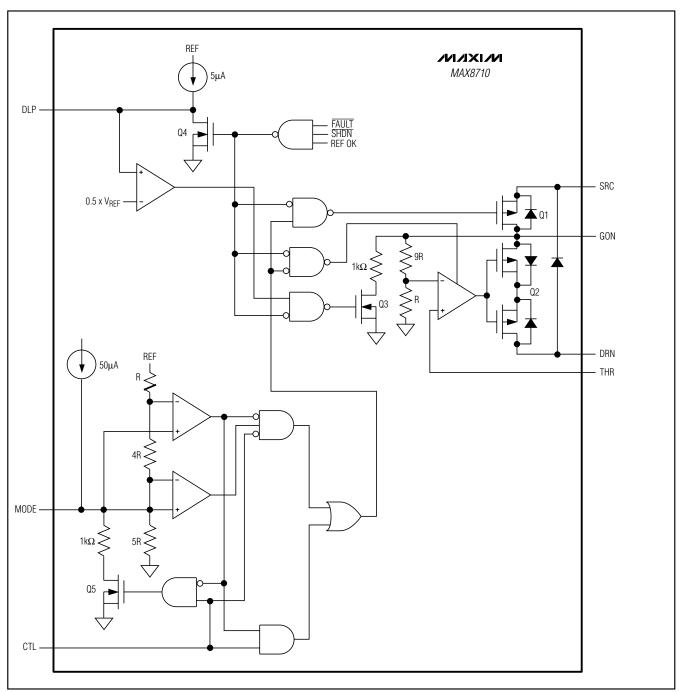

### Switch Control (MAX8710/MAX8761)

The MAX8710/MAX8761s' switch-control block (Figures 6 and 7) consists of a high-voltage p-channel MOSFET Q1 between SRC and GON, and a common-source-connected p-channel MOSFET pair Q2 between GON and DRN. The MAX8710 switch control block is enabled when VDLP goes above VREF / 2 and for MAX8761 VDLP has no control on switch control block. Both the MAX8710 and MAX8761 have two different modes of operation.

Activate the first mode by connecting MODE to REF. When CTL is logic high, Q1 turns on and Q2 turns off, connecting GON to SRC. When CTL is logic low, Q1 turns off and Q2 turns on, connecting GON to DRN. GON can then be discharged through a resistor connected between DRN and GND or OUTL. Q2 turns off and stops discharging GON when  $V_{\rm GON}$  reaches 10 times the voltage on THR.

When VMODE is less than 0.9 x VREF, the switch-control block works in the second mode. The rising edge of VCTL turns on Q1 and turns off Q2, connecting GON to SRC. An internal n-channel MOSFET Q5 between MODE and GND is also turned on to discharge an external capacitor between MODE and GND. The falling edge of VCTL turns off Q5, and an internal 50 $\mu$ A current source starts charging the MODE capacitor. Once VMODE exceeds 0.5 x VREF, the switch-control block turns off Q1 and turns on Q2, connecting GON to DRN. GON can then be discharged through a resistor connected between DRN and GND or OUTL. Q2 turns off and stops discharging GON when VGON reaches 10 times the voltage on THR.

Figure 6. MAX8710 High-Voltage Switch Control

Figure 7. MAX8761 High-Voltage Switch Control

### **Design Procedure**

### **Linear Regulator**

### **Output-Voltage Selection**

Adjust the linear-regulator output voltage by connecting a resistive voltage-divider from the linear-regulator output AVDD to GND with the center tap connected to FBL (Figure 1). Select the lower resistor of divider R2 in the  $10k\Omega$  to  $50k\Omega$  range. Calculate upper resistor R1 with the following equation:

$$R1 = R2 \times \left(\frac{V_{AVDD}}{V_{FBL}} - 1\right)$$

where  $V_{FBL} = 2.5V$  (typ) is the regulation point of the linear regulator.

### Input-Capacitor Selection

The linear regulator's output stage consists of a pnp pass transistor. Rapid movements of the input voltage must be avoided since the movement can be coupled into the base of the transistor through the base-to-emitter junction capacitance. The input capacitor reduces the current peaks drawn from the input supply and slows down the input voltage movement. One 10µF ceramic capacitor is used in the *Typical Operating Circuits* (Figures 1, 2, and 3) because of the high source impedance seen in typical lab setups. Actual applications usually have much lower source impedance, since the linear regulator typically runs directly from the output of another regulated supply and can operate with less input capacitance.

#### **Output-Capacitor Selection**

The output capacitor and its equivalent series resistance (ESR) affect the linear regulator's stability and transient response. The MAX8710/MAX8711/MAX8712 can deliver at least 300mA continuously and are stable with a 4.7µF output capacitor. The MAX8761 can deliver at least 500mA of output current and is stable with a 10µF output capacitor.

The typical load on the linear regulator for source-driver applications is a large pulsed load, with a peak current of approximately 1A and pulse width of approximately 2µs. The shape of the pulse is close to a triangle, so it is equivalent to a square pulse with 1A height and 1µs pulse width. The total voltage dip during the pulsed load transient also has two components: the ohmic dip due to the output capacitor's ESR, and the capacitive dip caused by discharging the output capacitance:

$$\begin{split} V_{DIP} &= V_{DIP(ESR)} + V_{DIP(C)} \\ V_{DIP(ESR)} &= I_{PULSE} \times R_{ESR} \\ V_{DIP(C)} &\approx \frac{I_{PULSE} \times t_{PULSE}}{C_{OUT}} \end{split}$$

where IPULSE is the height of the pulse load, and tPULSE is the pulse width. Higher capacitance and lower ESR result in less voltage dip. The ESR dip can be ignored when using ceramic output capacitors. Calculate the minimum required capacitance for the maximum allowed dip using:

$$C_{OUT(MIN)} \approx \frac{I_{PULSE} \times t_{PULSE}}{V_{DIP(MAX)}}$$

The above equations are "worst case" and assume that the linear regulator does not react to correct the output voltage during the load pulse. In fact, the regulator is fast enough to partially correct the output voltage, so the actual dip may be smaller, or a smaller capacitor may be acceptable. For the typical load pulse described above, assuming the voltage dip must be limited to 150mV, the minimum output capacitor is:

$$C_{OUT(MIN)} \approx \frac{1A \times 1\mu s}{0.15V} = 6.7\mu F$$

Because the regulator is able to limit the dip somewhat, the circuit of Figure 1 uses a  $4.7\mu\text{F}/10\mu\text{F}$  (MAX8710/MAX8761) output capacitor. The voltage rating and temperature characteristics of the output capacitor must also be considered.

### Feed-Forward Compensation

The output capacitance and equivalent load resistance determine the dominant pole. An internal parasitic capacitance of the regulator creates a second pole. This pole typically occurs at 100kHz, but can vary between 60kHz and 140kHz depending on the process variation. Since the pole occurs after the loop gain crossover, it does not affect the loop stability. However, canceling this pole with an additional zero can improve the load-transient response. An additional zero improves the closed-loop phase margin, thereby improving the transient response. The feed-forward network should be designed to get maximum positive phase at unity gain frequency (fu).

A zero can be added by connecting a feed-forward capacitor (C1) between OUTL and FBL as shown in Figure 1. The frequency of the zero can be calculated with the following equation:

$$f_{ZERO} = \frac{1}{2\pi R_1 C_1} = \frac{f_U}{\sqrt{V_{OUTL} / V_{FBL}}}$$

where R1 is the upper resistor of the feedback divider and  $f_u$  is the unity gain frequency. The unity gain frequency ( $f_u$ ) for the MAX8710/MAX8711/MAX8712 is approximately 80kHz; for MAX8761,  $f_u$  is approximately 160kHz. The value of R1 was calculated in the *Output-Voltage Selection* section to set  $V_{OUTL}$ . Use the value for unity gain frequency ( $f_u$ ), the ratio between  $V_{OUTL}$  and  $V_{FBL}$ , and R1 to calculate the value of C1.

### **Charge-Pump Regulators**

### Number of Charge-Pump Stages

For highest efficiency, always choose the lowest number of charge-pump stages that meets the output requirement.

The number of positive charge-pump stages is given by:

$$n_{POS} = \frac{V_P + V_{SWITCH} - V_{SUPCP}}{V_{NPUT} - 2 \times V_{DIODE}}$$

where npos is the number of positive charge-pump stages, Vp is the positive charge-pump regulator output, VINPUT is the supply voltage for the charge-pump regulators (VSUPCP, MAX8710/MAX8761 or VOUTL, MAX8711/MAX8712), VDIODE is the forward-voltage drop of the charge-pump diode, and VSWITCH is the voltage drop of the internal switches. Use VSWITCH = 0.3V.

The number of negative charge-pump stages is given by:

$$n_{NEG} = \frac{-V_{GOFF} + V_{SWITCH}}{V_{NPUT} - 2 \times V_{DIODE}}$$

where  $n_{NEG}$  is the number of negative charge-pump stages and  $V_{GOFF}$  is the negative charge-pump regulator output.

The above equations are derived based on the assumption that the first stage of the positive charge pump is connected to VMAIN and the first stage of the negative charge pump is connected to ground. Sometimes fractional stages are more desirable for better efficiency. This can be done by connecting the first stage to another available supply, such as a 5V supply. If the first charge-pump stage is powered from 5V, then the above equations become:

$$n_{POS} = \frac{V_P + V_{SWITCH} - 5V}{V_{INPUT} - 2 \times V_{DIODE}}$$

$$n_{NEG} = \frac{-V_{GOFF} + V_{SWITCH} + 5V}{V_{INPUT} - 2 \times V_{DIODE}}$$

### Output-Voltage Selection

Adjust the positive charge-pump-regulator output voltage by connecting a resistive voltage-divider from the regulator output Vp to GND with the center tap connected to FBP (Figure 1). Select the lower resistor of divider R4 in the range of  $10k\Omega$  to  $50k\Omega$ . Calculate upper resistor R3 with the following equation:

$$R3 = R4 \times \left(\frac{V_P}{V_{FBP}} - 1\right)$$

where  $V_{FBP} = 2.5V$  (typ) is the regulation point of the positive charge-pump regulator.

Adjust the negative charge-pump-regulator output voltage by connecting a resistive voltage-divider from the negative charge-pump output VGOFF to REF with the center tap connected to FBN (Figure 1). Select R6 in the  $20k\Omega$  to  $100k\Omega$  range. Calculate R5 with the following equation:

$$R5 = R6 \times \frac{V_{FBN} - V_{GOFF}}{V_{REF} - V_{FBN}}$$

where  $V_{REF} = 5V$  and  $V_{FBN} = 250$ mV is the regulation point of the negative charge-pump regulator.

### Flying Capacitor

Increasing the flying-capacitor (Cx) value lowers the effective source impedance and increases the output-current capability of the charge pump. Increasing the capacitance indefinitely has a negligible effect on output-current capability because the internal switch resistance and the diode impedance place a lower limit on the source impedance. A 0.1µF ceramic capacitor works well in most low-current applications. The flying capacitor's voltage rating must exceed the following:

where n is the stage number in which the flying capacitor is used, and V<sub>INPUT</sub> is the supply voltage for the charge-pump regulators (V<sub>SUPCP</sub>, MAX8710/MAX8761 or V<sub>OUTL</sub>, MAX8711/MAX8712).

### Charge-Pump Input Capacitor

Use an input capacitor with a value equal to or greater than the flying capacitor. Place the capacitor as close to the IC as possible. Connect the capacitor directly to PGND.

### Charge-Pump Output Capacitor

Increasing the output capacitance or decreasing the ESR reduces the output ripple voltage and the peak-to-peak transient voltage. With ceramic capacitors, the output voltage ripple is dominated by the capacitance value. Use the following equation to approximate the required capacitor value:

$$C_{OUT\_CP} \ge \frac{I_{LOAD\_CP}}{2f_{OSC}V_{RIPPLE\_CP}}$$

where C<sub>OUT\_CP</sub> is the output capacitor of the charge pump, I<sub>LOAD\_CP</sub> is the load current of the charge pump, and V<sub>RIPPLE\_CP</sub> is the desired peak-to-peak value of the output ripple.

### Charge-Pump Rectifier Diode

Use low-cost silicon switching diodes with a current rating equal to or greater than two times the average charge-pump input current. If it helps avoid an extra stage, some or all of the diodes can be replaced with Schottky diodes with an equivalent current rating.

### Applications Information