# LH5PV8512

### CMOS 4M (512K $\times$ 8) Pseudo-Static RAM

#### **FEATURES**

- 524,288 words × 8 bit organization

- CE access time (t<sub>CEA</sub>): 120 ns (MAX.)

- Cycle time (t<sub>RC</sub>): 190 ns (MIN.)

- Power supply:

$+3.0 \text{ V} \pm 0.15 \text{ V}$  (Operating)

+2.2 V to +3.15 V (Data retention)

Power consumption (MAX.):

126 mW (Operating)

95  $\mu$ W (Standby = CMOS input level)

221  $\mu$ W (Self-refresh = CMOS input level)

- Available for address refresh, auto-refresh, and self-refresh modes

- 2,048 refresh cycles/32 ms

- Address non-multiple

- Not designed or rated as radiation hardened

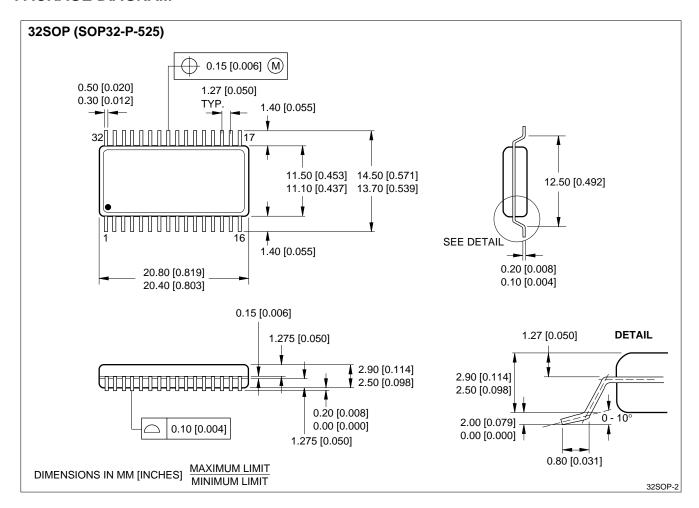

- Package:

32-pin, 525-mil SOP

Package material: Plastic

Substrate material: P-type silicon

Process: Silicon-gate CMOS

Operating temperature: 0 - 70°C

#### DESCRIPTION

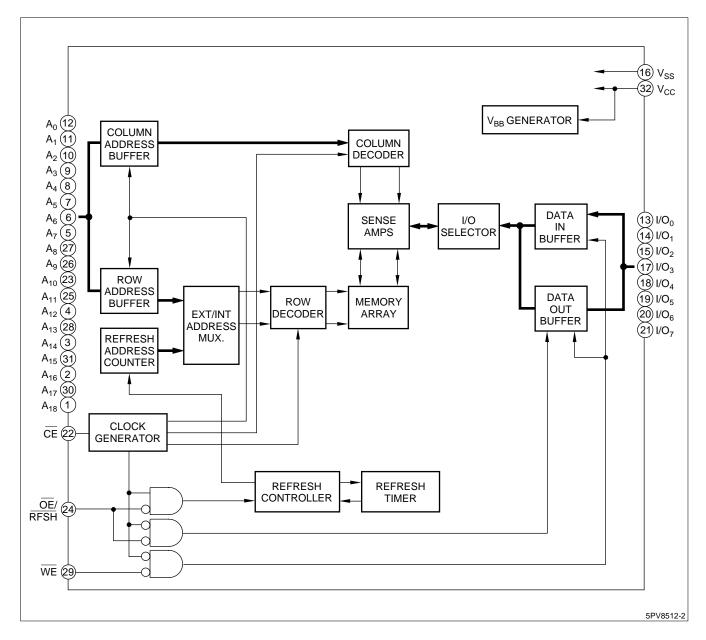

The LH5PV8512 is a 4M bit Pseudo-Static RAM with a 524,288 word  $\times$  8 bit organization. It is fabricated using silicon-gate CMOS process technology.

A PSRAM uses on-chip refresh circuitry with a DRAM memory cell for pseudo-static operation which eliminates external clock inputs, while having the same pinout as industry standard SRAMs. Moreover, due to the functional similarities between PSRAMs and SRAMs, existing 512K × 8 SRAM sockets can be filled with the LH5PV8512N with little or no changes. The advantage is the cost saving realized with the lower cost PSRAM.

The LH5PV8512 has the ability to fill the gap between DRAM and SRAM by offering low cost, low power standby and simple interface.

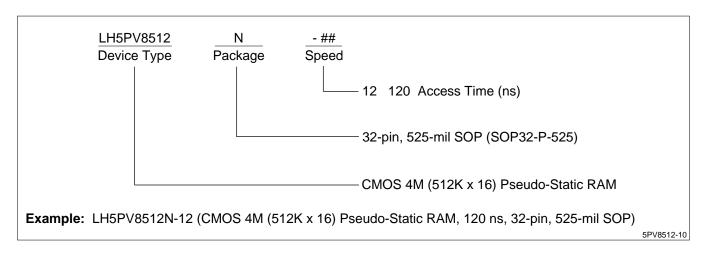

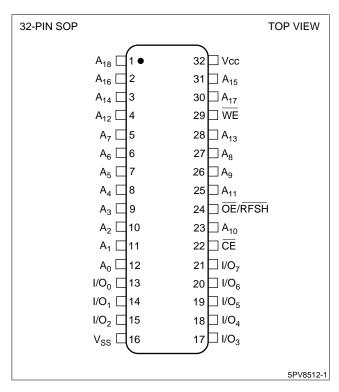

#### PIN CONNECTIONS

Figure 1. Pin Connections

Figure 2. LH5PV8512 Block Diagram

#### PIN DESCRIPTION

| PIN NAME                         | FUNCTION                                     |

|----------------------------------|----------------------------------------------|

| A <sub>0</sub> - A <sub>18</sub> | Address input                                |

| WE                               | Write enable input                           |

| OE/RFSH                          | Output enable input<br>Refresh control input |

| PIN NAME                            | FUNCTION          |

|-------------------------------------|-------------------|

| CE                                  | Chip enable input |

| I/O <sub>0</sub> - I/O <sub>7</sub> | Data input/output |

| V <sub>CC</sub>                     | Power supply      |

| GND                                 | Ground            |

#### **TRUTH TABLE**

| CE | OE/RFSH | WE | WE VO <sub>0</sub> - 7 |                 |

|----|---------|----|------------------------|-----------------|

| L  | L       | Н  | Output data            | Read            |

| L  | X       | L  | Input data             | Write           |

| L  | Н       | Н  | High-Z                 | CE only refresh |

| Н  | L       | X  | High-Z                 | Auto-refresh    |

| Н  | Н       | X  | High-Z                 | Standby         |

#### NOTES:

- 1. X = H or L

- 2. If RFSH = L, it is necessary to meet  $t_{OEH}$  and  $t_{OCD}$ .

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                    | SYMBOL           | RATING       | UNIT | NOTE |

|------------------------------|------------------|--------------|------|------|

| Applied voltage on all pins  | VT               | -0.5 to +4.6 | V    | 1    |

| Operating temperature        | T <sub>OPR</sub> | 0 to +70     | °C   | _    |

| Storage temperature          | T <sub>STG</sub> | -65 to +150  | °C   | _    |

| Output short circuit current | lo               | 50           | mA   |      |

| Power dissipation            | PD               | 600          | mW   | _    |

#### NOTE:

### RECOMMENDED DC OPERATING CONDITIONS ( $T_A = 0 \text{ to } +70^{\circ}\text{C}$ )

| PARAMETER      | SYMBOL          | MIN. | TYP. | MAX. | UNIT | NOTE |

|----------------|-----------------|------|------|------|------|------|

| Supply voltage | V <sub>CC</sub> | 2.85 | 3.0  | 3.15 | V    | 1    |

|                | V <sub>SS</sub> | 0    | 0    | 0    | V    |      |

| Input voltage  | V <sub>IH</sub> | 2.4  | _    | 4.5  | V    | _    |

|                | V <sub>IL</sub> | -0.5 | _    | 0.6  | V    |      |

#### NOTE:

## PIN CAPACITANCE $(T_A = +25^{\circ}C, f = 1 \text{ MHz}, V_{CC} = 3.0 \text{ V})$

| PARAMETER                | CONDITIONS                          | SYMBOL           | MIN. | MAX. | UNIT | NOTE |

|--------------------------|-------------------------------------|------------------|------|------|------|------|

|                          | A <sub>0</sub> - A <sub>18</sub>    | C <sub>IN1</sub> |      | 8    | pF   | 1    |

| Input capacitance        | WE, OE/RFSH                         | C <sub>IN2</sub> |      | 8    | pF   | 1    |

|                          | CE                                  | C <sub>IN3</sub> |      | 8    | pF   | 1    |

| Input/output capacitance | I/O <sub>0</sub> - I/O <sub>7</sub> | Cout1            |      | 10   | pF   | 1    |

#### NOTE

1. This parameter is sampled and not 100% tested.

<sup>1.</sup> The maximum applicable voltage on any pin with respect to  $V_{\mbox{\footnotesize SS}}.$

When the supply voltage falls down under the above recommended supply voltage by temporarily power-down, a wait time longer than

400 ms is necessary at V<sub>CC</sub> = 0 V before the next power-up. After the supply voltage rises and gets stable, a pause of 100 μs with

CE = RFSH = V<sub>IH</sub> and 8 dummy cycles are also necessary after the rises.

## DC ELECTRICAL CHARACTERISTICS (T\_A = 0 to +70°C, $V_{CC}$ = 3.0 V $\pm$ 0.15 V)

| PARAMETER                                    | SYMBOL           | CONDITIONS                                                                                                                                      | MIN. | MAX. | UNIT | NOTE |

|----------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Average supply current in normal operation   | Icc1             | t <sub>RC</sub> = 190 ns                                                                                                                        | _    | 40   | mA   | 1    |

| Average supply current in standby            | ICC2             | CE, OE, RFSH = V <sub>IH</sub>                                                                                                                  | _    | 0.5  | mA   | _    |

| mode                                         | 1002             | CE, OE, RFSH = V <sub>CC</sub> - 0.2 V                                                                                                          |      | 30   | mA   | _    |

| Average supply current in self-refresh cycle | I <sub>CC3</sub> | CE = V <sub>IH</sub><br>OE/RFSH = V <sub>IL</sub>                                                                                               | _    | 0.5  | mA   | _    |

|                                              | 1003             | CE = V <sub>CC</sub> - 0.2 V,<br>OE, RFSH = 0.2 V                                                                                               | _    | 70   | mA   | _    |

| Input leakage current                        | I <sub>LI</sub>  | $I_{LI} \qquad \begin{array}{c} 0 \text{ V} \leq \text{V}_{IN} \leq \text{V}_{CC} + 0.3 \text{ V} \\ 0 \text{ V on all other pins} \end{array}$ |      | 5    | μΑ   | _    |

| I/O leakage current                          | I <sub>LO</sub>  | $I_{LO}$ 0 V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>CC</sub> + 0.3 V Input/output pins in High-Z                                                 |      | 5    | μΑ   | _    |

| Output HIGH voltage                          | V <sub>OH</sub>  | V <sub>OH</sub> I <sub>OUT</sub> = -1 mA                                                                                                        |      | _    | V    | _    |

| Output LOW voltage                           | V <sub>OL</sub>  | I <sub>OUT</sub> = 2.1 mA                                                                                                                       | _    | 0.4  | V    | _    |

#### NOTE:

<sup>1.</sup> The input/output pins are in high impedance state.  $I_{\text{CC1}}$  depends on the cycle time.

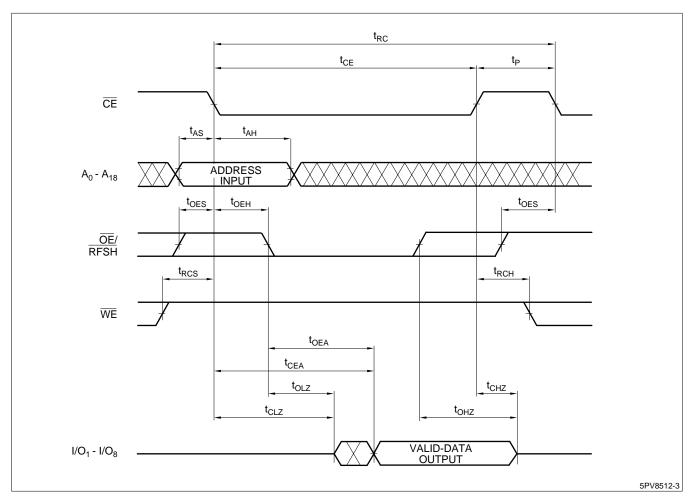

## AC ELECTRICAL CHARACTERISTICS $^{1,\,2,\,3,\,4,\,5}$ (T $_{A}$ = 0 to +70 $^{\circ}$ C, V $_{CC}$ = 3.0 V $\pm$ 0.15 V)

| PARAMETER                                           | SYMBOL           | MIN. | MAX.   | UNIT | NOTES              |

|-----------------------------------------------------|------------------|------|--------|------|--------------------|

| Random read, write cycle time                       | t <sub>RC</sub>  | 190  | _      | ns   | _                  |

| Random modify write cycle time                      | t <sub>RMW</sub> | 250  | _      | ns   | _                  |

| CE pulse width                                      | tce              | 120  | 10,000 | ns   | _                  |

| CE precharge time                                   | tp               | 70   | _      | ns   | _                  |

| Address setup time                                  | tas              | 0    |        | ns   | 6                  |

| Address hold time                                   | t <sub>AH</sub>  | 30   | _      | ns   | 6                  |

| Read command setup time                             | t <sub>RCS</sub> | 0    |        | ns   | _                  |

| Read command hold time                              | t <sub>RCH</sub> | 0    |        | ns   | _                  |

| CE access time                                      | tcea             | _    | 120    | ns   | 7                  |

| OE access time                                      | toea             | _    | 60     | ns   | 7                  |

| CE to output in Low-Z                               | t <sub>CLZ</sub> | 20   | _      | ns   | 8                  |

| OE to output in Low-Z                               | t <sub>OLZ</sub> | 0    | _      | ns   | 8                  |

| Write disable to output in Low-Z                    | t <sub>WLZ</sub> | 5    | _      | ns   | 8                  |

| Chip disable to output in High-Z                    | t <sub>CHZ</sub> | 0    | 30     | ns   | 8                  |

| Output disable to output in High-Z                  | tonz             | _    | 30     | ns   | 8                  |

| WE to output in High-Z                              | t <sub>WHZ</sub> | _    | 30     | ns   | 8                  |

| OE set up time from CE                              | toes             | 0    | _      | ns   | _                  |

| OE hold time from CE                                | toeh             | 15   | _      | ns   | _                  |

| OE setup time from chip disable                     | tocp             | 0    | _      | ns   | _                  |

| Write command pulse width                           | twp              | 35   | _      | ns   | _                  |

| Write command setup time                            | twcs             | 35   | 10,000 | ns   | _                  |

| Write command hold time                             | t <sub>WCH</sub> | 120  | 10,000 | ns   | _                  |

| Data setup time from write disable                  | t <sub>DSW</sub> | 30   | _      | ns   | 9                  |

| Data setup time from chip disable                   | tDSC             | 30   |        | ns   | 9                  |

| Data hold time from write disable                   | t <sub>DHW</sub> | 0    | _      | ns   | 9                  |

| Data hold time from chip disable                    | t <sub>DHC</sub> | 0    | _      | ns   | 9                  |

| Transition time (rise and fall)                     | t <sub>T</sub>   | 2    | 50     | ns   |                    |

| Refresh time interval (2,048 cycle)                 | t <sub>REF</sub> | _    | 32     | ms   | 10, 13, 14         |

| Auto refresh cycle time                             | t <sub>FC</sub>  | 190  | _      | ns   | _                  |

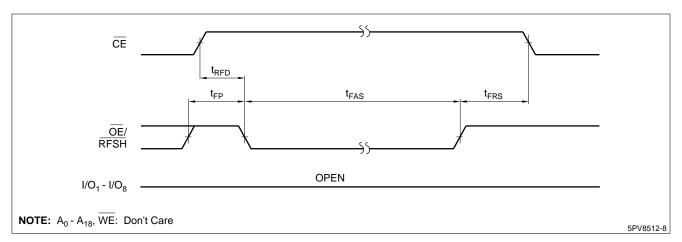

| Refresh delay time from CE                          | t <sub>RFD</sub> | 70   | _      | ns   | _                  |

| Refresh pulse width (Auto refresh)                  | t <sub>FAP</sub> | 80   | 8,000  | ns   | 11, 15             |

| Refresh precharge time (Auto refresh)               | t <sub>FP</sub>  | 40   |        | ns   | _                  |

| Refresh pulse width (Self refresh)                  | t <sub>FAS</sub> | 8    | _      | ms   | 11, 12, 13, 14, 15 |

| CE delay time from refresh precharge (Self refresh) | tFRS             | 600  | _      | ns   | _                  |

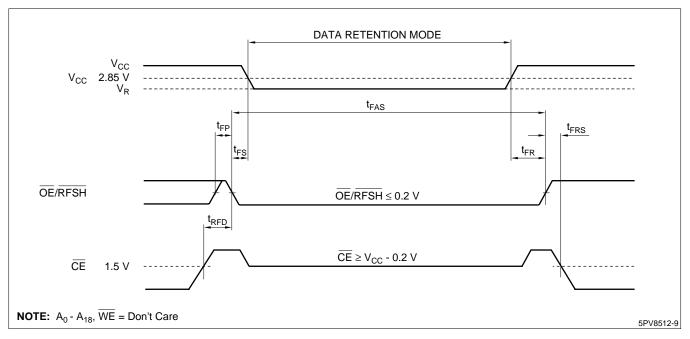

## DATA RETENTION CHARACTERISTICS $^{12, 13, 14, 15, 16, 17, 18, 19, 20}$ (T<sub>A</sub> = 0 to +70°C)

| PARAMETER                                                                                                                      | SYMBOL            | MIN. | MAX. | UNIT | NOTES |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|-------|

| Data retention voltage                                                                                                         | VR                | 2.2  | 3.15 | V    | _     |

| Data retention current $(V_{CC} = 3.15 \text{ V}, \overline{CE} = V_{CC} - 0.2 \text{ V}, \overline{OE/RFSH} = 0.2 \text{ V})$ | I <sub>CCDR</sub> | _    | 70   | μА   |       |

| Refresh setup time                                                                                                             | t <sub>FS</sub>   | 0    | _    | ns   |       |

| Recover time from data retention mode                                                                                          | t <sub>FR</sub>   | 5    |      | ms   |       |

#### NOTES:

- 1. AC characteristics are measured at t<sub>T</sub> = 2 ns.

- 2. AC characteristics are measured at the following condition:

|                        | INPUT           | VOLTAGE                         | OUTPUT VOLTAGE |                 |  |

|------------------------|-----------------|---------------------------------|----------------|-----------------|--|

|                        | V <sub>IH</sub> | V <sub>IH</sub> V <sub>IL</sub> |                | V <sub>OL</sub> |  |

| Input level            | 2.4 V           | 0.4 V                           | _              | _               |  |

| Input reference level  | 1.4 V           | 1.4 V                           | _              | _               |  |

| Output reference level |                 |                                 | 2.0 V          | 0.8 V           |  |

- 3. In order to initialize the circuit, CE and OE/RFSH should be kept V<sub>IH</sub> for 100 μs after power-up and followed by at least 8 dummy cycles.

- 4. If input signals of opposite phase to the outputs are applied in write cycle, OE or WE must disable output buffer proir to applying data to the device and data inputs must be floating prior to OE or WE turning on outputs buffer.

- Because a PSRAM operates dynamically like a DRAM, it is recommended to put bypass capacitors between V<sub>CC</sub> and GND to absorb power supply noise due to the peak current.

- 6. Address signals are latched in the memory at the falling edge of CE.

- 7. Measured with a load equivalent to 50 pF.

- t<sub>CLZ</sub>, t<sub>OLZ</sub>, t<sub>WLZ</sub>, t<sub>CHZ</sub>, t<sub>CHZ</sub>, t<sub>OHZ</sub>, and t<sub>WHZ</sub> are sampled, and not 100% tested. t<sub>CHZ</sub>, t<sub>OHZ</sub>, and t<sub>WHZ</sub> define the time at which the output achieves

the open circuit condition and they are not referenced to output voltage levels.

- 9. Input data is latched in the memory at the earlier rising edge of CE and WE.

- 10. CE only refresh or auto-refresh is needed to be executed 2,048 times within 32 ms.

- 11. Auto-refresh and self-refresh are defined by OE/RFSH pulse width during CE = V<sub>IH</sub>. If OE/RFSH pulse width is shorter than t<sub>FAP</sub> (MAX.), the cycle is an auto-refresh cycle and memory cells are refreshed by an internal address counter. If OE/RFSH pulse width is longer than t<sub>FAS</sub> (MIN.), the cycle is a self-refresh cycle and memory cells are refreshed by an internal clock generator automatically.

- 12. If  $\overline{\text{CE}}$  only refresh is used during normal read/write cycles, the first address refresh must be started within 15 μs after self-refresh or data retention mode ends, and the  $\overline{\text{CE}}$  only refresh must be executed continuously for 2,048 refresh cycles.

- 13. If distributed auto-refresh is used during normal read/write cycles, the first auto-refresh must be started within 15 μs after self-refresh or data retention mode ends.

- 14. If burst auto-refresh is used during normal read/write cycles, the first auto-refresh must be started within 15 μs after self-refresh or data retention mode ends, and the auto-refresh must be executed continuously for 2,048 refresh cycles.

- 15. After 8,000 ns (t<sub>FAP</sub> (MAX.)) from RFSH falling, the memory resets its internal address counter and enters self-refresh cycle. At the beginning of the self-refresh cycle, it takes longer than 8 ms (t<sub>FAS</sub> (MIN.)) for all addresses to be refreshed. Therefore, in case that the RFSH = L pulse length is from 8,000 ns to 8 ms, refresh all addresses by external clocks within 32 ms before the self-refresh to keep refresh time interval (t<sub>RFF</sub>).

- After self-refresh cycle or data retention mode ends, t<sub>FRS</sub> (MIN.) is necessary to reset the refresh operation. CE and OE/RFSH should kept V<sub>IH</sub> for t<sub>FRS</sub> (MIN.).

- 17. The data retention period is longer than  $t_{\text{FAS}}$  (MIN.) like self-refresh cycle.

- 18. OE/RFSH must be lower than 0.2 V during the data retention period.

- 19. CE must be higher than V<sub>CC</sub> 0.2 V during the data retention period.

- 20. The transition time of the supply voltage in data retention mode must be slower than 0.05 V/ms.

6

Figure 3. Read Cycle

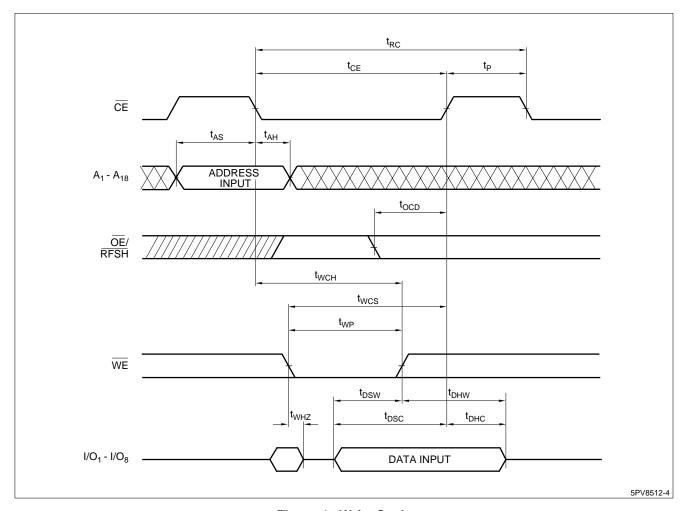

Figure 4. Write Cycle

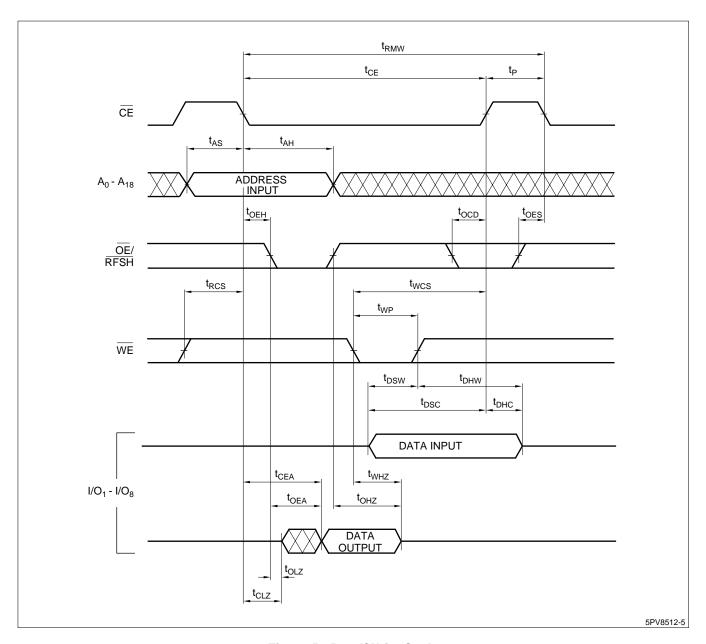

Figure 5. Read/Write Cycle

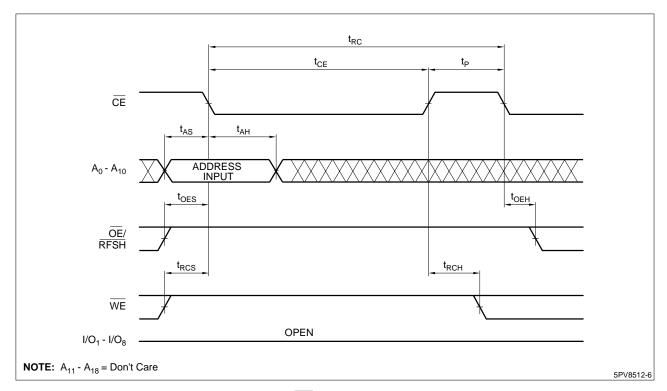

Figure 6. CE Only Refresh Cycle

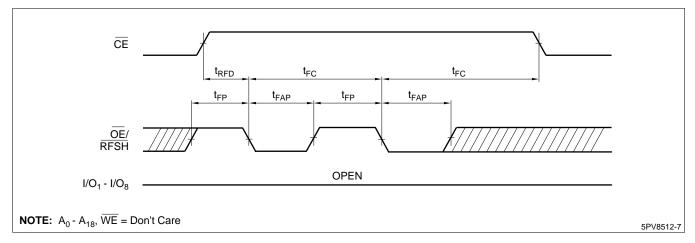

Figure 7. Auto-Refresh Cycle

Figure 8. Self-Refresh Cycle

Figure 9. Data Retention Mode

#### PACKAGE DIAGRAM

#### ORDERING INFORMATION