# SKYPER™ 32

### **Technical Explanations**

# Revision 04 Status: *preliminary*

This Technical Explanation is valid for the following parts:

| part number | type       | date code (YYWW) |

|-------------|------------|------------------|

| L6100100    | SKYPER™ 32 | ≥ 0519           |

#### Related documents:

| title                 | version      |

|-----------------------|--------------|

| Data Sheet SKYPER™ 32 | ≥ 03-06-2005 |

Prepared by: Markus Hermwille

\_\_\_\_\_

#### Content

| Application and Handling Instructions                                                               | 2  |

|-----------------------------------------------------------------------------------------------------|----|

| Further application support                                                                         | 2  |

| General Description                                                                                 |    |

| Features of SKYPER™ 32                                                                              | 2  |

| Block diagram                                                                                       |    |

| Dimensions                                                                                          |    |

| PIN Array – Primary Side                                                                            |    |

| PIN Array – Secondary Side                                                                          |    |

| Driver Performance                                                                                  |    |

| Insulation                                                                                          |    |

| Auxiliary Power Supply                                                                              |    |

| Under Voltage Protection of driver power supply (UVP)                                               |    |

| Input Signals                                                                                       |    |

| Short Pulse Suppression (SPS)                                                                       |    |

| Failure Management                                                                                  |    |

| Shut Down Input (SDI)                                                                               | g  |

| Dead Time generation (Interlock TOP / BOT) (DT)                                                     |    |

| Dynamic Short Circuit Protection by V <sub>CEsat</sub> monitoring / de-saturation monitoring (DSCP) | 10 |

| Adjustment of DSCP                                                                                  |    |

| High Voltage Diode for DSCP                                                                         | 12 |

| Gate resistors                                                                                      |    |

| External Boost Capacitors (BC)                                                                      |    |

| Application Example                                                                                 |    |

| Mounting Notes                                                                                      |    |

| Marking                                                                                             | 15 |

Information furnished in this document is believed to be accurate and reliable. However, no representation or warranty is given and no liability is assumed with respect to the accuracy or use of such information. Furthermore, this technical information specifies semiconductor devices but promises no characteristics. No warranty or guarantee expressed or implied is made regarding delivery, performance or suitability. Specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied and may be supersede by updates.

#### Please note:

All values in this technical explanation are typical values. Typical values are the average values expected in large quantities and are provided for information purposes only. These values can and do vary in different applications. All operating parameters should be validated by user's technical experts for each application.

#### **Application and Handling Instructions**

- Please provide for static discharge protection during handling. As long as the hybrid driver is not completely assembled, the input terminals have to be short-circuited. Persons working with devices have to wear a grounded bracelet. Any synthetic floor coverings must not be statically chargeable. Even during transportation the input terminals have to be short-circuited using, for example, conductive rubber. Worktables have to be grounded. The same safety requirements apply to MOSFET- and IGBT-modules.

- Any parasitic inductances within the DC-link have to be minimised. Over-voltages may be absorbed by C- or RCD-snubbers between main terminals for PLUS and MINUS of the power module.

- When first operating a newly developed circuit, SEMIKRON recommends to apply low collector voltage and load current in the beginning and to increase these values gradually, observing the turn-off behaviour of the free-wheeling diode and the turn-off voltage spikes generated across the IGBT. An oscillographic control will be necessary. Additionally, the case temperature of the module has to be monitored. When the circuit works correctly under rated operation conditions, short-circuit testing may be done, starting again with low collector voltage.

- It is important to feed any errors back to the control circuit and to switch off the device immediately in failure events. Repeated turn-on of the IGBT into a short circuit with a high frequency may destroy the device.

- The inputs of the hybrid driver are sensitive to over-voltage. Voltages higher than V<sub>S</sub> +0,3V or below -0,3V may destroy these inputs. Therefore, control signal over-voltages exceeding the above values have to be avoided.

- The connecting leads between hybrid driver and the power module should be as short as possible (max. 20cm), the driver leads should be twisted.

#### Further application support

Latest information is available at <a href="http://www.semikron.com">http://www.semikron.com</a>. For design support please read the SEMIKRON Application Manual Power Modules available at <a href="http://www.semikron.com">http://www.semikron.com</a>.

#### **General Description**

The SKYPER™ 32 core constitutes an interface between IGBT modules and the controller. This core is a half bridge driver. Basic functions for driving, potential separation and protection are integrated in the driver. Thus it can be used to build up a driver solution for IGBT modules.

#### Features of SKYPER™ 32

- Two output channels

- Integrated potential free power supply for the secondary side

- Short Pulse Suppression (SPS)

- Under Voltage Protection (UVP)

- Drive interlock (dead time) top / bottom (DT)

- Dynamic Short Circuit Protection (DSCP) by V<sub>CE</sub> monitoring and direct switch off

- Shut Down Input (SDI)

- Failure Management

- Expandable by External Boost Capacitors (BC)

- DC bus voltage up to 1200V

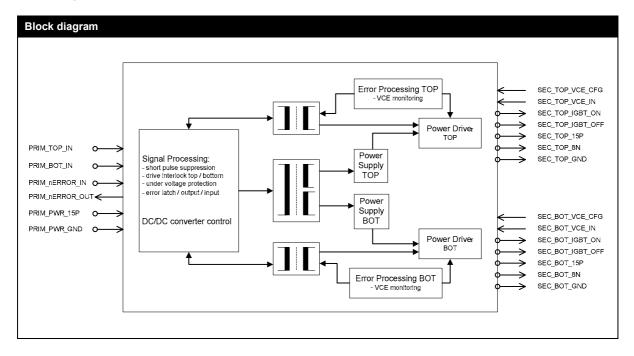

### **Block diagram**

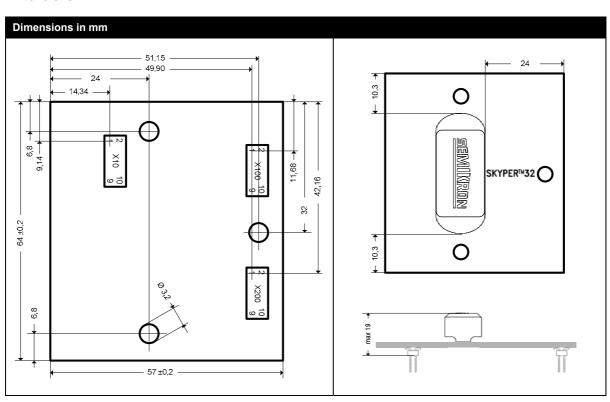

#### **Dimensions**

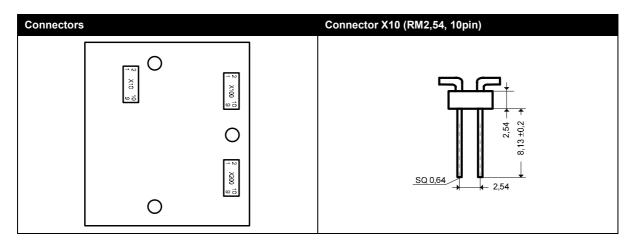

### PIN Array - Primary Side

| PIN    | Signal          | Function                                         | Specification                                                                                      |

|--------|-----------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------|

| X10:01 | PRIM_PWR_GND    | GND for power supply and GND for digital signals |                                                                                                    |

| X10:02 | PRIM_PWR_GND    | GND for power supply and GND for digital signals |                                                                                                    |

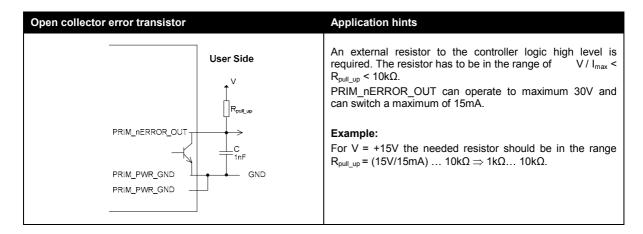

| X10:03 | PRIM_nERROR_OUT | ERROR output                                     | LOW = NO ERROR; open collector<br>output; max. 30V / 15mA (external pull<br>up resistor necessary) |

| X10:04 | PRIM_nERROR_IN  | ERROR input                                      | 5V logic; LOW active                                                                               |

| X10:05 | PRIM_PWR_GND    | GND for power supply and GND for digital signals |                                                                                                    |

| X10:06 | PRIM_PWR_GND    | GND for power supply and GND for digital signals |                                                                                                    |

| X10:07 | PRIM_TOP_IN     | Switching signal input (TOP switch)              | Digital 15 V; 10 kOhm impedance;<br>LOW = TOP switch off; HIGH = TOP<br>switch on                  |

| X10:08 | PRIM_BOT_IN     | Switching signal input (BOTTOM switch)           | Digital 15 V; 10 kOhm impedance;<br>LOW = BOT switch off; HIGH = BOT<br>switch on                  |

| X10:09 | PRIM_PWR_15P    | Drive core power supply                          | Stabilised +15V ±4%                                                                                |

| X10:10 | PRIM_PWR_15P    | Drive core power supply                          | Stabilised +15V ±4%                                                                                |

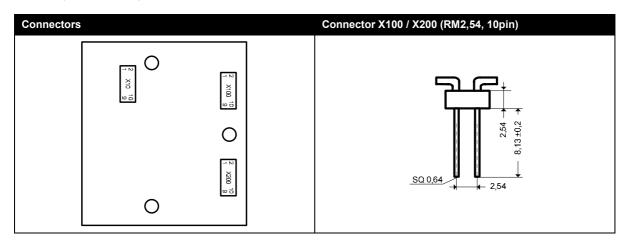

### PIN Array - Secondary Side

| PIN     | Signal           | Function                                           | Specification   |

|---------|------------------|----------------------------------------------------|-----------------|

| X100:01 | SEC_TOP_VCE_CFG  | Input reference voltage adjustment                 |                 |

| X100:02 | SEC_TOP_VCE_IN   | Input V <sub>CE</sub> monitoring                   |                 |

| X100:03 | SEC_TOP_15P      | Output power supply for external buffer capacitors | Stabilised +15V |

| X100:04 | SEC_TOP_15P      | Output power supply for external buffer capacitors | Stabilised +15V |

| X100:05 | SEC_TOP_GND      | GND for power supply and GND for digital signals   |                 |

| X100:06 | SEC_TOP_IGBT_ON  | Switch on signal TOP IGBT                          |                 |

| X100:07 | SEC_TOP_GND      | GND for power supply and GND for digital signals   |                 |

| X100:08 | SEC_TOP_IGBT_OFF | Switch off signal TOP IGBT                         |                 |

| X100:09 | SEC_TOP_8N       | Output power supply for external buffer capacitors | Stabilised -7V  |

| X100:10 | SEC_TOP_8N       | Output power supply for external buffer capacitors | Stabilised -7V  |

| X200:01 | SEC_BOT_VCE_CFG  | Input reference voltage adjustment                 |                 |

| X200:02 | SEC_BOT_VCE_IN   | Input V <sub>CE</sub> monitoring                   |                 |

| X200:03 | SEC_BOT_15P      | Output power supply for external buffer capacitors | Stabilised +15V |

| X200:04 | SEC_BOT_15P      | Output power supply for external buffer capacitors | Stabilised +15V |

| X200:05 | SEC_BOT_GND      | GND for power supply and GND for digital signals   |                 |

| X200:06 | SEC_BOT_IGBT_ON  | Switch on signal BOT IGBT                          |                 |

| X200:07 | SEC_BOT_GND      | GND for power supply and GND for digital signals   |                 |

| X200:08 | SEC_BOT_IGBT_OFF | Switch off signal BOT IGBT                         |                 |

| X200:09 | SEC_BOT_8N       | Output power supply for external buffer capacitors | Stabilised -7V  |

| X200:10 | SEC_BOT_8N       | Output power supply for external buffer capacitors | Stabilised -7V  |

#### **Driver Performance**

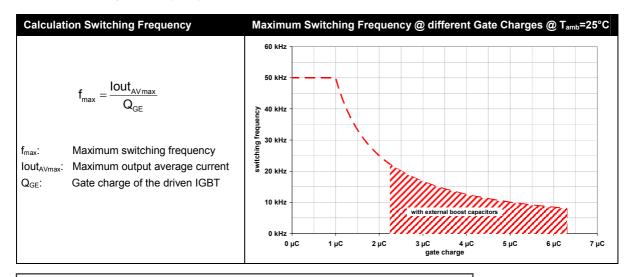

The driver is designed for application with half bridges or single modules and a maximum gate charge per pulse <  $2.5\mu C$  (<  $6.3\mu C$  with external boost capacitors). The charge necessary to switch the IGBT is mainly depending on the IGBT's chip size, the DC-link voltage and the gate voltage. This correlation is shown in module datasheets. It should, however, be considered that the driver is turned on at +15V and turned off at -7V. Therefore, the gate voltage will change by 22V during each switching procedure. Unfortunately, many datasheets do not show negative gate voltages. In order to determine the required charge, the upper leg of the charge curve may be prolonged to +22V for determination of approximate charge per switch.

The medium output current of the driver is determined by the switching frequency and the gate charge. The maximum switching frequency may be calculated with the shown equations.

#### Please note

The maximum value of the switching frequency is limited to 50kHz due to switching reasons.

#### Insulation

Magnetic transformers are used for insulation between gate driver primary and secondary side. The transformer set consists of pulse transformers which are used bidirectional for turn-on and turn-off signals of the IGBT and the error feedback between secondary and primary side, and a DC/DC converter. This converter provides a potential separation (galvanic separation) and power supply for the two secondary (TOP and BOT) sides of the driver. Thus, external transformers for external power supply are not required.

| Creepage and Clearance Distance in mm |           |

|---------------------------------------|-----------|

| Primary to secondary                  | Min. 12,2 |

#### **Auxiliary Power Supply**

A few basic rules should be followed when dimensioning the customer side power supply for the driver. The following table shows the required features of an appropriate power supply.

| Requirements of the auxiliary power supply  |          |  |

|---------------------------------------------|----------|--|

| Regulated power supply                      | +15V ±4% |  |

| Maximum rise time of auxiliary power supply | 50ms     |  |

| Minimum peak current of auxiliary supply    | 1A       |  |

| Power on reset completed after              | 150ms    |  |

#### Please note:

Do not apply switching signals during power on reset.

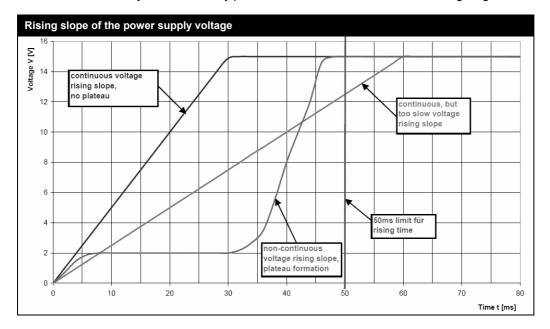

The supplying switched mode power supply may not be turned-off for a short time as consequence of its current limitation. Its output characteristic needs to be considered. Switched mode power supplies with fold-back

characteristic or hiccup-mode can create problems if no sufficient over current margin is available. The voltage has to rise continuously and without any plateau formation as shown in the following diagram.

If the power supply is able to provide a higher current, a peak current will flow in the first instant to charge up the input capacitances on the driver. Its peak current value will be limited by the power supply and the effective impedances (e.g. distribution lines), only.

It is recommended to avoid the paralleling of several customer side power supply units. Their different set current limitations may lead to dips in the supply voltage.

The driver is ready for operation typically 150ms after turning on the supply voltage. The driver error signal PRIM\_nERROR\_OUT is operational after this time. Without any error present, the error signal will be reset.

To assure a high level of system safety the TOP and BOT signal inputs should stay in a defined state (OFF state, LOW) during driver turn-on time. Only after the end of the power-on-reset, IGBT switching operation shall be permitted.

#### Under Voltage Protection of driver power supply (UVP)

The internally detected supply voltage of the driver has an under voltage protection. The table below gives an overview of the trip level.

| Supply voltage     | UVP level |

|--------------------|-----------|

| Regulated +15V ±4% | 13,5V     |

If the internally detected supply voltage of the driver falls below this level, the IGBTs will be switched off (IGBT driving signals set to LOW). The input side switching signals of the driver will be ignored. The error memory will be set, and the output PRIM nERROR OUT changes to the HIGH state.

#### **Input Signals**

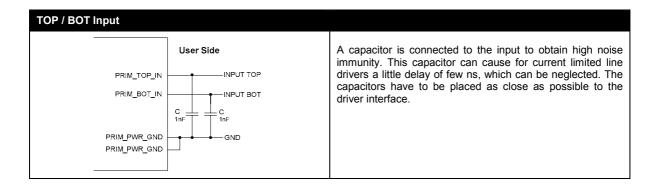

The signal transfer to each IGBT is made with pulse transformers, used for switching on and switching off the IGBT. The inputs have a Schmitt Trigger characteristic and a positive / active high logic (input HIGH = IGBT on; input LOW = IGBT off).

It is mandatory to use circuits which switch active to +15V and 0V. Pull up and open collector output stages must not be used for TOP / BOT control signals. It is recommended choosing the line drivers according to the demanded length of the signal lines.

#### Please note:

It is not permitted to apply switching pulses shorter than 1µs.

#### Short Pulse Suppression (SPS)

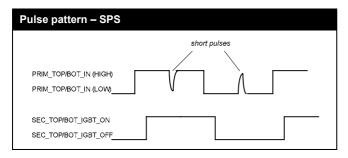

This circuit suppresses short turn-on and off-pulses of incoming signals. This way the IGBTs are protected against spurious noise as they can occur due to bursts on the signal lines. Pulses shorter than 625ns are suppressed and all pulses longer than 750ns get through for 100% probability. Pulses with a length in-between 625ns and 750ns can be either suppressed or get through.

#### **Failure Management**

Any error detected will set the error latch and force the output PRIM\_nERROR\_OUT into HIGH state. Switching pulses from the controller will be ignored. A reset of the latched error memory is only possible if no failure is present anymore and if the TOP and BOT input signals are set to the LOW level for a period of  $t_{\text{pERRRESET}} > 9\mu s$ .

The output PRIM\_nERROR\_OUT is an open collector output. For the error evaluation an external pull-up-resistor is necessary pulled-up to the positive operation voltage of the control logic (LOW signal = no error present, wire break safety is assured).

#### Please note:

The error output PRIM\_ERROR\_OUT is not short circuit proof.

#### Shut Down Input (SDI)

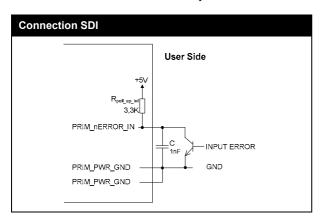

The shut down input / error input signal can gather error signals of other hardware components for switching off the IGBT (input HIGH = no turn-off; input LOW = turn-off).

A LOW signal at PRIM\_nERROR\_IN will set the error latch and force the output PRIM\_nERROR\_OUT into HIGH state. Switching pulses from the controller will be ignored. A reset of the latched error memory is only possible if no LOW signal at PRIM\_nERROR\_IN is present anymore and if the TOP and BOT input signals are set to the LOW level for a period of  $t_{perror} > 9\mu$ s.

The SDI function can be disabled by no connection or connecting to 5V.

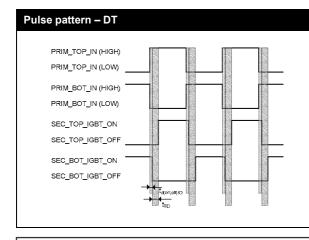

#### Dead Time generation (Interlock TOP / BOT) (DT)

The DT circuit prevents, that TOP and BOT IGBT of one half bridge are switched on at the same time (shoot through). The dead time is not added to a dead time given by the controller. Thus the total dead time is the maximum of "built in dead time" and "controller dead time". It is possible to control the driver with one switching signal and its inverted signal.

#### Please note:

The generated dead time is fixed and cannot be changed.

- The total propagation delay of the driver is the sum of interlock dead time (t<sub>TD</sub>) and driver input output signal propagation delay (t<sub>d(on:off)IO</sub>) as shown in the pulse pattern. Moreover the switching time of the IGBT chip has to be taken into account (not shown in the pulse pattern).

- In case both channel inputs (PRIM\_TOP\_IN and PRIM\_BOT\_IN) are at high level, the IGBTs will be turned off.

- If only one channel is switching, there will be no interlock dead time.

#### Please note:

No error message will be generated when overlap of switching signals occurs.

#### Dynamic Short Circuit Protection by V<sub>CEsat</sub> monitoring / de-saturation monitoring (DSCP)

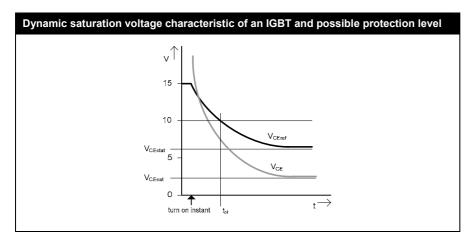

The DSCP circuit monitors the collector-emitter voltage  $V_{CE}$  of the IGBT during its on-state.  $V_{CE}$  is internally limited to 10V. If the reference voltage  $V_{CEref}$  is exceeded, the IGBT will be switched off and an error is indicated.

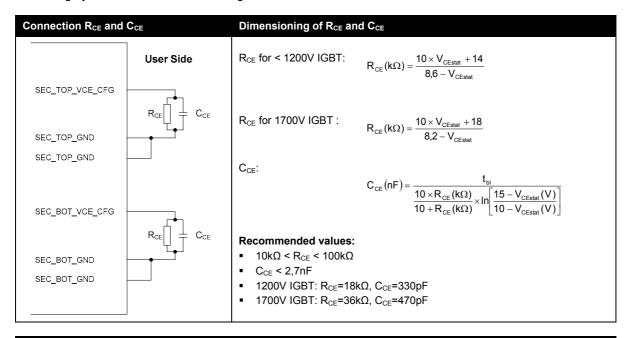

The reference voltage  $V_{\text{CEref}}$  may dynamically be adapted to the IGBTs switching behaviour. Immediately after turn-on of the IGBT, a higher value is effective than in steady state. This value will, however, be reset, when the IGBT is turned off.  $V_{\text{CEstat}}$  is the steady-state value of  $V_{\text{CEref}}$  and is adjusted to the required maximum value for each IGBT by an external resistor  $R_{\text{CE}}$ . It may not exceed 10V. The time constant for the delay of  $V_{\text{CEref}}$  may be increased by an external capacitor  $C_{\text{CE}}$ , which is connected in parallel to  $R_{\text{CE}}$ . It controls the blanking time  $t_{\text{bl}}$  which passes after turn-on of the IGBT before the  $V_{\text{CEsat}}$  monitoring is activated. This makes an adaptation to any IGBT switching behaviour possible.

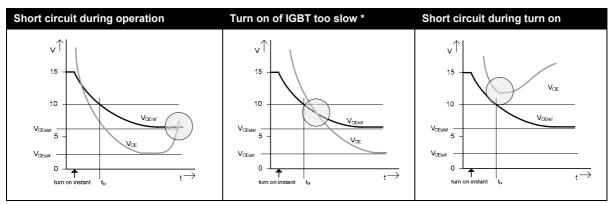

After  $t_{bl}$  has passed, the  $V_{CE}$  monitoring will be triggered as soon as  $V_{CEsat} > V_{CEref}$  and will turn off the IGBT. The error memory will be set, and the output PRIM\_nERROR\_OUT changes to the HIGH state. Possible failure modes are shows in the following pictures.

<sup>\*</sup> or adjusted blanking time too short

#### **Adjustment of DSCP**

The external components  $R_{CE}$  and  $C_{CE}$  are applied for adjusting the steady-state threshold and the short circuit monitoring dynamic as well as the blanking time.

#### **Application hints**

If the DSCP function is not used, for example during the experimental phase, SEC\_TOP\_VCE\_IN must be connected with SEC\_TOP\_GND for disabling SCP @ TOP side and SEC\_BOT\_VCE\_IN must be connected with SEC\_BOT\_GND for disabling SCP @ BOT side.

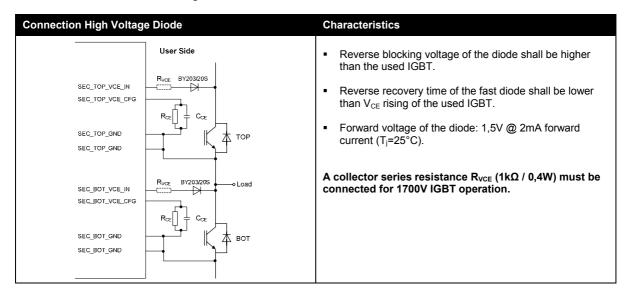

#### **High Voltage Diode for DSCP**

The high voltage diode blocks the high voltage during IGBT off state. The connection of this diode between driver and IGBT is shows in the following schematic.

#### **Gate resistors**

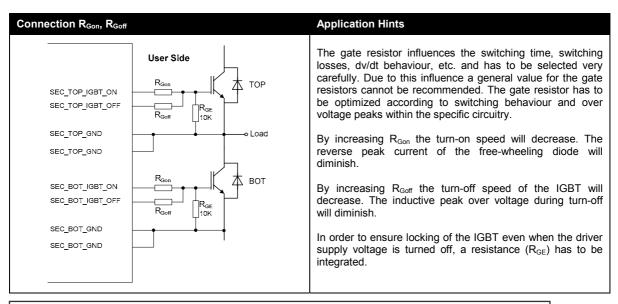

The output transistors of the driver are MOSFETs. The sources of the MOSFETs are separately connected to external terminals in order to provide setting of the turn-on and turn-off speed of each IGBT by the external resistors  $R_{\text{Gon}}$  and  $R_{\text{Goff}}$ . As an IGBT has input capacitance (varying during switching time) which must be charged and discharged, both resistors will dictate what time must be taken to do this. The final value of the resistance is difficult to predict, because it depends on many parameters as DC link voltage, stray inductance of the circuit, switching frequency and type of IGBT.

#### Please note:

Do not connect the terminals SEC\_TOP\_IGBT\_ON with SEC\_TOP\_IGBT\_OFF and SEC\_BOT\_IGBT\_ON with SEC\_BOT\_IGBT\_OFF, respectively.

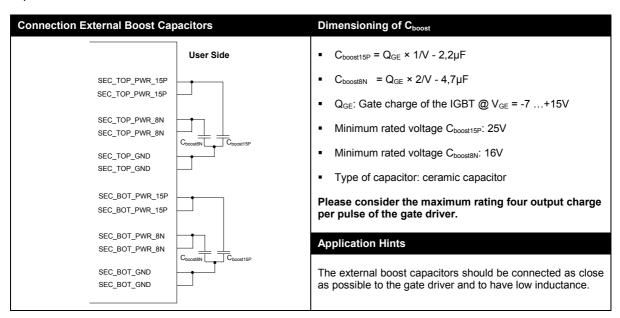

#### **External Boost Capacitors (BC)**

The rated gate charge of the driver may be increase by additional boost capacitors to drive IGBT with large gate capacitance.

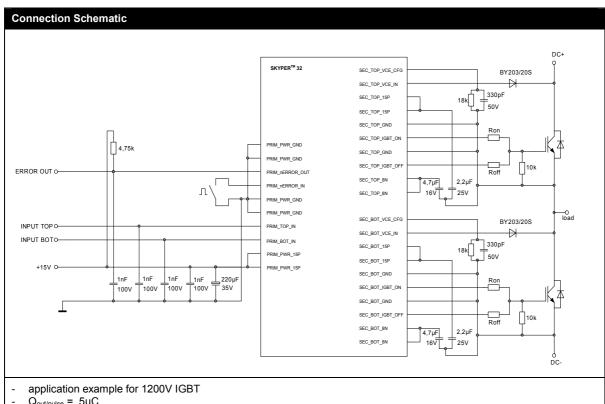

#### **Application Example**

- $Q_{out/pulse} = 5\mu C$

- $V_{CEref} = 5V$

- $t_{bl} = 1,5 \mu s$

2005-06-03 - Rev04 © by **SEMIKRON**

#### **Mounting Notes**

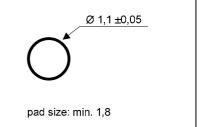

### Soldering Hints Drill Hole & Pad Size in mm

The temperature of the solder must not exceed 260°C, and solder time must not exceed 10 seconds.

The ambient temperature must not exceed the specified maximum storage temperature of the driver.

The solder joints should be in accordance to IPC A 610 Revision D (or later) - Class 3 (Acceptability of Electronic Assemblies) to ensure an optimal connection between driver core and printed circuit board.

#### Please note:

The driver is not suited for hot air reflow or infrared reflow processes.

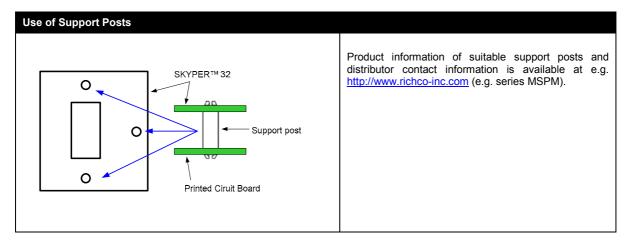

The connection between driver core and printed circuit board should be mechanical reinforced by using support posts.

#### Please note:

The use of agressive materials in cleaning and potting process of driver core may be detrimental for the device parameters. If the driver core is coated by the user, any warranty expires.

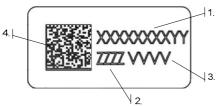

### Marking

Every driver core is marked. The marking contains the following items.

- 1. SEMIKRON part number (8 digits) + version number (2 digits)

- 2. Date code (4 digits): YYWW

- 3. Continuous number referred to date coce (4 digits)

- 4. Data matrix code

The Data Matrix Code is described as follows:

■ Type: **EEC 200**

Standard: ICO / IEC 16022 Cell size: 0,254 - 0,3 mm

$5\times 5~mm$ • The following data is coded:

Dimension:

0 **9 8 9 9** XXXXXXXYY ZZZZ VVVV

8 digits part number 2 digits version number

1 digit blank 4 digits date code

1 digit blank

4 digits continuous number

© by **SEMIKRON** 2005-06-03 – Rev04