# *HD-LINX*<sup>™</sup> GS1545 HDTV Serial Digital Equalizing Receiver

## PRELIMINARY DATA SHEET

#### FEATURES

- SMPTE 292M compliant

- 1.485 and 1.485/1.001Gb/s operation

- · integrated adaptive cable equalizer

- integrated adjustment-free reclocker

- 1:20 serial to parallel conversion

- · selectable reclocked serial output

- analog/digital input MUX

- carrier detect

- LOCK detect

- input jitter indicator (IJI)

- · cable length indication

- maximum cable length adjust

- 20 bit output

- 74.25MHz or 74.25/1.001MHz clock output

- single +5.0V power supply

- minimal component count for HD SDI receive solutions

#### APPLICATIONS

SMPTE 292M Serial Digital Interfaces for Video Cameras, Camcorders, VTR's, Signal Generators, Portable Equipment, and NLE's.

## DESCRIPTION

The GS1545 is a high performance integrated Equalizing Receiver designed for HDTV component signals, conforming to the SMPTE 292M standard. The GS1545 includes adjustment free, adaptive cable equalization, clock and data recovery, and serial to parallel conversion.

The Equalizer stage features DC restoration for immunity to the DC content in pathological test patterns.

The Clock and Data Recovery stage was designed to automatically recover the embedded clock signal and retime the data from SMPTE 292M compliant digital video signals. There is also a selectable reclocked serial data output and the ability to bypass the reclocker stage.

A unique feature, Input Jitter Indicator (IJI), is included for robust system design. This feature is used to indicate excessive input jitter before the chip mutes the outputs.

The Serial to Parallel conversion stage provides 1:20 S/P conversion

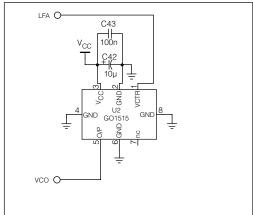

The GS1545 uses the GO1515 external VCO connected to the internal PLL circuitry to achieve ultra low noise PLL performance.

#### ORDERING INFORMATION

| PART NUMBER | PACKAGE      | TEMPERATURE |

|-------------|--------------|-------------|

| GS1545-CQR  | 128 pin MQFP | 0°C to 70°C |

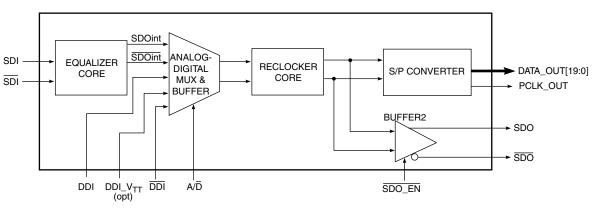

### SIMPLIFIED BLOCK DIAGRAM

GS1545

Revision Date: August 2000

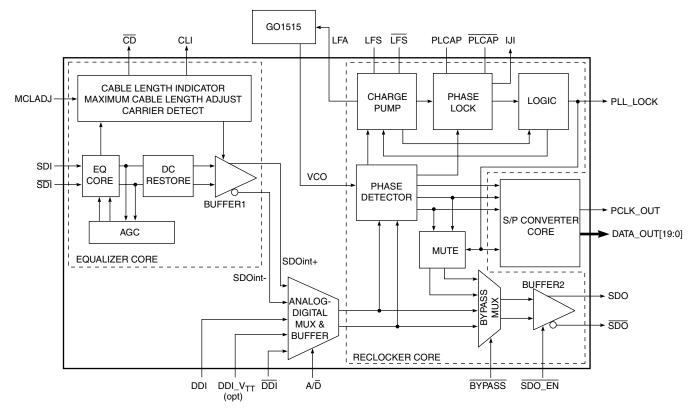

FUNCTIONAL BLOCK DIAGRAM

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}C$ , unless otherwise shown.

| PARAMETER                               | VALUE                                                                |

|-----------------------------------------|----------------------------------------------------------------------|

| Supply Voltage (V <sub>S</sub> )        | 5.5V                                                                 |

| Input Voltage Range (any input)         | $V_{EE} - 0.5 < V_{IN} < V_{CC} + 0.5$                               |

| Operating Temperature Range             | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$                             |

| Storage Temperature Range               | $-40^{\circ}\mathrm{C} \leq \mathrm{T_S} \leq 150^{\circ}\mathrm{C}$ |

| Power Dissipation ( $V_{CC} = 5.25V$ )  | 2.1W                                                                 |

| Lead Temperature (soldering 10 seconds) | 260°C                                                                |

| Input ESD Voltage                       | TBD                                                                  |

| Junction Temperature                    | 125°C                                                                |

522 - 28 - 00

GS1545

## DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 5V,  $V_{EE}$  = 0V,  $T_A$  = 0°C to 70°C, Data Rate = 1.485Gb/s.

| PARAMETER                                    | CONDITIONS                                                | SYMBOL           | MIN                    | TYP  | МАХ                    | UNITS | TEST<br>LEVEL |

|----------------------------------------------|-----------------------------------------------------------|------------------|------------------------|------|------------------------|-------|---------------|

| Positive Supply Voltage                      | Operating range                                           | V <sub>CC</sub>  | 4.75                   | 5.00 | 5.25                   | V     | 1             |

| Power Consumption                            | $V_{CC} = 5; T_A = 25^{\circ}C$                           | P <sub>D</sub>   | -                      | 1250 | -                      | mW    | 5             |

| Supply Current                               | $V_{CC} = 5; T_A = 25^{\circ}C$                           | I <sub>S</sub>   | -                      | 250  | -                      | mA    | 1             |

| Output CM Voltage (SDO, SDO)                 |                                                           | V <sub>CM</sub>  | 3.75                   | 4.0  | 4.25                   | V     | 5             |

| Input DC Voltage (DDI, DDI)                  |                                                           |                  | -                      | 4.0  | -                      | V     | 1             |

| Input DC Voltage (SDI, SDI)                  |                                                           |                  | -                      | 2.7  | -                      | V     | 1             |

| Serial Inputs (DDI, DDI)                     | Differential mode                                         | V <sub>SID</sub> | 100                    | -    | 1000                   | mV    | 7             |

|                                              | Common mode                                               | V <sub>CM</sub>  | 2.5+V <sub>SID/2</sub> | -    | $V_{CC}$ - $V_{SID/2}$ | V     | 7             |

| High Level Input Voltage<br>(A/D, BYPASS)    | $V_{CC} = 5, T_A = 25^{\circ}C$                           | V <sub>IH</sub>  | 2.0                    | -    | -                      | V     | 1             |

| Low Level Input Voltage (A/D,<br>BYPASS)     | $V_{CC} = 5, T_A = 25^{\circ}C$                           | V <sub>IL</sub>  | -                      | -    | 0.8                    | V     | 1             |

| High Level Output Voltage<br>(D[19:0], PCLK) | $V_{CC}$ = 5, $T_A$ = 25°C,<br>$I_{SOURCE}$ = 1.0mA       | V <sub>OH</sub>  | 2.4                    | -    | 3.0                    | V     | 1             |

| Low Level Output Voltage<br>(D[19:0], PCLK)  | $V_{CC}$ = 5, $T_A$ = 25°C,<br>$I_{SINK}$ = 1.0mA         | V <sub>OL</sub>  | -                      | -    | 0.4                    | V     | 1             |

| High Level Output Voltage<br>(PLL_LOCK)      | $V_{CC}$ = 5, $T_A$ = 25°C,<br>$I_{SOURCE}$ = 200µA       | V <sub>OH</sub>  | 3.0                    | -    | -                      | V     | 1             |

| Low Level Output Voltage<br>(PLL_LOCK)       | $V_{CC} = 5, T_A = 25^{\circ}C,$<br>$I_{SINK} = 500\mu A$ | V <sub>OL</sub>  | -                      | -    | 0.4                    | V     | 1             |

| Low Level Output Voltage (CD)                | $I_{SINK} = 500 \mu A$                                    | V <sub>OL</sub>  | -                      | 0.2  | -                      | V     | 1             |

| CLI DC Voltage                               | 1 meter, 800mV p-p Input                                  |                  | -                      | 3.3  | -                      | V     | 1             |

| CLI DC Voltage<br>(max cable length)         | 100 meters, 800mV p-p Input                               |                  | -                      | 1.3  | -                      | V     | 1             |

| MCLADJ DC Voltage                            | 1 meter, 800mV p-p Input                                  |                  | -                      | 4.1  | -                      | V     | 1             |

| MCLADJ DC Voltage<br>(max cable length)      | 100 meters, 800mV p-p Input                               |                  | -                      | 3.1  | -                      | V     | 1             |

GS1545

TEST LEVELS

1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

- 3. Production test at room temperature and nominal supply voltage.

- 4. QA sample test.

- 5. Calculated result based on Level 1,2, or 3.

- 6. Not tested. Guaranteed by design simulations.

- 7. Not tested. Based on characterization of nominal parts.

8. Not tested. Based on existing design/characterization data of similar product.

## AC ELECTRICAL CHARACTERISTICS - RECLOCKER STAGE

$V_{CC}$  = 5V,  $T_{A}$  = 0°C to 70°C unless otherwise shown.

| PARAMETER                                              | CONDITIONS                                                                                    | SYMBOL                                  | MIN         | TYP   | MAX | UNITS | TEST<br>LEVEL |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|-------------|-------|-----|-------|---------------|

| Serial Input – Data Rate                               | SMPTE 292M                                                                                    | BR <sub>SDI</sub>                       | 1.485/1.001 | 1.485 | -   | Gb/s  | 1             |

| Serial Input – Jitter Tolerance                        | Sinewave Modulation (p – p)                                                                   | J <sub>TOL</sub>                        | -           | 0.5   | -   | UI    | 1             |

| Phase Lock Time -<br>Asynchronous                      | Loop bandwidth approximately<br>1.4MHz @ 0.2 UI input jitter<br>modulation (LBCONT floating). | T <sub>ALOCK</sub>                      | -           | 200   | 250 | ms    | 7             |

| Phase Lock Time -<br>Synchronous                       | Loop bandwidth approximately<br>1.4MHz @ 0.2 UI input jitter<br>modulation (LBCONT floating). | Т <sub>SLOCK</sub>                      | -           | 2     | 4   | μs    | 7             |

| Carrier Detect Timer                                   | Loop bandwidth approximately<br>1.4MHz @ 0.2 UI input jitter<br>modulation (LBCONT floating). |                                         | -           | 12    | -   | ms    | 7             |

| Phase Lock/Unlock Timer<br>(1nF PLCAP)                 | Loop bandwidth approximately<br>1.4MHz @ 0.2 UI input jitter<br>modulation (LBCONT floating). |                                         | 60          | -     | -   | μs    | 7             |

| Serial Output - Signal Swing                           |                                                                                               | V <sub>SDO</sub>                        | 320         | 400   | 480 | mV    | 1             |

| Serial Digital Output –<br>Rise and Fall Time          |                                                                                               | t <sub>R-SDO</sub> , t <sub>F-SDO</sub> | -           | 150   | 270 | ps    | 7             |

| Serial Digital Output –<br>Rise and Fall Time Mismatch |                                                                                               |                                         | -           | -     | 100 | ps    | 7             |

| Serial Digital Output –<br>Intrinsic Jitter            | (RMS Jitter for clean PRN 2 <sup>23</sup> – 1<br>input on DDI/DDI inputs)                     | t <sub>iJ</sub>                         | -           | 10    | -   | ps    | 2             |

| Loop bandwidth                                         | @ 0.2UI jitter modulation<br>LBCONT floating                                                  |                                         | -           | 1.4   | -   | MHz   | 7             |

| Jitter peaking                                         |                                                                                               |                                         | -           | -     | 0.1 | dB    | 7             |

TEST LEVELS

1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

3. Production test at room temperature and nominal supply voltage.

- 4. QA sample test.

- 5. Calculated result based on Level 1,2, or 3.

- 6. Not tested. Guaranteed by design simulations.

7. Not tested. Based on characterization of nominal parts.

8. Not tested. Based on existing design/characterization data of similar product

## AC ELECTRICAL CHARACTERISTICS - EQUALIZER STAGE

$V_{CC} = 5V$ ,  $T_A = 0^{\circ}C$  to 70°C unless otherwise shown.

| PARAMETER                    | CONDITIONS   | SYMBOL          | MIN | TYP | MAX | UNITS | TEST<br>LEVEL |

|------------------------------|--------------|-----------------|-----|-----|-----|-------|---------------|

| Equalization                 | Belden 1694A |                 | -   | 110 | -   | m     | 2             |

| Input Resistance (SDI, SDI)  |              |                 | -   | 2.8 | -   | kΩ    | 7             |

| Input Capacitance (SDI, SDI) |              | C <sub>IN</sub> | -   | 2.0 | -   | pF    | 7             |

## AC ELECTRICAL CHARACTERISTICS - SERIAL TO PARALLEL STAGE

$V_{CC}$  = 5V,  $T_{A}$  = 0°C to 70°C unless otherwise shown.

| PARAMETER                             | CONDITIONS | SYMBOL                          | MIN         | TYP   | MAX  | UNITS | TEST<br>LEVEL |

|---------------------------------------|------------|---------------------------------|-------------|-------|------|-------|---------------|

| Parallel Output Clock Frequency       | SMPTE 292M | P <sub>CLK_OUT</sub>            | 74.25/1.001 | 74.25 | -    | MHz   | 1             |

| Clock Pulse Width Low                 | 15pF load  | t <sub>PWL</sub>                | 5           | 7     | -    | ns    | 7             |

| Clock Pulse Width High                | 15pF load  | t <sub>PWH</sub>                | 5           | 6     | -    | ns    | 7             |

| Output signal Rise/Fall time          | 15pF load  | t <sub>r</sub> , t <sub>f</sub> | -           | 2000  | 4000 | ps    | 7             |

| Output Signal Rise/Fall Time Matching | 15pF load  | t <sub>rfm</sub>                | -           | 1000  | 2000 | ps    | 7             |

| Output Setup Time                     | 15pF load  | t <sub>OD</sub>                 | 4           | 6     | -    | ns    | 2             |

| Output Hold Time                      | 15pF load  | t <sub>OH</sub>                 | 5           | 7     | -    | ns    | 2             |

#### TEST LEVELS

- 1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

- 2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

- 3. Production test at room temperature and nominal supply voltage.

- 4. QA sample test.

- 5. Calculated result based on Level 1,2, or 3.

- 6. Not tested. Guaranteed by design simulations.

- 7. Not tested. Based on characterization of nominal parts.

- 8. Not tested. Based on existing design/characterization data of similar product.

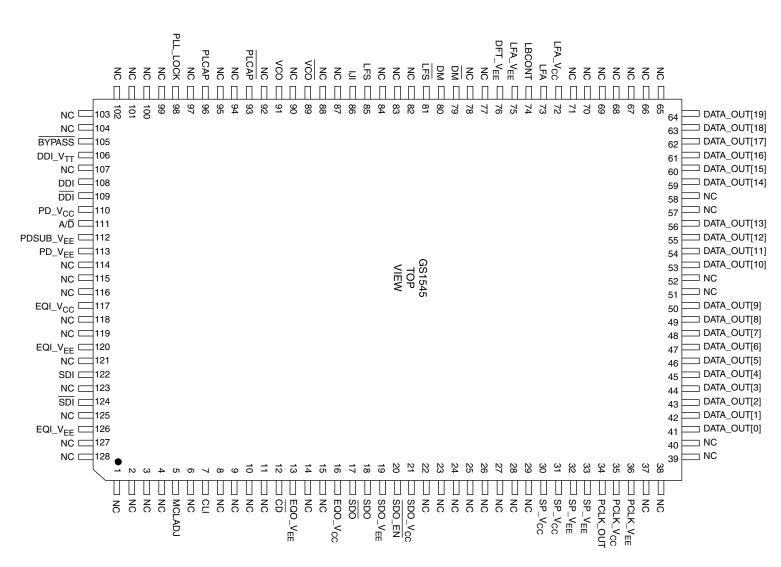

PIN CONNECTIONS

## **PIN DESCRIPTIONS**

| NUMBER                                                                                                                                                                                                                                                                                                                                             | SYMBOL              | LEVEL                  | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 1, 2, 3, 4, 6, 8, \\ 9, 10, 11, 14, \\ 15, 22, 23, 24, \\ 25, 26, 27, 28, \\ 29, 37, 38, 39, \\ 40, 51, 52, 57, \\ 58, 65, 66, 67, \\ 68, 69, 70, 71, \\ 77, 78, 82, 83, \\ 84, 87, 88, 90, \\ 92, 94, 95, 97, \\ 99, 100, 101, \\ 102, 103, 104, \\ 107, 114, 115, \\ 116, 118, 119, \\ 121, 123, 125, \\ 127, 128 \end{array}$ | NC                  |                        |        | No Connect. Leave these pins floating.                                                                                                                                                                                                                                                                                                                                                                            |

| 5                                                                                                                                                                                                                                                                                                                                                  | MCLADJ              | Analog                 | Input  | <b>Control Signal Input</b> . Adjusts the maximum amount of cable for the equalizer (from 0m to the maximum cable length). Normally the output is muted (latched to the last state) when the set maximum cable length is exceeded. To achieve maximum cable length, this pin should be left open (floating).                                                                                                      |

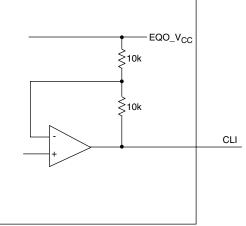

| 7                                                                                                                                                                                                                                                                                                                                                  | CLI                 | Analog                 | Output | Status Control Signal. The Cable Length Indication (CLI) signal provides approximate voltage representation of the amount of cable being equalized.                                                                                                                                                                                                                                                               |

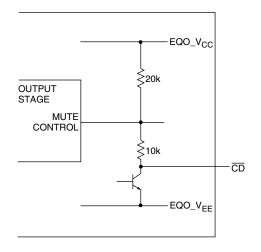

| 12                                                                                                                                                                                                                                                                                                                                                 | CD                  | Digital                | Output | <ul> <li>Status Signal. The Carrier Detect indicator is used as an output status signal.</li> <li>When the CD output is low, the carrier is present and the data output is active.</li> <li>When the CD output is high, the carrier is not present and the data output is muted (latched to the last state). This indicates that the maximum cable length as set by MCLADJ has been reached.</li> </ul>           |

| 13                                                                                                                                                                                                                                                                                                                                                 | EQO_V <sub>EE</sub> | Power                  | Input  | <b>Negative Supply</b> . Most negative power supply connection for Equalizer output buffer stage.                                                                                                                                                                                                                                                                                                                 |

| 16                                                                                                                                                                                                                                                                                                                                                 | EQO_V <sub>CC</sub> | Power                  | Input  | <b>Positive Supply</b> . Most positive power supply connection for Equalizer output buffer stage.                                                                                                                                                                                                                                                                                                                 |

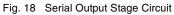

| 17, 18                                                                                                                                                                                                                                                                                                                                             | SDO, <del>SDO</del> | ECL/PECL<br>compatible | Output | Serial Data Output. Differential outputs. $50\Omega$ pull up resistors are included on chip.<br>Ensure that the trace length between the GS1545 and the GS1508 Cable driver is kept to a minimum and that a PCB trace characteristic impedance of $50\Omega$ is maintained between the GS1508 and the GS1545. $50\Omega$ end termination is recommended.                                                          |

| 19                                                                                                                                                                                                                                                                                                                                                 | SDO_V <sub>EE</sub> | Power                  | Input  | Negative Supply. Most negative power supply connection for serial data output stage.                                                                                                                                                                                                                                                                                                                              |

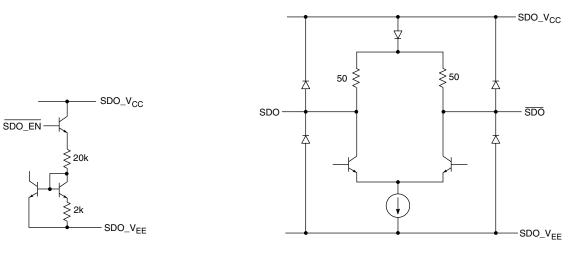

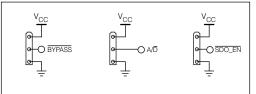

| 20                                                                                                                                                                                                                                                                                                                                                 | SDO_EN              | Power                  | Input  | Control Signal Input. Used to enable or disable the serial output stage.<br>If a loop through function is not required, then this pin should be tied<br>to the most positive power supply voltage.<br>When SDO_EN is tied to the most negative power supply voltage, the<br>SDO, SDO outputs are enabled.<br>When SDO_EN is tied to the most positive power supply voltage, the<br>SDO, SDO outputs are disabled. |

| 21                                                                                                                                                                                                                                                                                                                                                 | SDO_V <sub>CC</sub> | Power                  | Input  | Positive Supply. Most positive power supply connection for serial data output stage.                                                                                                                                                                                                                                                                                                                              |

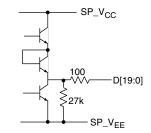

| 30, 31                                                                                                                                                                                                                                                                                                                                             | SP_V <sub>CC</sub>  | Power                  | Input  | <b>Positive Supply.</b> Most positive power supply connection for serial to parallel converter stage.                                                                                                                                                                                                                                                                                                             |

## PIN DESCRIPTIONS (Continued)

| NUMBER                                                                                     | SYMBOL               | LEVEL  | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------|----------------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32, 33                                                                                     | SP_V <sub>EE</sub>   | Power  | Input  | Negative Supply. Most negative power supply connection for the parallel output stage.                                                                                                                                                                                                                                                                           |

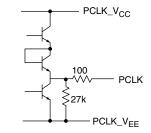

| 34                                                                                         | PCLK_OUT             | TTL    | Output | <b>Output Clock.</b> The device uses PCLK_OUT for clocking the output data stream from DATA_OUT[19:0]. This clock is also used to clock the data into the GS1500 HDTV Deformatter or GS1510 Deformatter.                                                                                                                                                        |

| 35                                                                                         | PCLK_V <sub>CC</sub> | Power  | Input  | Positive Supply. Most positive supply connection for parallel clock output stage.                                                                                                                                                                                                                                                                               |

| 36                                                                                         | PCLK_V <sub>EE</sub> | Power  | Input  | Negative Supply. Most negative power supply connection for parallel clock output stage.                                                                                                                                                                                                                                                                         |

| 41, 42, 43, 44,<br>45, 46, 47, 48,<br>49, 50, 53, 54,<br>55, 56, 59, 60,<br>61, 62, 63, 64 | DATA_OUT[19:0]       | TTL    | Output | <b>Parallel Data Output Bus.</b> The device outputs a 20 bit parallel data stream running at 74.25 or 74.25/1.001MHz on DATA_OUT[19:0]. DATA_OUT[19] is the MSB and DATA_OUT[0] is the LSB.                                                                                                                                                                     |

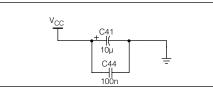

| 72                                                                                         | LFA_V <sub>CC</sub>  | Power  | Input  | Positive Supply. Loop filter most positive power supply connection.                                                                                                                                                                                                                                                                                             |

| 73                                                                                         | LFA                  | Analog | Output | Control Signal Output. Control voltage for GO1515 VCO.                                                                                                                                                                                                                                                                                                          |

| 74                                                                                         | LBCONT               | Analog | Input  | <b>Control Signal Input</b> . Used to provide electronic control of Loop Bandwidth.                                                                                                                                                                                                                                                                             |

| 75                                                                                         | $LFA_V_{EE}$         | Power  | Input  | Negative Supply. Loop filter most negative power supply connection.                                                                                                                                                                                                                                                                                             |

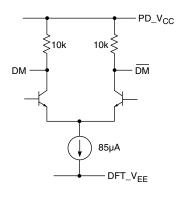

| 76                                                                                         | DFT_V <sub>EE</sub>  | Power  | Input  | Most negative power supply connection - enables the jitter<br>demodulator functionality. This pin should be connected to ground. If<br>left floating, the DM function is disabled resulting in a current saving of<br>340µA.                                                                                                                                    |

| 79, 80                                                                                     | DM, DM               | Analog | Output | <b>Test Signal</b> . Used for manufacturing test only.<br>These pins must be floating for normal operation.                                                                                                                                                                                                                                                     |

| 81, 85                                                                                     | LFS, LFS             | Analog | Input  | Loop Filter Connections.                                                                                                                                                                                                                                                                                                                                        |

| 86                                                                                         | IJ                   | Analog | Output | Status Signal Output. Approximates the amount of excessive jitter on the incoming DDI and DDI input.                                                                                                                                                                                                                                                            |

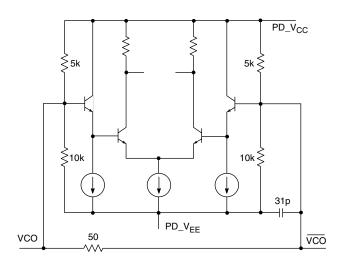

| 89                                                                                         | VCO                  | Analog | Input  | Control Signal Input. Input pin is AC coupled to ground using a $50\Omega$ transmission line.                                                                                                                                                                                                                                                                   |

| 91                                                                                         | VCO                  | Analog | Input  | Control Signal Input. Voltage controlled oscillator input. This pin is connected to the output pin of the GO1515 VCO. This pin must be connected to the GO1515 VCO output pin via a $50\Omega$ transmission line.                                                                                                                                               |

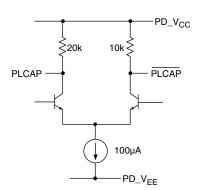

| 93, 96                                                                                     | PLCAP, PLCAP         | Analog | Input  | Control Signal Input. Phase lock detect time constant capacitor.                                                                                                                                                                                                                                                                                                |

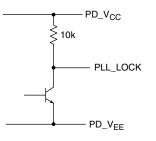

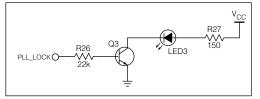

| 98                                                                                         | PLL_LOCK             | TTL    | Output | Status Indicator Signal. This signal is a combination (logical AND) of<br>the carrier detect and phase lock signals.<br>When input is present and PLL is locked, the PLL_LOCK goes high<br>and the outputs are valid. When the PLL_LOCK output is low the data<br>output is muted (latched at the last state).<br>PLL_LOCK is independent of the BYPASS signal. |

| 105                                                                                        | BYPASS               | TTL    | Input  | Control Signal Input. Selectable input that controls whether the input signal is reclocked or passed through the chip.<br>When BYPASS is high; the input signal is reclocked.<br>When BYPASS is low; the input signal is passed through the chip and not reclocked. Muting does not effect bypassed signal.                                                     |

## PIN DESCRIPTIONS (Continued)

| NUMBER   | SYMBOL                | LEVEL                    | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------------------|--------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 106      | DDI_V <sub>TT</sub>   | Analog                   | Input | Bias Input. Selectable input for interfacing standard ECL outputs requiring $50\Omega$ pull down to V <sub>TT</sub> power supply for a seamless interface. See Typical Application Circuit for recommended circuit application.                                                                                                                                                                                                            |

| 108, 109 | DDI, DDI              | Differential<br>ECL/PECL | Input | <b>Digital Data Input Signals.</b> Digital input signals from a GS1504<br>Equalizer or HD crosspoint switch.<br>Because of on chip $50\Omega$ termination resistors, a PCB trace<br>characteristic impedance of $50\Omega$ is recommended.                                                                                                                                                                                                 |

| 110      | PD_V <sub>CC</sub>    | Power                    |       | Positive Supply. Phase detector most positive power supply connection.                                                                                                                                                                                                                                                                                                                                                                     |

| 111      | A/D                   | TTL                      | Input | Control Signal Input. Used to select between the SDI/SDI input or DDI/DDI input.<br>When A/D is HIGH; the SDI/SDI input is selected.<br>When A/D is LOW; the DDI/DDI input is selected.                                                                                                                                                                                                                                                    |

| 112      | PDSUB_V <sub>EE</sub> | Power                    | Input | Substrate Connection. Connect to phase detector's most negative power supply.                                                                                                                                                                                                                                                                                                                                                              |

| 113      | PD_V <sub>EE</sub>    | Power                    | Input | Negative Supply. Phase detector most negative power supply connection.                                                                                                                                                                                                                                                                                                                                                                     |

| 117      | EQI_V <sub>CC</sub>   | Power                    | Input | Positive Supply. Most positive power supply connection for serial input stage.                                                                                                                                                                                                                                                                                                                                                             |

| 120, 126 | EQI_V <sub>EE</sub>   | Power                    | Input | Negative Supply. Most negative power supply connection for serial input stage.                                                                                                                                                                                                                                                                                                                                                             |

| 122, 124 | SDI, <u>SDI</u>       | Analog                   | Input | Serial Data Input Signals. AC coupled termination is recommended.<br>Single ended to differential conversion is also feasible. The SDI and<br>SDI input is selected when the $A/\overline{D}$ signal is high.<br>Ensure that the trace length between the input connector and the<br>GS1545 IC is kept to a minimum and that a PCB trace characteristic<br>impedance of 75 $\Omega$ is maintained between the connector and the<br>device. |

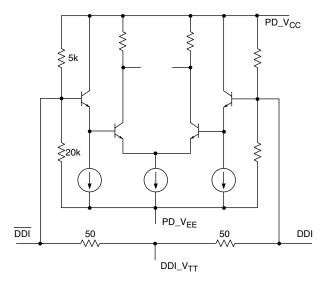

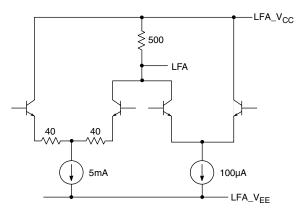

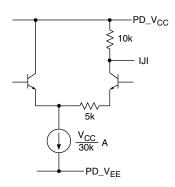

Fig. 1 DDI/DDI Input Circuit

Fig. 2 VCO/VCO Input Circuit

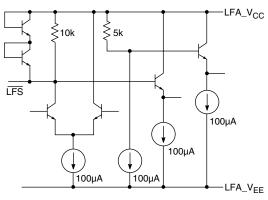

Fig. 3 DM/DM Output Circuit

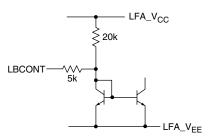

Fig. 5 LFA Circuit

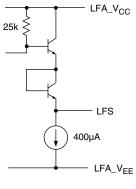

Fig. 6 LFS Output Circuit

Fig. 7 LFS Input Circuit

Fig. 8 PLL\_LOCK Output Circuit

Fig. 9 IJI Output Circuit

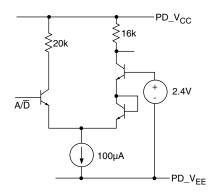

Fig. 10 A/D Input Circuit

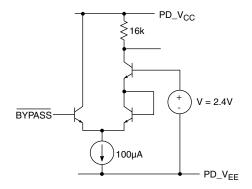

Fig. 11 BYPASS Circuit

Fig. 12 LBCONT Circuit

Fig. 13 D[19:0] Output Circuit

Fig. 14 PCLK Output Circuit

Fig. 15 SDO\_EN Circuit

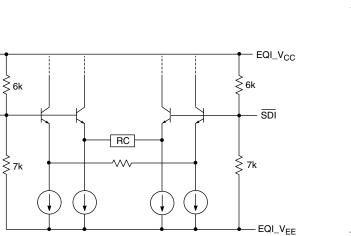

Fig. 16 Equalizer Input Circuit

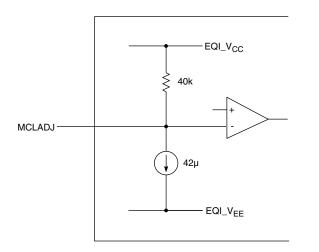

Fig. 17 MCLADJ Equivalent Circuit

SDI

#### DETAILED DESCRIPTION

The GS1545 is a single standard equalizing receiver for serial digital HDTV signals at 1.485Gb/s and 1.485/1.001Gb/s.

#### UNIQUE SLEW PHASE LOCK LOOP (S-PLL):

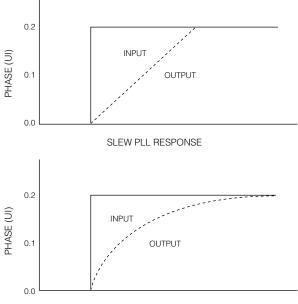

A unique feature of the GS1545 is the innovative slew phase lock loop (S-PLL). When a step phase change is applied to the PLL, the output phase gains constant rate of change with respect to time. This behaviour is termed slew. Figure 21 shows an example of input and output phase variation over time for slew and linear (conventional) PLLs. Since the slewing is a nonlinear behavior, the small signal analysis cannot be done in the same way as the standard PLL. However, it is still possible to plot input jitter transfer characteristics at a constant input jitter modulation.

Fig. 21 PLL Characteristics

Slew PLLs offer several advantages such as excellent noise immunity. Because of the infinite bandwidth for an infinitely small input jitter modulation (or jitter introduced by VCO), the loop corrects for that immediately thus the small signal noise of the VCO is cancelled. The GS1545 uses a very clean, external VCO called the GO1515 (*refer to the GO1515 Data Sheet for details*). In addition, the bi-level digital phase detector provides constant loop bandwidth that is predominantly independent of the data transition density. The loop bandwidth of a conventional tri-stable charge pump drops with reducing data transitions. During pathological signals, the data transition density reduces from 0.5 to 0.05, but the slew PLL's performance essentially remains unchanged. Because most of the PLL circuitry is digital, it is more like other digital systems which are generally more robust than their analog counterparts. Additionally, signals like DM/DM which represent the internal functionality can be generated without adding additional artifacts. Thus, system debugging is also possible with these features. The complete slew PLL is made up of several blocks including the phase detector, the charge pump and an external Voltage Controlled Oscillator (VCO).

#### DIGITAL INPUT BUFFER

The input buffer is a self-biased circuit. On-chip 50 $\Omega$  termination resistors provide a seamless interface for other HD-LINX<sup>TM</sup> products such as the GS1504 Adaptive Cable Equalizer. The digital input is selected by applying a logic low to the A/ $\overline{D}$  pin.

#### ANALOG INPUT

The HD serial data signal may be connected to the input pins (SDI/SDI) in either a differential or single ended configuration. AC coupling of the inputs is recommended, as the SDI and SDI inputs are internally biased at approximately 2.7 volts. The input signal passes through a variable gain equalizing stage whose frequency response closely matches the inverse cable loss characteristic. In addition, the variation of the frequency response with control voltage imitates the variation of the inverse cable loss characteristic with cable length. The analog input is selected by applying a logic high to the A/D pin.

The edge energy of the equalized signal is monitored by a detector circuit which produces an error signal corresponding to the difference between the desired edge energy and the actual edge energy. This error signal is integrated by an internal AGC filter capacitor providing a steady control voltage for the gain stage. As the frequency response of the gain stage is automatically varied by the application of negative feedback, the edge energy of the equalized signal is kept at a constant level which is representative of the original edge energy at the transmitter. The equalized signal is also DC restored, effectively restoring the logic threshold of the equalized signal to its correct level independent of shifts due to AC coupling.

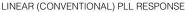

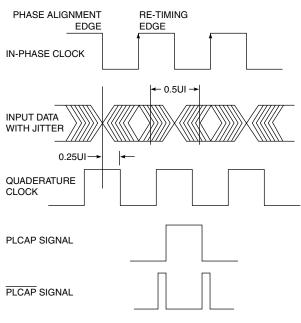

#### PHASE DETECTOR

The phase detector portion of the slew PLL used in the GS1545 is a bi-level digital phase detector. It indicates whether the data transition occurred before or after with respect to the falling edge of the internal clock. When the phase detector is locked, the data transition edges are aligned to the falling edge of the clock. The input data is then sampled by the rising edge of the clock, as shown in Figure 22. In this manner, the allowed input jitter is 1UI p-p in an ideal situation. However, due to setup and hold time, the GS1545 typically achieves 0.5UI p-p input jitter tolerance without causing any errors in this block. When the

signal is locked to the internal clock, the control output from the phase detector is refreshed at the transition of each rising edge of the data input. During this time, the phase of the clock drifts in one direction.

Fig. 22 Phase Detector Characteristics

During pathological signals, the amount of jitter that the phase detector will add can be calculated. By choosing the proper loop bandwidth, the amount of phase detector induced jitter can also be limited. Typically, for a 1.41MHz loop bandwidth at 0.2UI input jitter modulation, the phase detector induced jitter is about 0.015UIp-p. This is not very significant, even for the pathological signals.

#### CHARGE PUMP

The charge pump in a slew PLL is different from the charge pump in a linear PLL. There are two main functions of the charge pump. One function is to hold the frequency information of the input data. This information is held by  $C_{CP1}$ , which is connected between LFS and  $\overline{LFS}$ . The other capacitor, C<sub>CP2</sub> between LFS and LFA\_GND is used to remove common mode noise. Both  $C_{CP1}$  and  $C_{CP2}$  should be the same value. The second function of the charge pump is to provide a binary control voltage to the VCO depending upon the phase detector output. The output pin, LFA controls the VCO. Internally there is a 500 $\Omega$  pull-up resistor, which is driven with a 100 $\mu$ A current called I<sub>P</sub>. Another analog current IF, with 5mA maximum drive proportional to the voltage across the C<sub>CP1</sub>, is applied at the same node. The voltage at the LFA node is  $V_{IFAVCC}$  - 500( $I_P$ + $I_F$ ) at any time.

Because of the integrator,  $I_F$  changes very slowly whereas  $I_P$  could change at the positive edge of the data transition as often as a clock period. In the locked position, the average voltage at the LFA ( $V_{LFA_VCC} - 500(I_P/2+I_F)$ ) is such that VCO generates frequency *f*, equal to the data rate clock frequency. Since  $I_P$  is changing all the time between 0A and 100µA, there will be two levels generated at the LFA output.

## vco

The GO1515 is an external hybrid VCO, which has a centre frequency of 1.485GHz and is also guaranteed to provide 1.485/1.001GHz within the control voltage (3.1V - 4.65V) of the GS1545 over process, power supply and temperature. The GO1515 is a very clean frequency source and, because of the internal high Q resonator, it is an order of magnitude more immune to external noise as compared to on-chip VCOs.

The VCO gain, K*f*, is nominally 16MHz/V. The control voltage around the average LFA voltage will be 500 x  $I_P/2$ . This will produce two frequencies off from the centre by  $f=Kf \times 500 \times I_P/2$ .

#### LBCONT

The LBCONT pin is used to adjust the loop bandwidth by externally changing the internal charge pump current. For maximum loop bandwidth, connect LBCONT to the most positive power supply. For medium loop bandwidth, connect LBCONT through a pull-up resistor ( $R_{PULL-UP}$ ). For low loop bandwidth, leave LBCONT floating. The formula below shows the loop bandwidth for various configurations.

$$LBW = LBW_{NOMINAL} \times \frac{(25k\Omega + R_{PULL-UP})}{(5k\Omega + R_{PUUL-UP})}$$

where LBW nominal is the loop bandwidth when LBCONT is left floating.

#### LOOP BANDWIDTH OPTIMIZATION

Since the feed back loop has only digital circuits, the small signal analysis does not apply to the system. The effective loop bandwidth scales with the amount of input jitter modulation index.

#### PHASE LOCK

The phase lock circuit is used to determine the phase locked condition. It is done by generating a quadrature clock by delaying the in-phase clock (the clock whose falling edge is aligned to the data transition) by 166ps (0.25UI at 1.5GHz) with the tolerance of 0.05UI. When the PLL is locked, the falling edge of the in-phase clock is aligned with the data edges as shown in Figure 23. The quadrature clock is in a logic high state in the vicinity of input data transitions. The quadrature clock is sampled and latched by positive edges of the data transitions. The generated signal is low pass filtered with an RC network. The R is an on-chip  $20k\Omega$  resistor and  $C_{PL}$  is an external capacitor (recommended value 10nF). The time constant is about 67µs, or more than a video line.

Fig. 23 PLL Circuit Principles

If the signal is not locked, the data transition phase could be anywhere with respect to the internal clock or the quadrature clock. In this case, the normalized filtered sample of the quadrature clock will be 0.5. When VCO is locked to the incoming data, data will only sample the quadrature clock when it is logic high. The normalized filtered sample quadrature clock will be 1.0. We chose a threshold of 0.66 to generate the phase lock signal. Because the threshold is lower than 1, it allows jitter to be greater than 0.5UI before the phase lock circuit reads it as "not phase locked".

#### **INPUT JITTER INDICATOR (IJI)**

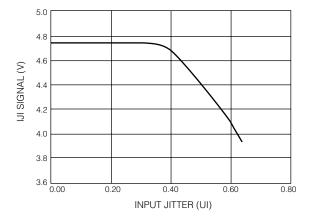

This signal indicates the amount of excessive jitter (beyond the quadrature clock window 0.5UI), which occurs beyond the guadrature clock window (see Figure 23). All the input data transitions occurring outside the quadrature clock window, will be captured and filtered by the low pass filter as mentioned in the Phase Lock section. The running time average of the ratio of the transitions inside the quadrature clock and outside the quadrature is available at the PLCAP/PLCAP pins. A signal, IJI, which is the buffered signal available at the PLCAP is provided so that loading does not effect the filter circuit. The signal at IJI is referenced with the power supply such that the factor  $V_{IJI}/V_{CC}$  is a constant over process and power supply for a given input jitter modulation. The IJI signal has  $10k\Omega$  output impedance. Figure 24 shows the relationship of the IJI signal with respect to the sine wave modulated input jitter.

| P-P SINE WAVE JITTER IN UI | IJI VOLTAGE |

|----------------------------|-------------|

| 0.00                       | 4.75        |

| 0.15                       | 4.75        |

| 0.30                       | 4.75        |

| 0.39                       | 4.70        |

| 0.45                       | 4.60        |

| 0.48                       | 4.50        |

| 0.52                       | 4.40        |

| 0.55                       | 4.30        |

| 0.58                       | 4.20        |

| 0.60                       | 4.10        |

| 0.63                       | 3.95        |

Fig. 24 Input Jitter Indicator (Typical at  $T_A = 25^{\circ}C$ )

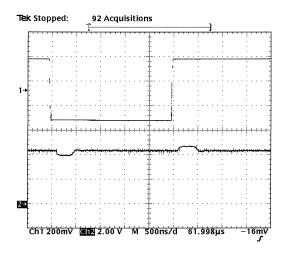

#### JITTER DEMODULATION (DM)

The differential jitter demodulation (DM) signal is available at the DM and  $\overline{\text{DM}}$  pins. This signal is the phase correction signal of the PLL loop, which is amplified and buffered. If the input jitter is modulated, the PLL tracks the jitter if it is within loop bandwidth. To track the input jitter, the VCO has to be adjusted by the phase detector via the charge pump. Thus, the signal which controls the VCO contains the information of the input jitter modulation. The jitter demodulation signal is only valid if the input jitter is less than 0.5Ulp-p. The DM/DM signals have 10k $\Omega$  output impedance, which could be low pass filtered with appropriate capacitors to eliminate high frequency noise. DFT\_V<sub>EE</sub> should be connected to GND to activate DM/DM signals.

The DM signals can be used as diagnostic tools. Assume there is an HDTV SDI source, which contains excessive noise during the horizontal blanking because of the transient current flowing in the power supply. In order to discover the source of the noise, one could probe around the source board with a low frequency oscilloscope (Bandwidth < 20MHz) that is triggered with an appropriately filtered DM/DM signal. The true cause of the modulation will be synchronous and will appear as a stationary signal with respect to the DM/DM signal.

Figure 25 shows an example of such a situation. An HDTV SDI signal is modulated with a modulation signal causing about 0.2UI jitter in Figure 25 (Channel 1). The GS1545 receives this signal and locks to it. Figure 25 (Channel 2) shows the DM signal. Notice the wave shape of the DM signal, which is synchronous to the modulating signal. The DM/DM signal could also be used to compare the output jitter of the HDTV signal source.

Fig. 25 Jitter Demodulation Signal

#### LOCK LOGIC

Logic is used to produce the PLL\_LOCK signal which is based on the LFS signal and phase lock signal. When there is not any data input, the integrator will charge and eventually saturate at either end. By sensing the saturation of the integrator, it is determined that no data is present. If either data is not present or phase lock is low, the lock signal is made low. Logic signals are used to acquire the frequency by sweeping the integrator. Injecting a current into the summing node of the integrator achieves the sweep. The sweep is disabled once phase lock is asserted. The direction of the sweep is also changed once LFS saturates at either end.

#### BYPASS

The BYPASS block bypasses the reclocked/mute path of the data whenever a logic low input is applied to the BYPASS input. In the bypass mode, the mute does not have any effect on the outputs. Also, the internal PLL still locks to a valid HDTV signal and shows PLL\_LOCK.

#### SERIAL OUTPUT STAGE

The serial output signals have a nominal voltage of 400mVpp differential, or 200mVpp single ended when terminated with  $50\Omega$ .

## SDO\_EN

The SDO\_EN enables or disables the serial output driver. To disable the driver, tie SDO\_EN to V<sub>CC</sub>. To enable the driver, tie SDO\_EN to V<sub>EE</sub>. When disabled, the supply current is reduced by approximately 10mA.

## A/D

$A/\overline{D}$  is a TTL compatible input pin used to select between the analog or digital input. When  $A/\overline{D}$  is at logic high, the analog input is selected. When  $A/\overline{D}$  is low, the digital input is enabled.

## CLI

The voltage output of CLI pin is proportional to the amount of cable present at the GS1545 analog input. With 0m of cable (800mV input signal levels), the CLI output voltage is approximately 3.3V. As the cable length increases, the CLI voltage decreases providing correlation between the CLI voltage and cable length. CLI voltage will be a function of the launch voltage and cable type/quality.

#### MCLADJ

The outputs of the GS1545 can be muted when the input signal decreases below a preselected input level. The MCLADJ pin may be left unconnected for applications where output muting is not required. The use of a Carrier Detect function with a fixed internal reference does not solve this problem since the signal to noise ratio on the circuit board could be significantly less than the default signal detection level set by the on chip reference.

## CARRIER DETECT

The  $\overline{CD}$  pin is a TTL compatible output signal. When a carrier is detected at the analog input, the  $\overline{CD}$  pin is pulled low. When a carrier is not detected, the  $\overline{CD}$  will be pulled high.

#### SERIAL TO PARALLEL CONVERTER

The high-speed serial to parallel converter accepts differential clock and data signals from the reclocker core. The S/P core converts this serial output into a 20-bit wide data stream (D[19:0]). It also provides a parallel clock, which is 1/20th the serial clock rate (PCLK\_OUT). The outputs of the S/P block are TTL compatible. When the PLL loses lock, the parallel clock continues to freewheel. The parallel clock and data outputs were designed for seamless interfaces to the GS1500 and GS1510.

CS1242

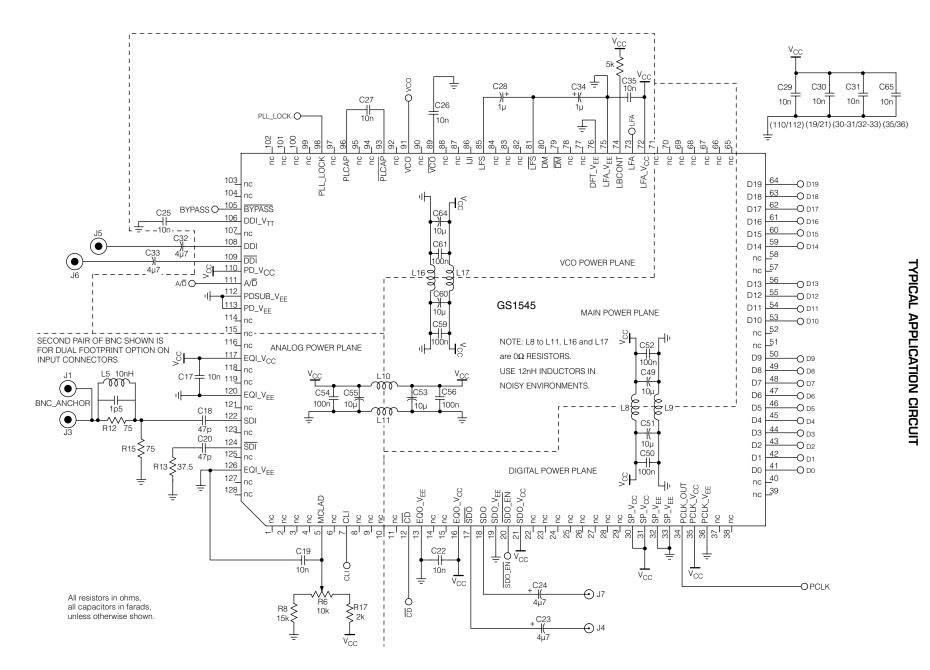

## TYPICAL APPLICATION CIRCUIT (continued)

#### GO1515 VCO

#### **GS1545 CONFIGURATION JUMPERS**

POWER CONNECT

#### GS1545 LOCK DETECT

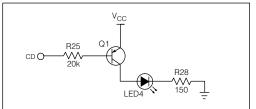

GS1545 CD

All resistors in ohms, all capacitors in farads, unless otherwise shown.

#### **APPLICATION INFORMATION**

Please refer to the EBHDRX evaluation board documentation for more detailed application and circuit information on using the GS1545 with the GS1500 and GS1510 Deformatters.

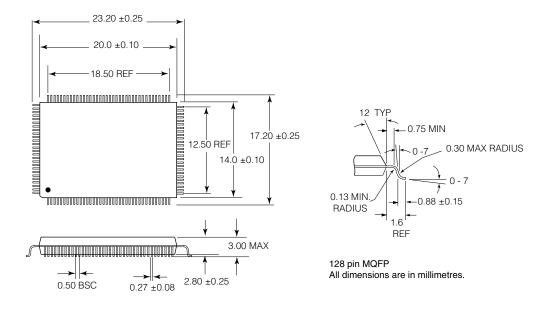

## PACKAGE DIMENSIONS

#### CAUTION ELECTROSTATIC SENSITIVE DEVICES DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

## DOCUMENT IDENTIFICATION

PRELIMINARY DATA SHEET The product is in a preproduction phase and specifications are subject to change without notice.

#### GENNUM CORPORATION

#### MAILING ADDRESS: P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3 Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946

SHIPPING ADDRESS: 970 Fraser Drive, Burlington, Ontario, Canada L7L 5P5

#### **REVISION NOTES:**

Upgraded to Preliminary Data Sheet; Updated Functional Block Diagram and Typical Application Circuit; Updated Absolute Maximum Ratings, AC and DC Electrical Characteristics Tables; Updated Pin Connections and Description.

For latest product information, visit www.gennum.com

GENNUM JAPAN CORPORATION C-101, Miyamae Village, 2-10-42 Miyamae, Suginami-ku Tokyo 168-0081, Japan Tel. +81 (03) 3334-7700 Fax. +81 (03) 3247-8839

GENNUM UK LIMITED 25 Long Garden Walk, Farnham, Surrey, England GU9 7HX Tel. +44 (0)1252 747 000 Fax +44 (0)1252 726 523

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

© Copyright May 2000 Gennum Corporation. All rights reserved. Printed in Canada.