# **CRD5376**

# Multichannel Seismic Reference Design

# Features

- Four Channel Seismic Acquisition Node

- CS3301 geophone amplifiers (2x)

- CS3302 hydrophone amplifiers (2x)

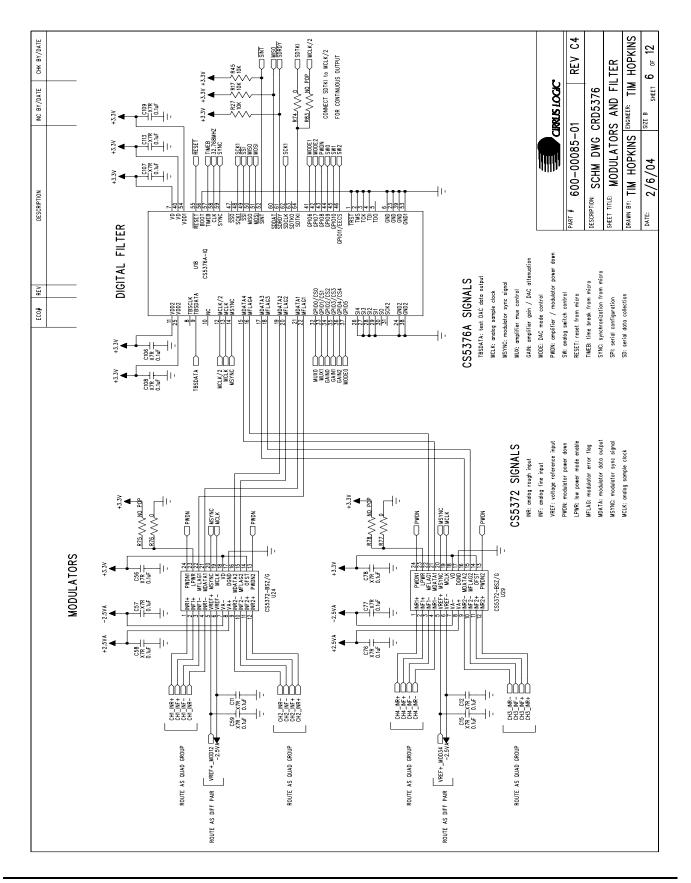

- CS5372 dual  $\Delta\Sigma$  modulators (2x)

- CS5376A quad digital filter (1x)

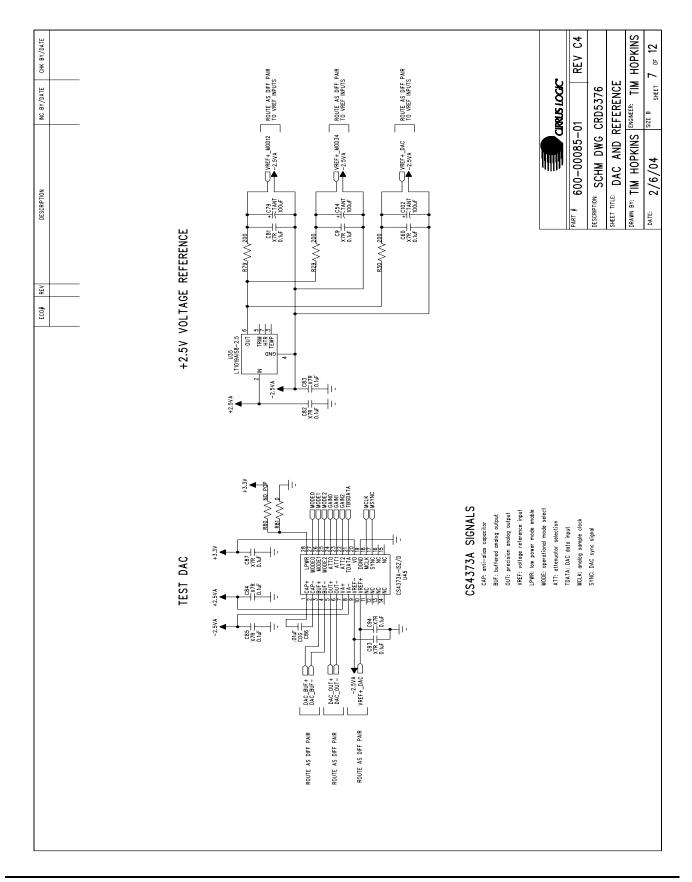

- CS4373A  $\Delta\Sigma$  test DAC (1x)

- Precision voltage reference

- Clock recovery PLL

- On-board Microcontroller

- SPI™ interface to digital filter

- USB communication with PC

- PC Evaluation Software

- Register setup & control

- FFT frequency analysis

- Time domain analysis

- Noise histogram analysis

# **General Description**

The CRD5376 board is a reference design for the Cirrus Logic multichannel seismic chip set. Data sheets for the CS3301, CS3302, CS4373A, CS5371/72, and CS5376A devices should be consulted when using the CRD5376 reference design.

Pin headers connect external differential geophone or hydrophone sensors to the analog inputs of the measurement channels. An on-board test DAC creates precision differential analog signals for in-circuit performance testing without an external signal source.

The reference design includes an 8051-type microcontroller with hardware SPI<sup>™</sup> and USB serial interfaces. The microcontroller communicates with the digital filter via SPI and with the PC evaluation software via USB. The PC evaluation software controls register and coefficient initialization and performs time domain, histogram, and FFT frequency analysis on captured data.

ORDERING INFORMATION CRD5376

Reference Design

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find the one nearest to you go to <u>www.cirrus.com</u>

#### IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANT-ED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICA-TIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EM-PLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

Windows is a registered trademark of Microsoft Corporation.

SPI is a trademark of Motorola, Inc.

Microwire is a trademark of National Semiconductor Corporation.

# CRD5376

# TABLE OF CONTENTS

| 1. | INITIAL SETUP                                   | 5  |

|----|-------------------------------------------------|----|

|    | 1.1 Kit Contents                                | 5  |

|    | 1.2 Hardware Setup                              | 5  |

|    | 1.2.1 Default Jumper Settings                   |    |

|    | 1.3 Software Setup                              |    |

|    | 1.3.1 PC Requirements                           |    |

|    | 1.3.2 Seismic Evaluation Software Installation  |    |

|    | 1.3.3 USBXpress Driver Installation             |    |

|    | 1.3.4 Launching the Seismic Evaluation Software |    |

|    | 1.4 Self-Testing CRD5376                        | 9  |

|    | 1.4.1 Noise Test                                |    |

|    | 1.4.2 Distortion Test                           |    |

| 2  | HARDWARE DESCRIPTION                            |    |

| 2. | 2.1 Block Diagram                               |    |

|    | 2.2 Analog Hardware                             |    |

|    | 2.2.1 Analog Inputs                             |    |

|    | 2.2.2 Differential Amplifiers                   |    |

|    | 2.2.3 Delta-Sigma Modulators                    |    |

|    | 2.2.4 Delta-Sigma Test DAC                      |    |

|    | 2.2.4 Delta-Signa Test DAC                      |    |

|    |                                                 |    |

|    | 2.3 Digital Hardware                            |    |

|    | 2.3.1 Digital Filter                            |    |

|    |                                                 |    |

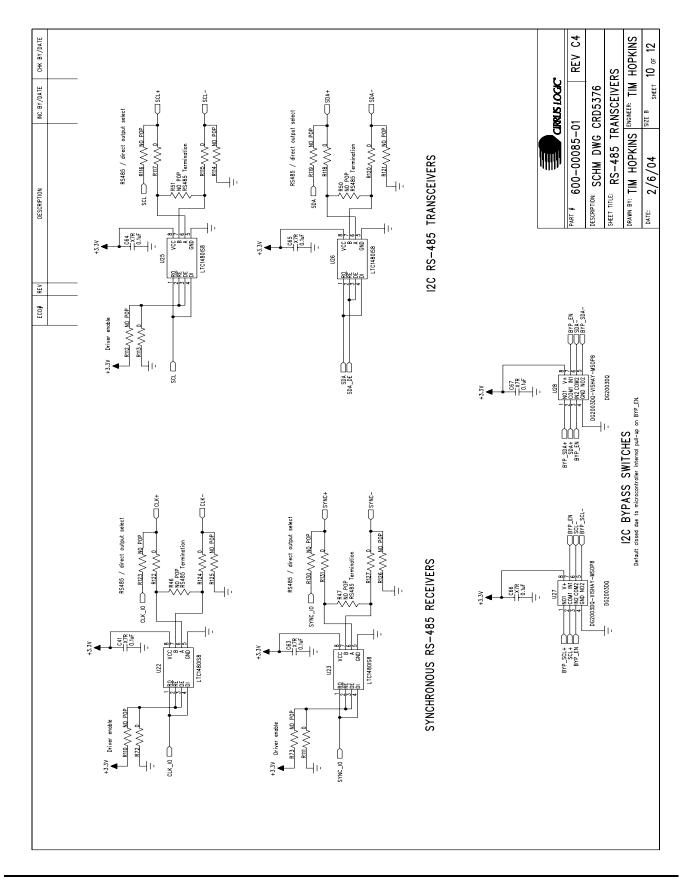

|    | 2.3.3 Phase Locked Loop                         |    |

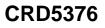

|    | 2.3.4 RS-485 Telemetry                          |    |

|    | 2.3.5 UART Connection                           |    |

|    | 2.3.6 External Connector                        |    |

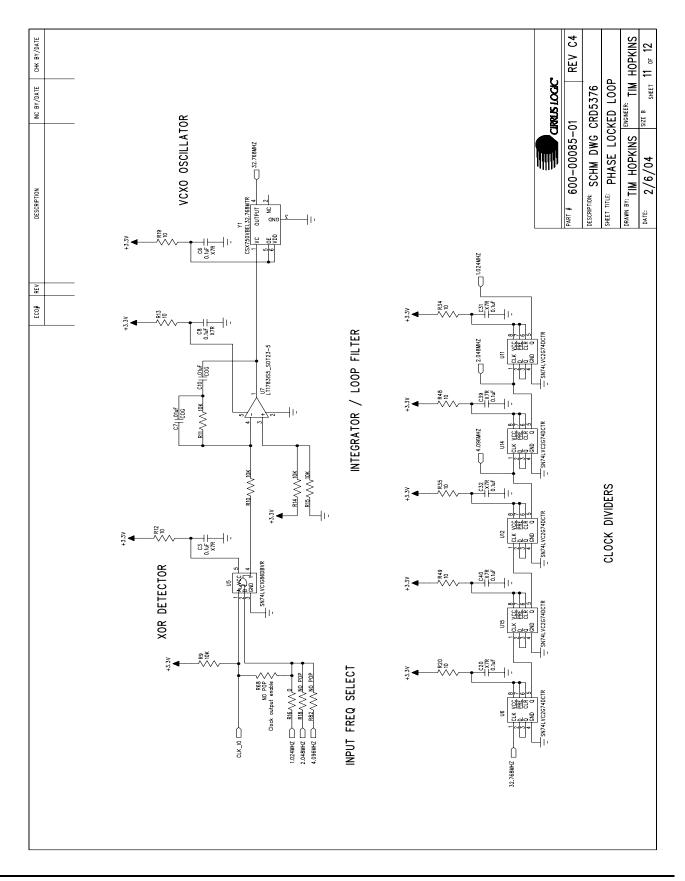

|    | 2.4 Power Supplies                              |    |

|    | 2.4.1 Analog Voltage Regulators                 |    |

|    | 2.5 PCB Layout                                  |    |

|    | 2.5.1 Layer Stack                               |    |

|    | 2.5.2 Differential Pairs                        |    |

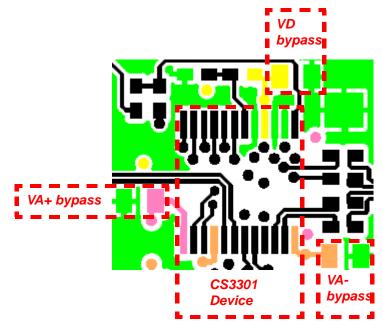

| •  | 2.5.3 Bypass Capacitors                         |    |

| 3. | SOFTWARE DESCRIPTION                            |    |

|    | 3.1 Menu Bar                                    |    |

|    | 3.2 About Panel                                 |    |

|    | 3.3 Setup Panel                                 |    |

|    | 3.3.1 USB Port                                  |    |

|    | 3.3.2 Digital Filter                            |    |

|    | 3.3.3 Analog Front End                          |    |

|    | 3.3.4 Test Bit Stream                           |    |

|    | 3.3.5 Gain/Offset                               |    |

|    | 3.3.6 Data Capture                              |    |

|    | 3.3.7 External Macros                           |    |

|    | 3.4 Analysis Panel                              |    |

|    | 3.4.1 Test Select                               |    |

|    | 3.4.2 Statistics                                |    |

|    | 3.4.3 Plot Enable                               |    |

|    | 3.4.4 Cursor                                    |    |

|    | 3.4.5 Zoom                                      |    |

|    | 3.4.6 Refresh                                   | 44 |

# CRD5376

|    | 3.4.7 Harmonics       |    |

|----|-----------------------|----|

|    | 3.4.8 Spot Noise      |    |

|    | 3.4.9 Plot Error      |    |

|    | 3.5 Control Panel     | 45 |

|    | 3.5.1 DF Registers    |    |

|    | 3.5.2 DF Commands     |    |

|    | 3.5.3 SPI             |    |

|    | 3.5.4 Macros          |    |

|    | 3.5.5 GPIO            |    |

|    | 3.5.6 Customize       |    |

|    | 3.5.7 External Macros |    |

| 4. | BILL OF MATERIALS     | 49 |

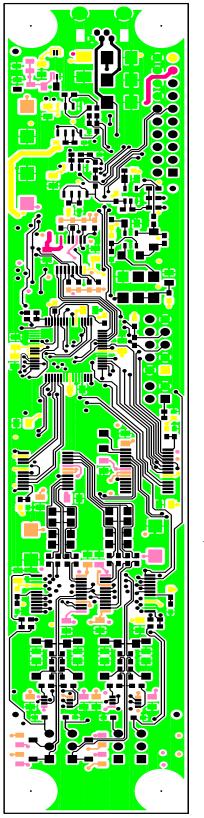

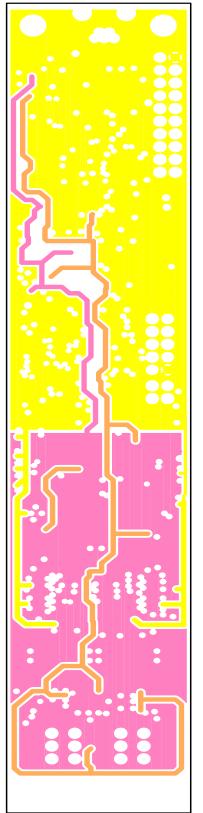

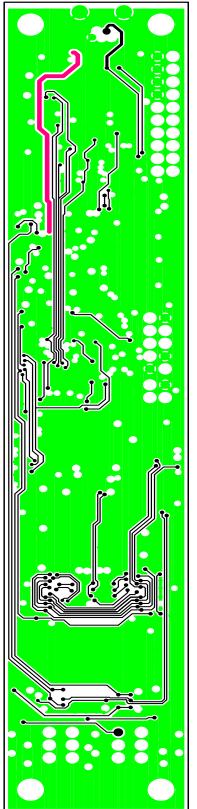

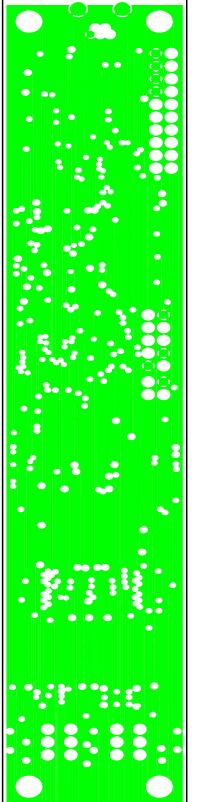

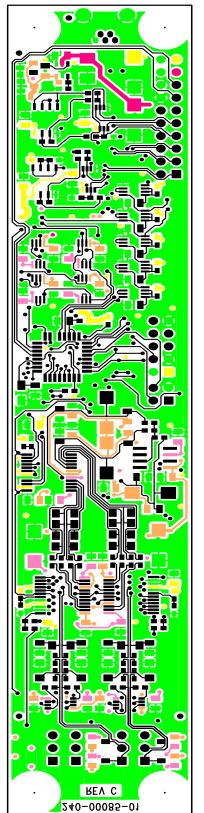

| 5. | LAYER PLOTS           | 51 |

| 6. | SCHEMATICS            |    |

|    |                       |    |

# **LIST OF FIGURES**

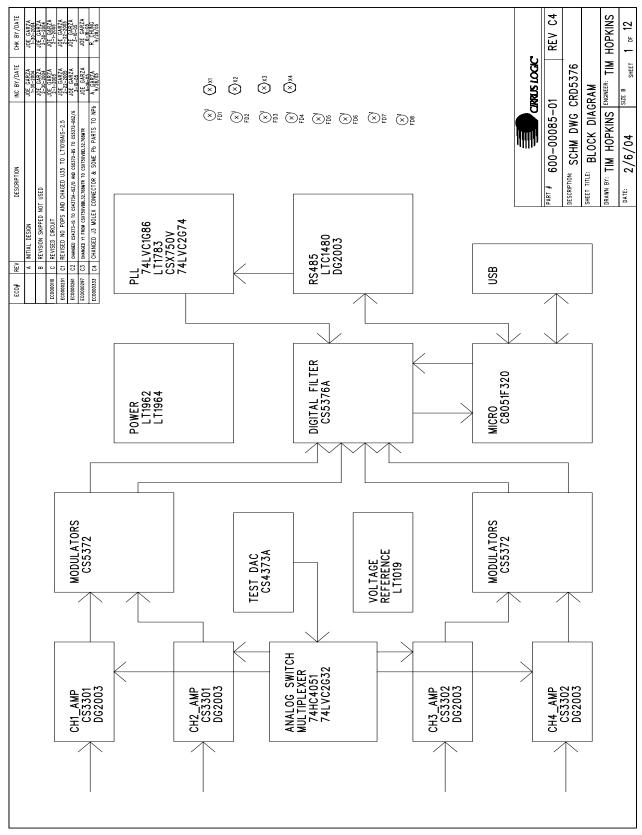

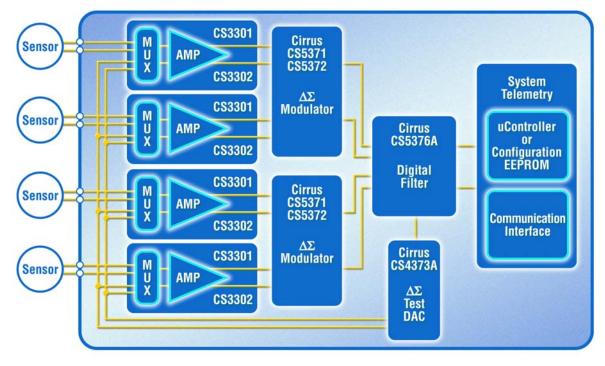

| Figure 1. CRD5376 Block Diagram      | 11 |

|--------------------------------------|----|

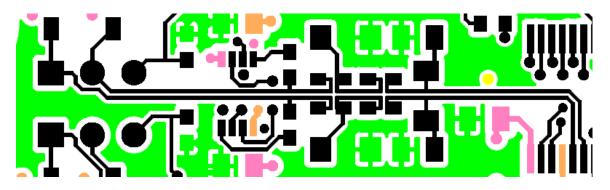

| Figure 2. Differential Pair Routing  |    |

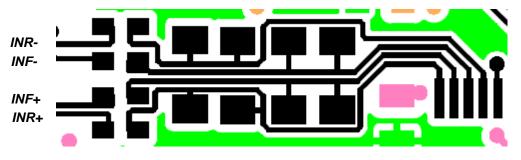

| Figure 3. Quad Group Routing         |    |

| Figure 4. Bypass Capacitor Placement | 31 |

# LIST OF TABLES

| Table 1. Amplifier Pin 13 Jumper Settings       | 6  |

|-------------------------------------------------|----|

| Table 2. SDTKI Input Jumper Settings            | 6  |

| Table 3. Analog Components LPWR Jumper Settings | 6  |

| Table 4. PLL Clock Input Jumper Settings        | 6  |

| Table 5. Pin Header Input Connections           | 12 |

| Table 6. Analog Switch Settings                 | 15 |

| Table 7. Amplifier Pin 13 Jumper Settings       | 16 |

| Table 8. SDTKI Input Jumper Settings            | 22 |

| Table 9. Analog Components LPWR Jumper Settings | 22 |

| Table 10. Clock Input / Output Jumper Settings  | 25 |

|                                                 |    |

# 1. INITIAL SETUP

#### 1.1 Kit Contents

The CRD5376 reference design kit includes:

- CRD5376 reference design board

- USB cable (A to mini-B)

- Software download information card

The following are required to operate CRD5376, and are not included:

- Bipolar power supply with clip lead outputs (+/- 3.3 V @ 100 mA)

- PC running Windows 2000 or XP with an available USB port

- Internet access to download the evaluation software

# 1.2 Hardware Setup

To set up the CRD5376 reference design hardware:

- Verify all jumpers are in the default settings (see next section).

- With power off, connect the CRD5376 power inputs to the power supply outputs.

J8 pin 17 = -3.3 V J8 pin 18 = 0 V J8 pin 19 = +3.3 V J8 pin 20 = 0 V

- Connect the USB cable between the CRD5376 USB connector and the PC USB port.

- Proceed to the Software Setup section to install the evaluation software and USB driver.

# 1.2.1 Default Jumper Settings

\* indicates the default jumper installation for CRD5376.

| Amplifier |     | CS3301       | CS3302 |

|-----------|-----|--------------|--------|

| CH1       | U16 | *R128 + *R84 | R129   |

| CH2       | U2  | *R86 + *R92  | R87    |

| CH3       | U33 | R95 + R132   | *R94   |

| CH4       | U3  | R58 + R100   | *R59   |

Table 1. Amplifier Pin 13 Jumper Settings

| CS5376A | uController | MCLK/2 |

|---------|-------------|--------|

| SDTKI   | *R74        | R83    |

Table 2. SDTKI Input Jumper Settings

|     | Component | NPWR | LPWR |

|-----|-----------|------|------|

| U16 | CS3301    | *R61 | R60  |

| U2  | CS3301    | *R89 | R88  |

| U33 | CS3302    | *R97 | R96  |

| U3  | CS3302    | *R71 | R70  |

| U24 | CS5372    | *R76 | R75  |

| U29 | CS5372    | *R77 | R78  |

| U45 | CS4373A   | *R81 | R80  |

Table 3. Analog Components LPWR Jumper Settings

| Input Clock | Jumper |

|-------------|--------|

| 1.024 MHz   | *R16   |

| 2.048 MHz   | R18    |

| 4.096 MHz   | R82    |

Table 4. PLL Clock Input Jumper Settings

#### 1.3 Software Setup

#### 1.3.1 PC Requirements

The PC hardware requirements for the Cirrus Seismic Evaluation system are:

- Windows XP, Windows 2000, Windows NT

- Intel Pentium 600MHz or higher microprocessor

- VGA resolution or higher video card

- Minimum 64MB RAM

- Minimum 40MB free hard drive space

#### 1.3.2 Seismic Evaluation Software Installation

**Important:** For reliable USB communication, the USBXpress driver must be installed after the Seismic Evaluation Software installation but **before** launching the application. The USBXpress driver files are included in a sub-folder as part of the installation.

To install the Cirrus Logic Seismic Evaluation Software:

- Go to the Cirrus Logic Industrial Software web page (<u>http://www.cirrus.com/industrialsoftware</u>). Click the link for *"Cirrus Seismic Evaluation GUI"* to get to the download page and then click the link for *"Cirrus Seismic Evaluation GUI Release Vxx"* (*xx* indicates the version number).

- Read the software license terms and click "Accept" to download the "SeismicEvalGUI\_vxx.zip" file to any directory on the PC.

- Unzip the downloaded file to any directory and a "distribution" sub-folder containing the installation application will automatically be created.

- Open the *"distribution"* sub-folder and run *"setup.exe"*. If the Seismic Evaluation Software has been previously installed, the uninstall wizard will automatically remove the previous version and you will need to run *"setup.exe"* again.

- Follow the instructions presented by the Cirrus Seismic Evaluation Installation Wizard. The default installation location is "C:\Program Files\Cirrus Seismic Evaluation".

An application note, AN271 - *Cirrus Seismic Evaluation GUI Installation Guide*, is available from the Cirrus Logic web site with step-by-step instructions on installing the Seismic Evaluation Software.

#### 1.3.3 USBXpress Driver Installation

**Important:** For reliable USB communication, the USBXpress driver must be installed after the Seismic Evaluation Software installation but **before** launching the application. The USBXpress driver files are included in a sub-folder as part of the installation.

The Cirrus Logic Seismic Evaluation Software communicates with CRD5376 via USB using the USBXpress driver from Silicon Laboratories (<u>http://www.silabs.com</u>). For convenience, the USBXpress driver files are included as part of the installation package.

To install the USBXpress driver (after installing the Seismic Evaluation Software):

• Connect CRD5376 to the PC through an available USB port and apply power. The PC will detect

CRD5376 as an unknown USB device.

- If prompted for a USB driver, skip to the next step. If not, using Windows Hardware Device Manager go to the properties of the unknown USB API device and select "Update Driver".

- Select "Install from a list or specific location", then select "Include this location in the search" and then browse to "C:\Program Files\Cirrus Seismic Evaluation\Driver\". The PC will recognize and install the USBXpress device driver.

- After driver installation, cycle power to CRD5376. The PC will automatically detect it and add it as a USBXpress device in the Windows Hardware Device Manager.

An application note, AN271 - *Cirrus Seismic Evaluation GUI Installation Guide*, is available from the Cirrus Logic web site with step-by-step instructions on installing the USBXpress driver.

# 1.3.4 Launching the Seismic Evaluation Software

**Important:** For reliable USB communication, the USBXpress driver must be installed after the Seismic Evaluation Software installation but **before** launching the application. The USBXpress driver files are included in a sub-folder as part of the installation.

To launch the Cirrus Seismic Evaluation Software, go to:

or:

• C:\Program Files\Cirrus Seismic Evaluation\SeismicGUI.exe

For the most up-to-date information about the software, please refer to it's help file:

• Within the software: *Help ⇒ Contents*

or:

or:

• C:\Program Files\Cirrus Seismic Evaluation\SEISMICGUI.HLP

#### 1.4 Self-Testing CRD5376

Noise and distortion self-tests can be performed once hardware and software setup is complete.

First, initialize the CRD5376 reference design:

- Launch the evaluation software and apply power to CRD5376.

- Click 'OK' on the **About** panel to get to the **Setup** panel.

- On the Setup panel, select Open Target on the USB Port sub-panel.

- When connected, the Board Name and MCU code version will be displayed.

#### 1.4.1 Noise Test

Noise performance of the measurement channel can be tested as follows:

• Set the controls on the **Setup** panel to match the picture:

| Cirrus Seismic Evaluation V2.4<br>File Setup! Analysis! Control! DataCapture! Help |                                                                                         |                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Eile Setup! Analysis!                                                              | Control! DataCapture! Help DIGITAL FILTER                                               | ANALOG FRONT END                                                                                                                                                                                                                                                                                           |  |  |

| CLOSE TARGET                                                                       | Channel Set 🖨 4 Channel Output Rate 🖨 500 SPS                                           | Amp Mux     TERM     Gain     x1       DAC Mode     PWDN     SW     Disable All                                                                                                                                                                                                                            |  |  |

| Board Name<br>CRD5376 RevC                                                         | Output Filter FIR2 Output<br>FIR Coeff Linear Phase                                     | DAC Quick Set                                                                                                                                                                                                                                                                                              |  |  |

| MCU code version<br>V1.4                                                           | IIR Coeff  3Hz@500SPS Filter Clock 16.384 MHz                                           | Mode Select Mode Clock Rate 0                                                                                                                                                                                                                                                                              |  |  |

| Reset Target<br>Flash MCU                                                          | MCLK Rate 2.048 MHz                                                                     | Gain Select Gain<br>Select Gain<br>Sync Disabled<br>ENABLE TBS<br>Loopback Disabled                                                                                                                                                                                                                        |  |  |

| GA                                                                                 | IN / OFFSET                                                                             | DATA CAPTURE                                                                                                                                                                                                                                                                                               |  |  |

| Gain<br>CH 1 0 0<br>CH 2 0 0<br>CH 3 0 0<br>CH 3 0 0<br>CH 4 0 0                   | Offset 0 USEGR Disabled 0 USEOR Disabled 0 USEOR Disabled 0 ORCAL Disabled 0 EXP[4:0] 0 | 4096       Total Samples       Capture Duta         Hodie (7-term)       Window       CAPTURE         0       Bandwidth Limit (Hz)       Remaining Captures         5B3A71       Full Scale Code       0         5.00       Full Scale Voltage       Skip Samples         1       Total Captures       100 |  |  |

| M1                                                                                 | МЗМ4                                                                                    |                                                                                                                                                                                                                                                                                                            |  |  |

- Once the Setup panel is set, select Configure on the Digital Filter sub-panel.

- After digital filter configuration is complete, click Capture on the Data Capture sub-panel.

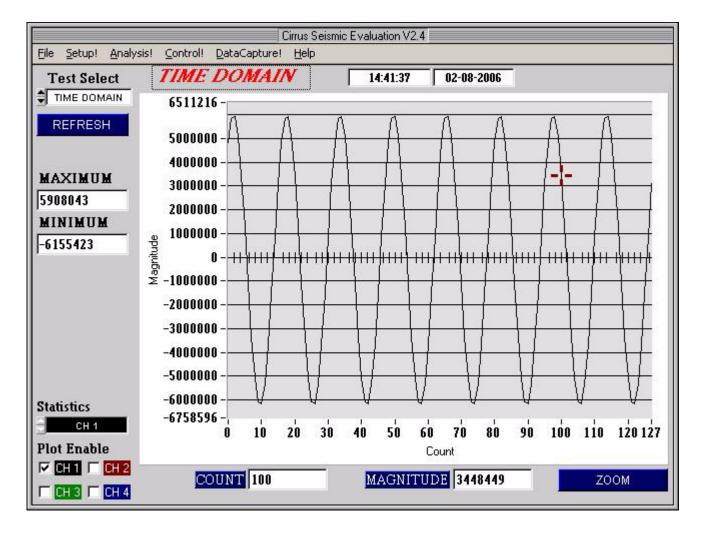

- Once the data record is collected, the Analysis panel is automatically displayed.

- Select Noise FFT from the Test Select control to display the calculated noise statistics.

- Verify the noise performance (S/N) is 124 dB or better.

#### 1.4.2 Distortion Test

• Set the controls on the **Setup** panel to match the picture:

| Cirrus Seismic Evaluation V2.4                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| Eile         Setup!         Analysis!         Control!         DataCapture!         Help           USB PORT         DIGITAL FILTER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ANALOG FRONT END                                                          |                                                                   |  |

|                                                                                                                                    | inel Set 🗘 4 Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Amp Mux Cain Cain Cain Cain Cain Cain Cain                                | x1<br>Disable All                                                 |  |

| CRD5376 RevC Outp                                                                                                                  | ut Rate \$ 500 SPS<br>ut Filter \$ FIR2 Output<br>R Coeff \$ Linear Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST BIT STREAM                                                           |                                                                   |  |

| MCU code version III                                                                                                               | R Coeff  The array of the second seco | DAC Quick Set<br>Mode Sine<br>Freq 31.25 Hz                               | 4                                                                 |  |

| Reset Target MCL                                                                                                                   | K Rate 2.048 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Gain Factor<br>Gain Gain Factor<br>Sync<br>DISABLE TBS<br>Loopback        | 4B8F2     Disabled     Disabled                                   |  |

| GAIN / O                                                                                                                           | FFSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DATA CAPTURE                                                              |                                                                   |  |

| Gain Offse<br>CH 1 0 0<br>CH 2 0 0<br>CH 3 0 0<br>CH 3 0 0<br>CH 4 0 0<br>READ WRITE                                               | 0     USEGR ♥ Disabled       0     USEOR ♥ Disabled       0     ORCAL ♥ Disabled       0     EXP[4:0] ♥ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Hodie (7-term) Window  Hodie (7-term) Window  SB3A71 Full Scale Code  Ren | CAPTURE<br>CAPTURE<br>naining Captures<br>0<br>kip Samples<br>100 |  |

| М1                                                                                                                                 | м2 М3 М4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M6M7M8                                                                    | J                                                                 |  |

- Once the Setup panel is set, select Configure on the Digital Filter sub-panel.

- After digital filter configuration is complete, click Capture on the Data Capture sub-panel.

- Once the data record is collected, the Analysis panel is automatically displayed.

- Select Signal FFT from the Test Select control to display the calculated noise statistics.

- Verify the distortion performance (S/D) is 112 dB or better.

#### 2. HARDWARE DESCRIPTION

#### 2.1 Block Diagram

Figure 1. CRD5376 Block Diagram

Major blocks of the CRD5376 reference design include:

- CS3301 Geophone Amplifier (2x)

- CS3302 Hydrophone Amplifier (2x)

- CS5372 Dual  $\Delta\Sigma$  Modulators (2x)

- CS5376A Digital Filter

- CS4373A  $\Delta\Sigma$  Test DAC

- Analog Switch Multiplexer

- Precision Voltage Reference

- Microcontroller with USB

- Phase Locked Loop

- RS-485 Transceivers

- Voltage Regulators

#### 2.2 Analog Hardware

#### 2.2.1 Analog Inputs

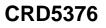

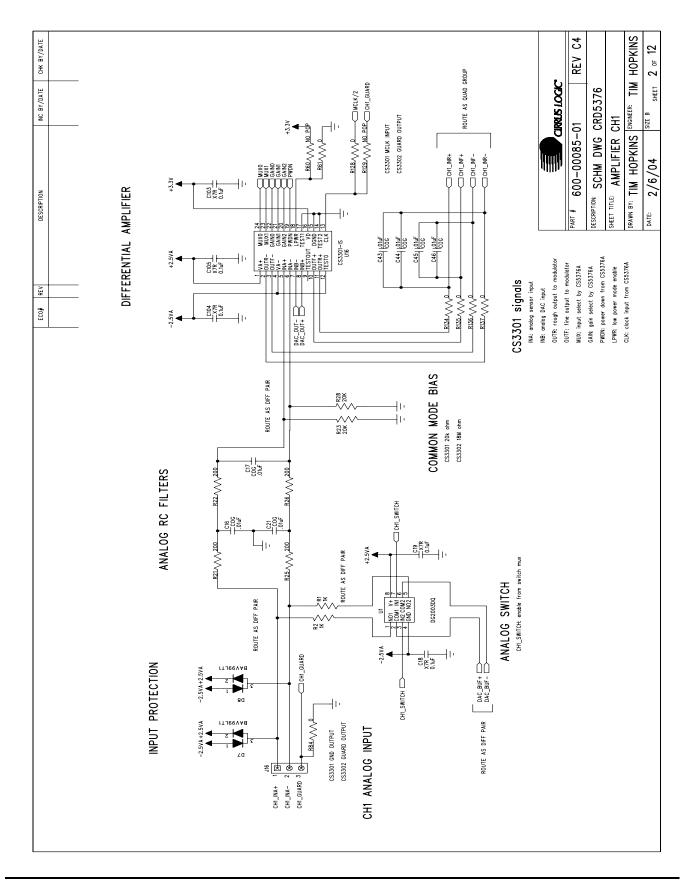

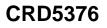

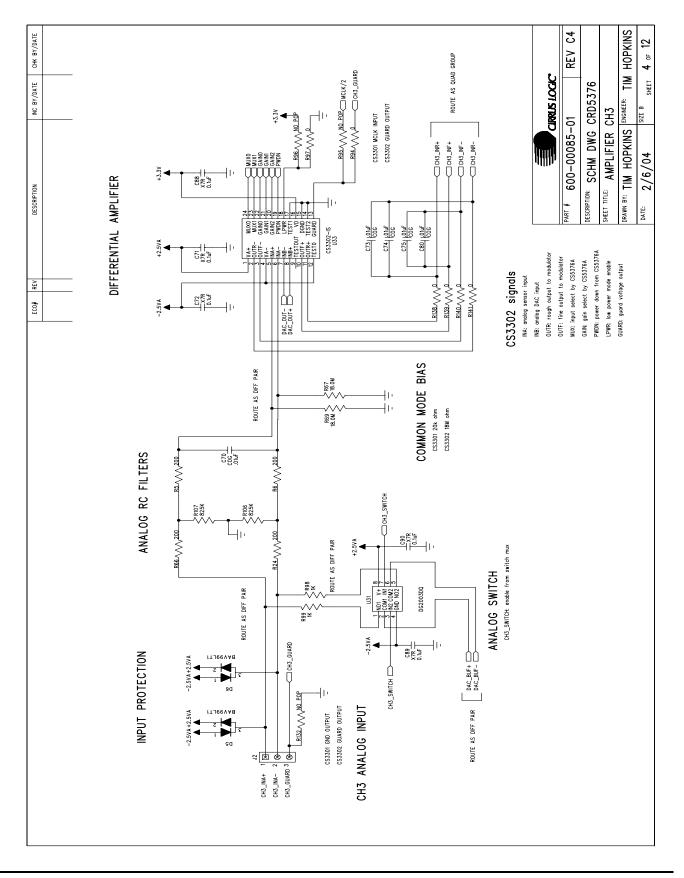

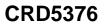

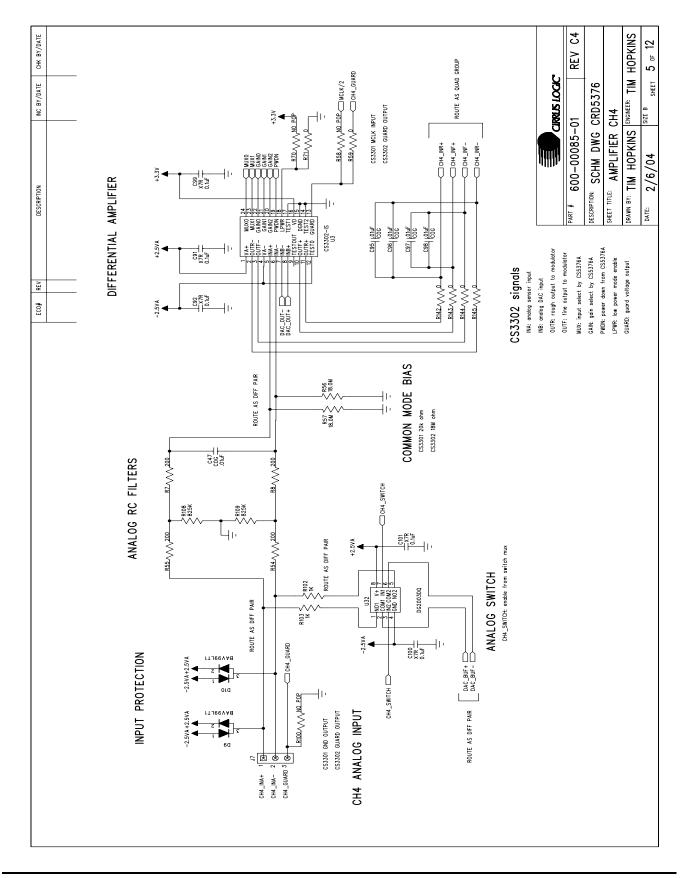

#### 2.2.1.1 External Inputs - INA

External signals into CRD5376 are from two major classes of sensors, moving coil geophones and piezoelectric hydrophones. Geophones are low-impedance sensors optimized to measure vibrations in land applications. Hydrophones are high-impedance sensors optimized to measure pressure in marine applications. Other sensors for earthquake monitoring and military applications are considered as geophones for this datasheet.

External signals connect to CRD5376 through 3-pin headers on the left side of the PCB. For each channel (CH1, CH2, CH3, CH4), these headers make connections to the differential INA amplifier inputs and to either a GND or GUARD signal for connection to the sensor cable shields, if present.

| Signal Input | Pin Header |

|--------------|------------|

| CH1 INA      | J16        |

| CH2 INA      | J1         |

| CH3 INA      | J2         |

| CH4 INA      | J7         |

#### Table 5. Pin Header Input Connections

# 2.2.1.2 GUARD Output, GND Connection

The CS3302 hydrophone amplifier provides a GUARD signal output designed to actively drive the cable shield of a high impedance sensor with the common mode voltage of the sensor differential signal. This GUARD output on the cable shield minimizes leakage by minimizing the voltage differential between the sensor signal and the cable shield.

By default, the GUARD signal is output to pin 3 of the input signal headers on the left side of the PCB for channels 3 and 4, which use the CS3302 amplifier. There is no GUARD signal output for channels 1 and 2 since they use the CS3301 amplifier, so the GUARD pins for these channels are connected to GND through 0  $\Omega$  jumpers.

# 2.2.1.3 Internal Inputs - DAC\_OUT, DAC\_BUF

The CS4373A test DAC has two high performance differential test outputs, a precision output (DAC\_OUT) and a buffered output (DAC\_BUF). The DAC\_OUT signal is wired directly to the INB inputs of the CS3301/02 amplifiers for testing the performance of the electronics channel. The DAC\_BUF signal is wired to the INA inputs of the amplifiers through differential analog switches and is used to test the performance of the measurement channel with a sensor attached.

#### 2.2.1.4 Input Protection

Sensor inputs must have circuitry to protect the analog electronics from voltage spikes. Geophone coils are susceptible to magnetic fields (especially from lightning) and hydrophones can produce large voltage spikes if located near an air gun source.

Discrete switching diodes quickly clamp the analog inputs to the power supply rails when the input voltage spikes. These diodes are reverse biased in normal operation and have low reverse bias leakage and capacitance characteristics to maintain high linearity on the analog inputs.

| Specification                                         | Value                |

|-------------------------------------------------------|----------------------|

| Dual Series Switching Diode - ON Semiconductor        | BAV99LT1             |

| Surface Mount Package Type                            | SOT-23               |

| Non-Repetitive Peak Forward Current (1 µs, 1 ms, 1 s) | 2.0 A, 1.0 A, 500 mA |

| Reverse Bias Leakage (25 C to 85 C)                   | 0.004 μΑ - 0.4 μΑ    |

| Reverse Bias Capacitance (0 V to 5 V)                 | 1.5 pF - 0.54 pF     |

Once a voltage spike is shunted to the power supply rail, a discharge path to ground must be present or the power supply will itself spike. Transient voltage suppressors clamp the  $\pm 2.5$  V analog supply rails in the event of a voltage spike.

| Specification                        | Value        |

|--------------------------------------|--------------|

| Dual Surface Mount TVS - Diodes Inc. | MMBZ5V6AL-7  |

| Surface Mount Package Type           | SOT-23       |

| Working Voltage, Leakage Current     | 3.0 V, 5 μA  |

| Breakdown Voltage, Threshold Current | 5.6 V, 20 mA |

| Clamp Voltage, Peak Current          | 8.0 V, 3.0 A |

# 2.2.1.5 Input RC Filters

Following the diode clamps is an RC filter network that bandwidth limits the sensor inputs into the amplifiers to 'chop-the-tops-off' residual voltage spikes not clamped by the discrete diodes. In addition, all Cirrus Logic component ICs have built in ESD protection diodes guaranteed to 2000 V HBM / 200 V MM (JEDEC standard). The small physical size of these ESD diodes restricts their current capacity to 10 mA.

For land applications using the CS3301 amplifier (CRD5376 channels 1 and 2), the INA input has a common mode and differential RC filter. The common mode filter sets a low-pass corner to shunt very high frequency components to ground with minimal noise contribution. The differential filter sets a low-pass corner high enough not to affect the magnitude response of the measurement bandwidth.

For marine applications that use the CS3302 amplifier (CRD5376 channels 3 and 4), the inherent capacitance of the piezoelectric sensor is combined with large resistors connected to the input signal common mode to create an analog high-pass RC filter to eliminate the low-frequency components of ocean noise. Following the high-pass common mode filter is a differential low-pass filter to reject high frequency signals into the amplifier. The cutoff frequency for the low-pass filter is high enough not to affect the magnitude response of the measurement bandwidth.

| Land Common Mode Filter Specification    | Value                                                    |

|------------------------------------------|----------------------------------------------------------|

| Common Mode Capacitance                  | 10 nF <u>+</u> 10%                                       |

| Common Mode Resistance                   | 200 Ω                                                    |

| Common Mode -3 dB Corner @ 6 dB/octave   | 80 kHz <u>+</u> 10%                                      |

| Land Differential Filter Specification   | Value                                                    |

| Differential Capacitance                 | 10 nF <u>+</u> 10%                                       |

| Differential Resistance                  | $200 \ \Omega + 200 \ \Omega = 400 \ \Omega$             |

| Differential -3 dB Corner @ 6 dB/octave  | 40 kHz <u>+</u> 10%                                      |

|                                          |                                                          |

| Marine Common Mode Filter Specification  | Value                                                    |

| Hydrophone Group Capacitance             | 128 nF <u>+</u> 10%                                      |

| Common Mode Resistance                   | 825 k $\Omega \parallel$ 825 k $\Omega$ = 412 k $\Omega$ |

| -3 dB Corner @ 6 dB/octave               | 3 Hz <u>+</u> 10%                                        |

| Marine Differential Filter Specification | Value                                                    |

| Differential Capacitance                 | 10 nF <u>+</u> 10%                                       |

| Differential Resistance                  | $200 \ \Omega + 200 \ \Omega = 400 \ \Omega$             |

| -3 dB Corner @ 6 dB/octave               | 40 kHz <u>+</u> 10%                                      |

# 2.2.1.6 Common Mode Bias

Differential analog signals into the CS3301/02 amplifiers are required to be biased to the center of the power supply voltage range, which for bipolar supplies is near ground potential. Resistors to create the common mode bias are selected based on the sensor impedance and may need to be modified from the CRD5376 defaults depending on the sensor to be used. Refer to the recommended operating bias conditions for the selected sensor, which are available from the sensor manufacturer.

| Specification                     | Value                                                                  |

|-----------------------------------|------------------------------------------------------------------------|

| Geophone Sensor Bias Resistance   | $20 \text{ k}\Omega \parallel 20 \text{ k}\Omega = 10 \text{ k}\Omega$ |

| Hydrophone Sensor Bias Resistance | $18 \text{ M}\Omega \parallel 18 \text{ M}\Omega = 9 \text{ M}\Omega$  |

# 2.2.1.7 Analog Test Switches

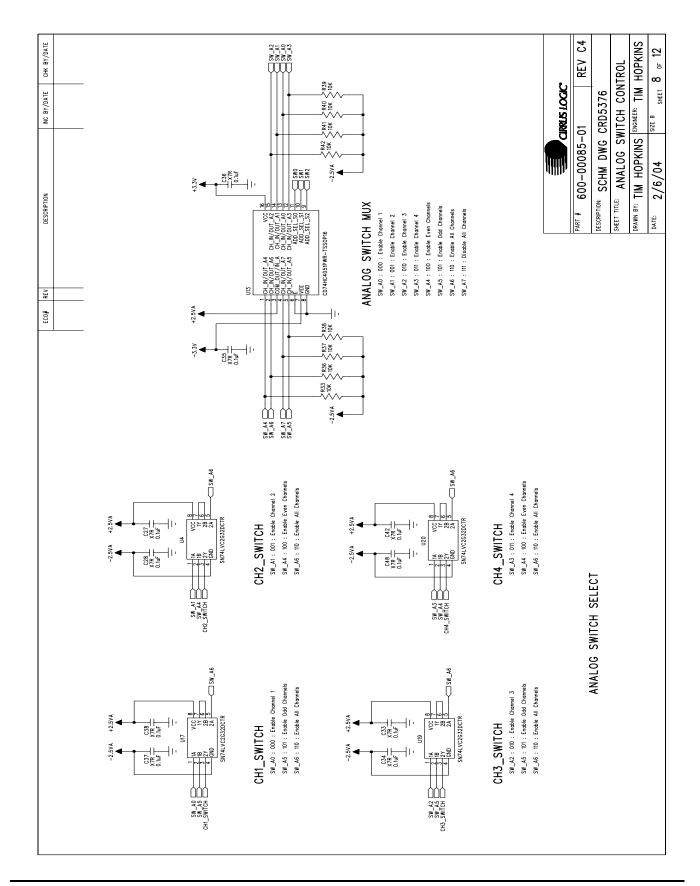

Analog switches on CRD5376 connect the DAC\_BUF test signal to the sensor. A two stage approach permits flexibility in switch operation while maximizing performance. First, control signals from the digital filter act as inputs to a 3-to-8 demultiplexer, selecting one of the eight outputs from the decoded GPIO input. Next, the demultiplexer creates level shifted control signals for the analog switches using the selected output and a pull-up / pull-down circuit on the analog power supplies. These level shifted signals control the analog switches to connect the test DAC buffered output (DAC\_BUF) to the amplifier sensor input (INA).

Using this level-shifting 3-to-8 demultiplexer scheme allows flexible control of the analog switches without directly coupling them to the digital power supplies. With eight possible decoded outputs from three GPIO pins, multiple combinations of on / off analog switch arrangements are possible.

| SW[20] | DAC_BUF to INA Connection |  |

|--------|---------------------------|--|

| 000    | Channel 1 Only            |  |

| 001    | Channel 2 Only            |  |

| 010    | Channel 3 Only            |  |

| 011    | Channel 4 Only            |  |

| 100    | Even Channels Connected   |  |

| 101    | Odd Channels Connected    |  |

| 110    | All Channels Connected    |  |

| 111    | All Channels Disconnected |  |

#### **Table 6. Analog Switch Settings**

Independent dual analog switches for each differential channel helps to eliminate crosstalk between them.

| Specification                                    | Value                  |

|--------------------------------------------------|------------------------|

| Analog Switch Mux - Texas Instruments            | CD74HC4051PWR          |

| Surface Mount Package Type                       | TSSOP-16               |

| Power Supply Voltage, Current                    | <u>+</u> 3.3V, 160 μA  |

| Individual Switch Settings - Ch1, Ch2, Ch3, Ch4  | 000, 001, 010, 011     |

| Even, Odd Switch Settings - Ch2+Ch4, Ch1+Ch3     | 100, 101               |

| All On Switch Setting - Ch1+Ch2+Ch3+Ch4          | 110                    |

| All Off Switch Setting                           | 111                    |

|                                                  |                        |

| Specification                                    | Value                  |

| Analog Switch Selection - TI LittleLogic Dual-OR | SN74LVC2G32DCTR        |

| Surface Mount Package Type                       | SSOP-8                 |

| Supply Voltage, Current                          | <u>+</u> 2.5 V, 10 μA  |

|                                                  |                        |

| Specification                                    | Value                  |

| Dual SPST Analog Switches - Vishay               | DG2003DS               |

| Surface Mount Package Type                       | SOT23-8                |

| On Resistance Match, + 5 V Supply                | 1.6 Ω                  |

| On Resistance Flatness, + 5 V Supply             | 0.2 Ω                  |

| Off Leakage Current                              | <u>+</u> 1 nA          |

| Off Isolation @ 1 MHz                            | -61 dB                 |

| Channel Crosstalk @ 1 MHz                        | -67 dB                 |

| Supply Voltage, Power Consumption                | <u>+</u> 2.5 V, 5.5 μW |

# 2.2.2 Differential Amplifiers

The CS3301/02 amplifiers act as a low-noise gain stage for internal or external differential analog signals.

| Analog Signals         | Description                            |  |

|------------------------|----------------------------------------|--|

| INA                    | Sensor analog input                    |  |

| INB                    | Test DAC analog input                  |  |

| OUTR, OUTF             | Analog rough / fine outputs            |  |

| GUARD                  | CS3302 guard output (jumper selection) |  |

|                        |                                        |  |

| <b>Digital Signals</b> | Description                            |  |

| MUX[01]                | Input mux selection                    |  |

| GAIN[02]               | Gain range selection                   |  |

| PWDN                   | Power down mode enable                 |  |

| CLK                    | CS3301 clock input (jumper selection)  |  |

# 2.2.2.1 MCLK/2 Input vs. GUARD Output

By default, channels 1 and 2 of CRD5376 use the CS3301 geophone amplifier while channels 3 and 4 use the CS3302 hydrophone amplifier. The CS3301 amplifier is chopper stabilized and connects pin 13 to a clock source (MCLK/2) to run the chopper circuitry synchronous to the modulator analog sampling clock. The CS3302 device is not chopper stabilized (with 1/f noise typically buried below the low-frequency ocean noise) to achieve very high input impedance. To minimize leakage from high impedance sensors connected to the CS3302 amplifier, pin 13 produces a GUARD signal output to actively drive a sensor cable shield with the common mode voltage of the sensor signal.

Comparing the CS3301 and CS3302 amplifiers, the functionality of pin 13 (CLK input vs. GUARD output) is the only external difference. CRD5376 can be converted to use any combination of CS3301 and CS3302 amplifiers by replacing the amplifier device and properly installing the pin 13 jumpers. Only one set of pin 13 jumpers should be installed per channel (either CS3301 or CS3302), and the others removed.

| Ar  | nplifier | CS3301     | CS3302 |

|-----|----------|------------|--------|

| CH1 | U16      | R128 + R84 | R129   |

| CH2 | U2       | R86 + R92  | R87    |

| CH3 | U33      | R95 + R132 | R94    |

| CH4 | U3       | R58 + R100 | R59    |

| Table 7. | Amplifier | Pin 13 | Jumper | Settings |

|----------|-----------|--------|--------|----------|

|----------|-----------|--------|--------|----------|

Common amplifier configurations for CRD5376 include 3x or 4x CS3301 amplifiers for land applications, 4x CS3302 amplifiers for marine streamer applications, and 3x CS3301 amplifiers plus 1x CS3302 amplifier for seabed reservoir monitoring applications. Replacement amplifiers can be requested as samples from the local Cirrus Logic sales representative.

# 2.2.2.2 Rough-Fine Outputs - OUTR, OUTF

The analog outputs of the CS3301/02 differential amplifiers are split into rough charge and fine charge signals for input to the CS5372  $\Delta\Sigma$  modulators. The amplifier outputs include integrated series resistors to create the anti-alias RC filters required to limit the modulator input signal bandwidth.

Analog signal traces out of the CS3301/02 amplifiers and into the CS5372 modulators are 4-wire INR+, INF+, INF-, INR- quad groups, and are routed with INF+ and INF- as a traditional differential pair and INR+ and INR- as guard traces outside the respective INF+ and INF- traces.

# 2.2.2.3 Anti-alias RC Filters

The CS5372  $\Delta\Sigma$  modulators are 4th order and high frequency input signals can cause instability. Simple single-pole anti-alias RC filters are required between the CS3301/02 amplifier outputs and the CS5372 modulator inputs to bandwidth limit analog signals into the modulator.

The CS3301/02 amplifier outputs include internal series resistors, so a differential anti-alias RC filter is created by connecting 20 nF of high linearity differential capacitance (2x 10 nF C0G) between each half of the rough and fine signals. External 0  $\Omega$  resistors are included in series with the amplifier internal anti-alias resistors to support testing of other anti-alias RC filter configurations.

#### 2.2.3 Delta-Sigma Modulators

Each CS5372 dual modulator performs the A/D function for differential analog signals from two CS3301/02 amplifiers. The digital outputs are oversampled  $\Delta\Sigma$  bit streams.

| Analog Signals         | Description                                       |  |

|------------------------|---------------------------------------------------|--|

| INR1, INF1             | Channel 1 analog rough / fine inputs              |  |

| INR2, INF2             | Channel 2 analog rough / fine inputs              |  |

| VREF                   | Voltage reference analog inputs                   |  |

|                        |                                                   |  |

| <b>Digital Signals</b> | Description                                       |  |

| MDATA[12]              | Modulator delta-sigma data outputs                |  |

| MFLAG[12]              | Modulator over-range flag outputs                 |  |

| MCLK                   | Modulator clock input                             |  |

| MSYNC                  | Modulator synchronization input                   |  |

| PWDN[12]               | Power down mode enable                            |  |

| OFST                   | Internal offset enable (+VD when using CS3301/02) |  |

# 2.2.3.1 Rough-Fine Inputs - INR, INF

The modulator analog inputs are separated into rough and fine signals, each of which has an anti-alias RC filter to limit the signal bandwidth into the modulator inputs.

# 2.2.3.2 Offset Enable - OFST

The CS5372  $\Delta\Sigma$  modulator requires differential offset to be enabled to eliminate idle tones for a terminated input. The use of internal offset to eliminate idle tones is described in the CS5372 data sheet. By default, OFST is enabled for the CS5372 modulators on CRD5376.

# 2.2.4 Delta-Sigma Test DAC

The CS4373A DAC creates differential analog signals for system tests. Multiple test modes are available and their use is described in the CS4373A data sheet.

| Analog Signals         | Description                                         |  |

|------------------------|-----------------------------------------------------|--|

| OUT                    | Precision differential analog output                |  |

| BUF                    | Buffered differential analog output                 |  |

| CAP                    | Capacitor connection for internal anti-alias filter |  |

| VREF                   | Voltage reference analog inputs                     |  |

|                        |                                                     |  |

| <b>Digital Signals</b> | Description                                         |  |

| TDATA                  | Delta-sigma test data input                         |  |

| MCLK                   | Clock input                                         |  |

| SYNC                   | Q 1 · · · ·                                         |  |

| SINC                   | Synchronization input                               |  |

| MODE[02]               | Test mode selection                                 |  |

# 2.2.4.1 Precision Output - DAC\_OUT

The CS4373A test DAC has a precision output (DAC\_OUT) that is routed to the amplifier INB inputs of all channels. The input impedance of the CS3301/02 INB amplifier inputs are high enough that the precision output can be directly connected to the INB inputs of all channels simultaneously.

# 2.2.4.2 Buffered Output - DAC\_BUF

The CS4373A test DAC has a buffered output (DAC\_BUF) that is routed through differential analog switches to the amplifier INA inputs for each channel. This output is less sensitive to loading than the precision outputs, and can drive a sensor attached to the amplifier INA inputs provided the sensor meets the impedance requirements specified in the CS4373A data sheet.

#### 2.2.5 Voltage Reference

A voltage reference on CRD5376 creates a precision voltage from the regulated analog supplies for the modulator and test DAC VREF inputs. Because the voltage reference output is generated relative to the negative analog power supply, VREF+ is near GND potential for bipolar power supplies.

| Specification                       | Value                |

|-------------------------------------|----------------------|

| Precision Reference - Linear Tech   | LT1019AIS8-2.5       |

| Surface Mount Package Type          | SO-8                 |

| Output Voltage Tolerance            | +/- 0.05%            |

| Temperature Drift                   | 10 ppm / degC        |

| Quiescent Current                   | 0.65 mA              |

| Output Voltage Noise, 10 Hz - 1 kHz | 4 ppm <sub>RMS</sub> |

| Ripple Rejection, 10 Hz - 200 Hz    | > 100 dB             |

# 2.2.5.1 VREF\_MOD12, VREF\_MOD34, VREF\_DAC

The voltage reference output is provided to the CS5372  $\Delta\Sigma$  modulators and the CS4373A test DAC through separate low pass RC filters. By separately filtering the voltage reference for each device, signal dependent sampling of VREF by one device is isolated from other devices. Each voltage reference signal is routed as a separate differential pair from the large RC filter capacitor to control the sensitive VREF source-return currents and keep them out of the ground plane. In addition to the RC filter function, the 100 uF filter capacitor provides a large charge-well to help settle voltage reference sampling transients.

#### 2.3 Digital Hardware

#### 2.3.1 Digital Filter

The CS5376A quad digital filter performs filtering and decimation of four delta-sigma bit streams from the CS5372 modulators. It also creates a delta-sigma bit stream output to create analog test signals in the CS4373A test DAC.

The CS5376A requires several control signal inputs from the external system.

| Control Signals | Description                                         |

|-----------------|-----------------------------------------------------|

| RESETz          | Reset input, active low                             |

| BOOT            | Microcontroller / EEPROM boot mode select           |

| TIMEB           | Time Break input, rising edge triggered             |

| CLK             | Master clock input, 32.768 MHz                      |

| SYNC            | Master synchronization input, rising edge triggered |

Configuration is completed through the SPI 1 port.

| SPI1 Signals | Description                                   |

|--------------|-----------------------------------------------|

| SSIz         | Serial chip select input, active low          |

| SCK1         | Serial clock input                            |

| MISO         | Master in / slave out serial data             |

| MOSI         | Master out / slave in serial data             |

| SINTz        | Serial acknowledge output, active low         |

| SSOz         | Serial chip select output (unused on CRD5376) |

Data is collected through the SD port.

| SD Port Signals | Description                                    |

|-----------------|------------------------------------------------|

| SDTKI           | Token input to initiate an SD port transaction |

| SDRDYz          | Data ready acknowledge, active low             |

| SDCLK           | Serial clock input                             |

| SDDAT           | Serial data output                             |

| SDTKO           | Token output (unused on CRD5376)               |

Modulator  $\Delta\Sigma$  data is input through the modulator interface.

| <b>Modulator Signals</b> | Description                        |

|--------------------------|------------------------------------|

| MCLK                     | Modulator clock output             |

| MCLK/2                   | Modulator clock output, half-speed |

| MSYNC                    | Modulator synchronization output   |

| MDATA[14]                | Modulator delta-sigma data inputs  |

| MFLAG[14]                | Modulator over-range flag inputs   |

Test DAC  $\Delta\Sigma$  data is generated by the test bit stream generator.

| <b>Test Bit Stream Signals</b> | Description                               |

|--------------------------------|-------------------------------------------|

| TBSDATA                        | Test DAC delta-sigma data output          |

| TBSCLK                         | Test DAC clock output (unused on CRD5376) |

Amplifier, modulator, test DAC and analog switch digital pins are controlled by the GPIO port.

| <b>GPIO Signals</b> | Description                           |

|---------------------|---------------------------------------|

| GPIO[01]:MUX[01]    | Amplifier input mux selection         |

| GPIO[24]:GAIN[02]   | Amplifier gain / test DAC attenuation |

| GPIO[57]:MODE[02]   | Test DAC mode selection               |

| GPIO[8]:PWDN        | Amplifier / modulator power down      |

| GPIO[911]:SW[02]    | Analog switch control                 |

The secondary serial port (SPI 2) and boundary scan JTAG port are unused on CRD5376.

| SPI2 Signals | Description                             |

|--------------|-----------------------------------------|

| SCK2         | Serial clock output (unused on CRD5376) |

| SO           | Serial data output (unused on CRD5376)  |

| SI[14]       | Serial data inputs (unused on CRD5376)  |

| JTAG Signals | Description                               |

|--------------|-------------------------------------------|

| TRSTz        | JTAG reset (unused on CRD5376)            |

| TMS          | JTAG test mode select (unused on CRD5376) |

| TCK          | JTAG test clock input (unused on CRD5376) |

| TDI          | JTAG test data input (unused on CRD5376)  |

| TDO          | JTAG test data output (unused on CRD5376) |

#### 2.3.1.1 MCLK vs. MCLK/2 Usage

The CS5376A digital filter creates the analog sampling clock used by the CS5372  $\Delta\Sigma$  modulators and CS4373A test DAC. MCLK has strict jitter requirements to guarantee the accuracy of analog-to-digital and digital-to-analog conversion, and so is carefully routed between the digital filter and modulators / test DAC.

The CS3301 amplifier also requires an analog sampling clock to run the internal chopper stabilization circuitry, but without the strict jitter or speed requirement and so can run equally well from the full-speed MCLK or half-speed MCLK/2. Although MCLK could be used as the amplifier input clock, using MCLK/2 isolates the sensitive modulator / test DAC analog sampling clock from the amplifier clock.

# 2.3.1.2 Configuration - SPI 1 Port

Configuration of the CS5376A digital filter is through the SPI 1 port by the on-board 8051 microcontroller which receives commands from the PC evaluation software via the USB interface. Evaluation software commands can write/read digital filter registers, specify digital filter coefficients and test bit stream data, and start/stop digital filter operation.

How the digital filter receives configuration information, either from a microcontroller or configuration EE-PROM, is selected by the BOOT signal. The BOOT signal is tied low on CRD5376 for microcontroller configuration.

# 2.3.1.3 Digital Control Signals

The reset, synchronization and timebreak signals to the CS5376A digital filter are generated by the onboard microcontroller and applied to the CS5376A digital filter RESET, SYNC, and TIMEB inputs.

Data collection transactions are initiated by a rising edge on the SDTKI input, as described in the CS5376A data sheet. Two options for providing the required SDTKI rising edge are available on CRD5376, as an input from the microcontroller to initiate data transactions on command or from the MCLK/2 clock to initiate data transactions automatically as soon as they are available from the digital filter.

| CS5376A | uController | MCLK/2 |

|---------|-------------|--------|

| SDTKI   | R74         | R83    |

#### Table 8. SDTKI Input Jumper Settings

The LPWR digital inputs to the analog components on CRD5376 reduce their power consumption at the expense of analog performance. Jumper options are provided to switch the analog components from normal operation at full specifications to low power operation with reduced specifications.

| (   | Component | NPWR | LPWR |

|-----|-----------|------|------|

| U16 | CS3301    | R61  | R60  |

| U2  | CS3301    | R89  | R88  |

| U33 | CS3302    | R97  | R96  |

| U3  | CS3302    | R71  | R70  |

| U24 | CS5372    | R76  | R75  |

| U29 | CS5372    | R77  | R78  |

| U45 | CS4373A   | R81  | R80  |

#### Table 9. Analog Components LPWR Jumper Settings

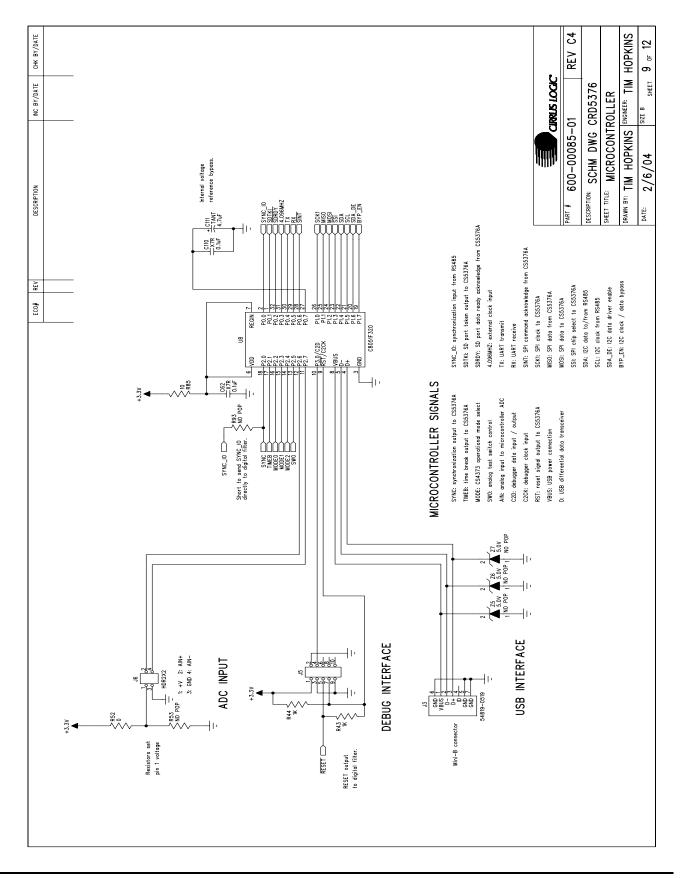

#### 2.3.2 *Microcontroller*

Included on CRD5376 is an 8051-type microcontroller with integrated hardware SPI and USB interfaces. This C8051F320 microcontroller is a product of Silicon Laboratories (http://www.silabs.com/). Key features of the C8051F320 microcontroller are:

8051 compatibility - uses industry standard 8051 software development tools

In-circuit debugger - software development on the target hardware

Internal memory - 16k flash ROM and 2k static RAM included on-chip

Multiple serial connections - SPI, USB, I2C, and UART

High performance - 25 MIPS maximum

Low power - 0.6 mA @ 1 MHz w/o USB, 9 mA @ 12 MHz with USB

Small size - 32 pin LQFP package, 9mm x 9mm

Industrial temperature - full performance (including USB) from -40 C to +85 C

Internal temperature sensor - with range violation interrupt capability

Internal timers - four general purpose plus one extended capability

Power on reset - can supply a reset signal to external devices

Analog ADC - 10 bit, 200 ksps SAR with internal voltage reference

Analog comparators - arbitrary high/low voltage compare with interrupt capability

The exact use of the microcontroller features is controlled by embedded firmware.

C8051F320 has dedicated pins for power and the USB connection, plus 25 general purpose I/O pins that connect to the various internal resources through a programmable crossbar. Hardware connections on CRD5376 limit how the blocks can operate, so the port mapping of microcontroller resources is detailed below.

| Pin # | Pin Name | Assignment | Description                                 |

|-------|----------|------------|---------------------------------------------|

| 1     | P0.1     | SDTKI      | Token to start CS5376A data transaction     |

| 2     | P0.0     | SYNC_IO    | SYNC signal from RS-485                     |

| 3     | GND      |            | Ground                                      |

| 4     | D+       |            | USB differential data transceiver           |

| 5     | D-       |            | USB differential data transceiver           |

| 6     | VDD      |            | +3.3 V power supply input                   |

| 7     | REGIN    |            | +5 V power supply input (unused on CRD5376) |

| 8     | VBUS     |            | USB voltage sense input                     |

| Pin # | Pin Name | Assignment | Description                       |

|-------|----------|------------|-----------------------------------|

| 9     | /RST     | RESETz     | Power on reset output, active low |

|       | C2CK     |            | Clock input for debug interface   |

| 10    | P3.0     | GPIO       | General purpose I/O               |

|       | C2D      |            | Data in/out for debug interface   |

| 11    | P2.7     | AIN-       | ADC input                         |

| 12    | P2.6     | AIN+       | ADC input                         |

| 13    | P2.5     | SW0        | Analog switch control             |

| 14    | P2.4     | MODE2      | CS4373A mode control              |

| 15    | P2.3     | MODE1      | CS4373A mode control              |

| 16    | P2.2     | MODE0      | CS4373A mode control              |

| Pin #                      | Pin Name                             | Assignment                  | Description                                                                                                                                      |

|----------------------------|--------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                         | P2.1                                 | TIMEB                       | Time Break signal to CS5376A                                                                                                                     |

| 18                         | P2.0                                 | SYNC                        | SYNC signal to CS5376A                                                                                                                           |

| 19                         | P1.7                                 | BYP_EN                      | I2C bypass switch control                                                                                                                        |

| 20                         | P1.6                                 | SDA_DE                      | I2C data driver enable                                                                                                                           |