# Micropower 1.2V/150mA CMOS LDO Regulator with Power Good

### **Features**

- 1-5ms Power Good (PG) control signal

- Regulated 1.2V output

- 150mA output current

- Low quiescent operating current (90µA typical)

- "Zero" disable mode current

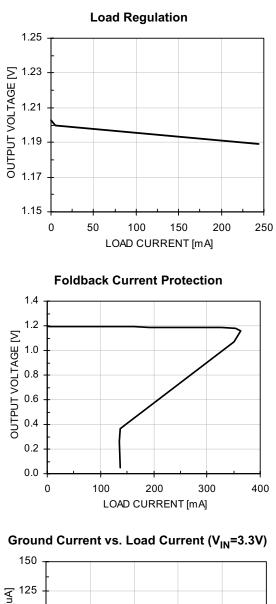

- Foldback current limiting protection

- Thermal shutdown protection

- Stable with low-ESR capacitors

- SOT23-5 package

- "MIC5258" pinout

- Lead-free version available

## Applications

- Pentium<sup>®</sup> 4 Motherboards

- Processor Power-up Sequencing

- Desktop, Notebook and Palmtop Computers

- PC Cards

- Peripheral Adapter Cards

Pentium<sup>®</sup> 4 Motherboard

### **Product Description**

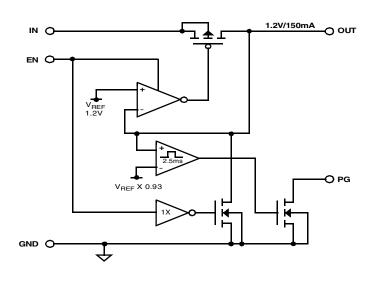

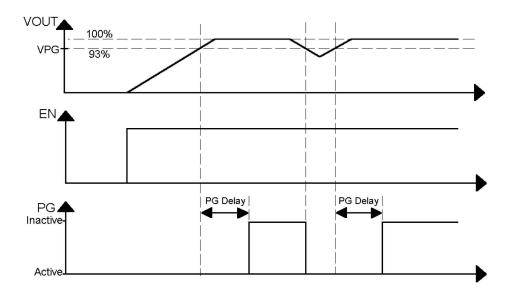

The CM3102 is a low quiescent current (90uA) regulator that delivers up to 150mA of load current at a fixed 1.2V output. In addition, the CM3102 features a Power Good output signal (PG) that goes open drain 1 to 5 ms after the output voltage has exceeded typically 93% of its nominal level.

A dedicated control input (EN, Active High) has been included for power-up sequencing flexibility. When this input is taken low, the regulator is disabled. In this state, the supply current will drop to near zero. An internal discharge MOSFET resistance ( $500\Omega$ ) will force the output to ground whenever the device has been shutdown.

The CM3102 is fully protected, offering both overload current limiting and high temperature thermal shut-down.

Available in a tiny SOT23 package, the device is ideal for space critical applications.

The CM3102 is available with optional lead-free finishing.

#### **Application Circuit** CM3102-12Sx 1.2V OUT VCC3 C O PG PG GND .1µF \* Input capacitor optional. Typical Application Circuit 47kΩ ۸۸۰ CM3102-12Sx OUT VIN C O Vour ΕN PG EN O O PG GND 1μF GND O \* Input capacitor optional. © 2004 California Micro Devices Corp. All rights reserved

### Simplified Electrical Schematic

1

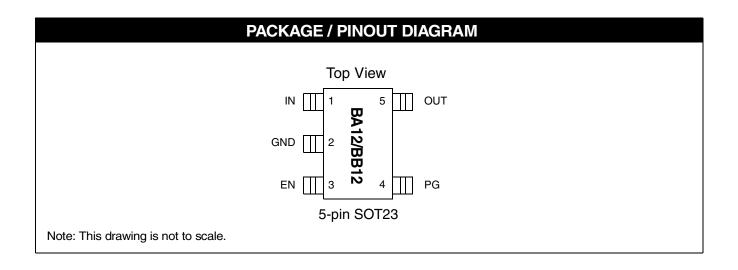

| PIN DESCRIPTIONS |      |                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN              | NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1                | IN   | Positive input voltage for the regulator. The internal loading on this input is typically 300 $\mu$ A when-<br>ever the regulator is enabled, and less than 1 $\mu$ A when the regulator is disabled. Although an input<br>filter capacitor is not required, it is recommended that a 1 $\mu$ F ceramic capacitor be used for addi-<br>tional filtering and stability if this pin is greater than 2 inches from the main input filter. |  |  |  |

| 2                | GND  | The negative reference for all voltages.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 3                | EN   | Enable/shutdown input. When EN is asserted high ( $V_{EN} \ge 1.6V$ ), the regulator is enabled. When EN                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                  |      | is asserted low (V <sub>EN</sub> $\leq$ 0.4V), the regulator's series pass transistor is forced into a high impedance                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                  |      | mode and an internal discharge resistance (500 $\Omega$ ) is applied to the output to quickly reduce the output voltage to 0 volts.                                                                                                                                                                                                                                                                                                    |  |  |  |

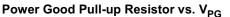

| 4                | PG   | Power Good output. This is an open drain output and functions as a supply voltage supervisor for the output voltage. It is asserted low when the output falls below 89% of its nominal value. This output becomes inactive when $V_{OUT}$ remains above 97% of its nominal value for 1 to 5ms.                                                                                                                                         |  |  |  |

| 5                | OUT  | The regulated voltage output. An output capacitor of $1\mu$ F is recommended to minimize any transient load disturbances under normal operating conditions. Additional output capacitance can be used to further improve transient load response.                                                                                                                                                                                      |  |  |  |

# **Ordering Information**

| PART NUMBERING INFORMATION |      |         |                     |              |                     |              |

|----------------------------|------|---------|---------------------|--------------|---------------------|--------------|

|                            |      |         | Standard Finish     |              | Lead-fre            | e Finish     |

|                            |      |         | Ordering Part       |              | Ordering Part       |              |

| Regulator                  | Pins | Package | Number <sup>1</sup> | Part Marking | Number <sup>1</sup> | Part Marking |

| CM3102-12                  | 5    | SOT23-5 | CM3102-12ST         | BA12         | CM3102-12SO         | BB12         |

Note 1: Parts are shipped in Tape & Reel form unless otherwise specified.

© 2004 California Micro Devices Corp. All rights reserved.

# Specifications

| ABSOLUTE MAXIMUM RATINGS                                                        |                                                                                                       |                |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| PARAMETER                                                                       | RATING                                                                                                | UNITS          |  |  |  |

| ESD Protection (HBM)                                                            | <u>+</u> 2000                                                                                         | V              |  |  |  |

| Pin Voltages<br>V <sub>IN</sub><br>V <sub>OUT</sub><br>V <sub>EN</sub>          | [GND - 0.6] to +6.0<br>[GND - 0.6] to [V <sub>IN</sub> +0.6]<br>[GND - 0.6] to [V <sub>IN</sub> +0.6] | V<br>V<br>V    |  |  |  |

| Storage Temperature Range<br>Operating Temperature Range<br>Ambient<br>Junction | -40 to +150<br>0 to +70<br>0 to +150                                                                  | ວ°<br>ວ°<br>ວ° |  |  |  |

| Power Dissipation (See note 1)                                                  | Internally Limited                                                                                    | W              |  |  |  |

Note 1: The power rating is based on a printed circuit board heat spreading capability equivalent to 2 square inches of copper connected to the GND pins. Typical multi-layer boards using power plane construction will provide this heat spreading ability without the need for additional dedicated copper area. Please consult with factory for thermal evaluation assistance.

| STANDARD OPERATING CONDITIONS       |                |       |  |  |  |  |

|-------------------------------------|----------------|-------|--|--|--|--|

| PARAMETER                           | VALUE          | UNITS |  |  |  |  |

| V <sub>IN</sub>                     | 2.7 to 5.5     | V     |  |  |  |  |

| Ambient Operating Temperature Range | 0 to +70       | °C    |  |  |  |  |

| Load Current                        | 0 to 150       | mA    |  |  |  |  |

| C <sub>OUT</sub>                    | 1 <u>+</u> 20% | μF    |  |  |  |  |

| ELECTRICAL OPERATING CHARACTERISTICS (SEE NOTE 1) |                               |                                                                                                                                        |     |           |            |          |

|---------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|------------|----------|

| SYM-<br>BOL                                       | PARAMETER                     | CONDITIONS                                                                                                                             | MIN | ТҮР       | МАХ        | UNITS    |

| V <sub>OUT</sub>                                  | Regulator Output Voltage      | 0.1mA < I <sub>LOAD</sub> < 150mA                                                                                                      | 1.1 | 1.2       | 1.3        | V        |

| V <sub>R LOAD</sub>                               | Load Regulation               | $10mA \le I_{LOAD} \le 150mA$                                                                                                          |     | 30        |            | mV       |

| V <sub>R LINE</sub>                               | Line Regulation               | $I_{LOAD} = 5mA; 2.7V \le V_{IN} \le to 3.6V$                                                                                          |     | 20        |            | mV       |

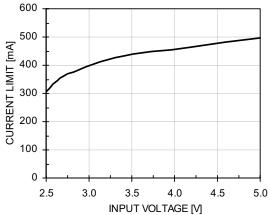

| I <sub>LIM</sub>                                  | Overload Current Limit        |                                                                                                                                        | 160 | 350       |            | mA       |

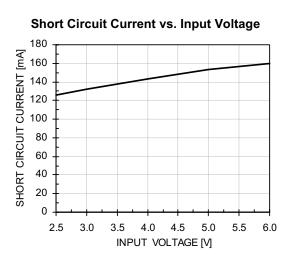

| I <sub>SC</sub>                                   | Short Circuit Current Limit   | V <sub>OUT</sub> < 0.5V                                                                                                                |     | 140       |            | mA       |

| R <sub>DISCH</sub>                                | Discharge Resistance          | EN tied to GND                                                                                                                         |     | 500       |            | Ω        |

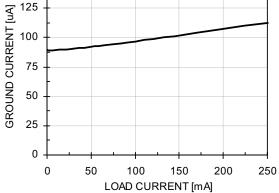

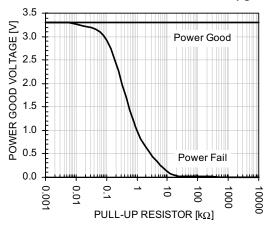

| I <sub>GND</sub>                                  | Ground Current                | Regulator Enabled (EN=V <sub>IN</sub> ); I <sub>LOAD</sub> = 0mA<br>Regulator Enabled (EN=V <sub>IN</sub> ); I <sub>LOAD</sub> = 150mA |     | 90<br>100 | 200<br>250 | μΑ<br>μΑ |

|                                                   |                               | Regulator Disabled (EN=GND); (Disable Mode)                                                                                            |     | 0.01      | 10         | μΑ       |

| V <sub>EN</sub>                                   | EN Input Logic High Threshold | Regulator Enabled                                                                                                                      | 1.6 |           |            | V        |

| V <sub>DIS</sub>                                  | EN Input Logic Low Threshold  | Regulator Disabled                                                                                                                     |     |           | 0.4        | V        |

| I <sub>EN</sub>                                   | Enable Input Current          |                                                                                                                                        |     | 0.01      |            | μA       |

| V <sub>PGL</sub>                                  | Power Good Low Threshold      | % of V <sub>OUT</sub> (PG ON)                                                                                                          | 89  |           |            | %        |

| V <sub>PGH</sub>                                  | Power Good High Threshold     | % of V <sub>OUT</sub> (PG OFF)                                                                                                         |     |           | 97         | %        |

| V <sub>OL</sub>                                   | Power Good Logic "0" Voltage  | $I_L=100\mu A$ ; Fault Condition                                                                                                       |     | 0.02      | 0.1        | V        |

| I <sub>PG</sub>                                   | Power Good Leakage Current    | Power Good Off; V <sub>PG</sub> =5.5V                                                                                                  |     | 0.01      |            | μA       |

| PG <sub>DELAY</sub>                               | Delay Time to Power Good      |                                                                                                                                        | 1   |           | 5          | mS       |

Note 1: Operating Characteristics are over Standard Operating Conditions unless otherwise specified.

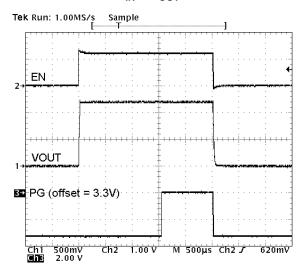

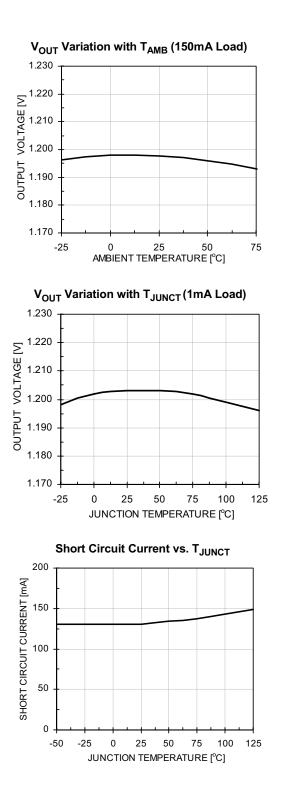

## **Timing Diagram**

© 2004 California Micro Devices Corp. All rights reserved.

### **Performance Information**

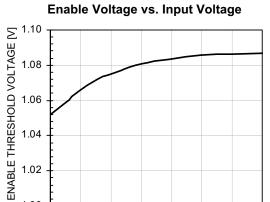

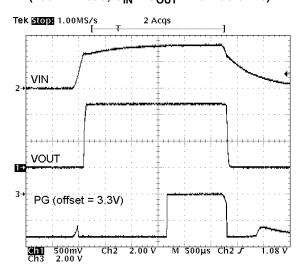

CM3102 Typical DC Characteristics (nominal conditions unless specified otherwise)

#### $\ensuremath{\textcircled{\sc 0}}$ 2004 California Micro Devices Corp. All rights reserved.

01/20/04 430 N. McCarthy Blvd., Milpitas, CA 95035-5112 🔺 Tel: 408.263.3214 🔺 Fax: 408.263.7846 🔺 www.calmicro.com

1.30 OUTPUT VOLTAGE [V] 1.25 1mA 1.20 150mA 1.15 1.10 2.5 2.0 3.0 3.5 4.0 4.5 5.0 5.5 6.0 INPUT VOLTAGE [V]

### Line Regulation (1% and 100% rated load)

Ground Current vs. Input Voltage (1mA Load)

5

### Performance Information (cont'd)

CM3102 Typical DC Characteristics (cont'd, nominal conditions unless specified otherwise)

Current Limit vs. Input Voltage (V<sub>OUT</sub>=1.15V)

PG<sub>DELAY</sub> vs. Input Voltage 2.0 1.5 PG<sub>DELAY</sub> [ms] 0.5 0.0 2.5 3.0 3.5 4.0 4.5 5.0 INPUT VOLTAGE [V]

© 2004 California Micro Devices Corp. All rights reserved.

1.02

1.00

2.5

3.0

3.5

4.0

4.5

INPUT VOLTAGE [V]

5.0

5.5

6.0

### Performance Information (cont'd)

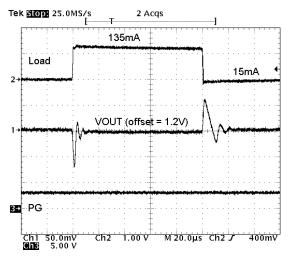

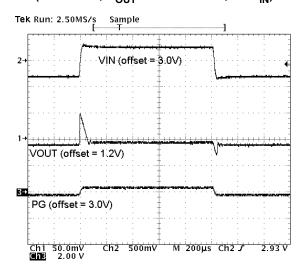

CM3102 Transient Characteristics (nominal conditions unless specified otherwise) (PG connected to  $V_{IN}$  with a  $47k\Omega$  resistor)

Load transient (10% to 90%) Step Response ( $V_{IN}$  = 3.3V,  $C_{IN}$  =  $C_{OUT}$  = 1uF Ceramic)

Enable Response (150mA Load, C<sub>IN</sub> = C<sub>OUT</sub> = 1uF Ceramic)

# Line Transient (0.6Vpp) Step Response (1mA Load, C<sub>OUT</sub> = 1uF Ceramic, no C<sub>IN</sub>)

Cold Start & Power Down (150mA Load, C<sub>IN</sub> = C<sub>OUT</sub> = 1uF Ceramic)

### Performance Information (cont'd)

### CM3102-12ST/SO Typical Thermal Characteristics

The overall junction to ambient thermal resistance  $(\theta_{JA})$  for device power dissipation (PD) consists primarily of two paths in series. The first path is the junction to the case  $(\theta_{JC})$  which is defined by the package style, and the second path is case to ambient  $(\theta_{CA})$  thermal resistance which is dependent on board layout. The final operating junction temperature for any set of conditions can be estimated by the following thermal equation:

$$T_{JUNC} = T_{AMB} + P_D (\theta_{JC}) + P_D (\theta_{CA})$$

$$= T_{AMB} + P_D (\theta_{JA})$$

The CM3102-12ST/SO uses a SOT23-5 package. When this package is mounted on a double sided printed circuit board with two square inches of copper allocated for "heat spreading", the resulting  $\theta_{JA}$  is 175°C/W.

Based on a maximum power dissipation of 315mW (2.1Vx150mA), with an ambient of 70°C the resulting junction temperature will be:

$$T_{JUNC} = T_{AMB} + P_D (\theta_{JA})$$

= 70°C + 315mW X (175°C/W)

= 70°C + 55°C = 125°C

Thermal characteristics were measured using a double sided board with two square inches of copper area connected to the GND pin for "heat spreading".

Measurements showing performance up to junction temperature of  $125^{\circ}$ C were performed under light load conditions (1mA). This allows the ambient temperature to be representative of the internal junction temperature.

Note: The use of multi-layer board construction with separate ground and power planes will further enhance the overall thermal performance. In the event of no copper area being dedicated for heat spreading, a multi-layer board construction, using only the minimum size pad layout, will provide the CM3102-12ST/SO with an overall  $\theta_{JA}$  of 175°C/W which allows up to 450mW to be safely dissipated for the maximum junction temperature.

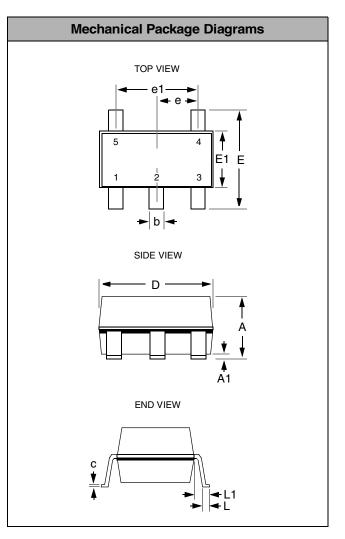

### **Mechanical Details**

### **SOT23-5 Mechanical Specifications**

Dimensions for CM3102-12ST/SO device packaged in 5-pin SOT23 package are presented below.

For complete information on the SOT23-5 package, see the California Micro Devices SOT23 Package Information document.

| PACKAGE DIMENSIONS     |                                |      |            |        |  |  |

|------------------------|--------------------------------|------|------------|--------|--|--|

| Package                | SOT23-5 (JEDEC name is MO-178) |      |            |        |  |  |

| Pins                   | 5                              |      |            |        |  |  |

| Dimensions             | Millimeters                    |      | Inches     |        |  |  |

| Dimensions             | Min                            | Max  | Min        | Мах    |  |  |

| А                      |                                | 1.45 |            | 0.0571 |  |  |

| A1                     | 0.00                           | 0.15 | 0.0000     | 0.0059 |  |  |

| b                      | 0.30                           | 0.50 | 0.0118     | 0.0197 |  |  |

| с                      | 0.08                           | 0.22 | 0.0031     | 0.0087 |  |  |

| D                      | 2.75                           | 3.05 | 0.1083     | 0.1201 |  |  |

| E                      | 2.60                           | 3.00 | 0.1024     | 0.1181 |  |  |

| E1                     | 1.45                           | 1.75 | 0.0571     | 0.0689 |  |  |

| е                      | 0.95                           | BSC  | 0.0374 BSC |        |  |  |

| e1                     | 1.90 BSC                       |      | 0.0748 BSC |        |  |  |

| L                      | 0.30                           | 0.60 | 0.0118     | 0.0236 |  |  |

| L1                     | 0.60                           | REF  | 0.0236 REF |        |  |  |

| # per tape<br>and reel | 3000 pieces                    |      |            |        |  |  |

Package Dimensions for SOT23-5.

© 2004 California Micro Devices Corp. All rights reserved.