# **CD1865**

# Intelligent Eight-Channel Communications Controller

## **Datasheet**

# **Product Features**

- Eight full-duplex asynchronous channels supporting data rates up to 115.2 kbps

- Note: To support this data rate, the specified system clock frequency is required.

- Register-based interrupt acknowledges eliminate need for separate interrupt acknowledge signals

- Automatic prioritizing scheme allows device to respond to an interrupt acknowledge with the highest internal interrupt pending (host-programmable)

- Sophisticated interrupt schemes

- —Vectored interrupts

- -Fair Share interrupts

- —Good Data™ interrupts for improved throughput

- Simultaneous interrupt requests for three classes of interrupts: Rx, Tx, and modem state changes

- Independent baud-rate generators for each channel/direction

- Software compatibility with the CD180 and CD1864 devices

- Generation and detection of special characters

- Automatic flow control

- —In-band (Xon, Xoff generation, and detection)

- —Out-of-band (DTR/DSR or RTS/CTS)

- On-chip FIFO 8 bytes each for Rx, Tx, and Status

- Line break detection and generation

- Multiple-chip daisy-chain cascading feature

- Odd, even, forced, or no parity

- modem/general-purpose I/O signals per channel

- System clock up to 66 MHz (x2), 33MHz (x1)

- CMOS technology in 100-pin MQFP

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The CD1865 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Ovo   | rview                                                            | 10 |

|-----|-------|------------------------------------------------------------------|----|

| 1.0 |       |                                                                  |    |

|     | 1.1   | Theory of Operation                                              |    |

| 2.0 | Con   | ventions                                                         |    |

|     | 2.1   | Abbreviations                                                    |    |

|     | 2.2   | Acronyms                                                         |    |

| 3.0 | Devi  | ice Selection Considerations                                     | 15 |

| 4.0 | Pin I | Information                                                      | 16 |

|     | 4.1   | Pin Diagram                                                      | 16 |

|     | 4.2   | Pin Assignments                                                  | 17 |

| 5.0 | Fund  | ctional Description                                              | 18 |

|     | 5.1   | Introduction                                                     | 18 |

|     | 5.2   | Internal Operation                                               |    |

|     | 5.3   | Service Request and Interrupt Operation                          |    |

|     |       | 5.3.1 Theory of Operation                                        |    |

|     |       | 5.3.2 Internal Implementation of the Service Request Logic       |    |

|     |       | 5.3.3 Priorities and Fair Share                                  |    |

|     | 5.4   | Types of Service Requests                                        |    |

|     |       | 5.4.1 Receive Service Requests                                   |    |

|     |       | 5.4.2 Transmit Service Requests                                  |    |

|     | 5.5   | Implementing Service Requests                                    |    |

|     | 3.3   | 5.5.1 Method 1a — Full Interrupt – Type A, Three-Level Interrupt | pt |

|     |       | with Three-Level Acknowledge                                     | 37 |

|     |       | 5.5.2 Method 1b — Full Interrupt – Type B, Three-Level           | 20 |

|     |       | Interrupt with Single-Level Acknowledge                          | 38 |

|     |       | Interrupt with Single-Level Acknowledge                          | 39 |

|     |       | 5.5.4 Method 3b — Polled Interface                               | 40 |

|     |       | 5.5.5 Comparison of Interrupt and Polled Code Sequences          |    |

|     |       | 5.5.6 Cascading Service Requests with Multiple CD1865s           |    |

|     |       | 5.5.7 Multiple CD1865s without Cascading                         |    |

|     |       | 5.5.8 Acknowledging Service Requests                             | 44 |

| 6.0 | Syst  | tem Bus Interface and System Clock                               | 46 |

|     | 6.1   | System Interface Considerations                                  | 47 |

|     | 6.2   | System Clock and Bit Rate Options                                |    |

|     |       | 6.2.1 System Clock                                               | 47 |

|     |       | 6.2.2 External Clock                                             |    |

|     |       | 6.2.3 1¥ Clock Option                                            |    |

|     |       | 6.2.4 Bit Rate Options                                           |    |

|     |       | 6.2.5 Maximum Throughput Limits                                  |    |

|     | 6.3   | CD1865 Basic Bus Interface and Addressing                        |    |

|     |       | 6.3.1 Intel, Versus Motorola, Interface Signals and Addressing.  | 51 |

|     |       |                                                      | ed Bus Interface          |    |

|-----|-------|------------------------------------------------------|---------------------------|----|

|     | 6.4   |                                                      |                           |    |

|     |       |                                                      | nily Processors           |    |

|     |       | 6.4.2 Interfacing to 680X0-Far                       | nily Processors           | 55 |

|     |       | 6.4.3 Interfacing to the VME B                       | us                        | 55 |

| 7.0 | Seria | Interfaces                                           |                           | 58 |

|     | 7.1   | Receiver Operation                                   |                           | 58 |

|     |       | 7.1.1 Basic Operation                                |                           | 58 |

|     |       |                                                      |                           |    |

|     |       |                                                      |                           |    |

|     |       | 7.1.4 Receive Service Reques                         | ts                        | 60 |

|     |       | 7.1.5 Receive Good Data‰ Se                          | ervice Request            | 61 |

|     |       | 7.1.6 Receive Exception Servi                        | ce Request                | 61 |

|     |       | 7.1.7 Types of Errors                                |                           | 62 |

|     |       | 7.1.8 Types of Exceptions                            |                           | 62 |

|     |       | 7.1.9 Flow-Control Characters                        |                           | 63 |

|     |       | 7.1.10 Programming Notes                             |                           | 68 |

|     | 7.2   | Transmitter Operation                                |                           | 68 |

|     |       | 7.2.1 Basic Operation                                |                           | 68 |

|     |       | 7.2.2 FIFO Operation                                 |                           | 69 |

|     |       | 7.2.3 Transmit Service Reque                         | sts                       | 69 |

|     |       | 7.2.4 Special Transmitter Com                        | mands                     | 70 |

|     |       | 7.2.5 Special Character Trans Special Character Comm | mission by Send<br>nand   | 70 |

|     |       | 7.2.6 Embedded Transmit Cor                          | nmands                    | 70 |

|     |       | 7.2.7 Sending Breaks                                 |                           | 71 |

|     |       | 7.2.8 Sending Inter-Character                        | Delays                    | 71 |

|     |       |                                                      | nsmitter Commands         |    |

|     | 7.3   | Flow Control                                         |                           | 72 |

|     |       | 7.3.1 Receiver Flow Control                          |                           | 72 |

|     |       | 7.3.2 Receiver Hardware (Out                         | -of-Band) Flow Control    | 73 |

|     |       | 7.3.3 Receiver Software (In-Ba                       | and) Flow Control         | 74 |

|     |       | 7.3.4 Transmitter Flow Control                       | ,                         | 75 |

|     |       |                                                      | out-of-Band) Flow Control |    |

|     |       | 7.3.6 Transmitter Software (In-                      | Band) Flow Control        | 76 |

|     | 7.4   | Modem Signals and General-Pur                        | pose I/O                  | 78 |

|     |       | 7.4.1 Generating Service Requ                        | uests with Modem Pins     | 80 |

|     |       |                                                      | eneral-Purpose I/O        |    |

|     | 7.5   |                                                      | < Tests                   |    |

| 8.0 | Prog  | amming                                               |                           | 83 |

|     | 8.1   | Types of Registers                                   |                           | 83 |

|     | 8.2   | Access Duty Cycle                                    |                           | 84 |

|     | 8.3   | Accessing FIFOs Versus Other F                       | Registers                 | 84 |

|     | 8.4   | Initialization                                       |                           | 84 |

|     | 8.5   | Global Register Initialization                       |                           | 86 |

|     | 8.6   |                                                      |                           |    |

|     | 8.7   |                                                      |                           |    |

|     | 8.8   | Channel Initialization and Chang                     | es                        | 87 |

|      | 8.9  |         | nitting Data                                                                                 |     |

|------|------|---------|----------------------------------------------------------------------------------------------|-----|

|      | 8.10 |         | ring Data                                                                                    |     |

|      | 8.11 |         | mming Examples                                                                               |     |

|      |      |         | Programming the Service Match Registers                                                      |     |

|      |      |         | CD1865 Initialization                                                                        |     |

|      |      |         | Basic I/O Operations                                                                         |     |

|      |      |         | Interrupt Response Operations                                                                |     |

|      |      | 8.11.5  | Polled Mode Operation                                                                        | 93  |

| 9.0  | Deta | iled Re | gister Descriptions                                                                          | 94  |

|      | 9.1  |         | er Map Quick Reference                                                                       |     |

|      | 9.2  | Global  | Registers                                                                                    |     |

|      |      | 9.2.1   | Miscellaneous Registers                                                                      | 98  |

|      |      | 9.2.2   | Configuration Registers                                                                      |     |

|      |      | 9.2.3   | Service Request/Interrupt Control Registers                                                  |     |

|      | 9.3  | Indexe  | d Indirect Registers                                                                         |     |

|      |      | 9.3.1   | Receive Data Count Register                                                                  |     |

|      |      | 9.3.2   | Receive Data Register                                                                        |     |

|      |      | 9.3.3   | Receive Character Status Register                                                            |     |

|      |      | 9.3.4   | Transmit Data Register                                                                       |     |

|      |      | 9.3.5   | End-of-Service Request Register                                                              |     |

|      | 9.4  |         | el Registers                                                                                 |     |

|      |      | 9.4.1   | Enable Register                                                                              |     |

|      |      | 9.4.2   | Channel Command Register                                                                     |     |

|      |      | 9.4.3   | Channel Option Register 1                                                                    |     |

|      |      | 9.4.4   | Channel Option Register 2                                                                    |     |

|      |      | 9.4.5   | Channel Option Register 3                                                                    |     |

|      |      | 9.4.6   | Channel Control Status Register                                                              |     |

|      |      | 9.4.7   | Receiver Bit Register                                                                        |     |

|      |      | 9.4.8   | Receive Time-Out Period Register                                                             |     |

|      |      | 9.4.9   | Receive Bit Rate Period Registers (High/Low)                                                 |     |

|      |      | 9.4.10  | 3 ( 3 )                                                                                      |     |

|      |      | 9.4.11  | Special Character Register 1                                                                 |     |

|      |      |         | Special Character Register 2                                                                 |     |

|      |      |         | Special Character Register 3                                                                 |     |

|      |      |         | Special Character Register 4                                                                 |     |

|      |      |         | Modem Change Register                                                                        |     |

|      |      |         | Modem Change Option Register 1                                                               |     |

|      |      |         | Modem Change Option Register 2                                                               |     |

|      |      | 9.4.18  | 3                                                                                            |     |

|      |      |         | Modem Signal Value Request-to-Send Register  Modem Signal Value Data-Terminal-Ready Register |     |

| 40.0 |      |         |                                                                                              |     |

| 10.0 |      | '       | pecifications                                                                                |     |

|      | 10.1 |         | te Maximum Ratings                                                                           |     |

|      | 10.2 |         | nmended Operating Conditions                                                                 |     |

|      | 10.3 |         | ectrical Characteristics                                                                     |     |

|      | 10.4 |         | of Timing Information                                                                        |     |

|      | 10.5 |         | ectrical Characteristics                                                                     |     |

|      |      | 10.5.1  | Clocked Bus Interface                                                                        | 128 |

# CD1865 — Intelligent Eight-Channel Communications Controller

|         |      | 40 F.O. Unalaskad Dva Interface                                               | 400 |

|---------|------|-------------------------------------------------------------------------------|-----|

|         |      | 10.5.2 Unclocked Bus Interface                                                |     |

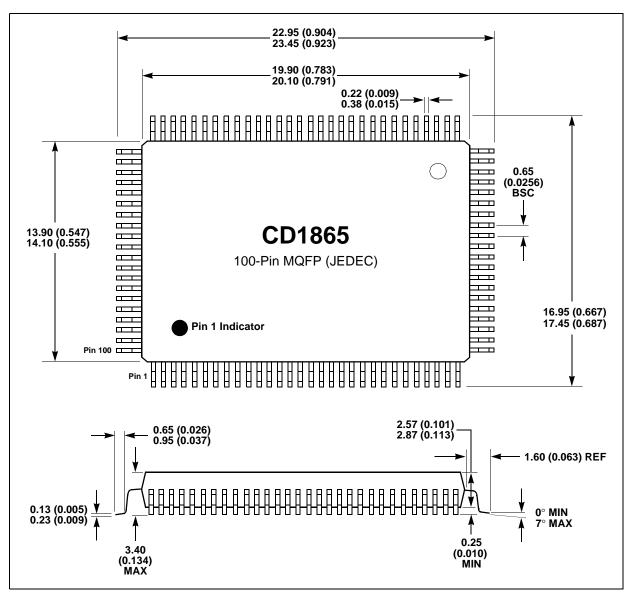

| 11.0    | Pack | age Specifications                                                            | 145 |

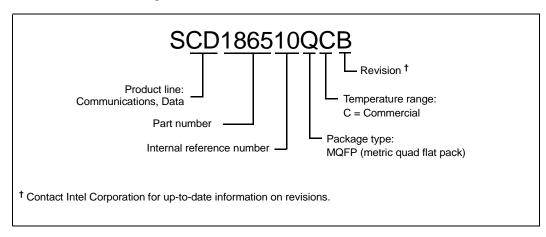

| 12.0    | Orde | ering Information                                                             | 146 |

| Index   |      |                                                                               | 147 |

| Figures |      |                                                                               |     |

|         | 1    | Functional Block Diagram                                                      |     |

|         | 2    | Internal Block Diagram                                                        |     |

|         | 3    | Foreground/Background Internal Structure                                      |     |

|         | 4    | Internal Operation Flow Chart                                                 |     |

|         | 5    | Internal Service Acknowledge Decision Tree                                    |     |

|         | 6    | Internal Fair-Share Operation                                                 |     |

|         | 7    | Receive Timer Operation                                                       | 34  |

|         | 8    | Three-Level Interrupt with Three-Level Acknowledge Example                    | 38  |

|         | 9    | Three-Level Interrupt with Single-Level Acknowledge Example                   | 39  |

|         | 10   | Single-Level Interrupt with Single-Level Acknowledge Example                  |     |

|         | 11   | Simple Software Polled Interface Example                                      | 41  |

|         | 12   | Polled Code Sequence                                                          | 42  |

|         | 13   | Interrupt Code Sequence                                                       | 43  |

|         | 14   | Internal Block Diagram                                                        | 46  |

|         | 15   | 2¥ Clock Option                                                               |     |

|         | 16   |                                                                               |     |

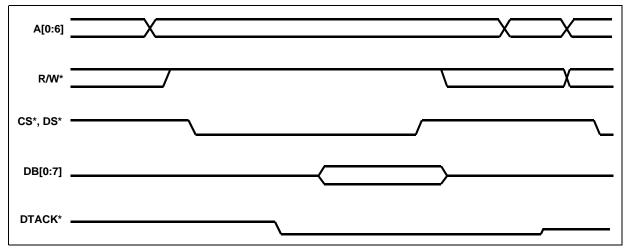

|         | 17   | Typical Unclocked Bus Interface                                               |     |

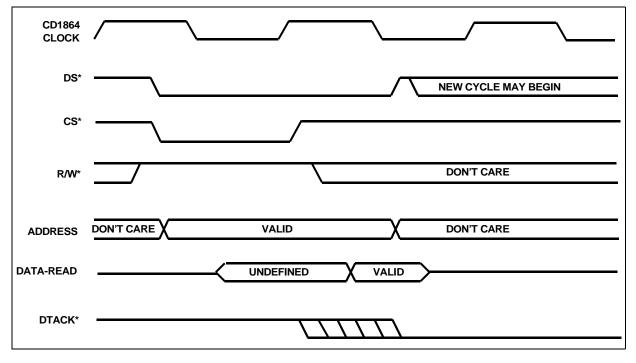

|         | 18   | Typical Clocked Bus Interface                                                 |     |

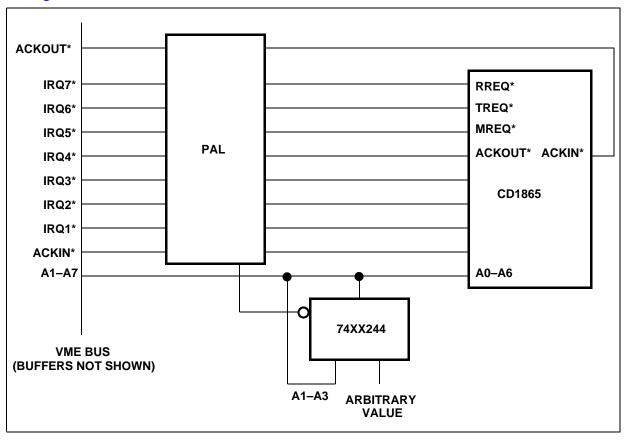

|         | 19   | Incorrect VME Interface                                                       |     |

|         | 20   | Correct VME Interface                                                         |     |

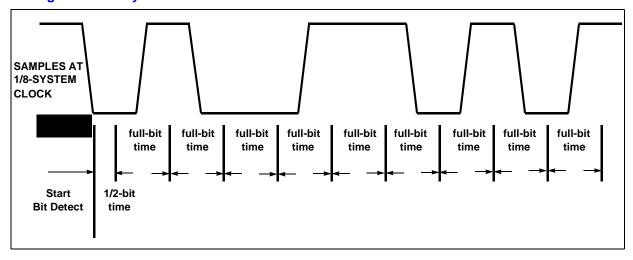

|         | 21   | Bit Synchronization in CD1865                                                 |     |

|         | 22   | Receive Operation                                                             |     |

|         | 23   | No New Data Timer Logic                                                       |     |

|         | 24   | Transmitter Operation                                                         |     |

|         | 25   | Receiver Flow-Control Logic                                                   |     |

|         | 26   | Transmitter Flow-Control Logic                                                |     |

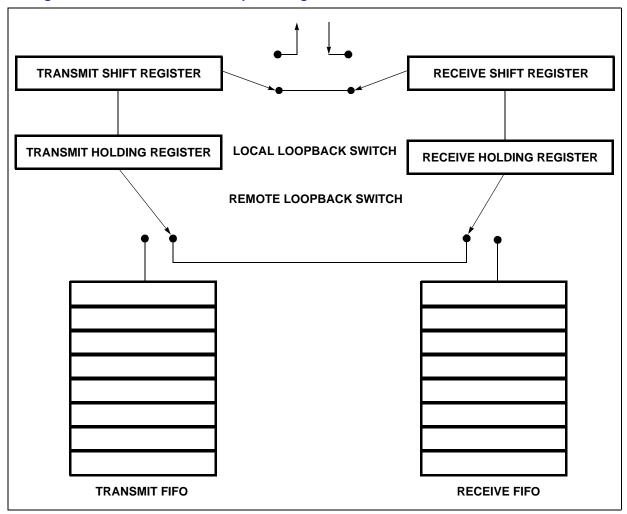

|         | 27   | Local and Remote Loopback Logic                                               |     |

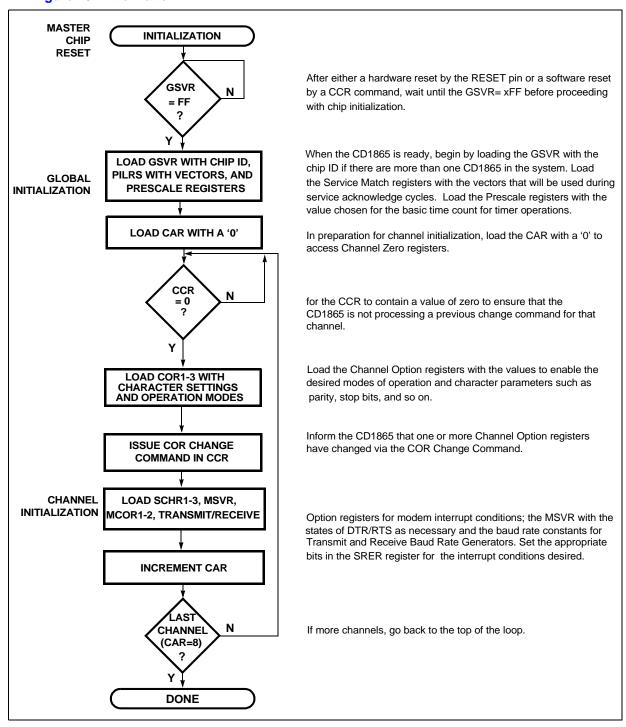

|         | 28   | Initialization                                                                |     |

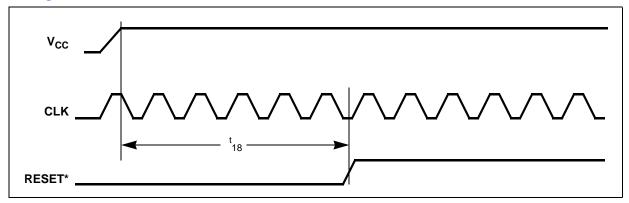

|         | 29   | Clocked Bus Interface Reset                                                   |     |

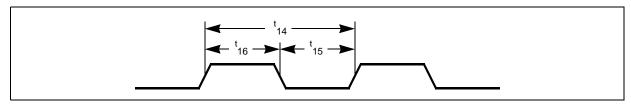

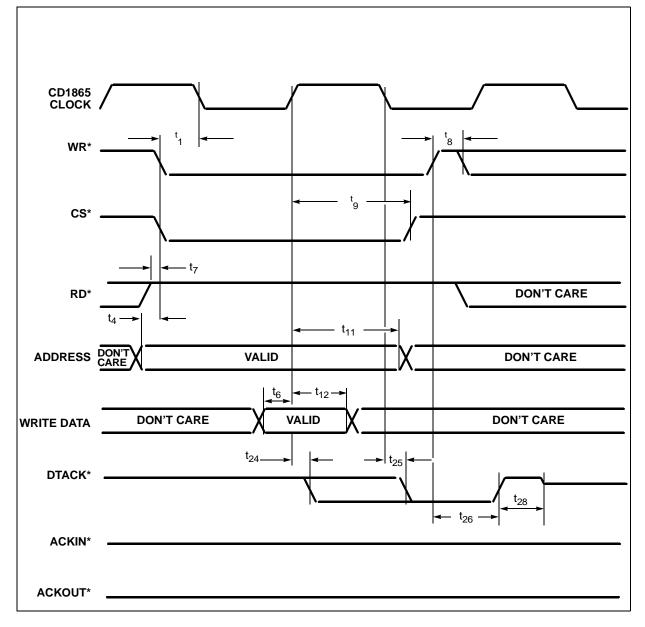

|         | 30   | Clocked Bus Interface Clocks                                                  | 131 |

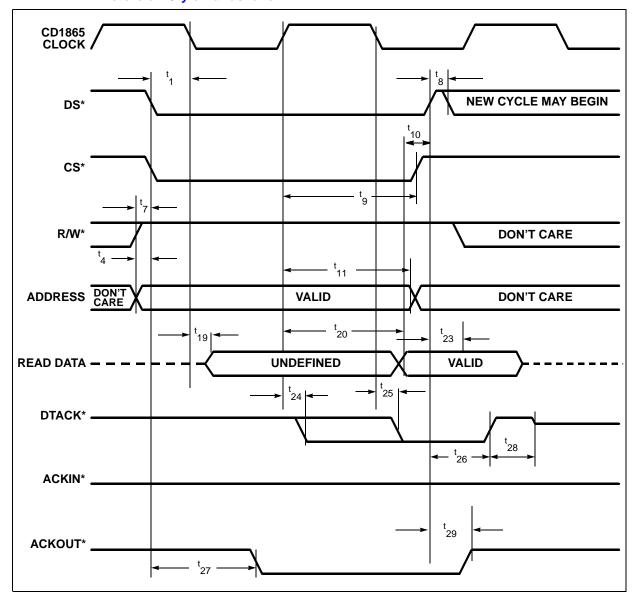

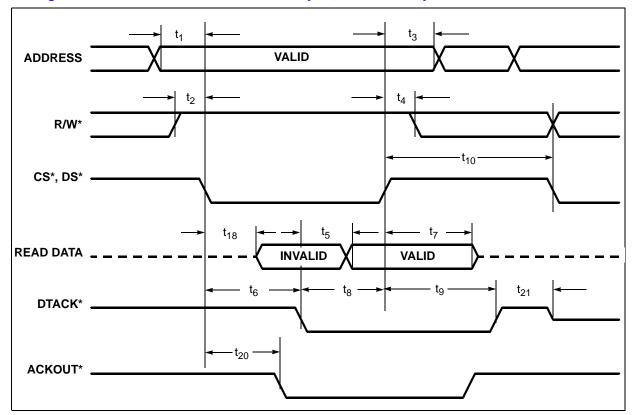

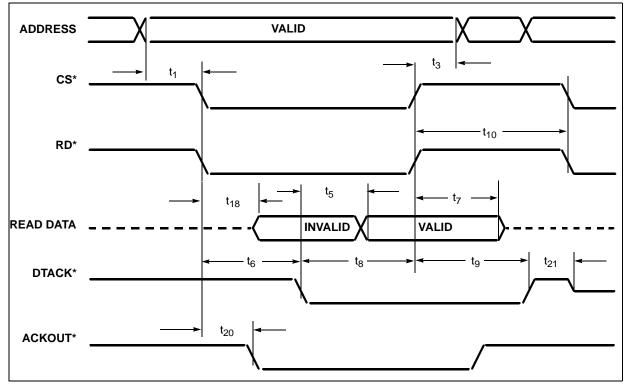

|         | 31   | Clocked Bus Interface Read Cycle, Motorola,-Style Handshake                   | 131 |

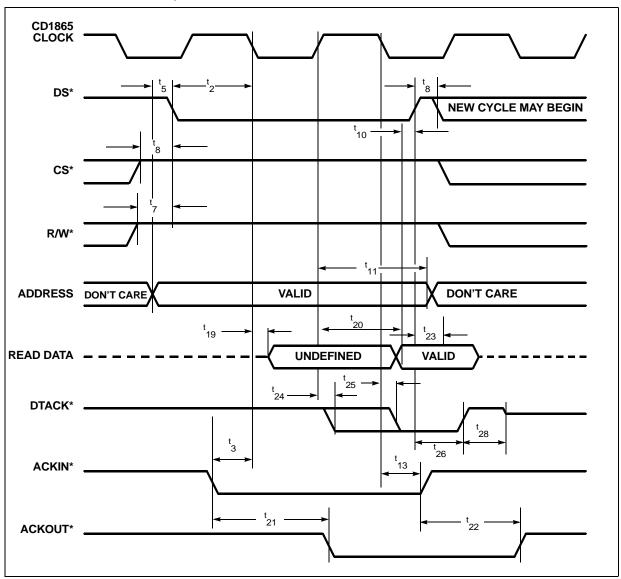

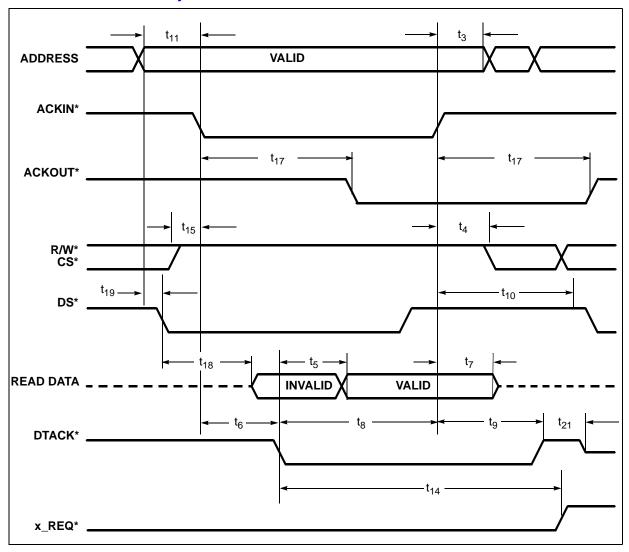

|         | 32   | Clocked Bus Interface Service Acknowledgment Cycle, Motorola,-Style Handshake | 132 |

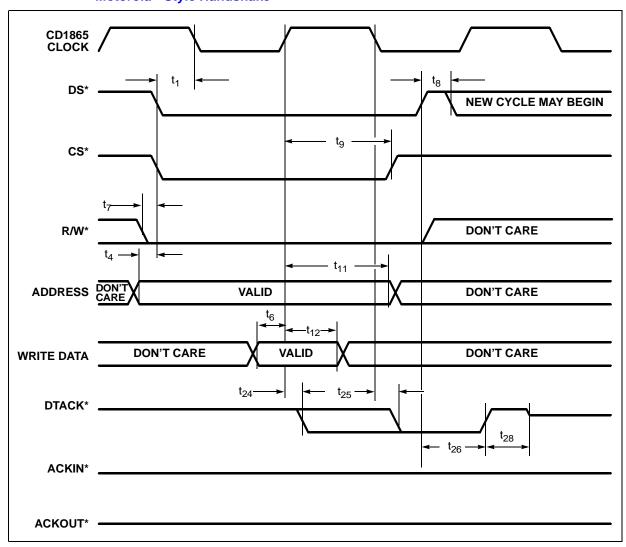

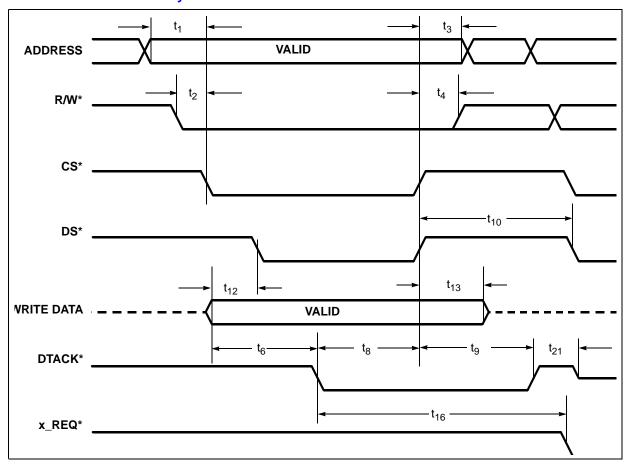

|         | 33   | Clocked Bus Interface Write Cycle, Motorola,-Style Handshake                  | 133 |

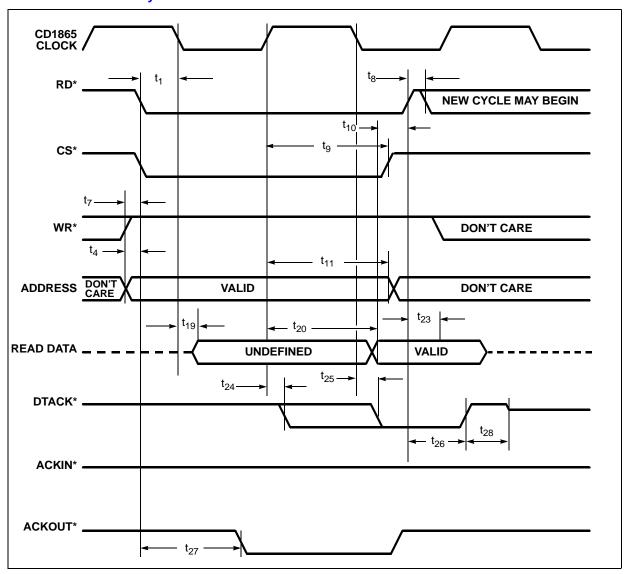

|         | 34   | Clocked Bus Interface Read Cycle, Intel,-Style Handshake                      | 134 |

|         | 35   | Clocked Bus Interface Service Acknowledgment Cycle, Intel,-Style Handshake    |     |

|         | 36   | Clocked Bus Interface Write Cycle, IntelStyle Handshake                       | 136 |

# Intelligent Eight-Channel Communications Controller — CD1865

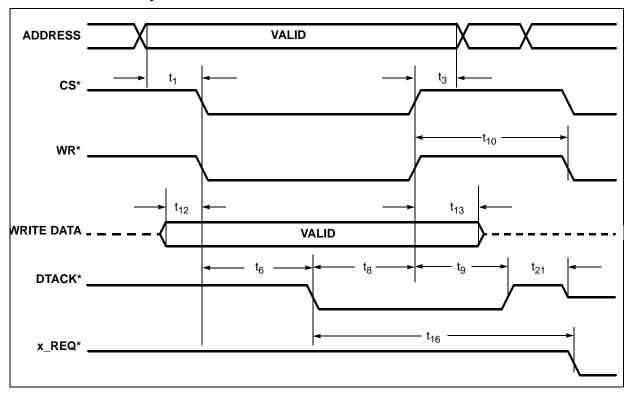

|               | 37 | Unclocked Bus Interface Read Cycle, Motorola,-Style Handshake | 139 |

|---------------|----|---------------------------------------------------------------|-----|

|               | 38 | Unclocked Bus Interface Service Acknowledgment Cycle,         |     |

|               |    | Motorola,-Style Handshake                                     | 140 |

|               | 39 | Unclocked Bus Interface Write Cycle,                          |     |

|               |    | Motorola,-Style Handshake                                     | 141 |

|               | 40 | Unclocked Bus Interface Read Cycle, Intel,-Style Handshake    |     |

|               | 41 | Unclocked Bus Interface Service Acknowledgment Cycle,         |     |

|               |    | Intel,-Style Handshake                                        | 143 |

|               | 42 | Unclocked Bus Interface Write Cycle,                          |     |

|               |    | Intel,-Style Handshake144                                     |     |

|               |    |                                                               |     |

| <b>Tables</b> |    |                                                               |     |

| Tablee        | 4  | OD40VV Day Last Fare'll                                       | 4.5 |

|               | 1  | CD18XX Product Family                                         |     |

|               | 2  | Differences Between the CD1865 and CD1864                     |     |

|               | 3  | State Machine Logic                                           | 29  |

|               | 4  | Service Request Methods                                       | 36  |

|               | 5  | Bit Rate Constants, CLK = 33 MHz                              | 49  |

|               | 6  | Bit Rate Constants, CLK = 25 MHz                              | 49  |

|               | 7  | Bit Rate Constants, CLK = 20 MHz                              |     |

|               | 8  | Bit Rate Constants, CLK = 15 MHz                              |     |

|               | 9  | Register Summary                                              |     |

|               | 10 | Clocked Timings                                               |     |

|               |    |                                                               |     |

|               | 11 | Unclocked Timings                                             | 137 |

# **Revision History**

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | May 2001 | Initial release. |

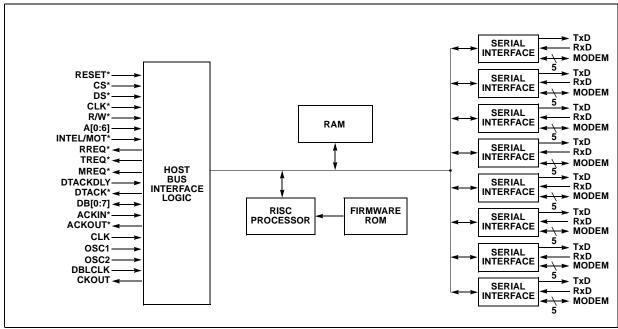

Figure 1. Functional Block Diagram

# 1.0 Overview

The CD1865 is a cost-effective controller capable of controlling eight full-duplex channels transferring data at rates up to 115.2 kbps. The advantage of the CD1865 lies in its ability to efficiently move data from the serial channels to the host. This results in an order-of-magnitude improvement in system-level throughput and a reduction in overhead on the host CPU.

To increase the overall data throughput of the system, the device relies on a combination of features. Most important are the buffers for transmit and receive data. Each serial channel has three 8-byte FIFOs — one each for transmit, receive, and receive exception status. The receive FIFOs have programmable thresholds to minimize interrupt latency requirements.

The CD1865 is based on a high-performance proprietary RISC processor architecture developed by Intel specifically for data communication applications. This processor executes all instructions in one clock cycle, and uses a register-window architecture to ensure zero-overhead context switch for each type of internal interrupt.

The CD1865 is fabricated in an advanced CMOS process. The device's high throughput, low-power consumption, and high-level of integration permit system designs with minimum parts count, maximum performance, and maximum reliability.

# 1.1 Theory of Operation

The CD1865 custom RISC processor is assisted by specialized peripheral logic. Serial data transmission and reception is handled by 'bit engines'. Each channel has a bit engine for transmit and another for receive. While each engine handles all bit-level timing, bit-to-character assembly is done in firmware. Bits are passed to the processor by internal interrupts, over a special bus dedicated to this purpose. To reduce internal interrupts to zero, special interrupt context hardware points to the correct register window for every possible context. A unique Global Index register eliminates address calculations by always pointing to the current channel.

The processor assembles bits into characters, checks parity and other formatting parameters, and stores the data in the FIFOs as required. FIFOs are maintained as RAM-based structures. Both the local processor and the host access them by Pointer registers, in effect an Indexed Addressing mode.

The CD1865 communicates with the host by service requests and service acknowledgments. Service requests can be detected by interrupt lines or by on-device registers. Regardless of the method used, the CD1865 has features to minimize both the number of requests to be serviced and the time required to service them. FIFOs help reduce the number of service requests to one every eight characters. To reduce the time required per request, the CD1865 supplies separate vectors for four different types of service requests. This reduces the time required by the processor to effect the proper operation. For instance, there is a unique vector for 'good data', so that the host wastes no time checking status bits or error conditions. If there is an error condition, the CD1865 supplies a unique vector pointing to the error-handling routine. Other vectors report transmit status and modem signal change.

Interrupts can be acknowledged either by an Interrupt Acknowledge pin, or by reading an ondevice register. This allows host software maximum flexibility and speed in handling service requests.

Because the CD1865 RISC processor is processing every character sent or received, features such as automatic flow control and special character recognition are easily implemented. This further reduces the processing burden on the host system. Both In-Band (Xon, Xoff) and Out-of-Band (RTS/CTS, DTR) Flow-Control modes are supported. For in-band flow control, the CD1865 automatically starts and stops its transmitter when the remote unit sends flow-control characters. The CD1865 also makes it easy for the local host to flow-control the remote, by the 'send special character' commands. For out-of-band flow control, the transmitter optionally asserts RTS and monitor CTS for permission to send; and assert/negate DTR when the Receive FIFO reaches a user- definable threshold. Together, the in-band and out-of-band features not only allow the data flow to be controlled in real time with minimum or no host intervention, it also prevents loss of data.

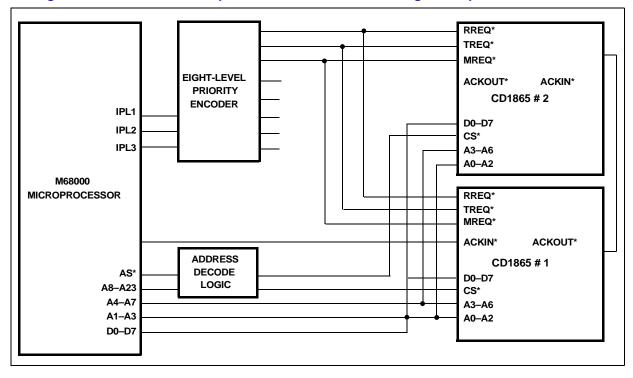

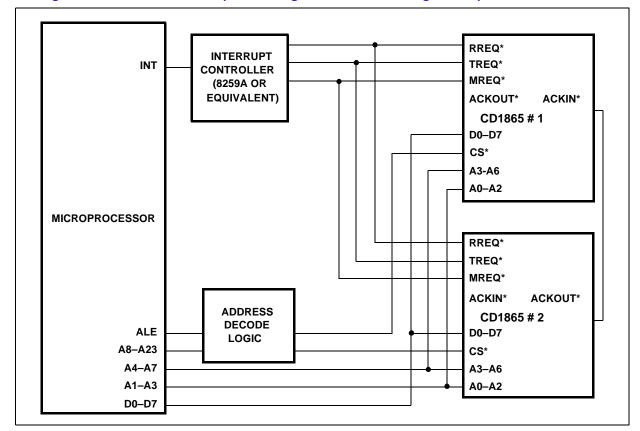

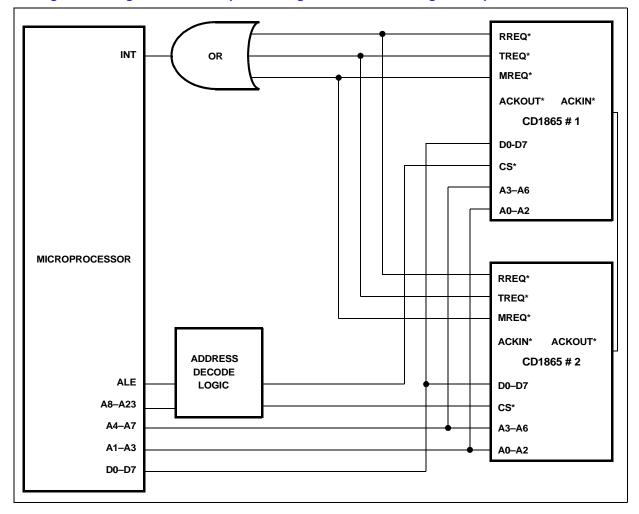

As shown on the previous page, the CD1865 can interface virtually any CPU, with a minimum of glue logic. Refer to the CD1865 Data Sheet for detailed information on how to interface various microprocessors. Systems with multiple CD1865s are easily implemented, with no external glue, by device a daisy-chain scheme. A 'fair share' feature ensures equal access for all service requests, both within one CD1865 and across multiple devices.

**FIFO** — 24 bytes of FIFO are dedicated to each channel partitioned as 8 bytes for transmitter, 8 bytes for receiver, and 8 bytes for status. The receive FIFO has a user-programmable threshold to optimize system response and latency. The receive FIFO threshold programming range is from 1–8 characters.

**Vectored Interrupt Structure** — Three interrupt signals ([R, T, M]REQ\*) are used. These signals may also be read as an on-device register. Each REQ\* signal represents one of three interrupt groups: receive, transmit, and modem signal state changes. Upon servicing by the host, an interrupt vector is generated by the CD1865 to define the interrupt group to be serviced and which CD1865 generated the interrupt. This allows the host software to enter directly into the proper interrupt service routine, reducing the amount of interaction between the host and the controller, and determining the nature of the interrupt.

**Good Data Interrupt** — If data received is all good, the host is advised of the number of good data bytes in the FIFO, allowing the host to read data without further status queries until all good data has been transferred.

**Fair-Share Interrupt Scheme** — To ensure equal service of all channels, a fair share scheme is used for each interrupt group. No channel can interrupt for the same condition until all others have a chance to be serviced for the same interrupt condition.

# CD1865 — Intelligent Eight-Channel Communications Controller

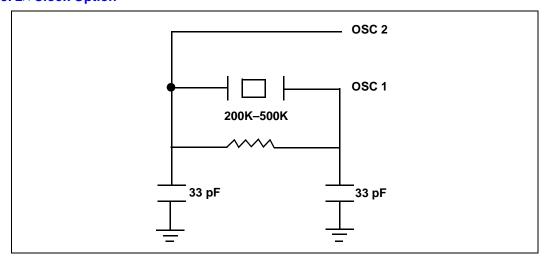

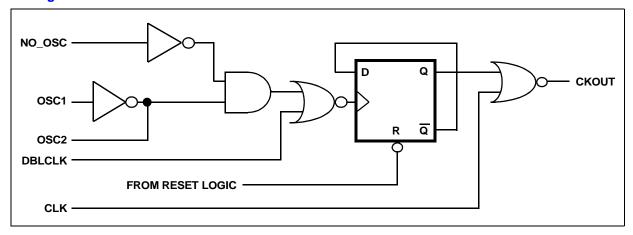

*Note:* To support 115.2 kbps, a system clock of 66 MHz is required. System design is simplified in the CD1865 by providing a choice of crystal or external clock operation, at 1×- or 2×-rated frequency.

# 2.0 Conventions

# 2.1 Abbreviations

| Symbol               | Units of measure                  |  |

|----------------------|-----------------------------------|--|

| °C                   | degree Celsius                    |  |

| μF                   | microfarad                        |  |

| μs                   | microsecond (1,000 nanoseconds)   |  |

| Hz                   | hertz (cycle per second)          |  |

| Kbit                 | kilobit (1,024 bits)              |  |

| kbps<br>kbits/second | kilobit (1,000 bits) per second   |  |

| Kbyte                | kilobyte (1,024 bytes)            |  |

| kbytes/second        | kilobyte (1,000 bytes) per second |  |

| kHz                  | kilohertz                         |  |

| kΩ                   | kilohm                            |  |

| Mbyte                | megabyte (1,048,576 bytes)        |  |

| MHz                  | megahertz (1,000 kilohertz)       |  |

| mA                   | milliampere                       |  |

| ms                   | millisecond (1,000 microseconds)  |  |

| ns                   | nanosecond                        |  |

| pV                   | picovolt                          |  |

| V                    | volt                              |  |

| W                    | watt                              |  |

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

# 2.2 Acronyms

| Acronym | Definition                              |

|---------|-----------------------------------------|

| AC      | alternating current                     |

| CMOS    | complementary metal-oxide semiconductor |

| DC      | direct current                          |

| DMA     | direct-memory access                    |

| DRAM    | dynamic random-access memory            |

| FIFO    | first in/first out                      |

# CD1865 — Intelligent Eight-Channel Communications Controller

| Acronym | Definition (Continued)         |

|---------|--------------------------------|

| HDLC    | high-level data link control   |

| ISA     | industry standard architecture |

| LSB     | least-significant bit          |

| MSB     | most-significant bit           |

| PPP     | point-to-point protocol        |

| MQFP    | metric quad flat pack          |

| RAM     | random-access memory           |

| R/W     | read/write                     |

| SDLC    | synchronous data link control  |

| TTL     | transistor-transistor logic    |

# 3.0 Device Selection Considerations

The CD1865 device is an enhanced version of the same product family as the CD180 and CD1864. The CD1865 is software compatible with both the CD180 and CD1864. If this is a new CD1865 design, please skip this page.

The CD1865 is recommended for any new designs. Please note that to achieve the high data rates, 66-MHz system clock is required. To support data rates of up to 115.2 kbps, the specified system clock frequency is required. Please refer to the differences in pins between the CD1864 and CD1865. It is recommended that the 66-MHz, 2×-clock option (oscillator or crystal) is used wherever possible.

Table 1. CD18XX Product Family

| Features          | CD180                          | CD1864                            | CD1865                         |

|-------------------|--------------------------------|-----------------------------------|--------------------------------|

| Package           | 84-pin PLCC                    | 100-pin PQFP                      | 100-pin MQFP                   |

| System clock      | 12.5 MHz                       | 25 MHz (×2) or<br>12.5 MHz (×1)   | 66 MHz (×2) or<br>33 MHz (×1)  |

| Maximum bit rates | 64 kbps                        | 64 kbps                           | 115.2 kbps                     |

|                   | DTRSEL *                       | -                                 | -                              |

| Pins              | 4 modem/IO signals per channel | 5 modem/IO signals per<br>channel | 5 modem/IO signals per channel |

*Note:* This input (DTRSEL) on the CD180 sets the mode for the DTR\*/CD\* pins. When DTRSEL is high, the DTR\*/CD\* pins implement the DTR\* output; when low, the DTR\*/CD\* pins become CD\* inputs.

The CD1864 and CD1865 have separate DTR and CD pins and so the DTRSEL is eliminated.

Table 2. Differences Between the CD1865 and CD1864

| Pin Number | CD1865<br>Pin Name | CD1864<br>Pin Name | Comments |

|------------|--------------------|--------------------|----------|

| 1          | V <sub>CC</sub>    | n/c                | Note 1   |

| 16         | GND                | n/c                | Note 1   |

| 37         | V <sub>CC</sub>    | n/c                | Note 2   |

#### NOTES

- 1. Pin 1 and pin 16 are truly no-connects on the CD1864 device.

- Pin 37 on the CD1864 is not a true no-connect, and can cause problems if connected to V<sub>CC</sub>. To make a single board design be compatible with either the CD1864 or CD1865, a configuration jumper must be used to allow pin 37 to be a no-connect or a V<sub>CC</sub> connection.

In January 1995, Intel changed all 100-pin PQFP package types from EIAJ to JEDEC. The CD1865 is now available in a JEDEC package. Before beginning any new design or converting from CD1864 to CD1865, please contact Intel for package details.

**Warning:** The CD1865 device may have potential latch up problems if used in socket. It is recommended that this device be surface mounted.

# 4.0 Pin Information

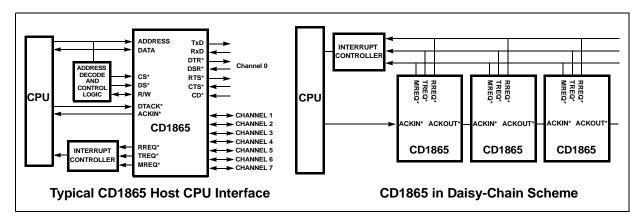

The CD1865 is available in a 100-pin MQFP (metric quad flat pack device) configuration as shown below.

# 4.1 Pin Diagram

NOTE: (\*) Denotes an active-low (negative-true) signal.

# 4.2 Pin Assignments

The following conventions are used in the table below: (\*) denotes an active-low signal; I = input; I/O = input/output; O = output; O = open drain; O = open drain;

# 5.0 Functional Description

#### 5.1 Introduction

The CD1865 I/O coprocessor controls eight full-duplex channels that transfer data at rates up to 115.2 kbps. The CD1865 efficiently moves data between the serial channels and the host, resulting in a great improvement in system-level throughput and a reduction in overhead on the host CPU. This improvement is obtained by reducing the number of service requests (interrupts) the host must respond to and reducing the complexity and time required to handle each service request.

The CD1865 relies on a combination of features to reduce the number and complexity of service requests. Most important are the buffers for transmit and receive data. Each serial channel has three 8-byte FIFOs — one each for transmit, receive, and receive-exception status. The Receive FIFOs have programmable thresholds to minimize interrupt latency requirements. The vectored service requests and the Good Data™ interrupt allow the host system to immediately transfer data upon beginning processing of a service request, without tedious checking of flags and error conditions.

The CD1865 is based on a high-performance, proprietary RISC processor architecture developed by Intel specifically for data communications applications. The CD1865 processor executes all instructions in one-clock cycle, and it uses a register window architecture to ensure zero-overhead context switch for each type of internal interrupt. The instruction set of this processor is optimized for bit-oriented tasks that combined with instantaneous response to sending or receiving one bit, allow highly efficient processing of characters. All firmware for the CD1865 processor is contained in an on-device ROM, and requires no user programming.

The CD1865 processor is assisted in its task by specialized peripheral logic. Serial data transmission and reception is handled by 'bit engines'. Each channel has a bit engine for transmitting and another for receiving. While each engine handles all bit-level timing, bit-to-character assembly is done in firmware. Bits are passed to the CD1865 processor by internal interrupts over a special bus dedicated to this purpose. Special internal-interrupt context hardware reduces overhead on internal interrupts to zero by pointing to the correct register window for every possible context, and a unique Global Index register eliminates address calculations by always pointing to the current channel. External service requests to the host system are also hardware assisted. There is a queue for each of the three classes of external service requests, and the request/acknowledgment mechanism is entirely in hardware to minimize response time.

The CD1865 processor assembles bits into characters, checks parity and formatting parameters, and stores the data in the FIFOs as required. FIFOs are maintained as RAM-based structures, and both the local CD1865 processor and the host access them by Pointer registers by an Indexed Addressing mode.

The CD1865 communicates with the host by service requests and service acknowledgments. Service requests can be handled either as interrupts or by polling. Regardless of the method used, the CD1865 has features to minimize both the number of requests to be serviced and the time required to service them. The number of service requests is reduced by the FIFOs since a service request is required only every eight characters. To reduce the time required per request, the CD1865 supplies separate vectors for four different types of service requests. This reduces the time required by the host CPU to determine what action to take. For example, there is a unique vector for Good Data so that the host wastes no time checking status bits for error conditions. If there is an error condition, the CD1865 supplies a unique vector pointing to the error-handling routine. Other vectors report transmit status and modem signal change.

#### Intelligent Eight-Channel Communications Controller — CD1865

Service requests to the host system are implemented on the CD1865 by three hardware service request state machines. Each machine has the ability to 'queue-up' multiple requests. The state machines are designed to offer the fastest response possible. Whenever the CD1865 processor determines that a condition needs a service request, it queues the request with the appropriate state machine. The state machine posts the external request, monitors acknowledgment cycles from the host, and informs the CD1865 processor when a valid service acknowledgment has been completely serviced. This allows the CD1865 to correctly maintain the internal context for processing the channel being serviced.

Because the CD1865 processor processes every character sent or received, features such as Automatic Flow Control and Special Character Recognition are easily implemented. This reduces the processing burden on the host system. Both In-Band (Xon, Xoff) and Out-of-Band (RTS/CTS, DTR/DSR) Flow Control modes are supported. For In-Band Flow Control, the CD1865 automatically starts and stops its transmitter when the remote unit sends flow-control characters. The CD1865 makes it easy for the local host to flow-control the remote by the 'Send Special Character' commands. For Out-of-Band Flow Control, the transmitter optionally asserts RTS and monitors CTS for permission to send, and assert/negate DTR when the Receive FIFO reaches a user-definable threshold. DSR can be used to gate the receiver on and off. Together, the In-Band and Out-of-Band features allow the data flow to be controlled in realtime with minimum or no host intervention, and this also prevents loss of data.

Systems with multiple CD1865s are easily implemented, with no external glue, by a daisy-chain scheme. A fair-share feature ensures equal access for all service requests, both within one CD1865 and across multiple devices. Alternately, multiple CD1865s can be operated in parallel as independent devices.

Serial channels on the CD1865 are entirely independent of one another. Any channel can be programmed to a combination of features regardless of the state of other channels. Bit-rate generators are programmed by loading a divisor value, so the transmitters and receivers can each operate at any standard or non-standard data rate.

The CD1865 can detect the received line-break condition, send break characters of any length, and transmit delays. This is done by transmit commands embedded in the Transmit Data Stream. The CD1865 can also be programmed to detect user-defined special characters and generate a special service request to the host. Parity checking is performed automatically, but can be overridden by the host to force parity errors for test purposes. Character length and Stop bit length are also programmable per-channel.

Modem pins on the CD1865 are general-purpose, that is, they are not hard-wired into the UART functions. If modem pins are not needed to interface to actual modems, they can be used as general-purpose I/O pins. In either case they are readable and writable directly by the host system. In addition, the CD1865 can be programmed to monitor levels on modem input pins and generate service requests to the host upon detecting a specified change.

The CD1865 is fabricated in an advanced CMOS process. Its high throughput, low-power consumption, and high level of integration permits system designs with minimum parts count, maximum performance, and greater reliability.

There is a significant difference between the CD1865 and conventional dumb UARTs; the CD1865 is more efficient and intelligent, even when operating in a polled environment. Systems built with the CD1865 interface between the host and the I/O device at a higher level than systems built with conventional UARTs. For example, with a dumb UART, the host must test each channel for presence of data, a process that is time-consuming. With the CD1865, the host queries the entire

serial I/O subsystem for the presence of data. If data is present, the CD1865 determines which channel it is on, and whether it is good or erroneous. Thus, using the CD1865, the host-peripheral interface is easier to implement, faster, and more efficient.

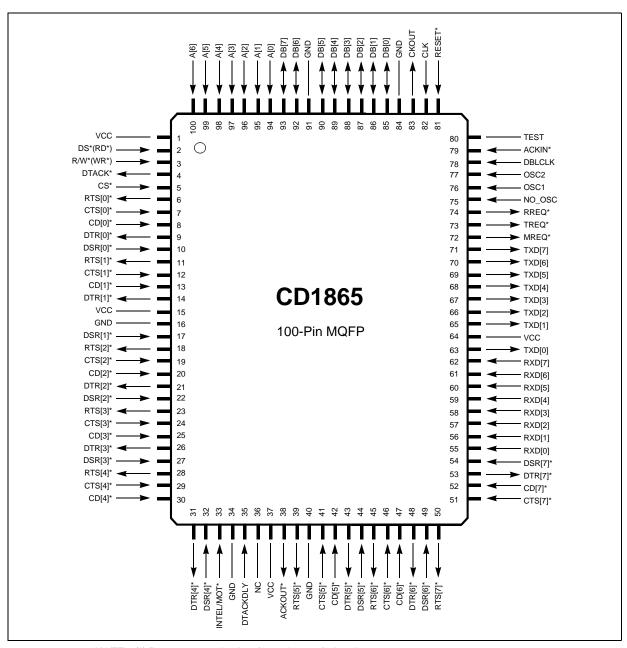

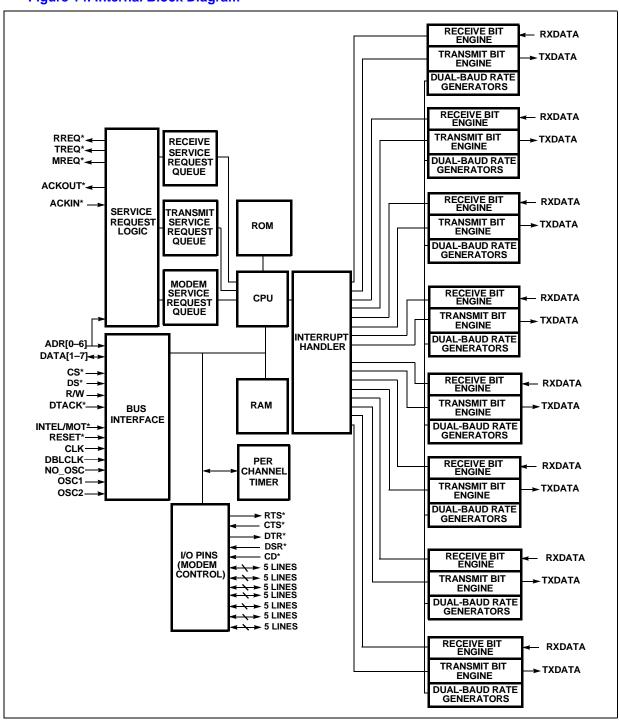

# 5.2 Internal Operation

The internal architecture of the CD1865 is shown in Figure 2. The foundation of the design is a custom-designed CPU that Intel has developed especially for this application. This CPU is optimized for bit-oriented tasks associated with UART functions, and it has a set of registers for each channel, arranged in a register window architecture. These registers and the ALU are eight bits wide. The CD1865 processor has a 16-bit instruction word that it retrieves from an on-device ROM. Every instruction is one-word long and executed in one-clock cycle.

Whenever an internal interrupt occurs (from a bit engine), the CD1865 processor automatically switches context to that channel's block of registers. No time is lost in saving any machine state. The CD1865 processor executes the instructions necessary to handle that bit (typically three to six instructions) and then returns to the context it was in prior to the internal interrupt. All internal interrupts are at the same priority level; the interrupt handler block ensures fair-share access across channels.

Each channel's serial interface logic consists of a receive-bit engine, a transmit-bit engine, a receive-baud-rate generator, a transmit-baud-rate generator, and a timer. The receive-bit engine samples the state of the RxD pin at the time indicated by the receive-baud-rate generator, and it reports this value to the CD1865 processor as an interrupt. The transmit-bit engine works in a similar manner. At the baud rate tick, it outputs the next bit and generates an interrupt to the CD1865 processor requesting the following bit.

The baud-rate generators are 16-bit dividers that operate from a master clock, which is the system clock divided by 16. All baud-rate generators are independent, so a channel can send and receive at any speed. In addition to the baud-rate generators, there are two channel timers for each channel. One is an 8-bit divider, operating off the master prescaler timer tick. This timer is used to time-out partially full FIFOs to avoid 'stale' data. The other is used to time embedded delays in the transmit data stream.

All eight channels are continuously scanned by internal logic that generates interrupts to the CD1865 processor in a 'fair' manner. This fair-share interrupt feature is the same as the mechanism used to share service requests across multiple devices. Whenever two or more channels are contending for interrupt service, the channel that is serviced first does not assert again until all other currently pending channels are serviced. This prevents a fast, 64-kbps channel from demanding service from a slow 1200-bps channel, yet it allows the faster channel the additional service it needs to support its higher speed. This allows more overall throughput than a 'round-robin' or an 'equal-access' method would provide.

Service requests for the host are handled by fast, dedicated logic on each of the three levels provided. Whenever the CD1865 processor detects a condition requiring external-host service, it queues the request with the service-request machine for that level. This machine asserts the External Request pin, and it monitors for a service acknowledgment of the same level. When a service acknowledgment is sensed, the machine automatically provides the vector to the host and sets up the internal context of the CD1865 for service. Upon completion of the service, the machine restores the normal context. The queue for service requests is two deep, so in a busy system there can be another request immediately pending when the first one is completed. This method avoids any delay between requests, and improves overall efficiency.

#### Intelligent Eight-Channel Communications Controller — CD1865

Modem I/O signals are implemented as 'conventional' input-output circuits, readable, and writable by either the on-device or the host CPU. This allows maximum flexibility in using these signals either in the conventional way, or for any other I/O function required. When the CD1865 processor is using these pins to implement flow-control functions, it reads them under software control and implements the function that way. There is no direct hardware association between the modem pins and the serial I/O hardware.

Figure 2. Internal Block Diagram

#### Intelligent Eight-Channel Communications Controller — CD1865

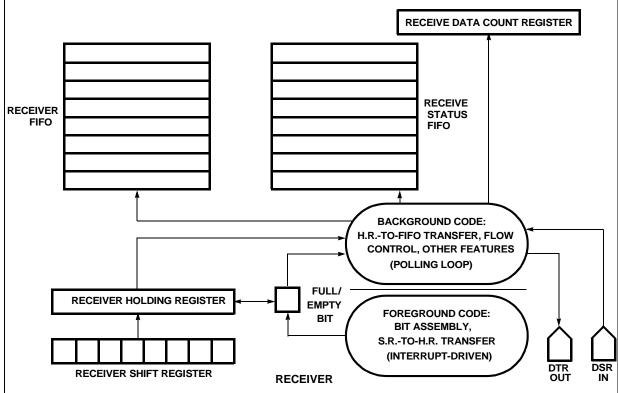

The CD1865 workload can be divided into two categories:

- Bit-to-character conversion (and vice versa) the 'traditional' UART function

- Character-level processing such as flow control, FIFO management, and host interface functions

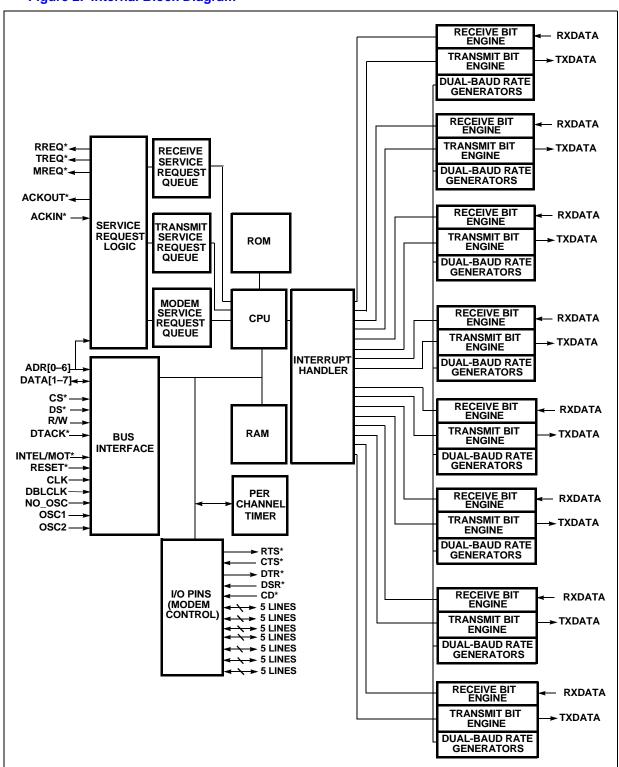

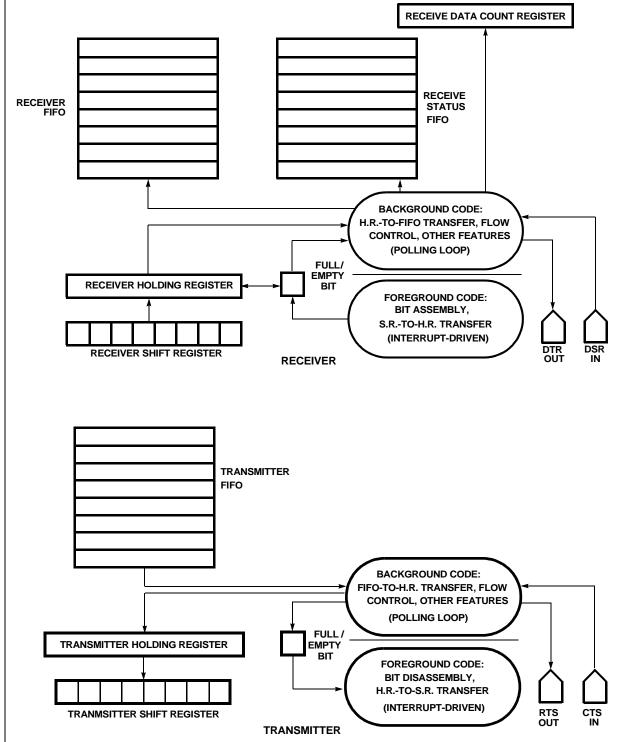

The CD1865 internal processor handles all these tasks in firmware. A foreground/background scheme is used: foreground for internal bit-engine interrupts and background for everything else. This internal structure represented in Figure 3 on page 24, shows how the foreground communicates with the background. Foreground code handles bit-to-character assembly for receive, and character-to-bit disassembly for transmit. In either case a Holding register, together with a Full/Empty bit, acts as the 'gateway' between the interrupt-driven foreground and the polling-loop background code.

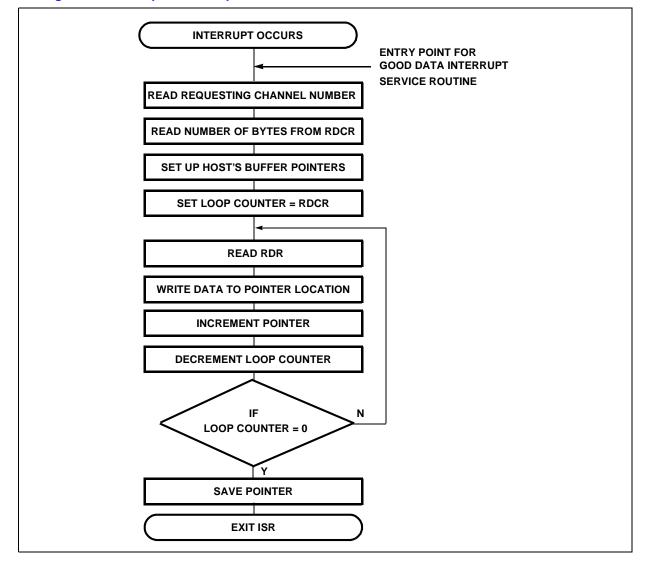

The background code executes the polling loop as shown in Figure 4. After power-on reset, the software runs continuously in an inner and an outer loop. Lower-priority tasks are handled in the outer loop, and higher-priority tasks are handled in the inner loop. The highest-priority tasks are bit events that are handled by foreground (that is, interrupt-driven) code.

The inner loop executes eight times as often as the outer loop. It checks each channel's Full/Empty bits to sense if another character needs to be moved. It first checks receive, and if there is a character to be moved, it is moved and execution moves on to the next channel. If receive data does not need processing, then transmit is checked. This mechanism gives a slightly higher priority to receive than to transmit, and is favorable because missing a receive character is a fatal error and being late in transmitting one is not an error. (The effect of this can be observed by programming the CD1865 for higher-than-rated serial baud rates and providing a source of receive traffic with virtually 100-percent loading. As the CD1865 is heavily loaded, it leaves short gaps between transmit characters because the firmware is following the 'receive' path through the code. Refer to Section 6.2.5 for details on maximum performance and maximum line speed).

After eight passes through the inner loop (for example, checking all eight channels for data), one pass is made through the outer loop. This pass checks one channel for host commands (such as 'Send Special Character'), timer functions, and a condition that requires posting an external service request (for example, Receive FIFO full, Transmit FIFO empty, modem signal change, and so on). If required, the firmware posts the service request within the queue of the appropriate service-request logic. It then continues normal operation, until the host responds to the service request. After a single pass through the outer loop, eight passes through the inner loop are again made.

In most cases the CD1865 checks the appropriate bit in RAM to determine which options are enabled and then modifies its processing accordingly. Some control bits must be interpreted and moved by the CD1865 firmware from their location in Option Bit registers to other locations in the device. Therefore, the host must notify the CD1865 when these bits are modified. Then, the CD1865 alters the channel as commanded. For details on channel command functions, refer to Section 7.2.

Figure 3. Foreground/Background Internal Structure

**POWER-ON** INITIALIZATION RESET FOR OUTER\_LOOP I = 1 TO 8 **HOST COMMAND PROCESSING GLOBAL** (SOFTWARE) RESET **TIMER FUNCTIONS** FOR INNER\_LOOP J = 1 TO 8 PROCESS RECEIVE CHAR.; RCV\_HLD\_REG **CHECK ALL SPECIAL FEATURES; PLACE IN FIFO** = FULL Ν PROCESS TRANSMIT CHAR.; XMT\_HLD\_REG **CHECK ALL SPECIAL FEATURES: FETCH FROM FIFO** = EMPTY N PROCESS RECEIVE **INTERRUPT RECEIVE SERVICE REQUEST SCANNING** TRANSMIT SERVICE **REQUEST SCANNING** MODEM SERVICE **REQUEST SCANNING**

Figure 4. Internal Operation Flow Chart

# 5.3 Service Request and Interrupt Operation

The CD1865 enhances design efficiency, because it is an intelligent device that more closely resembles an add-in controller board than a mere collection of TTL. Conventional UARTs are basically passive, 'dumb' logic. For example, when polling a device for channels requiring service, each channel is not individually tested. Because of this, certain restrictions are placed on when and how FIFOs are accessed. The CD1865 processor must determine what the host is doing, and when to manage the queue of events correctly and efficiently.

#### **Interrupt-Driven Versus Polled**

Choosing the software interface, interrupt-driven versus polled, is critical to overall system performance. This choice also affects how the software is written. In hardware implementation, a programmer has a choice of Mixed mode, that is, when to poll versus when to be interrupt-driven. Mixed-mode operation allows a programmer to optimize the efficiency of the system according to changing needs. The advantages of each method are discussed in Section 5.5.

# **5.3.1** Theory of Operation

The CD1865 has three independent service request levels, one for each of the three categories — Receive, Transmit, and Modem signal change. The priority of these lines is not fixed, but can be determined in one of the following three ways:

- It can be set within the CD1865 by the AutoPriority Option bits.

- A system designer can assign priorities by the manner in which the three service request lines are connected to the host interrupt controller.

- Under software control, the host system can define and redefine the order of service requests.

The Service Request interface to the host is implemented with five signals — \*, \*, \*, ACKIN\*, and ACKOUT\*. \*, \*, and \* are asserted when a service request is pending; ACKIN\* is asserted during service-acknowledgment cycles; and ACKOUT\* is used in multiple CD1865 designs to share service requests and daisy-chain acknowledgments.

Whenever the CD1865 processor determines that one or more channels need service from the host, it loads the appropriate service-request state machine with the information about the type of request. The service-request state machine for that level then asserts its request signal. Note that all three request signals can be active at the same time. At this point, the CD1865 has not determined which request should be handled first — it simply asserts any and all lines, as required by the status of various channels. (This is true even if the AutoPri Option is enabled; AutoPri takes effect when a service request is acknowledged, and at that time the CD1865 determines which is the most important request.)

The host, after noticing that one or more of the three service request pins are active — either because the host is interrupted or it polled an external or internal CD1865 status register — decides which of the requests (if more than one is active) it services first. The host begins the service operation by issuing a Service Acknowledge cycle. The purpose of this cycle is to cause the CD1865 to set up its internal state for that type of request. (Note that if AutoPri is set, it is not necessary for the host determine which level of service request to acknowledge; it simply acknowledges the CD1865 request and the CD1865 returns the vector for the highest-priority active request.)

#### Intelligent Eight-Channel Communications Controller — CD1865

If AutoPri is not being used, the CD1865 needs to be informed which one of the three possible pending requests the host wants to acknowledge. There are two different ways CD1865 can be informed of this — hardware and software.

The hardware method is based on the value in the address bus. The CD1865 determines the type of request being acknowledged by the value placed in the address bus during the acknowledge cycle. This is the method used by Motorola®-family processors. The host places the level of interrupt being serviced on the low-order address bits during an interrupt acknowledgment cycle. When the host performs a Service Acknowledge cycle, the CD1865 compares the value on the address bus with the three unique values stored in three internal registers — the . These values are set by the user at system initialization. A match occurs on only one of these registers, and this informs the CD1865 of the type of request being acknowledged.

In most circumstances the address bus should not have a value that does not match one of the three values during an acknowledgment cycle. This causes the CD1865 to not recognize that any bus cycle is occurring, and it does not assert DTACK\*, or terminate the cycle, or take any other action. Doing this does not affect the CD1865, but the system must have some other provision to terminate the bus cycle. If, for example, the CD1865 shares an interrupt level with another device, different values on the address bus should be used to control responses to an acknowledgment, but the bus cycle should terminate in a usable way.

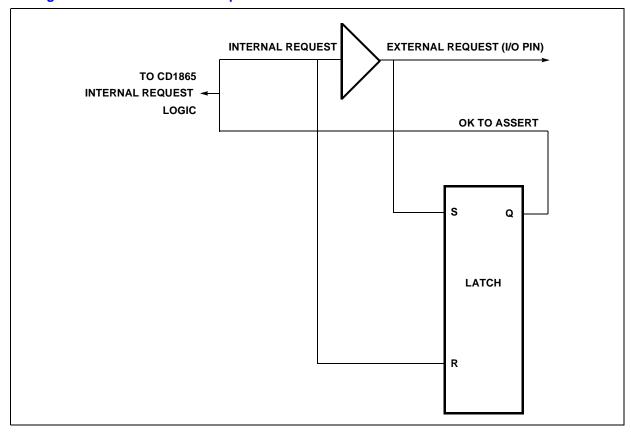

Service acknowledgments can also be performed by software. The host simply reads one of three Request Acknowledge registers, and the CD1865 performs as if a hardware service acknowledge cycle is executed.

Regardless of the method of acknowledgment used, within the CD1865, each service request state machine makes the following determination: if it has an internal service request pending, and there is a service acknowledge of the same type, it asserts its internal-acknowledge-accepted signal back to the Service Request Controller logic, negates the Service Request Output pin, and holds its acknowledge-out daisy chain in a negated state. It also drives the value in the Global Vector register (GVR) onto the data bus, for the host to read as part of the Service Acknowledge cycle. The GVR value placed on the bus during the Service Acknowledge cycle serves two purposes. The least-significant three bits of GVR indicate which of the four types of service requests are occurring. The upper-five bits are user-defined and serve to identify, in daisy-chained CD1865 systems, which of the multiple CD1865s is active.

If the service request state machine does not have a service request pending, and there is a software acknowledgment or address bus match, it passes the service acknowledgment down the chain by asserting ACKOUT\*. If there is no match, the state machine remains idle.

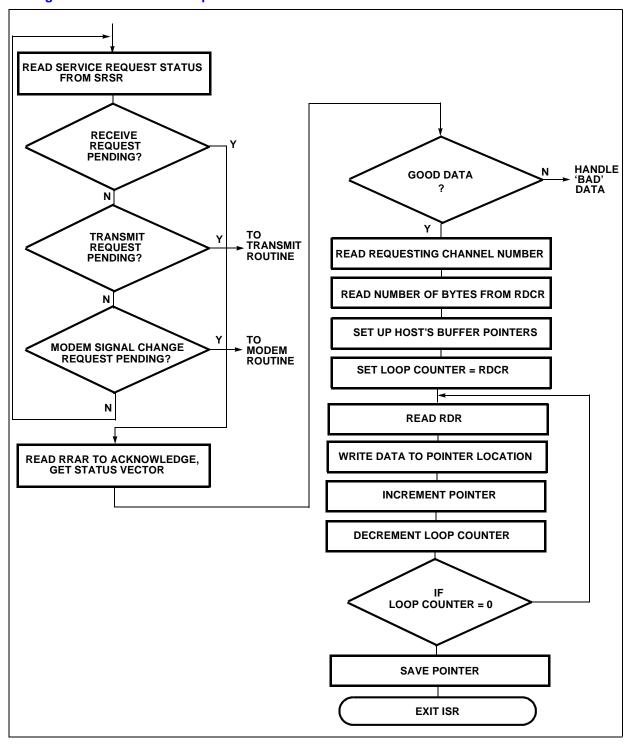

If a service request is pending and the Receive Service Request is to be handled, the CD1865 is notified because the three have different values in them; therefore, only one match (receive service, in this case) occurred. The internal grant from the service request state machine causes the receive service type code and active channel number (previously stored at the time the request is posted by the CD1865 processor) to be pushed onto the service request stack. This automatically causes the FIFO pointers to be set up for the active channel, with no host intervention.

The host, at this point, has all the information needed to handle the service request. It determines the exact type of service being requested (Transmit, Receive Good Data, Receive Exception, or Modem signal change) and which of the multiple CD1865s is requesting service. It gets the channel number by reading the Global Channel register (GCR) and then proceeds to service the request. At the completion of the service, the host performs a dummy write to the CD1865 End Of register (), that causes the CD1865 to exit its internal service request state by popping the service

request stack. At this time the CD1865 is ready to be serviced on another of its outstanding requests. If another request of the same level is pending, two clock periods after the write to are required for the CD1865 to reassert the request line.

Because the CD1865 has a service request stack, it can support nested-service requests. For example, the host can be in middle of a Transmit Service Request, detect that Receive Service Request has asserted, process the Receive Service Request, and after exiting the receive service routine, resume the Transmit Service Request. The CD1865 stack is three deep, so all three types (one of each) can be nested if required. The current service request context (for example, the stack) is readable in the Service Request Status register.

The Global Channel registers (GCR) are actually three registers that provide the number of the channel requesting service. Reading any of these registers causes the CD1865 to mask in three bits, specifying the channel number of the currently active channel. Normally these registers are read by the host when it is handling a service request. In this case, the three bits are the number of the channel requesting service. If any of the three GCR registers are read when the CD1865 is not in a service-request context, the three bits are the current value in the CAR. The current channel number is masked into the contents of bits 4:2 of this register by the CD1865 when it is read by the host. The actual contents of the register are not modified.

These three registers are provided as a convenience to the user. In most applications, the user only uses one of these locations, and set the register to some arbitrary value. However, it may be useful to record information about the state of the CD1865 (or the software driving it) that is associated with each of the three service-request types. In this case, the user can store whatever information is required in the unused bits. Then, when entering a service routine, the software can check these bits to find what state they were left in, and this could be used as a 'sub-vector'.

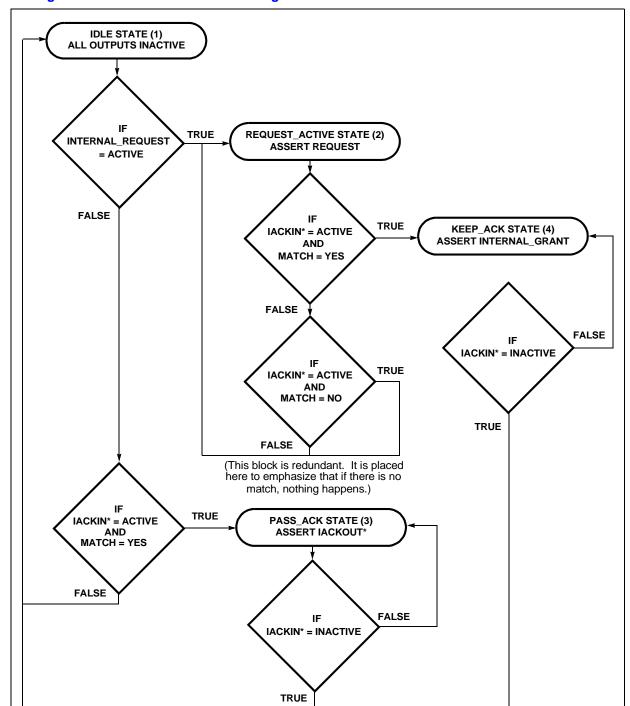

#### 5.3.2 Internal Implementation of the Service Request Logic

As discussed above, the heart of each service request level is an asynchronous state machine. This state machine has three inputs:

- MATCH from the Priority Interrupt Level register comparator,

- ACKIN\* from the host system, and

- INTERNAL\_REQUEST from the CD1865.

**Note:** Software acknowledgments (reads from the Service Request Acknowledge registers), in effect, force the MATCH value true for their respective level.

It also has three outputs:

- Svc\_Req to the host system,

- INTERNAL\_GRANT to the CD1865, and

- ACKOUT\*, which is combined with the other two ACKOUT\* signals to provide ACKOUT\* to the next CD1865 in the daisy chain.

Figure 5 on page 30 shows logic implemented by the state machine, which is described in Table 3.

Table 3. State Machine Logic

| State Name                                                            | Output Condition                                                | Comments                                                                                          |

|-----------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| IDLE IF (INTERNAL_REQUEST = 1) ELSE IF (ACKIN* = 1 & MATCH =1) ELSE   | all outputs inactive GoTo REQ_ACTIVE GoTo PASS_ACK Stay at IDLE | ; normal 'resting' state<br>; pass this acknowledge<br>; wait here                                |

| REQ_ACTIVE IF (ACKIN* = 1 & MATCH =1) IF (ACKIN* = 1 & MATCH =0) ELSE | GoTo KEEP_ACK Stay at REQ_ACTIVE Stay at REQ_ACTIVE             | request asserted ; keep this acknowledge ; wait here, ACK is for some other level (†) ; wait here |

| PASS_ACK IF (ACKIN* = 0) ELSE                                         | GoTo IDLE<br>Stay at PASS_ACK                                   | ACKOUT* asserted ; return when ACKIN* is gone ; wait here while ACKIN* active                     |

| KEEP_ACK IF (ACKIN* = 0) ELSE                                         | GoTo IDLE<br>Stay at KEEP_ACK                                   | INTERNAL_GRANT asserted ; return when ACKIN* is gone ; wait here while ACKIN* active              |

NOTE: The (†) denotes the point at which, if there is no match, the CD1865 determines *not* to pass the ACK down the daisy chain. It does this for two reasons: first, it is unacceptable to have the ACKOUT\* 'glitch' low; and second, the state machine should be as fast as possible. When the state machine senses an ACKIN\* and match is not valid, it cannot conclude that it should assert ACKOUT\*; the ACKIN\* may be for one of the other two service requests levels. It could wait for the results of the other two MATCH comparators; however, this complicates, and therefore slows down, the response of the state machine.

The reason this complication causes delay is (to implement the logical function 'assert ACKOUT\* if no match') it must determine how long to wait before declaring a no-match condition. To implement this delay function, a synchronous state machine is required, which at a 15-MHz clock, means a delay of several hundred nanoseconds from ACKIN\* to ACKOUT\*, instead of the 65 ns currently specified.

Figure 5. Internal Service Acknowledge Decision Tree

#### 5.3.3 Priorities and Fair Share

The CD1865 implements a fair-share mechanism to ensure that all channels receive equal service, without any 'data starvation'. Fair share works automatically among the channels in one device and across multiple devices.

Figure 6 on page 31 shows a fair-share operational block diagram. On each of the three service request lines, the CD1865 monitors both the internal and external value of the line. (The external value can differ because, in multiple CD1865 applications, it can be driven by other CD1865s.) At the end of a service acknowledgment bus cycle, the CD1865 checks the state of both request values. If they are different, the CD1865 determines that there is another part also driving the request line, and it does not reassert its own request line until the external request has gone inactive. This inactive level means every other CD1865 with a pending request is serviced; therefore, it is now okay to reassert requests without controlling host bandwidth.

Figure 6. Internal Fair-Share Operation

# 5.4 Types of Service Requests

The categories of service requests that a CD1865 can generate are explained below. Each channel's transmitter, receiver, and modem pins require service from the host occasionally; however, each category of service request conditions can tolerate different latencies in being serviced. Conditions for service requests fall into three basic categories:

• Data is received from the remote device and needs to be transferred to the host.

- Data from the host can be given to the Transmitter FIFO, which is now empty.

- A modem signal changes state.

Three separate service request levels are provided to support the following three categories:

| Source              | Pin Name | Request Match<br>Register Name |

|---------------------|----------|--------------------------------|

| Receive data        | *        |                                |

| Transmit data       | *        |                                |

| Modem signal change | *        |                                |

# 5.4.1 Receive Service Requests

The Receive Service Request is unique because it has two subtypes; that is, it is capable of returning one of the two different vectors during a service request acknowledge cycle. The two sub-types are — 'Receive Good Data' and 'Receive Exception'. The reason there are two types within one category of service request is that, while Good Data and Exceptions require different handling, they are both of equal priority, and need to be serviced in the order they are received. For example, suppose two good characters are received, then an exception character, and then another good character is received. There must be a service request for the first 2 bytes of Good Data, then for the Exception, and then for more Good Data. If Exception Service Request is at a different level, the exception character is processed either before or after the Good Data, and not in sequence as it should be. This method also allows the Receive Good Data-handling routine in the host to be very fast and efficient, since it only has to move 'N' bytes to a buffer. All special-case conditions can be put in a separate handler, where they do not slow down normal data transfers.

Exception characters are characters with errors or that match the defined special characters, line breaks, and certain time-out conditions.

Data must *not* be read from the Receive FIFO or the Receive Status FIFO except when the CD1865 is within the context of a Receive Data Service Request.

#### 5.4.1.1 Receive Good Data™

A Receive Good Data Service Request is asserted for any of the following three conditions:

- 1. RxFIFO threshold reached, and the FIFO contains Good Data.

- 2. RxFIFO threshold not reached, but the FIFO contains Good Data, and the Receive Data Timer times-out.

- 3. RxFIFO threshold not reached, but the FIFO contains Good Data, and the newly arrived data contains an exception condition.

When any of these conditions occur, the modified service request vector indicates to the host that the service request is for Good Data. The CD1865 continues to add bytes to the FIFO, and it increments the Count register for each good byte added, and this allows for optimally efficient use of the FIFO.

It is not necessary to accept any or all of the Good Data that is available when a Good Data Interrupt is received. If a host buffer is too full to accept 8 bytes, a smaller number (even 0) can be read, the service request context left, and the host buffer handled first. The CD1865 again generates another Good Data Service Request when any of the three conditions listed above are met.

#### Intelligent Eight-Channel Communications Controller — CD1865

If the condition that caused the request in the first place remains true, the CD1865 quickly generates another service request. If no data is read, this is always the case. If some, but not all, of the available data is read, Conditions 1 and 2 are not true, but Condition 3 may be true if an exception condition is the cause of the Good Data Interrupt. If this becomes a problem, one solution is to temporarily disable receiving interrupts on that channel. To avoid FIFO overflow, do not disable the channel for very long.

#### 5.4.1.2 Receive Exception

Unusual or exception conditions are reported to the host one character at a time through the Receive Exception Service Request. As with normal receive processing, the host determines the requesting channel by reading the GCR. It can then determine the specific exception(s) by reading the Receive Character Status register.

Exception conditions are generated for parity errors, framing errors, FIFO overrun, special character recognition, break detect, and for a special feature called the 'No New Data Timer' (NNDT).

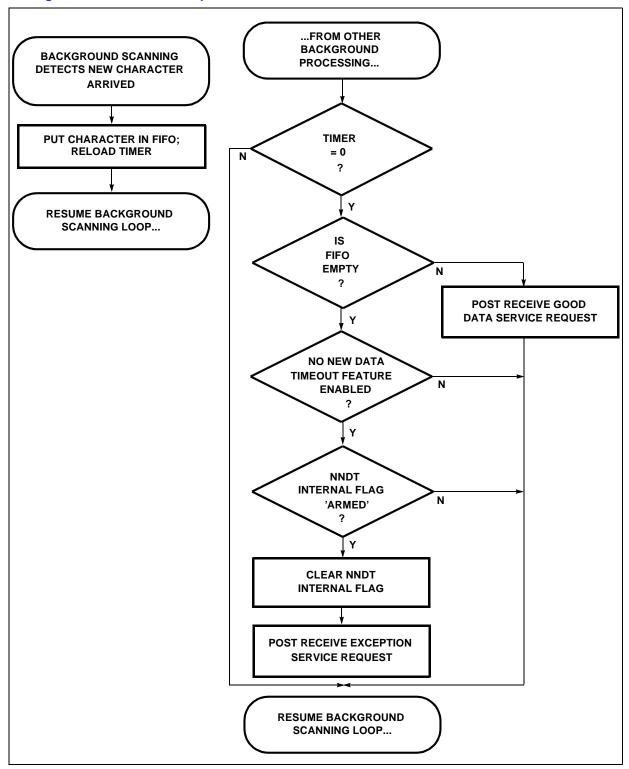

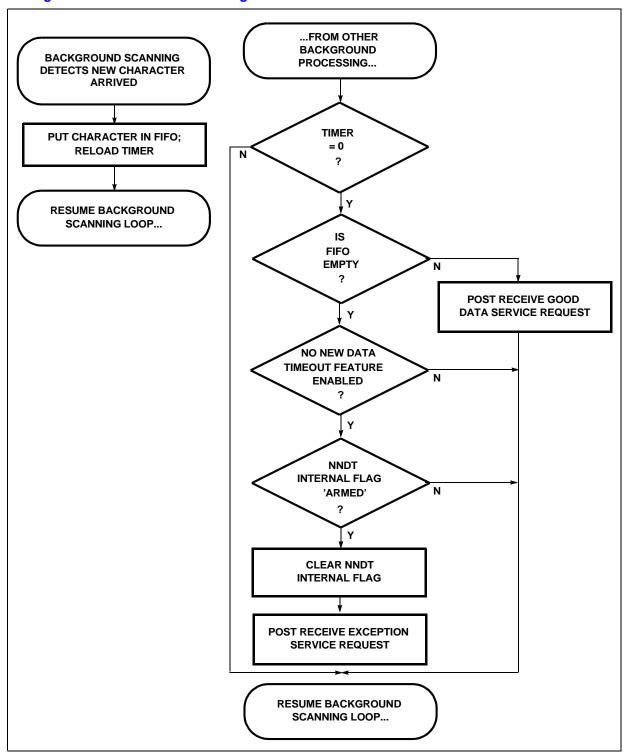

NNDT is a receive timer option to generate a service request for the first receive data time-out following the transfer of all data from the FIFO to the host. It is often useful, when managing relatively large I/O buffers, for an I/O processor to determine that 'no data has arrived lately'. This event is used to transfer the contents of the local buffer that has been storing data from the CD1865 FIFO for host-system processing.

This service request is a receive exception sub-type, and can be used to signal that it is time to transfer the buffer. This feature can be enabled or disabled by controlling the NNDT bit in the Service Request Enable register. As shown in Figure 7, every time a received character is loaded into the FIFO, the timer is restarted. If the timer times-out, the CD1865 checks if there is any data in the FIFO. If there is, a Good Data Service Request is posted to avoid 'stale data'. If there is no data in the FIFO, the CD1865 checks that NNDT is enabled and 'armed'. Arming occurs when the last character is transferred out of the FIFO to the host. If NNDT is on and armed, a Receive Exception Service Request is posted to inform the host of this event. Note that the NNDT is not armed if the last character removed from the FIFO is an exception character.

Every Receive Exception is a unique, one-character event. The Receive Data Count register has no meaning, unlike the Receive Good Data case, the Status byte in the receive exception handling routine must be read. The Receive Data Count register and the associated data character is discarded by the CD1865 at the end of the service routine. The Status byte must be read before reading the Data byte. Once the Data register is read, the Status byte is no longer available.

Figure 7. Receive Timer Operation

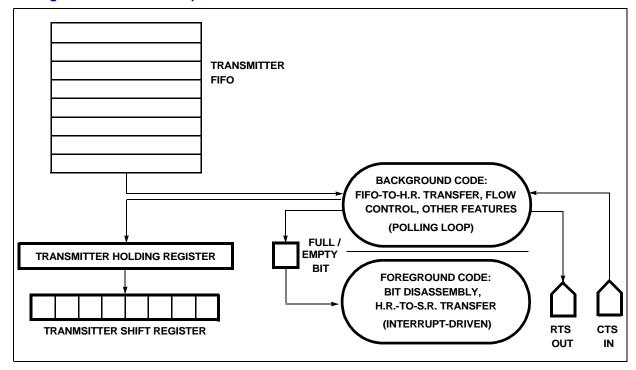

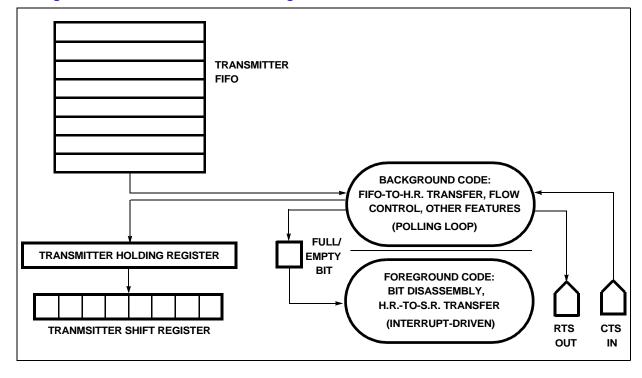

## 5.4.2 Transmit Service Requests

Each transmitter contains 8 bytes of Transmit FIFO in addition to the Transmit Holding register and the Transmit Shift register. As data is being transmitted, the FIFO status is being monitored by the CD1865. A service request is invoked for one of the following conditions:

- Transmit FIFO Empty When the Transmit FIFO is empty, there is still one character in the Transmit Holding register and one character in the Transmit Shift register. The host has two character times to respond to this request without causing a gap in the Transmit Data Stream.

- Transmitter Empty The Transmit FIFO, Transmit Holding register, and the Transmit Shift registers are now empty. This signifies that all characters written to the FIFO are completely transmitted.

The host can select which one of these causes a Transmit Service Request, and it is used by programming the options in the Service Request Enable register (SRER).

Data must *not* be put into the Transmit FIFO at any time other than when the CD1865 is in a Transmit Service Request context for that channel. During a transmit service, characters (up to eight) are placed into the FIFO by the Transmit Data register (TDR).

# 5.4.3 Modem Signal Change Service Requests

The CD1865 can be programmed to assert a service request when a channel's modem input signals has changed states. The change-detect options are programmed in the Modem Change Option registers. Individual modem pin service requests are enabled by setting the corresponding bits in the Service Request Enable register.

The host must read the Modem Change register during a modem change service to determine which modem signal changes were detected. This is indicated by a '1' in the appropriate bit location. The Modem Change register must be reset to a '0' by the host before exiting the service request because the CD1865 does not do this. Refer to Section 7.4 for more details.

#### 5.4.3.1 Using Modem Pins as Input/Output

The pins labelled as modem pins are general-purpose I/O pins that can be controlled by either the CD1865 processor or the host system. There is no direct, hardwired connection from any modem pin directly to a transmitter or a receiver. This means that these pins can be used for general-purpose I/O if they are not needed for modem-control purposes. See Section 7.4 for more details.

# 5.5 Implementing Service Requests