# 1.2 W High Efficiency Power Amplifier 800 - 960 MHz

AM52-0001

#### **Features**

- SOIC-8 Thermally Efficient Plastic Package

- +30.8 dBm Typical Power Out

- Greater than 50% Typical Power Added Efficiency

- 21 dB typical Power Gain

- Flexible External Output Matching

#### Description

M/A-COM's AM52-0001 is a GaAs power amplifier in a thermally efficient low cost SOIC-8 plastic package. The AM52-0001 is designed for high efficiency 1.2 W output power and 21 dB of associated gain in the 800-960 MHz frequency band. The AM52-0001 is unconditionally stable in both small and large signal operation. It features flexible biasing for improved dynamic range and off-chip matching for improved efficiency and flexibility.

The AM52-0001 is specifically designed for high efficiency final output power amplification in FM, GFSK and FSK type systems, such as AMPS, ETACS, NTACS, CT1, CDPD and ISM.

M/A-COM's AM52-0001 is fabricated using a mature 0.5 micron gate length GaAs MESFET power process. The process features full passivation for increased performance and reliability. The AM52-0001 can be used with standard automated SMT assembly equipment (See M/A-COM application note M558).

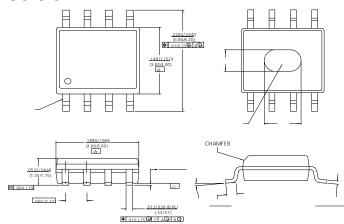

#### SOIC-8P

## **Ordering Information**

| Part Number Package |                         |

|---------------------|-------------------------|

| AM52-0001           | SOIC-8 Lead Plastic     |

| AM52-0001TR         | Forward Tape and Reel * |

| AM52-0001SMB        | Designer's Kit          |

<sup>\*</sup> If specific reel size is required, consult factory for part number assignment.

## Electrical Specifications: $V_{D1} = V_{D2} = 4.8V \pm 5\%$ , $T_A = +25$ °C, Freq. = 824-849 MHz, $V_{GG} = V_{G2} = V_{G1}$ adjusted for 150 mA quiescent drain Current.

| Parameter                      | Test Conditions                               | Units | Min. | Тур. | Max. |

|--------------------------------|-----------------------------------------------|-------|------|------|------|

| Linear Gain                    | Pin ≤ -20 dBm                                 | dB    |      | 29   |      |

| Output Power                   | Pin = 10 dBm                                  | dBm   |      | 30.8 |      |

| Power Gain                     |                                               | dB    |      | 21   |      |

| Power Added Efficiency         |                                               | %     |      | 55   |      |

| Second Harmonic                |                                               | dBc   |      | -30  |      |

| Third Harmonic                 |                                               | dBc   |      | -50  |      |

| Noise Power <sup>1</sup>       |                                               | dBm   |      | -92  |      |

| Stability <sup>2</sup>         |                                               | VSWR  |      |      | 10:1 |

| Load Mismatch <sup>3</sup>     |                                               | VSWR  |      |      | 10:1 |

| Gate Current                   |                                               | mA    |      |      | 5    |

| Adjustable Power Control (APC) | $V_{D1} = 0 \rightarrow 4.8 V V_{D2} = 4.8 V$ | dB    |      | 27   |      |

<sup>1.</sup> Noise power (30 KHz RBW), 45 MHz above T<sub>X</sub> Freq range, measured under rated output power conditions.

Specifications Subject to Change Without Notice.

Parasitic Oscillation defined as any spurious output less than 60 dBc with respect to desired signal level. Measured with nominal Pin and an output VSWR of 10:1 any phase, V<sub>DD</sub> = 4.8 V.

<sup>3.</sup> No permanent degradation with nominal Pin and an output VSWR of 10:1 at any phase (360° rotation in 10 sec.) with V<sub>DD</sub> up to 6V.

## **Absolute Maximum Ratings** <sup>1</sup>

| Parameter                         | Absolute Maximum              |

|-----------------------------------|-------------------------------|

| Input Power <sup>2</sup>          | +23 dBm                       |

| Operating Voltage <sup>2</sup>    | $V_{DD} = + 10 \text{ Volts}$ |

|                                   | $V_{GG} = -6 \text{ Volts}$   |

| Junction Temperature <sup>3</sup> | +150 °C                       |

| Storage Temperature               | -65 °C to +150 °C             |

| Operating Temperature             | -40 °C to +85 °C              |

- 1. Exceeding any one or combination of these limits may cause permanent damage.

- 2. Ambient Temperature  $(T_A) = +25^{\circ}C$

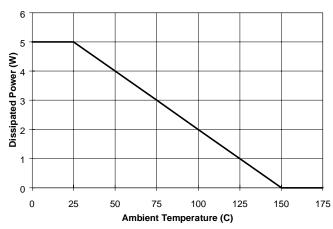

- 3. See temperature derating curve.

## **Pin Configuration**

| Pin No. | Pin Name | Description                           |  |

|---------|----------|---------------------------------------|--|

| 1       | $V_{G1}$ | Negative supply voltage, First stage  |  |

| 2       | RF IN    | RF Input of the amplifier             |  |

| 3       | GND      | DC and RF Ground                      |  |

| 4       | $V_{D1}$ | Positive supply voltage, First stage  |  |

| 5       | $V_{G2}$ | Negative supply voltage, First stage  |  |

| 6       | GND      | DC and RF Ground                      |  |

| 7       | RF OUT   | RF Output of the amplifier            |  |

| 8       | $V_{D2}$ | Positive supply voltage, Second stage |  |

| 9       | Puck     | DC and RF Ground                      |  |

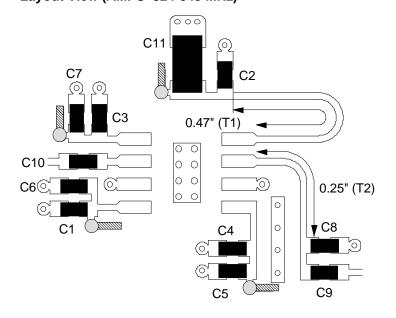

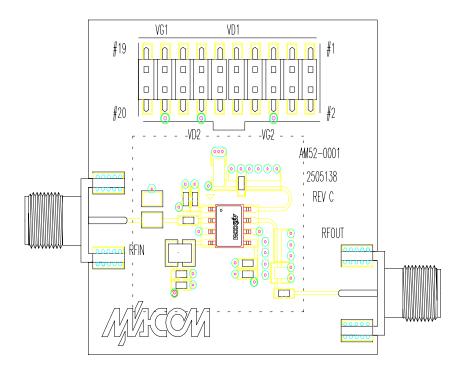

## **Recommended PCB Configuration** Layout View (AMPS 824-849 MHz)

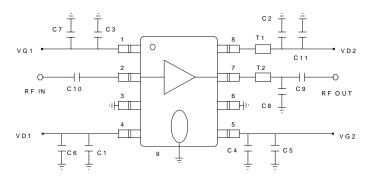

## **Functional Block Diagram** (AMPS 824-849 MHz)

## **External Circuitry Parts List** (AMPS 824-849 MHz)

| Part    | Value  | Purpose               |  |

|---------|--------|-----------------------|--|

| C1 - C3 | 220 pF | By-Pass               |  |

| C4 - C7 | 0.1 uF | By-Pass               |  |

| C8      | 8 pF   | Power Tuning          |  |

| C9, C10 | 56 pF  | DC Block              |  |

| C11     | 1.0 uF | By-Pass               |  |

| T1      | 0.470" | Matching Transmission |  |

| T2      | 0.250" | Lines $(50 \Omega)$   |  |

- 1.) The recommended layout is specifically for the AMPS application. It shows EIA code size 0603 standard SMT capacitors with the exception of C11 which is a EIA code size 3528

- 2.) The location of C9, C10 and C11 is not critical to the performance of the amplifier.

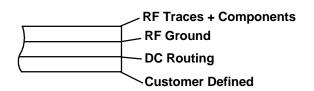

#### **Cross Section View**

The PCB dielectric between RF traces and RF ground layers should be chosen to reduce RF discontinuities between 50  $\Omega$  lines and package pins. M/A-COM recommends an FR-4 dielectric thickness of 0.008"(0.2 mm) yielding a 50  $\Omega$  line width of 0.015"(0.38 mm). The recommended metalization thickness is 1 oz. copper and ground metalization thickness is 2 oz.. Shaded traces are vias to DC Routing layer and traces on DC Routing layer.

#### **Biasing Procedure**

The AM52-0001 requires that V<sub>GG</sub> bias be applied prior to ANY V<sub>DD</sub> bias. Permanent damage will occur if this procedure is not followed. All FETs in the PA will draw IDSS and damage internal circuitry. Resistance added in seiries with  $V_{g1}$  and  $V_{g2}$  may degrade performance.

Specifications Subject to Change Without Notice.

M/A-COM Inc.

2

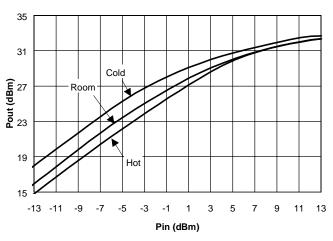

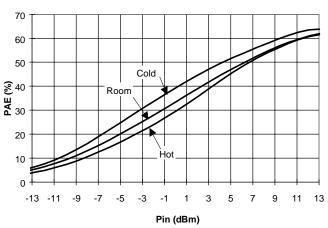

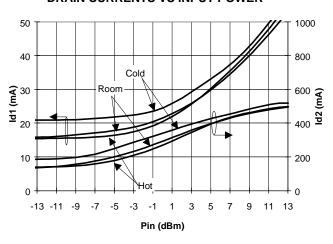

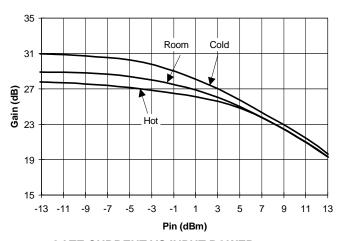

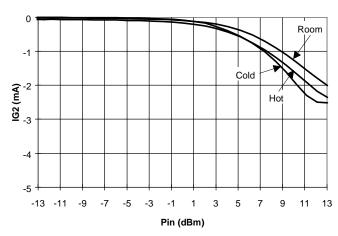

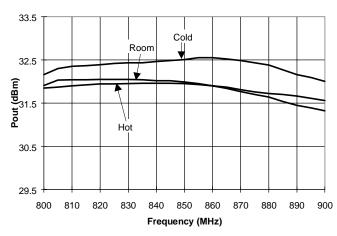

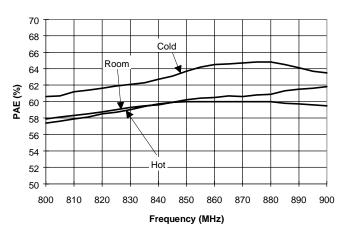

## Typical Power Data (AMPS 824 - 849 MHz)

Test Conditions (unless otherwise noted):  $T_{Room} = +25$ °C,  $T_{Cold} = -40$ °C,  $T_{Hot} = +85$ °C,  $T_{Ho$ V<sub>GG</sub> = V<sub>G1</sub> = V<sub>G2</sub> adjusted for 150 mA total quiescent drain current. External output matching circuitry is optimized for the 824 - 849 MHz AMPS application.

#### **OUTPUT POWER VS INPUT POWER**

#### **PAE VS INPUT POWER**

### **DRAIN CURRENTS VS INPUT POWER**

#### **GAIN VS INPUT POWER**

#### **GATE CURRENT VS INPUT POWER**

## **OUTPUT POWER VS FREQUENCY**

Specifications Subject to Change Without Notice.

M/A-COM Inc. North America:

Tel. (800) 366-2266 Fax (800) 618-8883

Asia/Pacific: Tel. +81 3 3226-8761 Fax +81 3 3226-8769

Europe:

Tel. +44 (1344) 869-595 Fax +44 (1344) 300 020

3

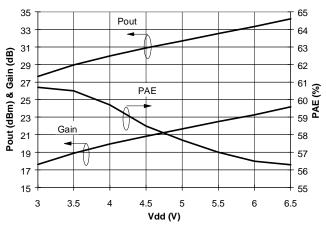

## Typical Power Data cont'd

#### PAE VS FREQUENCY

#### OUTPUT POWER, GAIN, AND PAE VS $V_{\text{DD}}$

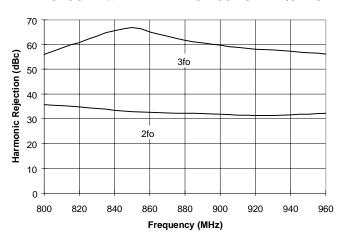

#### **SECOND & THIRD HARMONICS VS FREQUENCY**

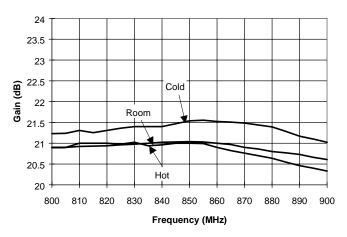

#### **GAIN VS FREQUENCY**

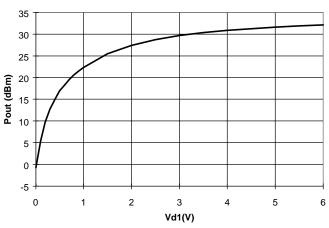

#### **OUTPUT CONTROL POWER**

#### **TEMPERATURE DERATING CURVE**

Note: Dissipated power in the above curve refers to power dissipated in output FET and is defined as (Pdiss=Vdd\*Id2-Pout). Typical Thermal Resistance ( $\theta$ jc) = 25°C/W.

Specifications Subject to Change Without Notice.

M/A-COM Inc.

\/1 00

## Designer's Kit AM52-0001SMB

The AM52-0001SMB Designer's Kit allows for immediate evaluation of M/A-COM's AM52-0001. The evaluation board consists of an AM52-0001, recommended external surface mount circuitry, RF connectors, and a DC multi-pin connector, all mounted to a multi-layer FR-4 PCB. Other items included in the Designer's Kit, a floppy disk (with typical performance data and a DXF file of

the recommended PCB layout) and any additional Application Notes. The AM52-0001SMB evaluation PCB is illustrated below with all functional ports labeled.

**AMPLIFIER PCB**

#### **DC Connector Pinout**

| PCB DC    | Function | Device Pin   | PCB DC    | Function | Device Pin   |

|-----------|----------|--------------|-----------|----------|--------------|

| Connector |          | Number       | Connector |          | Number       |

| 1         | GND      | 6 & 9 (Puck) | 11        |          |              |

| 2         |          |              | 12        |          |              |

| 3         |          |              | 13        |          |              |

| 4         |          |              | 14        | VD2      | 8            |

| 5         |          |              | 15        |          |              |

| 6         | VG2      | 5            | 16        |          |              |

| 7         |          |              | 17        | VG1      | 1            |

| 8         |          |              | 18        |          |              |

| 9         | VD1      | 4            | 19        | GND      | 6 & 9 (Puck) |

| 10        |          |              | 20        |          |              |

Specifications Subject to Change Without Notice.

5

1/4 00

#### **Designer's Kit Biasing Procedure**

In order to prevent transients which may damage the MMIC, please adhere to the following procedure.

Turn on all power supplies and set all voltages to 0 volts BEFORE connecting the power supplies to the DC connector.

Apply a -5.0 volt supply to DC connector pin 17 (V<sub>G1</sub>)

Apply a -5.0 volt supply to DC connector pin 6 (V<sub>G2</sub>)

Apply a +5.0 volt supply to the DC connector pin 9 ( $V_{D1}$ )

Apply a +5.0 volt supply to the DC connector pin 14 ( $V_{D2}$ )

Adjust all V<sub>GG</sub> supplies to -5 volts

Adjust all V<sub>DD</sub> supplies to +4.8 volts

Adjust  $V_{GG} = V_{G1} = V_{G2}$  supply for desired  $V_{DD}$  quiescent current (typically 150 mA)

To power off, reverse above procedure

- 1) Set  $V_{D1}$  &  $V_{D2}$  to 0 volts

- 2) Set  $V_{G1} & V_{G2}$  to 0 volts

- 3) Disconnect bias lines from DC connector

- 4) Turn off power supplies

#### **Evaluation PCB + RF Connector Losses**

| Port Reference | Loss (dB) |  |

|----------------|-----------|--|

| PA IN          | 0.1       |  |

| PA OUT         | 0.1       |  |

The DC connector on the Designer's Kit PCB allows convenient DC line access. This is accomplished by one or more of the following methods:

- 1. A mating female multi-pin connector (Newark Electronics Stock # 46F-4658, not included)

- 2. Wires soldered to the necessary pins (not included)

- 3. Clip leads (not included)

- 4. A combination of clip leads or wires and jumpers (jumpers included as required).

Specifications Subject to Change Without Notice.

M/A-COM Inc.

6

Fax +81 3 3226-8769