# AZ DISPLAYS, INC.

COMPLETE LCD SOLUTIONS

# SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY

PART NUMBER:

AGM1064B Series

**REVISED**:

MAY 14, 2003

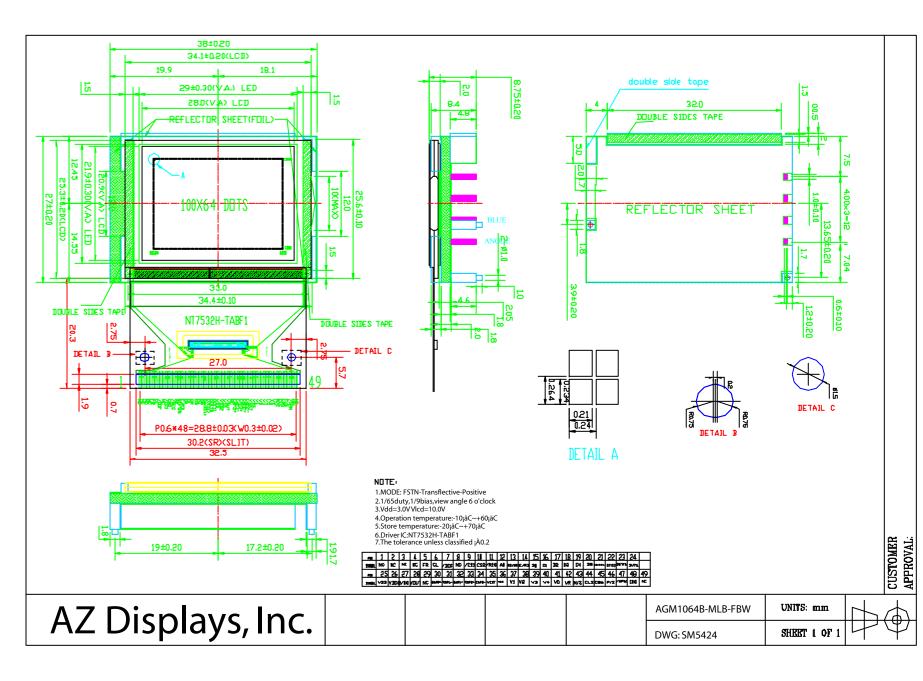

# **General Specification**

Table 1

| -                     |                                                                             |      |

|-----------------------|-----------------------------------------------------------------------------|------|

| Item                  | Standard Value                                                              | Unit |

| Character Format      | 100X64 DOTS                                                                 | Dots |

| Module Dimension      | 34.1(W) *25.3(H) *2.0(T)                                                    | mm   |

| Viewing Area          | 28.0(W) * 20.9(H)                                                           | mm   |

| DOT Size              | 0.21(W) * 0.234(H)                                                          | mm   |

| DOT Pitch             | 0.24(W) * 0.264(H)                                                          | mm   |

| Driving               | 1/64duty, 1/9bias                                                           |      |

| View Direction        | 6H 12H Other:                                                               |      |

| LCD Type              | TNSTN GraySTN BlueSTN Yellow GreenFSTN PositiveFSTN NegativeColor STNFM LCD |      |

| Display Mode          | Reflective Transflective<br>Transmissive                                    |      |

| Driver IC             | NT7532H-TABF1                                                               |      |

| Interface             | 6800 8080 I <sup>2</sup> C                                                  |      |

| DC/DC Converter       | Internal External                                                           |      |

| Operation Temperature | -10 —60                                                                     |      |

| Storage Temperature   | -20 —70                                                                     |      |

## **Electronic Units**

#### **3.1 Absolute Maximum Ratings**

| No | ITEM                     | Symbol                                         | Min. | Тур. | Max.    | Unit |  |  |  |

|----|--------------------------|------------------------------------------------|------|------|---------|------|--|--|--|

| 1  | OPERATING TEMPERATURE    | T <sub>OP</sub>                                | -10  | -    | 60      |      |  |  |  |

| 2  | STORAGE TEMPERATURE      | T <sub>ST</sub>                                | -20  | -    | 70      |      |  |  |  |

| 3  | SUPPLY VOLTAGE FOR LOGIC | $V_{DD}$ - $V_{SS}$                            | VSS  |      | 3.6     | V    |  |  |  |

| 4  | SUPPLY VOLTAGE FOR LCD   | V <sub>LCD</sub>                               | VSS  |      | 13.5    | V    |  |  |  |

| 5  | INPUT VOLTAGE            | VI                                             | VSS  | -    | VDD+0.5 | V    |  |  |  |

| 6  | STATIC ELECTRICITY       | Be sure that you are grounded when handing LCM |      |      |         |      |  |  |  |

#### **3.2 Electrical Characteristics**

|    |                               |                                   | (         | Ta=25 ,     | V <sub>DD</sub> =3. | 0V)             |          |  |

|----|-------------------------------|-----------------------------------|-----------|-------------|---------------------|-----------------|----------|--|

| No | Item                          | Symbol                            | Condition | Min.        | Тур.                | Max.            | Uni<br>t |  |

| 1  | Supply Voltage For Logic      | $V_{DD}$ - $V_{SS}$               | /         | /           | 3.0                 | /               | V        |  |

| 2  | Supply Voltage For LCD Driver | $V_{DD}$ - $V_o$<br>( $V_{LCD}$ ) | /         | /           | 10.0                | /               | V        |  |

| 3  | Input High Voltage            | $V_{\mathrm{IH}}$                 | H level   | $0.8V_{DD}$ | /                   | V <sub>DD</sub> | V        |  |

| 4  | Input Low Voltage             | V <sub>IL</sub>                   | L level   | 0           | /                   | $0.2V_{DD}$     | V        |  |

| 5  | Supply Current For Logic      | I <sub>DD</sub>                   | /         | /           | /                   | 1               | mA       |  |

| 9  | USED IC                       | NT7532H-TABF1(NOVATEK)            |           |             |                     |                 |          |  |

\*Idd Measurement condition is for all pixels on display. (Unit: mA)

#### **3.3 Interface Pin Function**

| NO | SYMBOL | I/O                                                                                                                    | Description                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----|--------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1  | NC     |                                                                                                                        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 2  | NC     |                                                                                                                        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 3  | NC     |                                                                                                                        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 4  | NC     |                                                                                                                        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 5  | FR     | I/O                                                                                                                    | This is the liquid crystal alternating current signal I/O terminal M/S = "H": Output M/S = "H": Input When the NT7532 chip is used in master/slave mode, the various FR terminals must be connected.                                                                                                                      |  |  |  |  |  |

| 6  | CL     | I/O                                                                                                                    | This is the display clock input terminal. When the NT7532 chips are used in master/slave mode, the various CL terminals must be connected.                                                                                                                                                                                |  |  |  |  |  |

| 7  | /DOF   | I/O                                                                                                                    | This is the liquid crystal display blanking control terminal.<br>M/S = "H": Output<br>M/S = "H": Input<br>When the NT7532 chip is used in master/slave mode, the<br>various DOF terminals must be connected.                                                                                                              |  |  |  |  |  |

| 8  | NC     | NC                                                                                                                     |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 9  | /CS1   | This is the chip select signal. When CS1="L" and CS2="H", then the chip select becomes active, and data/command I/O is |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 10 | CS2    | Ι                                                                                                                      | enabled.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 11 | RES    | Ι                                                                                                                      | When RES is set to "L", the settings are initialized. The reset operation is performed by the RES signal level                                                                                                                                                                                                            |  |  |  |  |  |

| 12 | A0     | Ι                                                                                                                      | This is connected to the least significant bit of the normal MPU<br>address bus, and it determines whether the data bits are data<br>or a command.<br>A0 = "H": Indicate that D0 to D7 are display data<br>A0 = "L": Indicates that D0 to D7 are control data                                                             |  |  |  |  |  |

| 13 | RD/WR  | I                                                                                                                      | When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU WR signal. The signals on the data bus are latched at the rising edge of the WR signal. When connected to a 6800 Series MPU, this is the read/write control signal input terminal. When W R/ = "H": Read When W R/ = "L": Write |  |  |  |  |  |

| 14 | E/RD   | I                                                                                                                      | When connected to an 8080 MPU, it is active LOW. This pad is<br>connected to the RD signal of the 8080MPU, and the<br>NT7532 data bus is in an output status when this signal is "L".<br>When connected to a 6800 Series MPU, this is active HIGH.<br>This is used as an enable clock input of the 6800 series MPU        |  |  |  |  |  |

| 15 | D0     | I/O                                                                                                                    | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.                                                                                                                                                                                                                       |  |  |  |  |  |

| 16 | D1         |        |                                   |                                    | s selected (P/S="L"), then D7<br>nput terminal (SI) and D6 serves as                                                     |

|----|------------|--------|-----------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 17 | D2         |        | the serial cloc<br>set to high im | k input termi<br>pedance.          | nal (SCL). At this time, D0 to D5 are                                                                                    |

| 18 | D3         |        | When the chi<br>impedance.        | p select is ina                    | active, D0 to D7 are set to high                                                                                         |

| 19 | D4         |        |                                   |                                    |                                                                                                                          |

| 20 | D5         |        |                                   |                                    |                                                                                                                          |

| 21 | D6 ( SCL ) |        |                                   |                                    |                                                                                                                          |

| 22 | D7 (SI)    |        |                                   |                                    |                                                                                                                          |

|    |            |        | Select the LO                     | CD driver du                       | ty                                                                                                                       |

| 23 | DUTY0      |        | DUTY1                             | DUTY1                              | LCD driver duty                                                                                                          |

|    |            |        | 0                                 | 0                                  | 1/33                                                                                                                     |

|    | DI 107871  | Ι      | 0                                 | 1                                  | 1/49                                                                                                                     |

| 24 | DUTY1      |        | 1                                 | 0                                  | 1/55                                                                                                                     |

|    |            |        | 1                                 | 1                                  | 1/69                                                                                                                     |

| 25 | VDD        | Supply | 2.4 - 3.5V pove each other.       | wer supply in                      | put. These pads must be connected                                                                                        |

| 26 | VDD2       | Supply |                                   |                                    | or the step-up voltage circuit for the connected each other.                                                             |

| 27 | VSS        | Supply | Ground outpu                      | ıt for pad opti                    | on.                                                                                                                      |

| 28 | VOUT       | 0      | DC/DC voltag                      | je converter o                     | putput                                                                                                                   |

| 29 | NC         | NC     |                                   |                                    |                                                                                                                          |

| 30 | CAP3+      | 0      | Capacitor 3+                      | pad for interr                     | nal DC/DC voltage converter.                                                                                             |

| 31 | CAP1-      | 0      | Capacitor 1-                      | oad for intern                     | al DC/DC voltage converter.                                                                                              |

| 32 | CAP1+      | 0      | Capacitor 1+                      | pad for interr                     | nal DC/DC voltage converter.                                                                                             |

| 33 | CAP2+      | 0      | Capacitor 2+                      | pad for interr                     | nal DC/DC voltage converter.                                                                                             |

| 34 | CAP2-      | 0      | Capacitor 2- p                    | oad for intern                     | al DC/DC voltage converter.                                                                                              |

| 35 | VEXT       | I      | internal voltag                   | ge regulator.<br>T must be $\ge 2$ | eference voltage (VREF) for the<br>It is valid only when external VREF<br>2.4V and $\leq$ VDD2. When using<br>ust be NC. |

|          |            |        | Calact the in                                                                            |                                                                                                                               |                | utornal valtar   |              |  |  |  |  |  |

|----------|------------|--------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------|--|--|--|--|--|

| 26       | VDC        | т      |                                                                                          | nternal voltage re<br>ing the external                                                                                        |                | xternal voltage  | e regulator. |  |  |  |  |  |

| 36       | VRS        | Ι      |                                                                                          | 0                                                                                                                             |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | ing the internal<br>supplies voltages                                                                                         |                | o determined     | hul CD       |  |  |  |  |  |

| 37       | <b>V1</b>  |        |                                                                                          | ance-converted                                                                                                                | U U U          |                  |              |  |  |  |  |  |

| <u> </u> |            |        |                                                                                          | nplifier for applic                                                                                                           |                |                  |              |  |  |  |  |  |

| 20       | 172        |        |                                                                                          | the following re                                                                                                              |                |                  |              |  |  |  |  |  |

| 38       | V2         |        |                                                                                          | $\sqrt{2} = \sqrt{3} = \sqrt{4} = \sqrt{4}$                                                                                   |                |                  |              |  |  |  |  |  |

|          |            |        | -                                                                                        | -                                                                                                                             |                | t is on the foll | owing        |  |  |  |  |  |

| 39       | <b>V3</b>  | Supply |                                                                                          | When the on-chip operating power circuit is on, the following voltages are supplied to V1 to V4 by the on-chip power circuit. |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | Voltage selection is performed by the Set LCD Bias command.                                                                   |                |                  |              |  |  |  |  |  |

| 40       | <b>V4</b>  |        | LCD                                                                                      |                                                                                                                               |                |                  |              |  |  |  |  |  |

|          |            |        | 1/5                                                                                      | bias                                                                                                                          | 4/5V0          | 3/5V0            | 2/5V0        |  |  |  |  |  |

|          |            |        | 1/6                                                                                      | bias                                                                                                                          | 5/6V0          | 4/6V0            | 2/6V0        |  |  |  |  |  |

| 41       | V0         |        | 1/7                                                                                      | bias                                                                                                                          | 6/7V0          | 5/7V0            | 2/7V0        |  |  |  |  |  |

|          | VU         |        | 1/8                                                                                      | bias                                                                                                                          | 7/8V0          | 6/8V0            | 2/8V0        |  |  |  |  |  |

|          |            |        | 1/9                                                                                      | bias                                                                                                                          | 8/9V0          | 7/9V0            | 2/9V0        |  |  |  |  |  |

|          |            | -      | Voltage adju                                                                             | ustment pad. App                                                                                                              | olies voltage  | between V0 a     | and VSS      |  |  |  |  |  |

| 42       | VR         | Ι      | using a resis                                                                            | stive divider.                                                                                                                | -              |                  |              |  |  |  |  |  |

|          |            |        | This termina                                                                             | al selects the ma                                                                                                             | ster/slave op  | peration for the | Э            |  |  |  |  |  |

|          |            |        |                                                                                          | os. Master opera                                                                                                              |                |                  |              |  |  |  |  |  |

| 43       | M/S        | Ι      | that are requ                                                                            | uired for the LCE                                                                                                             | ) display, wh  | ile slave oper   | ation        |  |  |  |  |  |

|          |            |        |                                                                                          | ming signals req                                                                                                              |                |                  | display,     |  |  |  |  |  |

|          |            |        |                                                                                          | ng the liquid crys                                                                                                            |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | select whether e                                                                                                              | nable or dis   | able the displa  | ay clock     |  |  |  |  |  |

|          |            |        | internal osci                                                                            |                                                                                                                               |                |                  |              |  |  |  |  |  |

| 44       | CLS        | Ι      |                                                                                          | nternal oscillator                                                                                                            |                |                  |              |  |  |  |  |  |

|          | CLD        | -      |                                                                                          | nternal oscillator                                                                                                            | circuit is dis | abled            |              |  |  |  |  |  |

|          |            |        | (requires ex                                                                             | • •                                                                                                                           |                |                  | l mard       |  |  |  |  |  |

|          |            |        |                                                                                          | = "L", input the d<br>/IPU interface sv                                                                                       |                |                  | L pad.       |  |  |  |  |  |

| 45       | <b>CQ(</b> | Ι      |                                                                                          | 800 Series MPL                                                                                                                |                | 1                |              |  |  |  |  |  |

| 45       | C86        | 1      |                                                                                          | 080 MPU interfa                                                                                                               |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | arallel data inpu                                                                                                             |                | input switch to  | erminal      |  |  |  |  |  |

|          |            |        |                                                                                          | arallel data inpu                                                                                                             |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | erial data input                                                                                                              |                |                  |              |  |  |  |  |  |

|          |            |        | The followin                                                                             | g applies depen                                                                                                               | ding on the l  | P/S status:      |              |  |  |  |  |  |

|          |            |        | P/S                                                                                      | Data/Command                                                                                                                  | Data           | Read/Write       | Serial       |  |  |  |  |  |

| 46       | P/S        | Ι      | "H"                                                                                      | A0                                                                                                                            | D0 to D7       | RD WR            | -            |  |  |  |  |  |

|          |            |        | "L"                                                                                      | <u>A0</u>                                                                                                                     | SI (D7)        | Write only       | SCL (D6)     |  |  |  |  |  |

|          |            |        |                                                                                          | = "L", D0 to D5 ar                                                                                                            |                |                  |              |  |  |  |  |  |

|          |            |        | • •                                                                                      | ) and WR( W R                                                                                                                 | ,              |                  |              |  |  |  |  |  |

|          |            |        | Supported.                                                                               | lata input, RAM                                                                                                               | uispiay uala   | reading is not   |              |  |  |  |  |  |

| $\vdash$ |            |        |                                                                                          | ower control ter                                                                                                              | minal for the  | power supply     | , circuit    |  |  |  |  |  |

|          |            |        | for liquid cry                                                                           |                                                                                                                               |                |                  | Should       |  |  |  |  |  |

|          |            |        |                                                                                          | Normal mode                                                                                                                   |                |                  |              |  |  |  |  |  |

| 47       | /HPM       | Ι      | HPM = "L", High power mode<br>This pad is enabled only when the master operation mode is |                                                                                                                               |                |                  |              |  |  |  |  |  |

| , T      | /          | · ·    |                                                                                          |                                                                                                                               |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | d It is fixed to eit                                                                                                          |                |                  |              |  |  |  |  |  |

|          |            |        | operation m                                                                              | ode is selected.                                                                                                              |                |                  |              |  |  |  |  |  |

|          |            |        | This termina                                                                             | al selects the res                                                                                                            | istors for the | V0 voltage le    | vel          |  |  |  |  |  |

|          |            |        | adjustment.                                                                              |                                                                                                                               |                | -                |              |  |  |  |  |  |

| 48       | IRS        | Ι      |                                                                                          | lse the internal r                                                                                                            |                |                  |              |  |  |  |  |  |

|          |            |        |                                                                                          | o not use the int                                                                                                             |                |                  |              |  |  |  |  |  |

|          |            |        | The V0 volta                                                                             | age level is regu                                                                                                             | ated by an e   | external resisti | ve           |  |  |  |  |  |

|    |    |    | voltage divider attached to the VR terminal. This pad is<br>enabled only when the master operation mode is selected. It<br>is fixed to either "H" or "L" when the slave operation mode is<br>selected |

|----|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49 | NC | NC |                                                                                                                                                                                                       |

#### **3.4 Commands**

The display control instructions control the internal state of the NT7532H-TABF1(NOVATEK). Instruction is received from MPU to NT7532H-TABF1(NOVATEK) for the splay control. The following table shows various instructions.

\*: Don't care

| ~                           |    |    |    | Code                      |    |    |       |        |    |                |                  |                                           |                                                                       |

|-----------------------------|----|----|----|---------------------------|----|----|-------|--------|----|----------------|------------------|-------------------------------------------|-----------------------------------------------------------------------|

| Command                     | A0 | RD | WR | D7                        | D6 | D5 | D4    | D3     | D2 | D1             | D0               | Hex                                       | Function                                                              |

| Display OFF                 | 0  | 1  | 0  | 1                         | 0  | 1  | 0     | 1      | 1  | 1              | 0<br>1           | AEh<br>AFh                                | Turn on LCD panel<br>when goes<br>high, and turn off<br>when goes low |

| Set Display<br>Start Line   | 0  | 1  | 0  | 0 1 Display Start Address |    |    |       |        |    |                | 40h<br>TO<br>7Fh | Specifies RAM<br>display line for<br>COM0 |                                                                       |

| Set Page<br>Address         | 0  | 1  | 0  | 1                         | 0  | 1  | 1     |        | Ū. | Address        |                  | B0h<br>to<br>BFh                          | Set the display data<br>RAM page in<br>Page Address register          |

| Set Column                  | 0  | 1  | 0  | 0                         | 0  | 0  | 1     | H      |    | Colum<br>lress | in               | 00h                                       | Set 4 higher bits and 4 lower bits                                    |

| Address                     | 0  | 1  | 0  | 0                         | 0  | 0  | 0     | L      |    | Colum<br>lress | n                | TO<br>1Fh                                 | of column address of<br>display data<br>RAM in register               |

| Read Status                 | 0  | 0  | 1  | Status 0 0 0 0            |    |    |       |        |    | 0              | XX               | Reads the status information              |                                                                       |

| Write Display<br>Data       | 1  | 1  | 0  |                           |    |    | Write | e Data |    |                |                  | XX                                        | Write data in display data RAM                                        |

| Read Display<br>Data        | 1  | 0  | 1  |                           |    |    | Read  | l Data |    |                |                  | XX                                        | Read data from<br>display data RAM                                    |

| ADC Select                  | 0  | 1  | 0  | 1                         | 0  | 1  | 0     | 0      | 0  | 0              | 0<br>1           | A0h<br>A1h                                | Set the display data<br>RAM address<br>SEG output<br>correspondence   |

| Normal/Rever<br>se Display  | 0  | 1  | 0  | 1                         | 0  | 1  | 0     | 0      | 1  | 1              | 0<br>1           | A6h<br>A7h                                | Normal indication<br>when low, but<br>full indication when<br>high    |

| Entire<br>Display<br>ON/OFF | 0  | 1  | 0  | 1                         | 0  | 1  | 0     | 0      | 1  | 0              | 0<br>1           | A4h<br>A5h                                | Selects normal<br>display (0) or entire<br>display on                 |

| Set LCD Bias                | 0  | 1  | 0  | 1                         | 0  | 1  | 0     | 0      | 0  | 1              | 01               | A2h<br>A3h                                | Sets LCD driving voltage bias ratio                                   |

| Read-Modify-<br>Write       | 0  | 1  | 0  | 1                         | 1  | 1  | 0     | 0      | 0  | 0              | 0                | E0h                                       | Increments column<br>address<br>counter during each<br>write          |

| End                         | 0  | 1  | 0  | 1                         | 1  | 1  | 0     | 1      | 1  | 1              | 0                | EEh                                       | Releases the<br>Read-Modify-Write                                     |

| Reset                                                        | 0 | 1 | 0 | 1 | 1 | 1                        | 0 | 0      | 0 | 1                   | 0      | E2h                                                            | Resets internal functions                                      |

|--------------------------------------------------------------|---|---|---|---|---|--------------------------|---|--------|---|---------------------|--------|----------------------------------------------------------------|----------------------------------------------------------------|

| Common<br>Output Mode<br>Select                              | 0 | 1 | 0 | 1 | 1 | 0                        | 0 | 0<br>1 | * | *                   | *      | C0h<br>to<br>CFh                                               | Selects COM output<br>scan direction<br>*: invalid data        |

| Set Power<br>Control                                         | 0 | 1 | 0 | 0 | 0 | 1                        | 0 | 1      |   | Operation<br>Status |        | 28h<br>to<br>2Fh                                               | Selects the power<br>circuit operation<br>mode                 |

| V0 Voltage<br>Regulator<br>Internal<br>Resistor ratio<br>Set | 0 | 1 | 0 | 0 | 0 | 1                        | 0 | 0      |   | Resistor Ratio      |        | 20h<br>to<br>27h                                               | Selects internal<br>resistor ratio<br>Rb/Ra mode               |

| Electronic                                                   | 0 | 1 | 0 | 1 | 0 | 0                        | 0 | 0      | 0 | 0                   | 1      | 81h                                                            |                                                                |

| Volume<br>mode Set<br>Electronic<br>Volume<br>Register Set   | 0 | 1 | 0 | * | * | Electronic Control Value |   |        |   |                     | XX     | Sets the V0 output<br>voltage<br>electronic volume<br>register |                                                                |

| Set Static<br>indicator<br>ON/OFF                            | 0 | 1 | 0 | 0 | 0 | 1                        | 0 | 1      | 0 | 1                   | 0<br>1 | ACh<br>ADh                                                     | Sets static indicator<br>ON/OFF<br>0: OFF, 1: ON               |

| Set Static<br>Indicator<br>Register                          | 0 | 1 | 0 | * | * | *                        | * | *      | * | Mo                  | ode    | XX                                                             | Sets the flash mode                                            |

| Power Save                                                   | 0 | 1 | 0 | - | - | -                        | - | -      | - | -                   | -      | -                                                              | Compound command<br>of Display<br>OFF and Entire<br>Display ON |

| NOP                                                          | 0 | 1 | 0 | 1 | 1 | 1                        | 0 | 0      | 0 | 1                   | 1      | E3h                                                            | Command for<br>non-operation                                   |

| Test<br>Command                                              | 0 | 1 | 0 | 1 | 1 | 1                        | 1 | *      | * | *                   | *      | F1h<br>to<br>FFh                                               | IC test command. Do not use!                                   |

| Test Mode<br>Reset                                           | 0 | 1 | 0 | 1 | 1 | 1                        | 1 | 0      | 0 | 0                   | 0      | F0h                                                            | Command of test<br>mode reset                                  |

#### **3.5 Timing Characteristics**

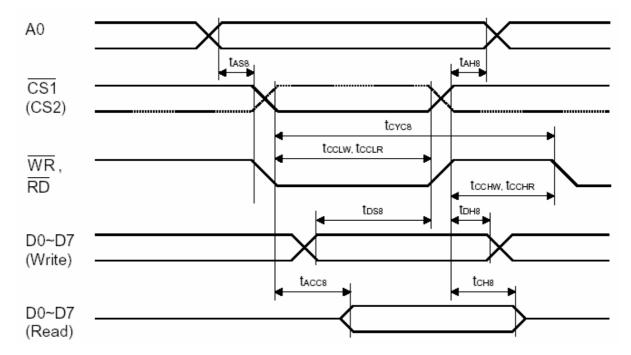

1. System Buses Read/Write Characteristics (for 8080 Series MPU)

| Symbol            | Parameter                        | Min | TYP | MAX | UNIT | Condition   |  |

|-------------------|----------------------------------|-----|-----|-----|------|-------------|--|

| T <sub>AH8</sub>  | Address hold time                | 0   | -   | -   | ns   | A0          |  |

| T <sub>AS8</sub>  | Address setup time               | 0   | -   | -   | ns   | AU          |  |

| T <sub>CYC8</sub> | System cycle time                | 300 | -   | -   | ns   | SCL         |  |

| T <sub>EWHW</sub> | Control low pulse width (write)  | 90  | -   | -   | ns   | WR          |  |

| T <sub>EWHR</sub> | Control low pulse width (read)   | 120 | -   | -   | ns   | RD          |  |

| T <sub>EWLW</sub> | Control high pulse width (write) | 120 | -   | -   | ns   | WR          |  |

| T <sub>EWLR</sub> | Control high pulse width (read)  | 60  | -   | -   | ns   | RD          |  |

| T <sub>DS8</sub>  | Data setup time                  | 40  | -   | -   | ns   | D0~D7       |  |

| T <sub>DH8</sub>  | Data hold time                   | 15  | -   | -   | ns   | D0~D7       |  |

| T <sub>ACC8</sub> | /RD access time                  | -   | -   | 140 | ns   | D0~D7,      |  |

| T <sub>OH8</sub>  | Output disable time              | 10  | -   | 400 | ns   | CL = 100 pF |  |

\*1. The input signal rise time and fall time  $(t_r, t_f)$  is specified at 15ns or less.

$(t_r + t_f) < (t_{CYC8} - t_{CCLW} - t_{CCHW}) \text{ for write, } (tr + t_f) < (t_{CYC8} - t_{CCLR} - t_{CCHR}) \text{ for read.}$

\*2. All timing is specified using 20% and 80% of VDD as the reference.

\*3.  $t_{CCLW}$  and  $t_{CCLR}$  are specified as the overlap interval when CS1 is low (CS2 is high) and WR or RD is low.

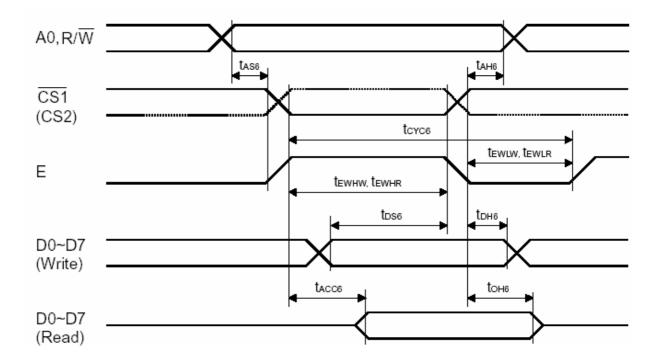

| Symbol            | Parameter                        | Min | TYP | MAX | UNIT | Condition   |  |

|-------------------|----------------------------------|-----|-----|-----|------|-------------|--|

| T <sub>AH6</sub>  | Address hold time                | 0   | -   | -   | ns   | A0          |  |

| T <sub>AS6</sub>  | Address setup time               | 0   | -   | -   | ns   | AU          |  |

| T <sub>CYC6</sub> | System cycle time                | 300 | -   | -   | ns   | SCL         |  |

| T <sub>EWHW</sub> | Control low pulse width (write)  | 90  | -   | -   | ns   | WR          |  |

| T <sub>EWHR</sub> | Control low pulse width (read)   | 120 | -   | -   | ns   | RD          |  |

| T <sub>EWLW</sub> | Control high pulse width (write) | 120 | -   | -   | ns   | WR          |  |

| T <sub>EWLR</sub> | Control high pulse width (read)  | 60  | -   | -   | ns   | RD          |  |

| T <sub>DS6</sub>  | Data setup time                  | 40  | -   | -   | ns   | D0~D7       |  |

| T <sub>DH6</sub>  | Data hold time                   | 15  | -   | -   | ns   | D0~D7       |  |

| T <sub>ACC6</sub> | /RD access time                  | -   | -   | 140 | ns   | D0~D7,      |  |

| T <sub>OH6</sub>  | Output disable time              | 10  | -   | 400 | ns   | CL = 100 pF |  |

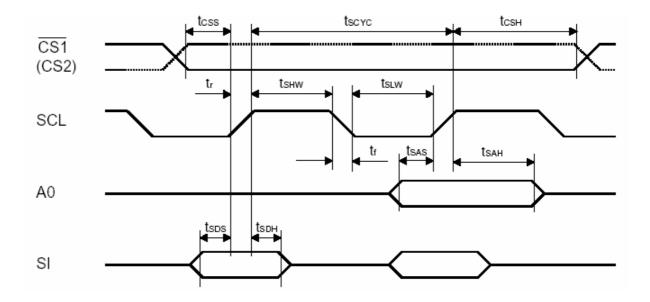

#### 3. Serial Interface Timing

| Symbol            | Parameter                     | Min | TYP | MAX | UNIT | Condition |

|-------------------|-------------------------------|-----|-----|-----|------|-----------|

| T <sub>SCYC</sub> | Serial clock cycle            | 250 | -   | -   | ns   | SCL       |

| T <sub>SHW</sub>  | Serial clock H pulse<br>width | 100 | -   | -   | ns   | SCL       |

| T <sub>SLW</sub>  | Serial clock L pulse<br>width | 100 | -   | -   | ns   | SCL       |

| T <sub>SAS</sub>  | Address setup time            | 150 | -   | -   | ns   | D/I       |

| T <sub>SAH</sub>  | Address hold time             | 150 | -   | -   | ns   | D/I       |

| T <sub>SDS</sub>  | Data setup time               | 100 | -   | -   | ns   | SDI       |

| T <sub>SDH</sub>  | Data hold time                | 100 | -   | -   | ns   | SDI       |

| T <sub>CSS</sub>  | Chip select setup time        | 150 | -   | -   | ns   | CS1, CS2  |

| T <sub>CSH</sub>  | Chip select hold time         | 150 | -   | -   | ns   | CS1, CS2  |

\*1. The input signal rise time and fall time (tr, tr) is specified at 15ns or less.

\*2. All timing is specified using 20% and 80% of VDD as the standard.

# **Electro-optical Units**

## 4.1 Electro-optical Characteristics

| No | Item                      |            | Symbol          | Condition                                 | Min | Тур | Max | Unit | Drive                                                                   |

|----|---------------------------|------------|-----------------|-------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------|

| 1  | Contrast Ratio            |            | C <sub>R</sub>  | $T_a=23\pm3$                              | -   | 5.5 | -   | -    |                                                                         |

| 2  | Response<br>time          | Rise       | T <sub>r</sub>  | 1 <b>=</b> 2 <b>=</b>                     | -   | 260 | -   | ms   |                                                                         |

|    |                           | Down       | $T_{\rm f}$     | <sub>3</sub> = <sub>4</sub> =0            | -   | 200 | -   | ms   |                                                                         |

| 3  | Viewing<br>Angle<br>Range | 6H<br>=270 | 1               |                                           | -   | 60  | -   | Deg  | V <sub>op</sub> =10V<br>1/64<br>Duty<br>1/9 Bias<br>f=100H <sub>Z</sub> |

|    |                           | 12H<br>=90 | 2               | T <sub>a</sub> =23±3<br>C <sub>r</sub> =2 | -   | 25  | -   |      |                                                                         |

|    |                           | 3H<br>=0   | 3               | C <sub>r</sub> =2                         | -   | 50  | -   |      |                                                                         |

|    |                           | 9Н<br>=180 | 4               |                                           | -   | 50  | -   |      |                                                                         |

| 4  | LCD Driving<br>Voltage    |            | V <sub>OP</sub> | T <sub>a</sub> =23±3                      | -   | 10  | -   | V    |                                                                         |