# **Features**

**PowerManager**™

# **General Description**

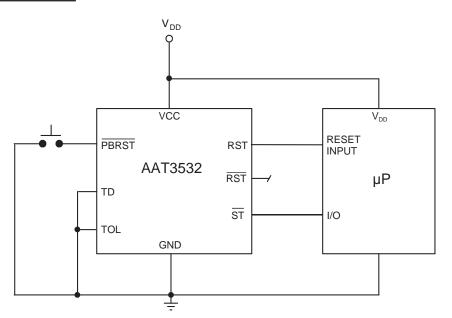

The AAT3532 PowerManager is a member of AnalogicTech's Total Power Management IC™ (TPMIC™) product family. It is a fully integrated device for monitoring microprocessor activity, external reset, and power supply conditions. The device holds the microprocessor in a reset condition for a minimum of 250ms while V<sub>CC</sub> is established to ensure correct system start-up. A manual reset can be initiated via a de-bounced input pin. As an additional level of protection, the AAT3532 includes a watchdog timer which requires a periodic strobe input from the microprocessor to ensure correct operation. The AAT3532 has a programmable watchdog timer and voltage tolerance level. The quiescent supply current is extremely low, typically 23µA.

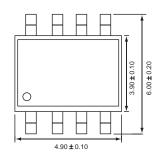

The AAT3532 is available in a Pb-free, 8-pin SOP package and is specified over the -40°C to +85°C temperature range.

- Adjustable 4.5V or 4.75V Voltage Monitor

- 250ms (min) Reset Pulse Width

- Low Quiescent Current: Typically 23µA

- Adjustable Watchdog Timer (150ms, 600ms, or 1200ms)

- De-bounced Manual Reset Input

- Operates Down to 20ns Strobe Input Pulse Width

- No External Components

- Temperature Range: -40° to +85°C

- Standard 8-Pin SOP Package

- Pin Compatible with MAX1232

# **Applications**

- Automotive

- Computers

- Controllers

- Embedded Systems

- Intelligent Instrumentation

- Telecom Equipment

# **Typical Application**

# **Pin Descriptions**

| Pin # | Symbol | Function                                                                                                                                                                                                                     |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PBRST  | Push-button reset input. A de-bounced active low input for manual reset. Guaranteed                                                                                                                                          |

|       |        | to recognize inputs 20ms or greater.                                                                                                                                                                                         |

| 2     | TD     | Watchdog time delay set input. See Table 1 for watchdog timeout selections.                                                                                                                                                  |

| 3     | TOL    | Tolerance set. Input selects 5% or 10% threshold detection.                                                                                                                                                                  |

| 4     | GND    | IC ground connection.                                                                                                                                                                                                        |

| 5     | RST    | Reset output (active high). Activated when either: $V_{CC}$ falls below the reset voltage threshold; $\overline{PBRST}$ is forced low; $\overline{ST}$ is not strobed within the minimum timeout period; or during power-up. |

| 6     | RST    | Reset output (active low, open drain). Inverse of RST.                                                                                                                                                                       |

| 7     | ST     | Strobe input to watchdog timer. A pulse is required within the watchdog timeout period to prevent RST and RST entering active state.                                                                                         |

| 8     | VCC    | 5V supply.                                                                                                                                                                                                                   |

# **Pin Programming Selections**

|                 | Timeout |        |        |

|-----------------|---------|--------|--------|

| TD Pin          | Min     | Тур    | Max    |

| GND             | 62.5ms  | 150ms  | 250ms  |

| Float           | 250ms   | 600ms  | 1000ms |

| V <sub>CC</sub> | 500ms   | 1200ms | 2000ms |

**Table 1: TD Pin Programming for Watchdog Timeout Selections.**

| TOL Pin         | Tolerance |

|-----------------|-----------|

| V <sub>CC</sub> | 10%       |

| GND             | 5%        |

**Table 2: Reset Voltage Threshold Programming Selections.**

# **Pin Configuration**

SOP-8 (Top View)

# MicroPower™ Microprocessor Reset Circuit

# Absolute Maximum Ratings<sup>1</sup>

$T_A = 25$ °C, unless otherwise noted.

| Symbol            | Description                                      | Value                          | Units |

|-------------------|--------------------------------------------------|--------------------------------|-------|

| V <sub>CC</sub>   | V <sub>CC</sub> to GND                           | -0.5 to 6                      | V     |

| V <sub>I/O</sub>  | Voltage on I/O Pins Relative to GND              | -0.5 to (V <sub>CC</sub> +0.5) | V     |

| T <sub>A</sub>    | Operating Temperature Range                      | -40 to 85                      | °C    |

| T <sub>S</sub>    | Storage Temperature Range                        | -65 to 150                     | °C    |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at leads) for 10s | 300                            | °C    |

| V <sub>ESD</sub>  | ESD Rating <sup>2</sup> —HBM                     | 2000                           | V     |

# Thermal Characteristics<sup>3</sup>

| Symbol         | Description                                | Value | Units |  |

|----------------|--------------------------------------------|-------|-------|--|

| $\Theta_{JA}$  | Θ <sub>JA</sub> Maximum Thermal Resistance |       | °C/W  |  |

| P <sub>D</sub> | Maximum Power Dissipation                  | 1.25  | W     |  |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

<sup>3.</sup> Mounted on an FR4 board.

$\frac{\text{DC Electrical Characteristics}}{\text{V}_{\text{IN}} = 4.5 \text{V to } 5.5 \text{V}, \, \text{T}_{\text{A}} = -40 ^{\circ} \text{C to } +85 ^{\circ} \text{C}, \, \text{unless otherwise noted.}}$  Typical values are  $\text{T}_{\text{A}} = 25 ^{\circ} \text{C}.$

| Symbol            | Description                     | Conditions             |             | Min  | Тур  | Max            | Units |

|-------------------|---------------------------------|------------------------|-------------|------|------|----------------|-------|

| V <sub>cc</sub>   | Supply Voltage                  |                        |             | 4.5  | 5.0  | 5.5            | V     |

|                   | Outpount Comment                | \/                     | CMOS Levels |      | 23   | 50             | μA    |

| I <sub>Q</sub>    | Quiescent Current <sup>1</sup>  | $V_{CC} = 5.5V$        | TTL Levels  |      | 160  | 500            |       |

| \/                | Reset Threshold 5% TOL = GI     |                        | •           | 4.50 | 4.62 | 4.74           | V     |

| V <sub>CCTP</sub> | Reset Threshold 10%             | $TOL = V_{CC}$         |             | 4.25 | 4.37 | 4.49           | V     |

| I <sub>IL</sub>   | Input Leakage ST, TOL           |                        |             | -1.0 |      | 1.0            | μΑ    |

| I <sub>OH</sub>   | Output Current RST <sup>2</sup> | V <sub>OH</sub> = 2.4V |             | -8.0 |      |                | mA    |

| I <sub>OL</sub>   | Current RST <sup>2</sup> , RST  | $V_{OL} = 0.4V$        |             | 10.0 |      |                | mA    |

| V <sub>IH</sub>   | ST and PBRST Input High         |                        |             | 2.0  |      | $V_{CC} + 0.3$ | V     |

| V <sub>IL</sub>   | ST and PBRST Input Low          |                        |             | -0.3 |      | 0.8            | V     |

| I <sub>RST</sub>  | RST Output Leakage              | $V_{OH} = V_{CC}$      |             |      |      | 1.0            | μΑ    |

# **AC Electrical Characteristics**

$\overline{V_{IN}}$  = 4.5V to 5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are  $T_A$  = 25°C.

| Symbol           | Description                                    | Conditions               | Min  | Тур  | Max  | Units |

|------------------|------------------------------------------------|--------------------------|------|------|------|-------|

| C <sub>IN</sub>  | Input Capacitance ST, TOL <sup>3</sup>         | $T_A = 25^{\circ}C$      |      |      | 5    | pF    |

| C <sub>OUT</sub> | Output Capacitance RST, RST <sup>3</sup>       | $T_A = 25^{\circ}C$      |      |      | 7    | pF    |

| t <sub>PB</sub>  | PBRST⁴                                         | See Figure 2             | 20   |      |      | ms    |

| t <sub>PBD</sub> | PBRST Delay                                    | See Figure 2             | 1    | 4    | 20   | ms    |

| t <sub>RST</sub> | Reset Active Time                              |                          | 250  | 610  | 1000 | ms    |

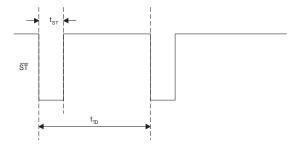

| t <sub>ST</sub>  | ST Pulse Width                                 | See Figure 3             | 20   |      |      | ns    |

|                  |                                                | TD Pin = 0V              | 62.5 | 150  | 250  |       |

| t <sub>TD</sub>  | ST Time-out Period                             | TD Pin = Open            | 250  | 600  | 1000 | ms    |

|                  |                                                | TD Pin = V <sub>CC</sub> | 500  | 1200 | 2000 |       |

| t <sub>f</sub>   | V <sub>CC</sub> Fall Time <sup>3</sup>         | 4.75V to 4.25V           | 10   |      |      | μs    |

| t <sub>r</sub>   | V <sub>CC</sub> Rise Time <sup>3</sup>         | 4.25V to 4.75V           | 0    | 5    |      | μs    |

| t <sub>RPD</sub> | V <sub>CC</sub> Detect to RST High and RST Low | V <sub>CC</sub> Falling  |      |      | 50   | μs    |

| t <sub>RPU</sub> | V <sub>CC</sub> Detect to RST Low and RST Open | V <sub>CC</sub> Rising   | 250  | 610  | 1000 | ms    |

<sup>1.</sup> Measured with outputs open and  $\overline{ST}$  toggling at 100kHz, 50% duty cycle.

<sup>2.</sup> RST is an open drain output.

<sup>3.</sup> Guaranteed by design and not subject to production testing.

<sup>4.</sup> PBRST must remain low for greater than 20ms to guarantee a reset.

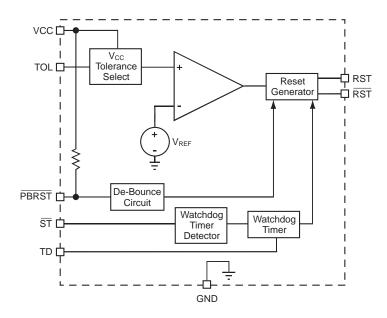

# **Functional Block Diagram**

# **Applications Information**

### **Power Monitor**

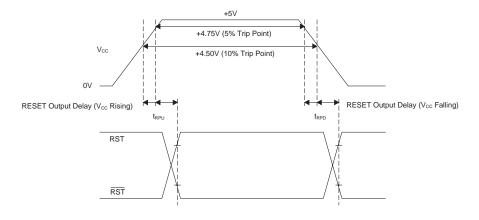

The reset function monitors the  $V_{CC}$  supply to ensure a microprocessor is correctly reset and is powered up into a known condition following a power supply failure. RST and  $\overline{RST}$  will remain valid for  $V_{CC}$  voltages down to 1.4V.

The RST and  $\overline{RST}$  pins are asserted whenever  $V_{CC}$  drops below the reset threshold voltage. This volt-

age can be set by programming the TOL pin. Connecting TOL to  $V_{CC}$  sets the 10% tolerance of the  $V_{CC}$  supply (typically 4.37V for  $V_{CC}=5$ V). Connecting TOL to GND sets the 5% tolerance of the  $V_{CC}$  supply (typically 4.62V for  $V_{CC}=5$ V). The reset pin is guaranteed to remain asserted for a minimum period of 250ms after  $V_{CC}$  has risen above the reset threshold voltage. (See Figure 1.)

RST output is an open drain output. For correct operation, a pull-up resistor of  $10k\Omega$  should be connected between this output and  $V_{CC}$ .

Figure 1: Reset Output Delay.

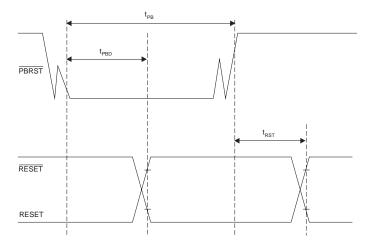

### Manual Reset

The PBRST pin makes it possible to manually reset the system by either directly connecting a mechanical push-button between the PBRST pin and GND or connecting to a logic low output. Internal de-bounce circuitry is provided to reduce

the effect of noise glitches at the input. The signal should remain low for a minimum of 20ms for correct operation. Once the PBRST signal is released (or goes to a logic high), RESET (RESET) remains asserted for a minimum of 250ms.

Figure 2: Push-Button Reset.

## **Watchdog Timer**

The watchdog timer monitors the microprocessor to ensure that the system is functioning correctly. The ST pin of the AAT3532 can be derived from the microprocessor data signals, address signals, and/or I/O signals. The watchdog timer function forces the RST and RST signals into the active state when the ST input is not toggled by a predetermined time. This time period is set by the logic state of the TD pin, as shown in Table 1. The timer

starts once the RST signals become inactive. If the watchdog timer does not receive a high-to-low transition within the specified timeout period, then the RST signals are activated for a minimum 250ms. In normal operation, the timer should receive a transition from the microprocessor within the timeout period, in which case the timer is reset and normal operation continues.

The AAT3532 will accept and recognize  $\overline{ST}$  pulses down to a minimum of 20ns wide.

Figure 3: Watchdog Input.

6 3532.2005.12.1.2

# **Ordering Information**

| Package | Marking | Part Number (Tape and Reel) <sup>1</sup> |

|---------|---------|------------------------------------------|

| SOP-8   | 3532    | AAT3532IAS-T1                            |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

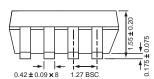

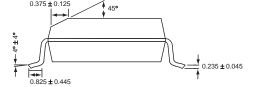

# **Package Information**

SOP-8

All dimensions in millimeters.

<sup>1.</sup> Sample stock is generally held on all part numbers listed in BOLD.

# AAT3532 MicroPower™ Microprocessor Reset Circuit

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. AnalogicTech warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with AnalogicTech's standard warranty. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed.

# Advanced Analogic Technologies, Inc.

830 E. Arques Avenue, Sunnyvale, CA 94085 Phone (408) 737-4600 Fax (408) 737-4611

8 3532,2005.12.1.2